Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 13-Bit Differential Input, Low Power A/D Converter with SPI Serial Interface

#### **Features**

- · Full Differential Inputs

- 2 Differential or 4 Single-ended inputs (MCP3302)

- 4 Differential or 8 Single-ended Inputs (MCP3304)

- · ±1 LSB maximum DNL

- ±1 LSB maximum INL (MCP3302/04-B)

- ±2 LSB maximum INL (MCP3302/04-C)

- Single supply operation: 4.5V to 5.5V

- 100 ksps sampling rate with 5V supply voltage

- 50 nA typical standby current, 1 μA maximum

- 450 µA maximum active current at 5V

- Industrial Temperature Range: -40°C to +85°C

- 14 and 16-pin PDIP, SOIC, and TSSOP packages

- Mixed Signal PICtail™ Demo Board (P/N: MXSIGDM) compatible

#### **Applications**

- Remote Sensors

- · Battery-operated Systems

- · Transducer Interface

#### **General Description**

The MCP3302/04 13-bit A/D converter features full differential inputs and low-power consumption in a small package that is ideal for battery-powered systems and remote data acquisition applications.

The MCP3302 is user-programmable to provide two differential input pairs or four single-ended inputs.

The MCP3304 is also user-programmable to configure into four differential input pairs or eight single-ended inputs.

Incorporating a successive approximation architecture with on-board sample and hold circuitry, these 13-bit A/D converters are specified to have ±1 LSB Differential Nonlinearity (DNL); ±1 LSB Integral Nonlinearity (INL) for B-grade and ±2 LSB for C-grade devices. The industry-standard SPI serial interface enables 13-bit A/D converter capability to be added to any PIC® microcontroller.

The MCP3302/04 devices feature low current design that permits operation with typical standby and active currents of only 50 nA and 300  $\mu$ A, respectively. The device is capable of conversion rates of up to 100 ksps with tested specifications over a 4.5V to 5.5V supply range. The reference voltage can be varied from 400 mV to 5V, yielding input-referred resolution between 98  $\mu$ V and 1.22 mV.

The MCP3302 is available in 14-pin PDIP, 150 mil SOIC and TSSOP packages. The MCP3304 is available in 16-pin PDIP and 150 mil SOIC packages. The full differential inputs of these devices enable a wide variety of signals to be used in applications such as remote data acquisition, portable instrumentation, and battery-operated applications.

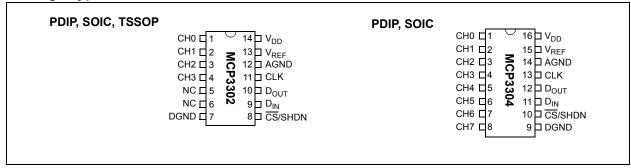

#### **Package Types**

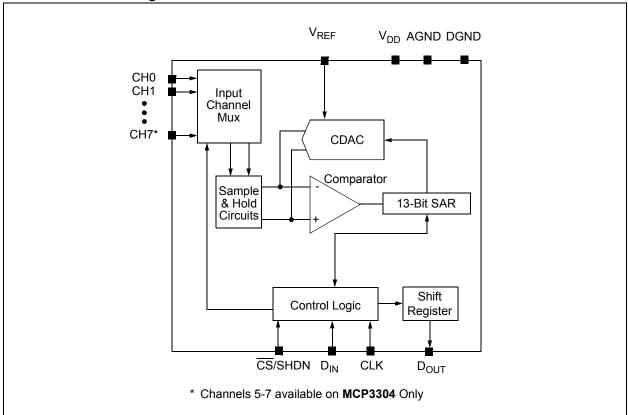

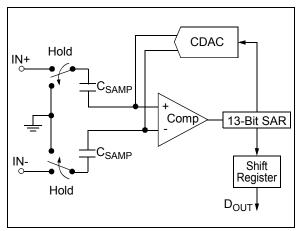

### **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| V <sub>DD</sub>                               | 7.0V                          |

|-----------------------------------------------|-------------------------------|

| All inputs and outputs w.r.t. V <sub>SS</sub> | 0.3V to V <sub>DD</sub> +0.3V |

| Storage temperature                           | 65°C to +150°C                |

| Ambient temp. with power applied              | 65°C to +125°C                |

| Maximum Junction Temperature                  | 150°C                         |

| ESD protection on all pins (HBM)              | > 4 kV                        |

**† Notice:** Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL SPECIFICATIONS**

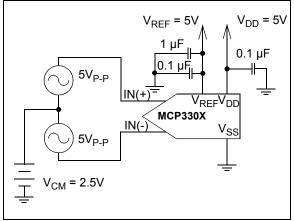

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{SS}$  = 0V, and  $V_{REF}$  = 5V. Full differential input configuration (Figure 1-5) with fixed common mode voltage of 2.5V. All parameters apply over temperature with  $T_A$  = -40°C to +85°C (Note 7). Conversion speed ( $F_{SAMPLE}$ ) is 100 ksps with  $F_{CLK}$  = 21\* $F_{SAMPLE}$

| , , GAINI EE                   |                     |     | <u>'</u>  | OLIN     | <b>L</b> |                                            |  |  |

|--------------------------------|---------------------|-----|-----------|----------|----------|--------------------------------------------|--|--|

| Parameter                      | Symbol              | Min | Тур       | Max      | Units    | Conditions                                 |  |  |

| Conversion Rate                |                     |     |           |          |          |                                            |  |  |

| Maximum Sampling Frequency     | F <sub>SAMPLE</sub> | _   | _         | 100      | ksps     | See F <sub>CLK</sub> specification. Note 8 |  |  |

| Conversion Time                | T <sub>CONV</sub>   |     | 13        |          | CLK      |                                            |  |  |

|                                |                     |     |           |          | periods  |                                            |  |  |

| Acquisition Time               | T <sub>ACQ</sub>    |     | 1.5       |          | CLK      |                                            |  |  |

|                                |                     |     |           |          | periods  |                                            |  |  |

| DC Accuracy                    |                     |     |           |          |          |                                            |  |  |

| Resolution                     |                     | 12  | data bits | + sign   | bits     |                                            |  |  |

| Integral Nonlinearity          | INL                 | _   | ±0.5      | ±1       | LSB      | MCP3302/04-B                               |  |  |

|                                |                     | _   | ±1        | ±2       | LSB      | MCP3302/04-C                               |  |  |

| Differential Nonlinearity      | DNL                 | _   | ±0.5      | ±1       | LSB      | Monotonic over temperature                 |  |  |

| Positive Gain Error            |                     | -3  | -0.75     | +2       | LSB      |                                            |  |  |

| Negative Gain Error            |                     | -3  | -0.5      | +2       | LSB      |                                            |  |  |

| Offset Error                   |                     | -3  | +3        | +6       | LSB      |                                            |  |  |

| Dynamic Performance            |                     |     |           |          |          |                                            |  |  |

| Total Harmonic Distortion      | THD                 | _   | -91       | _        | dB       | Note 3                                     |  |  |

| Signal-to-Noise and Distortion | SINAD               | _   | 78        |          | dB       | Note 3                                     |  |  |

| Spurious Free Dynamic Range    | SFDR                | _   | 92        | _        | dB       | Note 3                                     |  |  |

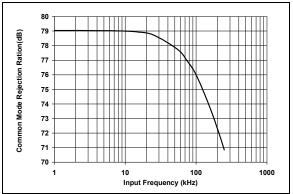

| Common Mode Rejection          | CMRR                | _   | 79        | _        | dB       | Note 6                                     |  |  |

| Channel to Channel Crosstalk   | СТ                  | _   | > -110    | _        | dB       | Note 6                                     |  |  |

| Power Supply Rejection         | PSR                 | _   | 74        | _        | dB       | Note 4                                     |  |  |

| Reference Input                |                     |     |           |          |          |                                            |  |  |

| Voltage Range                  |                     | 0.4 | _         | $V_{DD}$ | V        | Note 2                                     |  |  |

| Current Drain                  |                     | _   | 100       | 150      | μΑ       |                                            |  |  |

|                                |                     | _   | 0.001     | 3        | μA       | <u>CS</u> = V <sub>DD</sub> = 5V           |  |  |

|                                |                     |     |           |          |          |                                            |  |  |

- Note 1: This specification is established by characterization and not 100% tested.

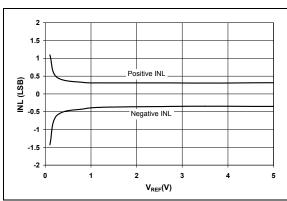

- 2: See characterization graphs that relate converter performance to  $V_{\mbox{\scriptsize REF}}$  level.

- 3:  $V_{IN} = 0.1V \text{ to } 4.9V @ 1 \text{ kHz}.$

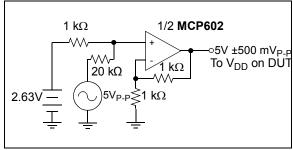

- 4:  $V_{DD}$  =5V DC ±500 mV<sub>P-P</sub> @ 1 kHz, see test circuit Figure 1-4.

- 5: Maximum clock frequency specification must be met.

- **6:**  $V_{REF} = 400 \text{ mV}, V_{IN} = 0.1 \text{V to } 4.9 \text{V} @ 1 \text{ kHz}.$

- 7: TSSOP devices are only specified at 25°C and +85°C.

- 8: For slow sample rates, see Section 5.2 "Driving the Analog Input" for limitations on clock frequency.

- **9:** 4.5V 5.5V is the supply voltage range for specified performance.

### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{SS}$  = 0V, and  $V_{REF}$  = 5V. Full differential input configuration (Figure 1-5) with fixed common mode voltage of 2.5V. All parameters apply over temperature with  $T_A$  = -40°C to +85°C (Note 7). Conversion speed ( $F_{SAMPLE}$ ) is 100 ksps with  $F_{CLK}$  = 21\* $F_{SAMPLE}$

| Parameter                        | Symbol                             | Min                 | Тур      | Max                   | Units | Conditions                                           |  |  |

|----------------------------------|------------------------------------|---------------------|----------|-----------------------|-------|------------------------------------------------------|--|--|

| Analog Inputs                    |                                    |                     |          |                       |       |                                                      |  |  |

| Full Scale Input Span            | CH0 - CH7                          | -V <sub>REF</sub>   | _        | $V_{REF}$             | V     |                                                      |  |  |

| Absolute Input Voltage           | CH0 - CH7                          | -0.3                | _        | V <sub>DD</sub> + 0.3 | V     |                                                      |  |  |

| Leakage Current                  |                                    | _                   | 0.001    | ±1                    | μΑ    |                                                      |  |  |

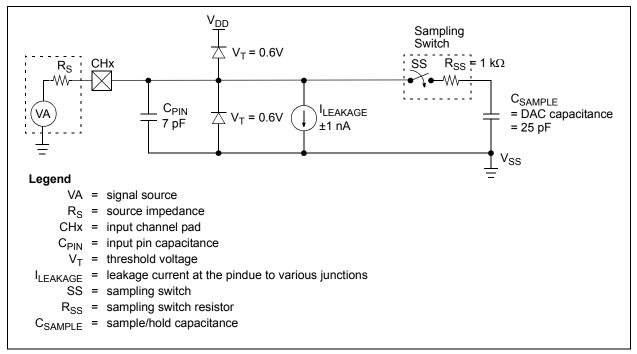

| Switch Resistance                | R <sub>S</sub>                     | _                   | 1        | _                     | kΩ    | See Figure 5-3                                       |  |  |

| Sample Capacitor                 | C <sub>SAMPLE</sub>                | _                   | 25       | _                     | pF    | See Figure 5-3                                       |  |  |

| Digital Input/Output             |                                    |                     |          |                       |       |                                                      |  |  |

| Data Coding Format               |                                    | Binary              | Two's Co | mplement              |       |                                                      |  |  |

| High Level Input Voltage         | V <sub>IH</sub>                    | 0.7 V <sub>DD</sub> |          | _                     | V     |                                                      |  |  |

| Low Level Input Voltage          | $V_{IL}$                           |                     |          | 0.3 V <sub>DD</sub>   | V     |                                                      |  |  |

| High Level Output Voltage        | V <sub>OH</sub>                    | 4.1                 |          | _                     | V     | $I_{OH} = -1 \text{ mA}, V_{DD} = 4.5 \text{V}$      |  |  |

| Low Level Output Voltage         | V <sub>OL</sub>                    |                     |          | 0.4                   | V     | I <sub>OL</sub> = 1 mA, V <sub>DD</sub> = 4.5V       |  |  |

| Input Leakage Current            | I <sub>LI</sub>                    | -10                 |          | 10                    | μA    | $V_{IN} = V_{SS}$ or $V_{DD}$                        |  |  |

| Output Leakage Current           | I <sub>LO</sub>                    | -10                 | 1        | 10                    | μA    | $V_{OUT} = V_{SS}$ or $V_{DD}$                       |  |  |

| Pin Capacitance                  | C <sub>IN</sub> , C <sub>OUT</sub> | _                   |          | 10                    | pF    | $T_A = +25$ °C, F = 1 MHz, <b>Note 1</b>             |  |  |

| Timing Specifications:           |                                    |                     |          |                       |       |                                                      |  |  |

| Clock Frequency (Note 8)         | F <sub>CLK</sub>                   | 0.105               | 1        | 2.1                   | MHz   | V <sub>DD</sub> = 5V, F <sub>SAMPLE</sub> = 100 ksps |  |  |

| Clock High Time                  | T <sub>HI</sub>                    | 210                 |          | _                     | ns    | Note 5                                               |  |  |

| Clock Low Time                   | T <sub>LO</sub>                    | 210                 |          | _                     | ns    | Note 5                                               |  |  |

| CS Fall To First Rising CLK Edge | T <sub>SUCS</sub>                  | 100                 | _        | _                     | ns    |                                                      |  |  |

| Data In Setup time               | T <sub>SU</sub>                    | 50                  | _        | _                     | ns    |                                                      |  |  |

| Data In Hold Time                | T <sub>HD</sub>                    | 50                  | _        | _                     | ns    |                                                      |  |  |

| CLK Fall To Output Data Valid    | $T_DO$                             | _                   | _        | 125                   | ns    | V <sub>DD</sub> = 5V, see Figure 1-2                 |  |  |

|                                  |                                    | _                   | _        | 200                   | ns    | V <sub>DD</sub> = 2.7V, see Figure 1-2               |  |  |

| CLK Fall To Output Enable        | T <sub>EN</sub>                    |                     | _        | 125                   | ns    | V <sub>DD</sub> = 5V, see Figure 1-2                 |  |  |

|                                  |                                    | _                   | _        | 200                   | ns    | V <sub>DD</sub> = 2.7V, see Figure 1-2               |  |  |

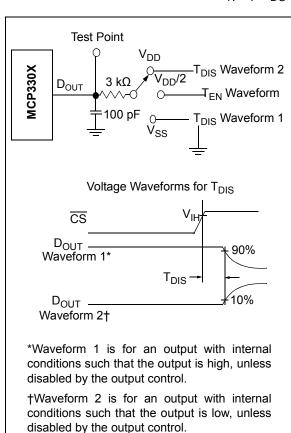

| CS Rise To Output Disable        | T <sub>DIS</sub>                   | _                   | _        | 100                   | ns    | See test circuits, Figure 1-2 Note 1                 |  |  |

| CS Disable Time                  | T <sub>CSH</sub>                   | 475                 |          | _                     | ns    |                                                      |  |  |

| D <sub>OUT</sub> Rise Time       | T <sub>R</sub>                     | _                   | _        | 100                   | ns    | See test circuits, Figure 1-2 Note 1                 |  |  |

| D <sub>OUT</sub> Fall Time       | T <sub>F</sub>                     | _                   | _        | 100                   | ns    | See test circuits, Figure 1-2 Note 1                 |  |  |

- Note 1: This specification is established by characterization and not 100% tested.

- 2: See characterization graphs that relate converter performance to  $V_{\mbox{\scriptsize REF}}$  level.

- 3:  $V_{IN} = 0.1V \text{ to } 4.9V @ 1 \text{ kHz}.$

- 4:  $V_{DD}$  =5V DC ±500 mV<sub>P-P</sub> @ 1 kHz, see test circuit Figure 1-4.

- 5: Maximum clock frequency specification must be met.

- **6:**  $V_{REF}$  = 400 mV,  $V_{IN}$  = 0.1V to 4.9V @ 1 kHz.

- 7: TSSOP devices are only specified at 25°C and +85°C.

- 8: For slow sample rates, see Section 5.2 "Driving the Analog Input" for limitations on clock frequency.

- **9:** 4.5V 5.5V is the supply voltage range for specified performance.

### **ELECTRICAL SPECIFICATIONS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise noted, all parameters apply at  $V_{DD}$  = 5V,  $V_{SS}$  = 0V, and  $V_{REF}$  = 5V. Full differential input configuration (Figure 1-5) with fixed common mode voltage of 2.5V. All parameters apply over temperature with  $T_A$  = -40°C to +85°C (**Note 7**). Conversion speed ( $F_{SAMPLE}$ ) is 100 ksps with  $F_{CLK}$  = 21\* $F_{SAMPLE}$

| Parameter           | Symbol           | Min | Тур  | Max | Units | Conditions                                                           |  |  |  |

|---------------------|------------------|-----|------|-----|-------|----------------------------------------------------------------------|--|--|--|

| Power Requirements: |                  |     |      |     |       |                                                                      |  |  |  |

| Operating Voltage   | $V_{DD}$         | 4.5 | _    | 5.5 | V     | Note 9                                                               |  |  |  |

| Operating Current   | I <sub>DD</sub>  |     | 300  | 450 | μA    | $V_{DD}$ , $V_{REF}$ = 5V, $D_{OUT}$ unloaded                        |  |  |  |

|                     |                  | _   | 200  | _   | μA    | V <sub>DD</sub> , V <sub>REF</sub> = 2.7V, D <sub>OUT</sub> unloaded |  |  |  |

| Standby Current     | I <sub>DDS</sub> | _   | 0.05 | 1   | μΑ    | $\overline{\text{CS}} = V_{\text{DD}} = 5.0V$                        |  |  |  |

- Note 1: This specification is established by characterization and not 100% tested.

- 2: See characterization graphs that relate converter performance to  $V_{\mbox{\scriptsize REF}}$  level.

- 3:  $V_{IN} = 0.1V$  to 4.9V @ 1 kHz.

- 4:  $V_{DD}$  =5V DC ±500 mV<sub>P-P</sub> @ 1 kHz, see test circuit Figure 1-4.

- 5: Maximum clock frequency specification must be met.

- **6:**  $V_{REF} = 400 \text{ mV}, V_{IN} = 0.1 \text{V to } 4.9 \text{V} @ 1 \text{ kHz}.$

- 7: TSSOP devices are only specified at 25°C and +85°C.

- 8: For slow sample rates, see Section 5.2 "Driving the Analog Input" for limitations on clock frequency.

- 9: 4.5V 5.5V is the supply voltage range for specified performance.

#### **TEMPERATURE CHARACTERISTICS**

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{DD}$ = +2.7V to +5.5V, $V_{SS}$ = GND. |                   |     |      |      |       |            |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|-------|------------|--|--|--|

| Parameters                                                                                               | Sym               | Min | Тур  | Max  | Units | Conditions |  |  |  |

| Temperature Ranges                                                                                       |                   |     |      |      |       |            |  |  |  |

| Specified Temperature Range                                                                              | T <sub>A</sub>    | -40 | _    | +125 | °C    |            |  |  |  |

| Operating Temperature Range                                                                              | T <sub>A</sub>    | -40 | _    | +125 | °C    |            |  |  |  |

| Storage Temperature Range                                                                                | T <sub>A</sub>    | -65 | _    | +150 | °C    |            |  |  |  |

| Thermal Package Resistances                                                                              |                   |     |      |      |       |            |  |  |  |

| Thermal Resistance, 14L-PDIP                                                                             | $\theta_{JA}$     | _   | 70   | _    | °C/W  |            |  |  |  |

| Thermal Resistance, 14L-SOIC                                                                             | $\theta_{\sf JA}$ | _   | 95.3 | _    | °C/W  |            |  |  |  |

| Thermal Resistance, 14L-TSSOP                                                                            | $\theta_{\sf JA}$ | _   | 100  | _    | °C/W  |            |  |  |  |

| Thermal Resistance, 16L-PDIP                                                                             | $\theta_{JA}$     | _   | 70   | _    | °C/W  |            |  |  |  |

| Thermal Resistance, 16L-SOIC                                                                             | $\theta_{\sf JA}$ | _   | 86.1 | _    | °C/W  |            |  |  |  |

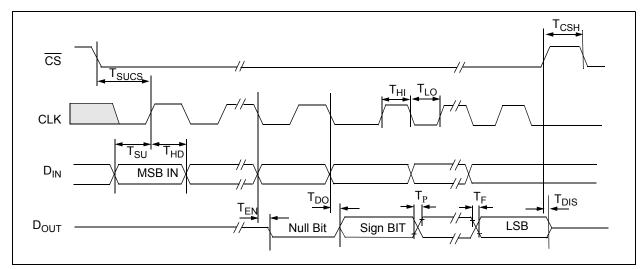

FIGURE 1-1: Timing Parameters.

#### 1.1 Test Circuits

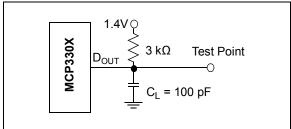

**FIGURE 1-2:** Load Circuit for  $T_B$ ,  $T_F$ ,  $T_{DO}$ .

**FIGURE 1-3:** Load circuit for  $T_{DIS}$  and  $T_{EN}$ .

**FIGURE 1-4:** Power Supply Sensitivity Test Circuit (PSRR).

**FIGURE 1-5:** Full Differential Test Configuration Example.

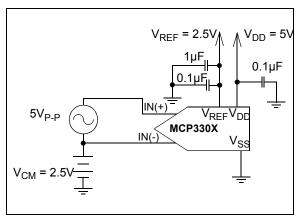

**FIGURE 1-6:** Pseudo Differential Test Configuration Example.

#### 2.0 TYPICAL PERFORMANCE CURVES

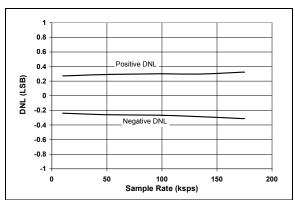

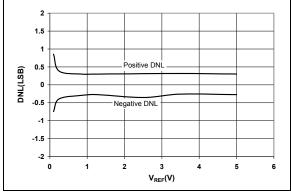

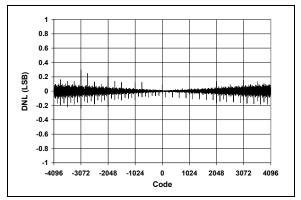

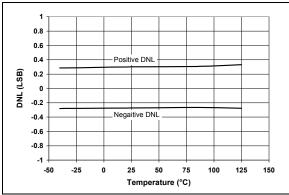

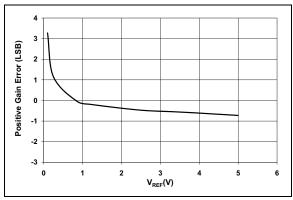

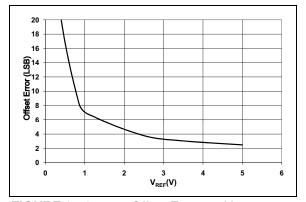

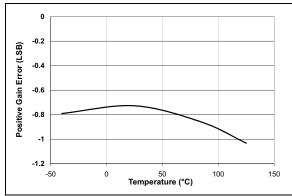

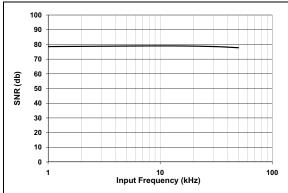

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25°C$ .

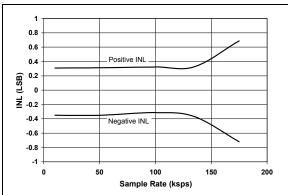

FIGURE 2-1: Integral Nonlinearity (INL) vs. Sample Rate.

**FIGURE 2-2:** Integral Nonlinearity (INL) vs. V<sub>RFF</sub>

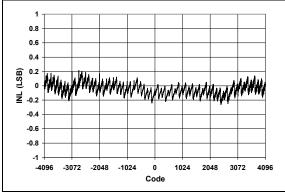

**FIGURE 2-3:** Integral Nonlinearity (INL) vs. Code (Representative Part).

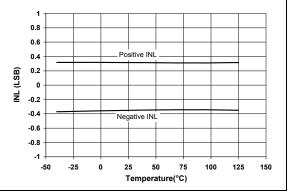

**FIGURE 2-4:** Integral Nonlinearity (INL) vs. Temperature.

FIGURE 2-5: Differential Nonlinearity (DNL) vs. Sample Rate.

**FIGURE 2-6:** Differential Nonlinearity (DNL) vs. V<sub>REF</sub>

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , Full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25°C$ .

FIGURE 2-7: Differential Nonlinearity (DNL) vs. Code (Representative Part).

**FIGURE 2-8:** Differential Nonlinearity (DNL) vs. Temperature.

FIGURE 2-9: Positive Gain Error vs. V<sub>REF</sub>

FIGURE 2-10: Offset Error vs. V<sub>REF</sub>

**FIGURE 2-11:** Positive Gain Error vs. Temperature.

FIGURE 2-12: Signal-to-Noise Ratio (SNR) vs. Input Frequency.

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , Full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25$ °C.

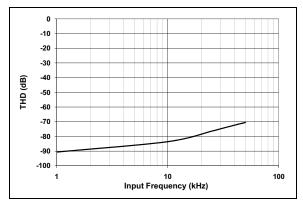

**FIGURE 2-13:** Total Harmonic Distortion (THD) vs. Input Frequency.

**FIGURE 2-14:** Offset Error vs. Temperature.

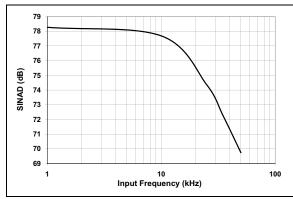

FIGURE 2-15: Signal-to-Noise and Distortion (SINAD) vs. Input Frequency.

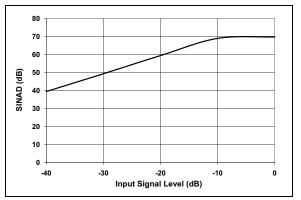

FIGURE 2-16: Signal-to-Noise and Distortion (SINAD) vs. Input Signal Level.

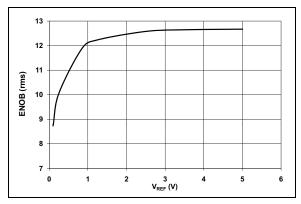

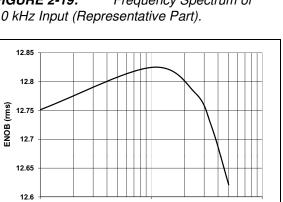

**FIGURE 2-17:** Effective Number of Bits (ENOB) vs.  $V_{REF}$ .

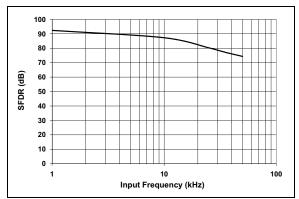

FIGURE 2-18: Spurious Free Dynamic Range (SFDR) vs. Input Frequency.

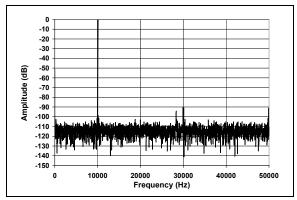

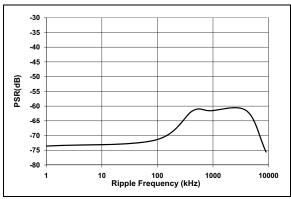

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , Full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25$ °C.

**FIGURE 2-19:** Frequency Spectrum of 10 kHz Input (Representative Part).

Input Frequency (kHz)

**FIGURE 2-20:** Effective Number of Bits (ENOB) vs. Input Frequency.

**FIGURE 2-21:** Power Supply Rejection (PSR) vs. Ripple Frequency. A 0.1 μF bypass capacitor is connected to the  $V_{DD}$  pin.

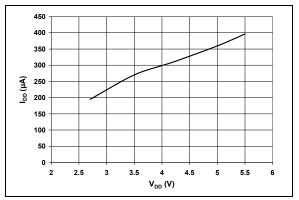

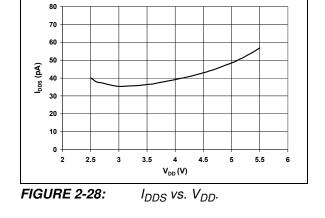

**FIGURE 2-22:** I<sub>DD</sub> vs. V<sub>DD</sub>.

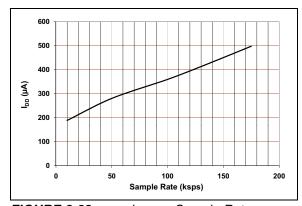

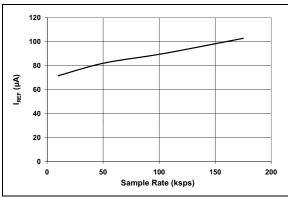

**FIGURE 2-23:** I<sub>DD</sub> vs. Sample Rate.

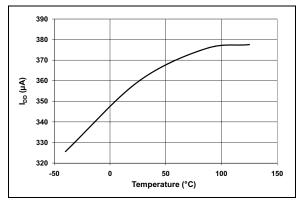

**FIGURE 2-24:** I<sub>DD</sub> vs. Temperature.

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , Full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25°C$ .

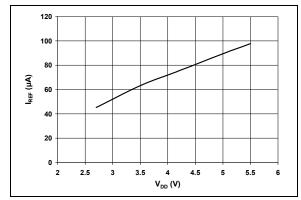

**FIGURE 2-25:**  $I_{REF}$  vs.  $V_{DD}$ .

FIGURE 2-26: I<sub>REF</sub> vs. Sample Rate.

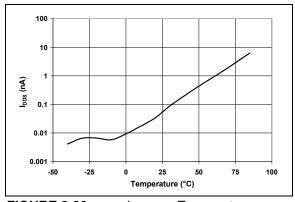

FIGURE 2-29: I<sub>DDS</sub> vs. Temperature.

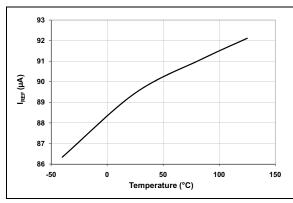

FIGURE 2-27: I<sub>REF</sub> vs. Temperature.

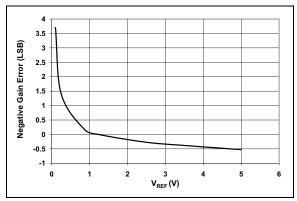

**FIGURE 2-30:** Negative Gain Error vs. Reference Voltage.

**Note:** Unless otherwise indicated,  $V_{DD} = V_{REF} = 5V$ , Full differential input configuration,  $V_{SS} = 0V$ ,  $F_{SAMPLE} = 100$  ksps,  $F_{CLK} = 21*F_{SAMPLE}$ ,  $T_A = +25°C$ .

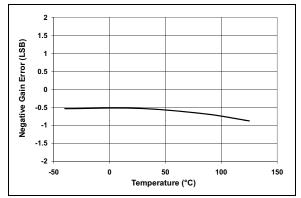

FIGURE 2-31: Temperature.

Negative Gain Error vs.

FIGURE 2-32: vs. Frequency.

Common Mode Rejection

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP3302           | MCP3304    | Symbol           | Description                  |

|-------------------|------------|------------------|------------------------------|

| PDIP, SOIC, TSSOP | PDIP, SOIC | Symbol           | Description                  |

| 1                 | 1          | CH0              | Analog Input                 |

| 2                 | 2          | CH1              | Analog Input                 |

| 3                 | 3          | CH2              | Analog Input                 |

| 4                 | 4          | CH3              | Analog Input                 |

| _                 | 5          | CH4              | Analog Input                 |

| _                 | 6          | CH5              | Analog Input                 |

| _                 | 7          | CH6              | Analog Input                 |

| _                 | 8          | CH7              | Analog Input                 |

| 7                 | 9          | DGND             | Digital Ground               |

| 8                 | 10         | CS/SHDN          | Chip Select / Shutdown Input |

| 9                 | 11         | D <sub>IN</sub>  | Serial Data In               |

| 10                | 12         | D <sub>OUT</sub> | Serial Data Out              |

| 11                | 13         | CLK              | Serial Clock                 |

| 12                | 14         | AGND             | Analog Ground                |

| 13                | 15         | $V_{REF}$        | Reference Voltage Input      |

| 14                | 16         | V <sub>DD</sub>  | +4.5V to 5.5V Power Supply   |

| 5, 6              | _          | NC               | No Connection                |

#### 3.1 Analog Inputs (CH0-CH7)

Analog input channels. These pins have an absolute voltage range of  $V_{SS}$  - 0.3V to  $V_{DD} + \, 0.3V$ . The full scale differential input range is defined as the absolute value of (IN+) - (IN-). This difference can not exceed the value of  $V_{REF}$  - 1 LSB or digital code saturation will occur.

#### 3.2 Digital Ground (DGND)

Ground connection to internal digital circuitry. To ensure accuracy this pin must be connected to the same ground as AGND. If an analog ground plane is available, it is recommended that this device be tied to the analog ground plane in the circuit. See **Section 5.6** "Layout Considerations" for more information regarding circuit layout.

### 3.3 Chip Select/Shutdown (CS/SHDN)

The  $\overline{\text{CS}}/\text{SHDN}$  pin is used to initiate communication with the device when pulled low. This pin will end a conversion and put the device in low-power standby when pulled high. The  $\overline{\text{CS}}/\text{SHDN}$  pin must be pulled high between conversions and cannot be tied low for multiple conversions. See Figure 6-2 for serial communication protocol.

#### 3.4 Serial Data Input (D<sub>IN</sub>)

The SPI port serial data input pin is used to clock in input channel configuration data. Data is latched on the rising edge of the clock. See Figure 6-2 for serial communication protocol.

#### 3.5 Serial Data Output (D<sub>OUT</sub>)

The SPI serial data output pin is used to shift out the results of the A/D conversion. Data will always change on the falling edge of each clock as the conversion takes place. See Figure 6-2 for serial communication protocol.

#### 3.6 Serial Clock (CLK)

The SPI clock pin is used to initiate a conversion, as well as to clock out each bit of the conversion as it takes place. See **Section 5.2 "Driving the Analog Input"** for constraints on clock speed, and Figure 6-2 for serial communication protocol.

#### 3.7 Analog Ground (AGND)

Ground connection to internal analog circuitry. To ensure accuracy, this pin must be connected to the same ground as DGND. If an analog ground plane is available, it is recommended that this device be tied to the analog ground plane in the circuit. See Section 5.6 "Layout Considerations" for more information regarding circuit layout.

### 3.8 Voltage Reference (V<sub>REF</sub>)

This input pin provides the reference voltage for the device, which determines the maximum range of the analog input signal and the LSB size.

The LSB size is determined according to the equation shown below. As the reference input is reduced, the LSB size is reduced accordingly.

#### **EQUATION 3-1:**

$$LSB \ Size = \frac{2 \ x \ V_{REF}}{8192}$$

When using an external voltage reference device, the system designer should always refer to the manufacturer's recommendations for circuit layout. Any instability in the operation of the reference device will have a direct effect on the accuracy of the ADC conversion results.

### 3.9 Power Supply (V<sub>DD</sub>)

The device can operate from 2.7V to 5.5V, but the data conversion performance is from 4.5V to 5.5V supply range. To ensure accuracy, a 0.1  $\mu F$  ceramic bypass capacitor should be placed as close as possible to the pin. See **Section 5.6 "Layout Considerations"** for more information regarding circuit layout.

#### 4.0 DEFINITION OF TERMS

**Bipolar Operation -** This applies to either a differential or single-ended input configuration, where both positive and negative codes are output from the A/D converter. Full bipolar range includes all 8192 codes. For bipolar operation on a single-ended input signal, the A/D converter must be configured to operate in pseudo differential mode.

**Unipolar Operation -** This applies to either a singleended or differential input signal where only one side of the device transfer is being used. This could be either the positive or negative side, depending on which input (IN+ or IN-) is being used for the DC bias. Full unipolar operation is equivalent to a 12-bit converter.

**Full Differential Operation** - Applying a full differential signal to both the IN(+) and IN(-) inputs is referred to as *full differential operation*. This configuration is described in Figure 1-5.

**Pseudo-Differential Operation** - Applying a single-ended signal to only one of the input channels with a bipolar output is referred to as *pseudo differential operation*. To obtain a bipolar output from a single-ended input signal the inverting input of the A/D converter must be biased above V<sub>SS</sub>. This operation is described in Figure 1-6.

**Integral Nonlinearity -** The maximum deviation from a straight line passing through the endpoints of the bipolar transfer function is defined as the maximum *integral nonlinearity* error. The endpoints of the transfer function are a point 1/2 LSB above the first code transition (0x1000) and 1/2 LSB below the last code transition (0x0FFF).

**Differential Nonlinearity** - The difference between two measured adjacent code transitions and the 1 LSB ideal is defined as *differential nonlinearity*.

**Positive Gain Error -** This is the deviation between the last positive code transition (0x0FFF) and the ideal voltage level of  $V_{REF}$ -1/2 LSB, after the bipolar offset error has been adjusted out.

**Negative Gain Error -** This is the deviation between the last negative code transition (0X1000) and the ideal voltage level of - $V_{REF}$ -1/2 LSB, after the bipolar offset error has been adjusted out.

**Offset Error -** This is the deviation between the first positive code transition (0x0001) and the ideal 1/2 LSB voltage level.

**Acquisition Time** - The *acquisition time* is defined as the time during which the internal sample capacitor is charging. This occurs for 1.5 clock cycles of the external CLK as defined in Figure 6-2.

**Conversion Time -** The *conversion time* occurs immediately after the *acquisition time*. During this time, successive approximation of the input signal occurs as the 13-bit result is being calculated by the internal circuitry. This occurs for 13 clock cycles of the external CLK as defined in Figure 6-2.

Signal-to-Noise Ratio - Signal-to-Noise Ratio (SNR) is defined as the ratio of the signal-to-noise measured at the output of the converter. The signal is defined as the rms amplitude of the fundamental frequency of the input signal. The noise value is dependant on the device noise as well as the quantization error of the converter and is directly affected by the number of bits in the converter. The theoretical signal-to-noise ratio limit based on quantization error only for an N-bit converter is defined as:

#### **EQUATION 4-1:**

$$SNR = (6.02N + 1.76)dB$$

For a 13-bit converter, the theoretical SNR limit is 80.02 dB.

**Total Harmonic Distortion -** *Total Harmonic Distortion* (*THD*) is the ratio of the rms sum of the harmonics to the fundamental, measured at the output of the converter. For the MCP3302/04, it is defined using the first 9 harmonics, as is shown in the following equation:

#### **EQUATION 4-2:**

$$THD(-dB) = -20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_8^2 + V_9^2}}{V_1^2}$$

Here  $V_1$  is the rms amplitude of the fundamental and  $V_2$  through  $V_9$  are the rms amplitudes of the second through ninth harmonics.

Signal-to-Noise plus Distortion (SINAD) - Numerically defined, SINAD is the calculated combination of SNR and THD. This number represents the dynamic performance of the converter, including any harmonic distortion.

#### **EQUATION 4-3:**

$$SINAD(dB) = 20 \log \sqrt{10^{(SNR/10)} + 10^{-(THD/10)}}$$

**Effective Number of Bits** - *Effective Number of Bits* (*ENOB*) states the relative performance of the ADC in terms of its resolution. This term is directly related to SINAD by the following equation:

#### **EQUATION 4-4:**

$$ENOB(N) = \frac{SINAD - 1.76}{6.02}$$

For SINAD performance of 78 dB, the effective number of bits is 12.66.

**Spurious Free Dynamic Range -** *Spurious Free Dynamic Range (SFDR)* is the ratio of the rms value of the fundamental to the next largest component in the output spectrum of the ADC. This is, typically, the first harmonic, but could also be a noise peak.

NOTES:

#### 5.0 APPLICATIONS INFORMATION

#### 5.1 Conversion Description

The MCP3302/04 A/D converter employ a conventional SAR architecture. With this architecture, the potential between the IN+ and IN- inputs are simultaneously sampled and stored with the internal sample circuits for 1.5 clock cycles (t<sub>ACQ</sub>). Following this sampling time, the input hold switches of the converter open and the device uses the collected charge to produce a serial 13-bit binary two's complement output code. This conversion process is driven by the external clock and must include 13 clock cycles, one for each bit. During this process, the most significant bit (MSB) is output first. This bit is the sign bit and indicates whether the IN+ input or the IN- input is at a higher potential.

FIGURE 5-1: Simplified Block Diagram.

#### 5.2 Driving the Analog Input

The analog input of the MCP3302/04 is easily driven, either differentially or single ended. Any signal that is common to the two input channels will be rejected by the common mode rejection of the device. During the charging time of the sample capacitor, a small charging current will be required. For low-source impedances, this input can be driven directly. For larger source impedances, a larger acquisition time will be required, due to the RC time constant that includes the source impedance. For the A/D Converter to meet specification, the charge holding capacitor (C<sub>SAMPLE</sub>) must be given enough time to acquire a 13-bit accurate voltage level during the 1.5 clock cycle acquisition period.

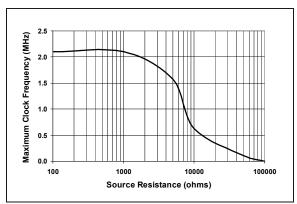

An analog input model is shown in Figure 5-3. This model is accurate for an analog input, regardless of whether it is configured as a single-ended input, or the IN+ and IN- input in differential mode. In this diagram, it is shown that the source impedance ( $R_{\rm S}$ ) adds to the internal sampling switch ( $R_{\rm SS}$ ) impedance, directly affecting the time that is required to charge the capacitor ( $C_{\rm SAMPLE}$ ). Consequently, a larger source impedance with no additional acquisition time increases the offset, gain, and integral linearity errors of the conversion. To overcome this, a slower clock speed can be used to allow for the longer charging time. Figure 5-2 shows the maximum clock speed associated with source impedances.

**FIGURE 5-2:** Maximum Clock Frequency vs. Source Resistance  $(R_S)$  to maintain  $\pm 1$  LSB INL.

FIGURE 5-3: Analog Input Model.

### 5.2.1 MAINTAINING MINIMUM CLOCK SPEED

When the MCP3302/04 initiates, charge is stored on the sample capacitor. When the sample period is complete, the device converts one bit for each clock that is received. It is important for the user to note that a slow clock rate will allow charge to bleed off the sample capacitor while the conversion is taking place. For the MCP330X devices, the recommended minimum clock speed during the conversion cycle ( $T_{\rm CONV}$ ) is 105 kHz. Failure to meet this criteria may induce linearity errors into the conversion outside the rated specifications. It should be noted that during the entire conversion cycle, the A/D converter does not have requirements for clock speed or duty cycle, as long as all timing specifications are met.

#### 5.3 Biasing Solutions

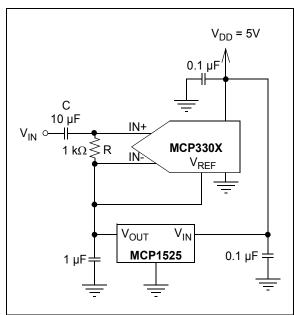

For pseudo-differential bipolar operation, the biasing circuit shown in Figure 5-4 shows a single-ended input AC coupled to the converter. This configuration will give a digital output range of -4096 to +4095. With the 2.5V reference, the LSB size equal to 610  $\mu V.$

Although the ADC is not production tested with a 2.5V reference as shown, linearity will not change more than 0.1 LSB. See Figure 2-2 and Figure 2-6 for INL and DNL errors versus  $V_{REF}$  at  $V_{DD}$  = 5V. A trade-off exists between the high-pass corner and the acquisition time. The value of C will need to be quite large in order to bring down the high-pass corner. The value of R needs to be 1 k $\Omega$ , or less, since higher input impedances require additional acquisition time.

Using the values in Figure 5-4, we have a 100 Hz corner frequency. See Figure 5-2 for relation between input impedance and acquisition time.

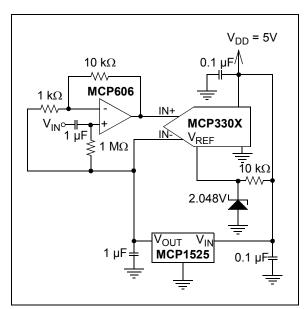

FIGURE 5-4: Pseudo-differential biasing circuit for bipolar operation.

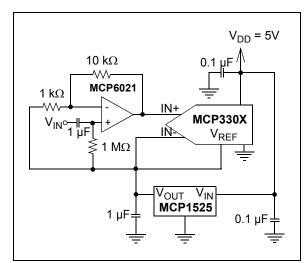

Using an external operation amplifier on the input allows for gain and also buffers the input signal from the input to the ADC allowing for a higher source impedance. This circuit is shown in Figure 5-5.

**FIGURE 5-5:** Adding an amplifier allows for gain and also buffers the input from any high-impedance sources.

This circuit shows that some headroom will be lost due to the amplifier output not being able to swing all the way to the rail. An example would be for an output swing of 0V to 5V. This limitation can be overcome by supplying a  $V_{REF}$  that is slightly less than the common mode voltage. Using a 2.048V reference for the A/D converter while biasing the input signal at 2.5V solves the problem. This circuit is shown in Figure 5-6.

**FIGURE 5-6:** Circuit solution to overcome amplifier output swing limitation.

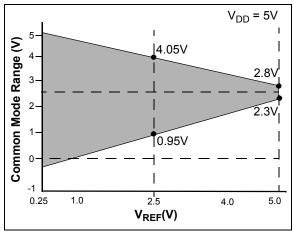

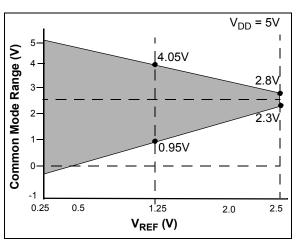

#### 5.4 Common Mode Input Range

The common mode input range has no restriction and is equal to the absolute input voltage range:  $V_{SS}$ -0.3V to  $V_{DD}$  + 0.3V. However, for a given  $V_{REF}$ , the common mode voltage has a limited swing, if the entire range of the A/D converter is to be used. Figure 5-7 and Figure 5-8 show the relationship between  $V_{REF}$  and the common mode voltage swing. A smaller  $V_{REF}$  allows for wider flexibility in a common mode voltage.  $V_{REF}$  levels, down to 400 mV, exhibit less than 0.1 LSB change in INL and DNL.

For characterization graphs that show this performance relationship, see Figure 2-2 and Figure 2-6.

**FIGURE 5-7:** Common Mode Input Range of Full Differential Input Signal versus V<sub>REF</sub>

**FIGURE 5-8:** Common Mode Input Range versus V<sub>REF</sub> for Pseudo Differential Input.

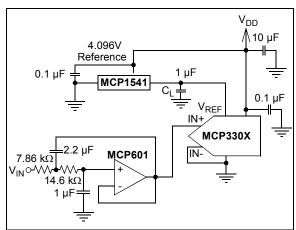

# 5.5 Buffering/Filtering the Analog Inputs

Inaccurate conversion results may occur if the signal source for the A/D converter is not a low-impedance source. Buffering the input will overcome the impedance issue. It is also recommended that an analog filter be used to eliminate any signals that may be aliased back into the conversion results. This is illustrated in Figure 5-9, where an op amp is used to drive the analog input of the MCP3302/04. This amplifier provides a low-impedance source for the converter input and a low-pass filter, which eliminates unwanted high-frequency noise. Values shown are for a 10 Hz Butterworth Low-Pass filter.

Low-pass (anti-aliasing) filters can be designed using Microchip's interactive FilterLab<sup>®</sup> software. FilterLab will calculate capacitor and resistor values, as well as determine the number of poles that are required for the application. For more detailed information on filtering signals, see *AN699 "Anti-Aliasing, Analog Filters for Data Acquisition Systems"*, at www.microchip.com.

FIGURE 5-9: The MCP601 Operational Amplifier is used to implement a 2nd order antialiasing filter for the signal being converted by the MCP3302/04.

#### 5.6 Layout Considerations

When laying out a printed circuit board for use with analog components, care should be taken to reduce noise wherever possible. A bypass capacitor from  $V_{DD}$  to ground should always be used with this device and should be placed as close as possible to the device pin. A bypass capacitor value of 0.1  $\mu F$  is recommended.

Digital and analog traces on the board should be separated as much as possible, with no traces running underneath the device or the bypass capacitor. Extra precautions should be taken to keep traces with high-frequency signals (such as clock lines) as far as possible from analog traces.

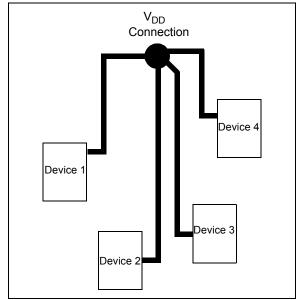

Use of an analog ground plane is recommended in order to keep the ground potential the same for all devices on the board. Providing V<sub>DD</sub> connections to devices in a "star" configuration can also reduce noise by eliminating current return paths and associated errors (see Figure 5-10). Layout tips for using the MCP3302, MCP3304, or other ADC devices, are available in AN688, "Layout Tips for 12-Bit A/D Converter Applications", from www.microchip.com.

FIGURE 5-10: V<sub>DD</sub> traces arranged in a 'Star' configuration in order to reduce errors caused by current return paths.

## 5.7 Utilizing the Digital and Analog Ground Pins

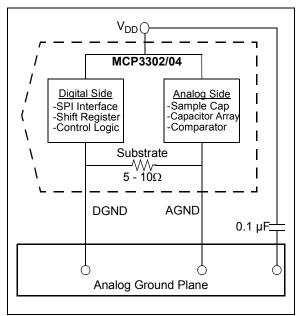

The MCP3302/04 devices provide both digital and analog ground connections to provide another means of noise reduction. As shown in Figure 5-11, the analog and digital circuitry are separated internal to the device. This reduces noise from the digital portion of the device being coupled into the analog portion of the device. The two grounds are connected internally through the substrate which has a resistance of  $5-10\Omega$ .

If no ground plane is utilized, then both grounds must be connected to  $V_{SS}$  on the board. If a ground plane is available, both digital and analog ground pins should be connected to the analog ground plane. If both an analog and a digital ground plane are available, both the digital and the analog ground pins should be connected to the analog ground plane, as shown in Figure 5-11. Following these steps will reduce the amount of digital noise from the rest of the board being coupled into the A/D Converter.

**FIGURE 5-11:** Separation of Analog and Digital Ground Pins.MCP3302/04.

NOTES:

#### 6.0 SERIAL COMMUNICATIONS

#### 6.1 Output Code Format

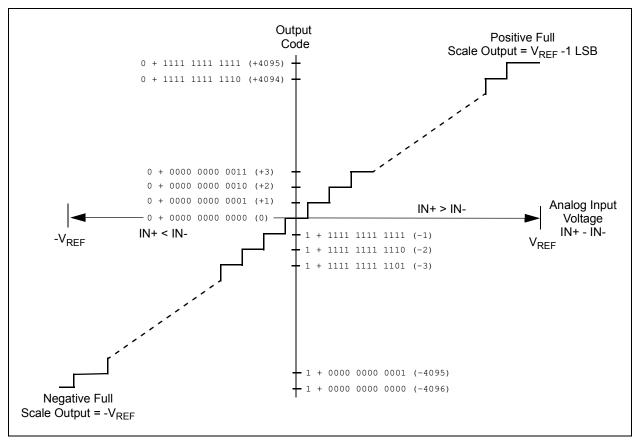

The output code format is a binary two's complement scheme, with a leading sign bit that indicates the sign of the output. If the IN+ input is higher than the IN-input, the sign bit will be a zero. If the IN- input is higher, the sign bit will be a '1'.

The diagram shown in Figure 6-1 shows the output code transfer function. In this diagram, the horizontal axis is the analog input voltage and the vertical axis is the output code of the ADC. It shows that when IN+ is equal to IN-, both the sign bit and the data word is zero. As IN+ gets larger with respect to IN-, the sign bit is a zero and the data word gets larger. The full scale output code is reached at +4095 when the input [(IN+) - (IN-)] reaches  $V_{REF}$  - 1 LSB. When IN- is larger than IN+, the two's complement output codes will be seen with the sign bit being a one. Some examples of analog input levels and corresponding output codes are shown in Table 6-1.

TABLE 6-1: BINARY TWO'S COMPLEMENT OUTPUT CODE EXAMPLES.

|                     | Analog Input Levels                                          | Sign<br>Bit | Binary Data    | Decimal DATA |

|---------------------|--------------------------------------------------------------|-------------|----------------|--------------|

| Full Scale Positive | (IN+)-(IN-)=V <sub>REF</sub> -1 LSB                          | 0           | 1111 1111 1111 | +4095        |

|                     | (IN+)-(IN-) = V <sub>REF</sub> -2 LSB                        | 0           | 1111 1111 1110 | +4094        |

|                     | IN+ = (IN-) +2 LSB                                           | 0           | 0000 0000 0010 | +2           |

|                     | IN+ = (IN-) +1 LSB                                           | 0           | 0000 0000 0001 | +1           |

|                     | IN+ = IN-                                                    | 0           | 0000 0000 0000 | 0            |

|                     | IN+ = (IN-) - 1 LSB                                          | 1           | 1111 1111 1111 | -1           |

|                     | IN+ = (IN-) - 2 LSB                                          | 1           | 1111 1111 1110 | -2           |

|                     | IN <sup>+</sup> - IN <sup>-</sup> = -V <sub>REF</sub> +1 LSB | 1           | 0000 0000 0001 | -4095        |

| Full Scale Negative | IN <sup>+</sup> - IN <sup>-</sup> = -V <sub>REF</sub>        | 1           | 0000 0000 0000 | -4096        |

FIGURE 6-1: Output Code Transfer Function.

# 6.2 Communicating with the MCP3302 and MCP3304

Communication with the MCP3302/04 devices is done using a standard SPI-compatible serial interface. Initiating communication with either device is done by bringing the  $\overline{\text{CS}}$  line low (see Figure 6-2). If the device was powered up with the CS pin low, it must be brought high and back low to initiate communication. The first clock received with  $\overline{\text{CS}}$  low and D<sub>IN</sub> high will constitute a start bit. The SGL/DIFF bit follows the start bit and will determine if the conversion will be done using singleended or differential input mode. Each channel in Single-ended mode will operate as a 12-bit converter with a unipolar output. No negative codes will be output in Single-ended mode. The next three bits (D0, D1, and D2) are used to select the input channel configuration. Table 6-1 and Table 6-2 show the configuration bits for the MCP3302 and MCP3304, respectively. The device will begin to sample the analog input on the fourth rising edge of the clock after the start bit has been received. The sample period will end on the falling edge of the fifth clock following the start bit.

After the D0 bit is input, one more clock is required to complete the sample and hold period ( $D_{IN}$  is a "don't care" for this clock). On the falling edge of the next clock, the device will output a low null bit. The next 13

clocks will output the result of the conversion with the sign bit first, followed by the 12 remaining data bits, as shown in Figure 6-2. Note that if the device is operating in the Single-ended mode, the sign bit will always be transmitted as a '0'. Data is always output from the device on the falling edge of the clock. If all 13 data bits have been transmitted, and the device continues to receive clocks while the  $\overline{\text{CS}}$  is held low, the device will output the conversion result, LSB, first, as shown in Figure 6-3. If more clocks are provided to the device while  $\overline{\text{CS}}$  is still low (after the LSB first data has been transmitted), the device will clock out zeros indefinitely.

If necessary, it is possible to bring CS low and clock in leading zeros on the  $D_{\text{IN}}$  line before the start bit. This is often done when dealing with microcontroller-based SPI ports that must send 8 bits at a time. Refer to Section 6.3 "Using the MCP3302/04 with Microcontroller (MCU) SPI Ports" for more details on using the MCP3302/04 devices with hardware SPI ports.

TABLE 6-1: CONFIGURATION BITS FOR THE MCP3302

| _                        | ontro<br>electi |    |    | Input         | Channel                |  |

|--------------------------|-----------------|----|----|---------------|------------------------|--|

| Si <u>ngl</u> e<br>/Diff | D2*             | D1 | D0 | Configuration | Selection              |  |

| 1                        | Х               | 0  | 0  | single ended  | CH0                    |  |

| 1                        | Х               | 0  | 1  | single ended  | CH1                    |  |

| 1                        | Х               | 1  | 0  | single ended  | CH2                    |  |

| 1                        | Х               | 1  | 1  | single ended  | CH3                    |  |

| 0                        | Х               | 0  | 0  | differential  | CH0 = IN+<br>CH1 = IN- |  |

| 0                        | Х               | 0  | 1  | differential  | CH0 = IN-<br>CH1 = IN+ |  |

| 0                        | Х               | 1  | 0  | differential  | CH2 = IN+<br>CH3 = IN- |  |

| 0                        | Х               | 1  | 1  | differential  | CH2 = IN-<br>CH3 = IN+ |  |

<sup>\*</sup>D2 is don't care for MCP3302

TABLE 6-2: CONFIGURATION BITS FOR THE MCP3304

|                          | ontrol |    |    | Input         | Channel                |

|--------------------------|--------|----|----|---------------|------------------------|

| Si <u>ngl</u> e<br>/Diff | D2     | D1 | D0 | Configuration | Selection              |

| 1                        | 0      | 0  | 0  | single ended  | CH0                    |

| 1                        | 0      | 0  | 1  | single ended  | CH1                    |

| 1                        | 0      | 1  | 0  | single ended  | CH2                    |

| 1                        | 0      | 1  | 1  | single ended  | CH3                    |

| 1                        | 1      | 0  | 0  | single ended  | CH4                    |

| 1                        | 1      | 0  | 1  | single ended  | CH5                    |

| 1                        | 1      | 1  | 0  | single ended  | CH6                    |

| 1                        | 1      | 1  | 1  | single ended  | CH7                    |

| 0                        | 0      | 0  | 0  | differential  | CH0 = IN+<br>CH1 = IN- |

| 0                        | 0      | 0  | 1  | differential  | CH0 = IN-<br>CH1 = IN+ |

| 0                        | 0      | 1  | 0  | differential  | CH2 = IN+<br>CH3 = IN- |

| 0                        | 0      | 1  | 1  | differential  | CH2 = IN-<br>CH3 = IN+ |

| 0                        | 1      | 0  | 0  | differential  | CH4 = IN+<br>CH5 = IN- |

| 0                        | 1      | 0  | 1  | differential  | CH4 = IN-<br>CH5 = IN+ |

| 0                        | 1      | 1  | 0  | differential  | CH6 = IN+<br>CH7 = IN- |

| 0                        | 1      | 1  | 1  | differential  | CH6 = IN-<br>CH7 = IN+ |