Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MCP3421

# 18-Bit Analog-to-Digital Converter with I<sup>2</sup>C Interface and On-Board Reference

#### **Features**

- 18-bit  $\Delta\Sigma$  ADC in a SOT-23-6 package

- · Differential Input Operation

- Self Calibration of Internal Offset and Gain Per Each Conversion

- · On-Board Voltage Reference:

- Accuracy: 2.048V ± 0.05%

- Drift: 15 ppm/°C

- On-Board Programmable Gain Amplifier (PGA):

- Gains of 1,2, 4 or 8

- · On-Board Oscillator

- INL: 10 ppm of FSR (FSR = 4.096V/PGA)

- · Programmable Data Rate Options:

- 3.75 SPS (18 bits)

- 15 SPS (16 bits)

- 60 SPS (14 bits)

- 240 SPS (12 bits)

- · One-Shot or Continuous Conversion Options

- · Low Current Consumption:

- 145 μA typical

(V<sub>DD</sub>= 3V, Continuous Conversion)

- 39 μA typical

- (V<sub>DD</sub>= 3V, One-Shot Conversion with 1 SPS)

- Supports I<sup>2</sup>C Serial Interface:

- Standard, Fast and High Speed Modes

- · Single Supply Operation: 2.7V to 5.5V

- Extended Temperature Range: -40°C to +125°C

#### **Typical Applications**

- · Portable Instrumentation

- · Weigh Scales and Fuel Gauges

- Temperature Sensing with RTD, Thermistor, and Thermocouple

- · Bridge Sensing for Pressure, Strain, and Force.

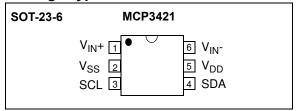

#### **Package Types**

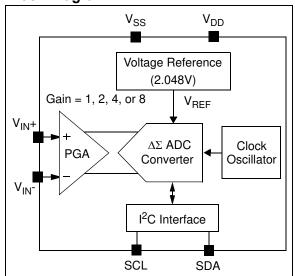

#### **Description**

The MCP3421 is a single channel low-noise, high accuracy  $\Delta\Sigma$  A/D converter with differential inputs and up to 18 bits of resolution in a small SOT-23-6 package. The on-board precision 2.048V reference voltage enables an input range of  $\pm 2.048V$  differentially ( $\Delta$  voltage = 4.096V). The device uses a two-wire I<sup>2</sup>C compatible serial interface and operates from a single 2.7V to 5.5V power supply.

The MCP3421 device performs conversion at rates of 3.75, 15, 60, or 240 samples per second (SPS) depending on the user controllable configuration bit settings using the two-wire I<sup>2</sup>C serial interface. This device has an on-board programmable gain amplifier (PGA). The user can select the PGA gain of x1, x2, x4, or x8 before the analog-to-digital conversion takes place. This allows the MCP3421 device to convert a smaller input signal with high resolution. The device has two conversion modes: (a) Continuous mode and (b) One-Shot mode. In One-Shot mode, the device enters a low current standby mode automatically after one conversion. This reduces current consumption greatly during idle periods.

The MCP3421 device can be used for various high accuracy analog-to-digital data conversion applications where design simplicity, low power, and small footprint are major considerations.

#### **Block Diagram**

# MCP3421

NOTES:

# 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Absolute Maximum Ratings†

| V <sub>DD</sub> 7.0V                                         |

|--------------------------------------------------------------|

| All inputs and outputs w.r.t $V_{SS}$ 0.3V to $V_{DD}$ +0.3V |

| Differential Input Voltage                                   |

| Output Short Circuit CurrentContinuous                       |

| Current at Input Pins±2 mA                                   |

| Current at Output and Supply Pins±10 mA                      |

| Storage Temperature65°C to +150°C                            |

| Ambient Temp. with power applied55°C to +125°C               |

| ESD protection on all pins $\geq 6$ kV HBM, $\geq 400 V$ MM  |

| Maximum Junction Temperature (T <sub>J</sub> )+150°C         |

**†Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 1.2 Electrical Specifications

### **ELECTRICAL CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{DD} = +5.0\text{V}$ ,  $V_{SS} = 0\text{V}$ ,  $V_{IN^+} = V_{IN^-} = V_{REF}/2$ . All ppm units use  $2^*V_{REF}$  as full scale range.

| v <sub>IN</sub> + = v <sub>IN</sub> - = v <sub>REF</sub> /2. All ppm units use 2 v <sub>REF</sub> as full scale range. |                      |                      |            |                      |                   |                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------------|----------------------|-------------------|------------------------------------------------------------------------|--|--|--|

| Parameters                                                                                                             | Sym                  | Min                  | Тур        | Max                  | Units             | Conditions                                                             |  |  |  |

| Analog Inputs                                                                                                          |                      |                      |            |                      |                   |                                                                        |  |  |  |

| Differential Input Range                                                                                               |                      | _                    | ±2.048/PGA | _                    | V                 | $V_{IN} = V_{IN} + - V_{IN}$                                           |  |  |  |

| Common-Mode Voltage Range (absolute) (Note 1)                                                                          |                      | V <sub>SS</sub> -0.3 | _          | V <sub>DD</sub> +0.3 | V                 |                                                                        |  |  |  |

| Differential Input Impedance (Note 2)                                                                                  | Z <sub>IND</sub> (f) | _                    | 2.25/PGA   | _                    | МΩ                | During normal mode operation                                           |  |  |  |

| Common Mode input Impedance                                                                                            | Z <sub>INC</sub> (f) | _                    | 25         | _                    | МΩ                | PGA = 1, 2, 4, 8                                                       |  |  |  |

| System Performance                                                                                                     |                      |                      |            |                      |                   |                                                                        |  |  |  |

| Resolution and No Missing                                                                                              |                      | 12                   | _          | _                    | Bits              | DR = 240 SPS                                                           |  |  |  |

| Codes (Note 8)                                                                                                         |                      | 14                   | _          | I                    | Bits              | DR = 60 SPS                                                            |  |  |  |

|                                                                                                                        |                      | 16                   | _          | l                    | Bits              | DR = 15 SPS                                                            |  |  |  |

|                                                                                                                        |                      | 18                   | _          | l                    | Bits              | DR = 3.75 SPS                                                          |  |  |  |

| Data Rate (Note 3)                                                                                                     | DR                   | 176                  | 240        | 328                  | SPS               | S1,S0 = '00', (12 bits mode)                                           |  |  |  |

|                                                                                                                        |                      | 44                   | 60         | 82                   | SPS               | S1,S0 = '01', (14 bits mode)                                           |  |  |  |

|                                                                                                                        |                      | 11                   | 15         | 20.5                 | SPS               | S1,S0 = '10', (16 bits mode)                                           |  |  |  |

|                                                                                                                        |                      | 2.75                 | 3.75       | 5.1                  | SPS               | S1,S0 = '11', (18 bits mode)                                           |  |  |  |

| Output Noise                                                                                                           |                      | _                    | 1.5        | _                    | μV <sub>RMS</sub> | T <sub>A</sub> = +25°C, DR = 3.75 SPS,<br>PGA = 1, V <sub>IN</sub> = 0 |  |  |  |

| Integral Nonlinearity (Note 4)                                                                                         | INL                  | _                    | 10         | 35                   | ppm of<br>FSR     | DR = 3.75 SPS<br>(Note 6)                                              |  |  |  |

| Internal Reference Voltage                                                                                             | $V_{REF}$            | _                    | 2.048      | _                    | V                 |                                                                        |  |  |  |

- Note 1: Any input voltage below or greater than this voltage causes leakage current through the ESD diodes at the input pins.

This parameter is ensured by characterization and not 100% tested.

- 2: This input impedance is due to 3.2 pF internal input sampling capacitor.

- 3: The total conversion speed includes auto-calibration of offset and gain.

- 4: INL is the difference between the endpoints line and the measured code at the center of the quantization band.

- 5: Includes all errors from on-board PGA and V<sub>REF</sub>.

- **6:** Full Scale Range (FSR) = 2 x 2.048/PGA = 4.096/PGA.

- 7: This parameter is ensured by characterization and not 100% tested.

- 8: This parameter is ensured by design and not 100% tested.

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40$ °C to +85°C,  $V_{DD} = +5.0$ V,  $V_{SS} = 0$ V,  $V_{IN^+} = V_{IN^-} = V_{REF}/2$ . All ppm units use  $2*V_{REF}$  as full scale range.

| $v_{\text{IN}}$ + = $v_{\text{IN}}$ - = $v_{\text{REF}}$ /2. All ppm un | its use Z VR      | EF as Iuli S        | cale rarige. | 1                  |        |                                                               |

|-------------------------------------------------------------------------|-------------------|---------------------|--------------|--------------------|--------|---------------------------------------------------------------|

| Parameters                                                              | Sym               | Min                 | Тур          | Max                | Units  | Conditions                                                    |

| Gain Error (Note 5)                                                     |                   | _                   | 0.05         | 0.35               | %      | PGA = 1, DR = 3.75 SPS                                        |

| PGA Gain Error Match (Note 5)                                           |                   | _                   | 0.1          | _                  | %      | Between any 2 PGA gains                                       |

| Gain Error Drift (Note 5)                                               |                   | _                   | 15           | _                  | ppm/°C | PGA=1, DR=3.75 SPS                                            |

| Offset Error                                                            | V <sub>OS</sub>   | _                   | 15           | 40                 | μV     | Tested at PGA = 1<br>V <sub>DD</sub> = 5.0V and DR = 3.75 SPS |

| Offset Drift vs. Temperature                                            |                   | _                   | 50           | _                  | nV/°C  | V <sub>DD</sub> = 5.0V                                        |

| Common-Mode Rejection                                                   |                   | _                   | 105          | _                  | dB     | at DC and PGA =1,                                             |

|                                                                         |                   | _                   | 110          | _                  | dB     | at DC and PGA =8,<br>T <sub>A</sub> = +25°C                   |

| Gain vs. V <sub>DD</sub>                                                |                   | _                   | 5            | _                  | ppm/V  | $T_A = +25$ °C, $V_{DD} = 2.7$ V to 5.5V, PGA = 1             |

| Power Supply Rejection at DC                                            |                   | _                   | 100          | _                  | dB     | $T_A = +25$ °C, $V_{DD} = 2.7$ V to 5.5V, PGA = 1             |

| Power Requirements                                                      |                   |                     |              |                    |        |                                                               |

| Voltage Range                                                           | $V_{DD}$          | 2.7                 | _            | 5.5                | V      |                                                               |

| Supply Current during                                                   | $I_{DDA}$         | _                   | 155          | 190                | μΑ     | V <sub>DD</sub> = 5.0V                                        |

| Conversion                                                              |                   | _                   | 145          | _                  | μΑ     | V <sub>DD</sub> = 3.0V                                        |

| Supply Current during Standby Mode                                      | $I_{DDS}$         | _                   | 0.1          | 0.5                | μΑ     |                                                               |

| I <sup>2</sup> C Digital Inputs and Digital O                           | utputs            |                     |              |                    |        |                                                               |

| High level input voltage                                                | V <sub>IH</sub>   | 0.7 V <sub>DD</sub> | _            | $V_{DD}$           | V      |                                                               |

| Low level input voltage                                                 | V <sub>IL</sub>   | _                   | _            | 0.3V <sub>DD</sub> | V      |                                                               |

| Low level output voltage                                                | V <sub>OL</sub>   | _                   | _            | 0.4                | ٧      | $I_{OL} = 3 \text{ mA}, V_{DD} = +5.0 \text{V}$               |

| Hysteresis of Schmitt Trigger for inputs (Note 7)                       | V <sub>HYST</sub> | 0.05V <sub>DD</sub> | _            | _                  | V      | f <sub>SCL</sub> = 100 kHz                                    |

| Supply Current when I <sup>2</sup> C bus line is active                 | I <sub>DDB</sub>  | _                   | _            | 10                 | μА     |                                                               |

| Input Leakage Current                                                   | I <sub>ILH</sub>  |                     | _            | 1                  | μΑ     | V <sub>IH</sub> = 5.5V                                        |

|                                                                         | I <sub>ILL</sub>  | -1                  |              | _                  | μΑ     | V <sub>IL</sub> = GND                                         |

| Pin Capacitance and I <sup>2</sup> C Bus C                              | apacitance        |                     |              |                    |        |                                                               |

| Pin capacitance                                                         | C <sub>PIN</sub>  |                     | _            | 10                 | pF     |                                                               |

| I <sup>2</sup> C Bus Capacitance                                        | C <sub>b</sub>    | _                   | _            | 400                | pF     |                                                               |

|                                                                         |                   |                     |              |                    |        |                                                               |

**Note 1:** Any input voltage below or greater than this voltage causes leakage current through the ESD diodes at the input pins. This parameter is ensured by characterization and not 100% tested.

- 2: This input impedance is due to 3.2 pF internal input sampling capacitor.

- 3: The total conversion speed includes auto-calibration of offset and gain.

- 4: INL is the difference between the endpoints line and the measured code at the center of the quantization band.

- 5: Includes all errors from on-board PGA and V<sub>REF</sub>.

- 6: Full Scale Range (FSR) = 2 x 2.048/PGA = 4.096/PGA.

- 7: This parameter is ensured by characterization and not 100% tested.

- 8: This parameter is ensured by design and not 100% tested.

### **TEMPERATURE SPECIFICATIONS**

| <b>Electrical Characteristics:</b> Unless otherwise indicated, $T_A = -40$ °C to $+85$ °C, $V_{DD} = +5.0$ V, $V_{SS} = 0$ V. |                |     |       |      |      |            |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-------|------|------|------------|--|

| Parameters Sym Min Typ Max Units Condition                                                                                    |                |     |       |      |      | Conditions |  |

| Temperature Ranges                                                                                                            |                |     |       |      |      |            |  |

| Specified Temperature Range                                                                                                   | T <sub>A</sub> | -40 | _     | +85  | °C   |            |  |

| Operating Temperature Range                                                                                                   | T <sub>A</sub> | -40 | _     | +125 | °C   |            |  |

| Storage Temperature Range                                                                                                     | T <sub>A</sub> | -65 | _     | +150 | °C   |            |  |

| Thermal Package Resistances                                                                                                   |                |     |       |      |      |            |  |

| Thermal Resistance, 6L SOT-23                                                                                                 | $\theta_{JA}$  | _   | 190.5 | _    | °C/W |            |  |

# MCP3421

NOTES:

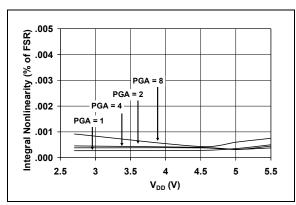

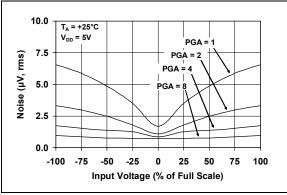

#### 2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

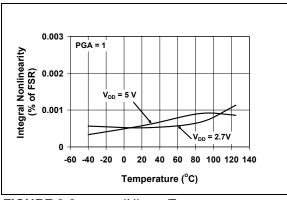

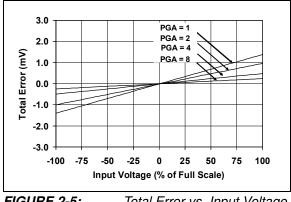

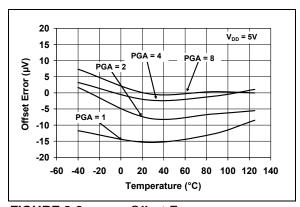

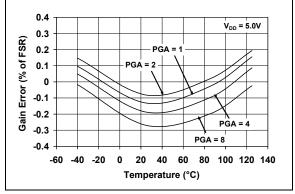

Note: Unless otherwise indicated,  $T_A = -40$ °C to +85°C,  $V_{DD} = +5.0$ V,  $V_{SS} = 0$ V,  $V_{IN} + = V_{IN} - = V_{REF}/2$ .

FIGURE 2-1: INL vs. Supply Voltage  $(V_{DD})$ .

FIGURE 2-4: Output Noise vs. Input Voltage.

FIGURE 2-2: INL vs. Temperature.

FIGURE 2-5: Total Error vs. Input Voltage.

FIGURE 2-3: Offset Error vs. Temperature.

FIGURE 2-6: Gain Error vs. Temperature.

**Note:** Unless otherwise indicated,  $T_A = -40$ °C to +85°C,  $V_{DD} = +5.0$ V,  $V_{SS} = 0$ V,  $V_{IN} + = V_{IN} - = V_{REF}/2$ .

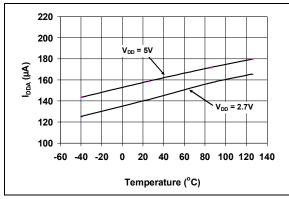

FIGURE 2-7: I<sub>DDA</sub> vs. Temperature.

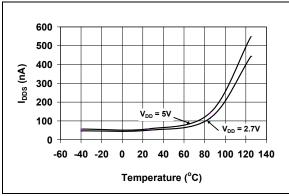

FIGURE 2-8: I<sub>DDS</sub> vs. Temperature.

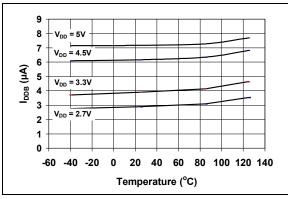

FIGURE 2-9: I<sub>DDB</sub> vs. Temperature.

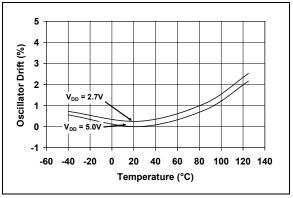

FIGURE 2-10: OSC Drift vs. Temperature.

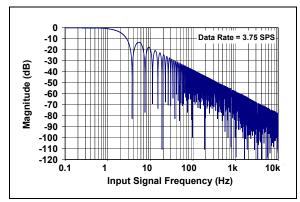

FIGURE 2-11: Frequency Response.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP3421 | Symbol            | Description                                                     |  |  |  |

|---------|-------------------|-----------------------------------------------------------------|--|--|--|

| 1       | V <sub>IN</sub> + | Positive Differential Analog Input Pin                          |  |  |  |

| 2       | $V_{SS}$          | Ground Pin                                                      |  |  |  |

| 3       | SCL               | Serial Clock Input Pin of the I <sup>2</sup> C Interface        |  |  |  |

| 4       | SDA               | Bidirectional Serial Data Pin of the I <sup>2</sup> C Interface |  |  |  |

| 5       | $V_{DD}$          | Positive Supply Voltage Pin                                     |  |  |  |

| 6       | V <sub>IN</sub> - | Negative Differential Analog Input Pin                          |  |  |  |

#### 3.1 Analog Inputs $(V_{IN}+, V_{IN}-)$

$V_{IN^+}$  and  $V_{IN^-}$  are differential signal input pins. The MCP3421 device accepts a fully differential analog input signal which is connected on the  $V_{IN^+}$  and  $V_{IN^-}$  input pins. The differential voltage that is converted is defined by  $V_{IN} = (V_{IN^+} - V_{IN^-})$  where  $V_{IN^+}$  is the voltage applied at the  $V_{IN^+}$  pin and  $V_{IN^-}$  is the voltage applied at the  $V_{IN^-}$  pin. The user can also connect  $V_{IN^-}$  pin to  $V_{SS}$  for a single-ended operation. See Figure 6-4 for differential and single-ended connection examples.

The input signal level is amplified by the programmable gain amplifier (PGA) before the conversion. The differential input voltage should not exceed an absolute of ( $V_{REF}/PGA$ ) for accurate measurement, where  $V_{REF}$  is the internal reference voltage (2.048V) and PGA is the PGA gain setting. The converter output code will saturate if the input range exceeds ( $V_{REF}/PGA$ ).

The absolute voltage range on each of the differential input pins is from V<sub>SS</sub>-0.3V to V<sub>DD</sub>+0.3V. Any voltage above or below this range will cause leakage currents through the Electrostatic Discharge (ESD) diodes at the input pins. This ESD current can cause unexpected performance of the device. The common mode of the analog inputs should be chosen such that both the differential analog input range and the absolute voltage range on each pin are within the specified operating Section 1.0 "Electrical range defined in Characteristics" and Section 4.0 "Description of Device Operation".

See **Section 4.5 "Input Voltage Range"** for more details of the input voltage range.

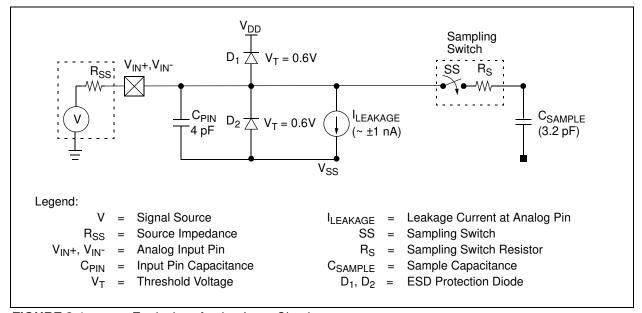

Figure 3-1 shows the input structure of the device. The device uses a switched capacitor input stage at the front end.  $C_{PIN}$  is the package pin capacitance and typically about 4 pF.  $D_1$  and  $D_2$  are the ESD diodes.  $C_{SAMPLE}$  is the differential input sampling capacitor.

#### 3.2 Supply Voltage $(V_{DD}, V_{SS})$

$V_{DD}$  is the power supply pin for the device. This pin requires an appropriate bypass capacitor of about 0.1  $\mu F$  (ceramic) to ground. An additional 10  $\mu F$  capacitor (tantalum) in parallel is also recommended to further attenuate high frequency noise present in some application boards. The supply voltage  $(V_{DD})$  must be maintained in the 2.7V to 5.5V range for specified operation.

$V_{SS}$  is the ground pin and the current return path of the device. The user must connect the  $V_{SS}$  pin to a ground plane through a low impedance connection. If an analog ground path is available in the application PCB (printed circuit board), it is highly recommended that the  $V_{SS}$  pin be tied to the analog ground path or isolated within an analog ground plane of the circuit board.

#### 3.3 Serial Clock Pin (SCL)

SCL is the serial clock pin of the  $I^2C$  interface. The MCP3421 acts only as a slave and the SCL pin accepts only external serial clocks. The input data from the Master device is shifted into the SDA pin on the rising edges of the SCL clock and output from the MCP3421 occurs at the falling edges of the SCL clock. The SCL pin is an open-drain N-channel driver. Therefore, it needs a pull-up resistor from the  $V_{\rm DD}$  line to the SCL pin. Refer to Section 5.3 " $I^2C$  Serial Communications" for more details of  $I^2C$  Serial Interface communication.

### 3.4 Serial Data Pin (SDA)

SDA is the serial data pin of the  $I^2C$  interface. The SDA pin is used for input and output data. In read mode, the conversion result is read from the SDA pin (output). In write mode, the device configuration bits are written (input) though the SDA pin. The SDA pin is an opendrain N-channel driver. Therefore, it needs a pull-up resistor from the  $V_{DD}$  line to the SDA pin. Except for start and stop conditions, the data on the SDA pin must be stable during the high period of the clock. The high or low state of the SDA pin can only change when the clock signal on the SCL pin is low. Refer to **Section 5.3** " $I^2C$  **Serial Communications**" for more details of  $I^2C$  Serial Interface communication.

Typical range of the pull-up resistor value for SCL and SDA is from 5 k $\Omega$  to 10 k $\Omega$  for standard (100 kHz) and fast (400 kHz) modes, and less than 1 k $\Omega$  for high speed mode (3.4 MHz). The High-Speed mode is not recommended for V<sub>DD</sub> less than 2.7V.

FIGURE 3-1: Equivalent Analog Input Circuit.

# 4.0 DESCRIPTION OF DEVICE OPERATION

#### 4.1 General Overview

The MCP3421 is a low-power, 18-Bit Delta-Sigma A/D converter with an I<sup>2</sup>C serial interface. The device contains an on-board voltage reference (2.048V), programmable gain amplifier (PGA), and internal oscillator. When the device powers up (POR is set), it automatically resets the configuration bits to default settings.

### Device default settings are:

- Conversion bit resolution: 12 bits (240 sps)

- PGA gain setting: x1

- · Continuous conversion

Once the device is powered-up, the user can reprogram the configuration bits using I<sup>2</sup>C serial interface any time. The configuration bits are stored in volatile memory.

#### User selectable options are:

- · Conversion bit resolution: 12, 14, 16, or 18 bits

- PGA Gain selection: x1, x2, x4, or x8

- · Continuous or one-shot conversion

In the Continuous Conversion mode, the device converts the inputs continuously. While in the One-Shot Conversion mode, the device converts the input one time and stays in the low-power standby mode until it receives another command for a new conversion. During the standby mode, the device consumes less than 1  $\mu A$  maximum.

#### 4.2 Power-On-Reset (POR)

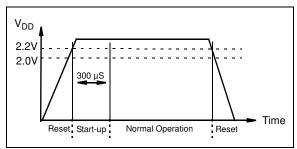

The device contains an internal Power-On-Reset (POR) circuit that monitors power supply voltage ( $V_{DD}$ ) during operation. This circuit ensures correct device start-up at system power-up and power-down events. The POR has built-in hysteresis and a timer to give a high degree of immunity to potential ripples and noises on the power supply. A 0.1  $\mu$ F decoupling capacitor should be mounted as close as possible to the  $V_{DD}$  pin for additional transient immunity.

The threshold voltage is set at 2.2V with a tolerance of approximately  $\pm 5\%$ . If the supply voltage falls below this threshold, the device will be held in a reset condition. The typical hysteresis value is approximately 200 mV.

The POR circuit is shut-down during the low-power standby mode. Once a power-up event has occurred, the device requires additional delay time (approximately 300 µs) before a conversion can take place. During this time, all internal analog circuitries are settled before the first conversion occurs. Figure 4-1 illustrates the conditions for power-up and power-down events under typical start-up conditions.

When the device powers up, it automatically resets and sets the configuration bits to default settings. The default configuration bit conditions are a PGA gain of 1 V/V and a conversion speed of 240 SPS in Continuous Conversion mode. When the device receives an I<sup>2</sup>C General Call Reset command, it performs an internal reset similar to a Power-On-Reset event.

FIGURE 4-1: POR Operation.

#### 4.3 Internal Voltage Reference

The device contains an on-board 2.048V voltage reference. This reference voltage is for internal use only and not directly measurable. The specifications of the reference voltage are part of the device's gain and drift specifications. Therefore, there is no separate specification for the on-board reference.

### 4.4 Analog Input Channel

The differential analog input channel has a switched capacitor structure. The internal sampling capacitor (3.2 pF for PGA = 1) is charged and discharged to process a conversion. The charging and discharging of the input sampling capacitor creates dynamic input currents at each input pin. The current is a function of the differential input voltages, and inversely proportional to the internal sampling capacitance, sampling frequency, and PGA setting.

#### 4.5 Input Voltage Range

The differential  $(V_{IN})$  and common mode voltage  $(V_{INCOM})$  at the input pins without considering PGA setting are defined by:

$$\begin{split} V_{IN} &= V_{IN} + -V_{IN} \\ V_{INCOM} &= \frac{V_{IN} + +V_{IN}}{2} \end{split}$$

The input signal levels are amplified by the internal programmable gain amplifier (PGA) at the front end of the  $\Delta\Sigma$  modulator.

The user needs to consider two conditions for the input voltage range: (a) Differential input voltage range and (b) Absolute maximum input voltage range.

## 4.5.1 DIFFERENTIAL INPUT VOLTAGE RANGE

The device performs conversions using its internal reference voltage ( $V_{REF} = 2.048V$ ). Therefore, the absolute value of the differential input voltage ( $V_{IN}$ ), with PGA setting is included, needs to be less than the internal reference voltage. The device will output saturated output codes (all 0s or all 1s except sign bit) if the absolute value of the input voltage ( $V_{IN}$ ), with PGA setting is included, is greater than the internal reference voltage ( $V_{REF} = 2.048V$ ). The input full-scale voltage range is given by:

#### **EQUATION 4-1:**

$$-V_{REF} \leq (V_{IN} \bullet PGA) \leq (V_{REF} - 1LSB)$$

Where:

$$V_{IN} = V_{IN} + V_{IN} - V_{REF} = 2.048V$$

If the input voltage level is greater than the above limit, the user can use a voltage divider and bring down the input level within the full-scale range. See Figure 6-7 for more details of the input voltage divider circuit.

# 4.5.2 ABSOLUTE MAXIMUM INPUT VOLTAGE RANGE

The input voltage at each input pin must be less than the following absolute maximum input voltage limits:

- Input voltage < V<sub>DD</sub>+0.3V

- Input voltage > V<sub>SS</sub>-0.3V

Any input voltage outside this range can turn on the input ESD protection diodes, and result in input leakage current, causing conversion errors, or permanently damage the device.

Care must be taken in setting the input voltage ranges so that the input voltage does not exceed the absolute maximum input voltage range.

#### 4.6 Input Impedance

The device uses a switched-capacitor input stage using a 3.2 pF sampling capacitor. This capacitor is switched (charged and discharged) at a rate of the sampling frequency that is generated by on-board clock. The differential input impedance varies with the PGA settings. The typical differential input impedance during a normal mode operation is given by:

$$Z_{IN}(f) = 2.25 M\Omega/PGA$$

Since the sampling capacitor is only switching to the input pins during a conversion process, the above input impedance is only valid during conversion periods. In a low power standby mode, the above impedance is not presented at the input pins. Therefore, only a leakage current due to ESD diode is presented at the input pins.

The conversion accuracy can be affected by the input signal source impedance when any external circuit is connected to the input pins. The source impedance adds to the internal impedance and directly affects the time required to charge the internal sampling capacitor. Therefore, a large input source impedance connected to the input pins can degrade the system performance, such as offset, gain, and Integral Non-Linearity (INL) errors. Ideally, the input source impedance should be zero. This can be achievable by using an operational amplifier with a closed-loop output impedance of tens of ohms.

### 4.7 Aliasing and Anti-aliasing Filter

Aliasing occurs when the input signal contains timevarying signal components with frequency greater than half the sample rate. In the aliasing conditions, the device can output unexpected output codes. For applications that are operating in electrical noise environments, the time-varying signal noise or high frequency interference components can be easily added to the input signals and cause aliasing. Although the device has an internal first order sinc filter, the filter response (Figure 2-11) may not give enough attenuation to all aliasing signal components. To avoid the aliasing, an external anti-aliasing filter, which can be accomplished with a simple RC low-pass filter, is typically used at the input pins. The low-pass filter cuts off the high frequency noise components and provides a band-limited input signal to the input pins.

#### 4.8 Self-Calibration

The device performs a self-calibration of offset and gain for each conversion. This provides reliable conversion results from conversion-to-conversion over variations in temperature as well as power supply fluctuations.

# 4.9 Digital Output Codes and Conversion to Real Values

## 4.9.1 DIGITAL OUTPUT CODE FROM DEVICE

The digital output code is proportional to the input voltage and PGA settings. The output data format is a binary two's complement. With this code scheme, the MSB can be considered a sign indicator. When the MSB is a logic '0', the input is positive. When the MSB is a logic '1', the input is negative. The following is an example of the output code:

- a. for a negative full scale input voltage: 100...000 Example:  $(V_{IN}+-V_{IN}-) \cdot PGA = -2.048V$

- b. for a zero differential input voltage: 000...000 Example:  $(V_{IN}+-V_{IN}-)=0$

- c. for a positive full scale input voltage: 011...111

Example:  $(V_{IN} + - V_{IN} -) \cdot PGA = 2.048V$

The MSB (sign bit) is always transmitted first through the  $I^2C$  serial data line. The resolution for each conversion is 18, 16, 14, or 12 bits depending on the conversion rate selection bit settings by the user.

The output codes will not roll-over even if the input voltage exceeds the maximum input range. In this case, the code will be locked at  $0111\ldots11$  for all voltages greater than (V<sub>REF</sub> - 1 LSB)/PGA and  $1000\ldots00$  for voltages less than -V<sub>REF</sub>/PGA. Table 4-2 shows an example of output codes of various input levels for 18 bit conversion mode. Table 4-3 shows an example of minimum and maximum output codes for each conversion rate option.

The number of output code is given by:

#### **EQUATION 4-2:**

Number of Output Code

$$= (Maximum\ Code + I) \times PGA \times \frac{(V_{IN} + -V_{IN} - )}{2.048V}$$

Where:

See Table 4-3 for Maximum Code.

The LSB of the data conversion is given by:

#### **EQUATION 4-3:**

$$LSB = \frac{2 \times V_{REF}}{2^N} = \frac{2 \times 2.048V}{2^N}$$

Where:

N = User programmable bit resolution: 12,14,16, or 18

Table 4-1 shows the LSB size of each conversion rate setting. The measured unknown input voltage is obtained by multiplying the output codes with LSB. See the following section for the input voltage calculation using the output codes.

TABLE 4-1: RESOLUTION SETTINGS VS.

| Resolution Setting | LSB       |

|--------------------|-----------|

| 12 bits            | 1 mV      |

| 14 bits            | 250 μV    |

| 16 bits            | 62.5 μV   |

| 18 bits            | 15.625 μV |

TABLE 4-2: EXAMPLE OF OUTPUT CODE FOR 18 BITS (NOTE 1,NOTE 2)

| Input Voltage:<br>[V <sub>IN</sub> + - V <sub>IN</sub> -] • PGA | Digital Output Code                     |

|-----------------------------------------------------------------|-----------------------------------------|

| ≥ V <sub>REF</sub>                                              | 011111111111111111                      |

| V <sub>REF</sub> - 1 LSB                                        | 011111111111111111                      |

| 2 LSB                                                           | 000000000000000000000000000000000000000 |

| 1 LSB                                                           | 0000000000000000001                     |

| 0                                                               | 000000000000000000                      |

| -1 LSB                                                          | 111111111111111111                      |

| -2 LSB                                                          | 11111111111111111                       |

| - V <sub>REF</sub>                                              | 1000000000000000000                     |

| < -V <sub>REF</sub>                                             | 1000000000000000000                     |

Note 1: MSB is a sign indicator:

0: Positive input (V<sub>IN</sub>+ > V<sub>IN</sub>-)

1: Negative input (V<sub>IN</sub>+ < V<sub>IN</sub>-)

**2:** Output data format is binary two's complement.

TABLE 4-3: MINIMUM AND MAXIMUM OUTPUT CODES (NOTE)

| Resolution<br>Setting | Data Rate | Minimum<br>Code | Maximum<br>Code |

|-----------------------|-----------|-----------------|-----------------|

| 12                    | 240 SPS   | -2048           | 2047            |

| 14                    | 60 SPS    | -8192           | 8191            |

| 16                    | 15 SPS    | -32768          | 32767           |

| 18                    | 3.75 SPS  | -131072         | 131071          |

Note: Maximum n-bit code =  $2^{N-1}$  - 1 Minimum n-bit code =  $-1 \times 2^{N-1}$

# 4.9.2 CONVERTING THE DEVICE OUTPUT CODE TO INPUT SIGNAL VOLTAGE

When the user gets the digital output codes from the device as described in **Section 4.9.1** "**Digital output code from device**", the next step is converting the digital output codes to a measured input voltage. Equation 4-4 shows an example of converting the output codes to its corresponding input voltage.

If the sign indicator bit (MSB) is `0', the input voltage is obtained by multiplying the output code with the LSB and divided by the PGA setting.

If the sign indicator bit (MSB) is '1', the output code needs to be converted to two's complement before multiplied by LSB and divided by the PGA setting. Table 4-4 shows an example of converting the device output codes to input voltage.

# EQUATION 4-4: CONVERTING OUTPUT CODES TO INPUT VOLTAGE

If MSB = 0 (Positive Output Code):

Input Voltage = (Output Code)  $\bullet \frac{LSB}{PGA}$

If MSB = 1 (Negative Output Code):

Input Voltage =  $(2 \text{ 's complement of Output Code}) \bullet \frac{LSB}{PGA}$

Where:

LSB = See Table 4-1

2's complement = 1's complement + 1

TABLE 4-4: EXAMPLE OF CONVERTING OUTPUT CODE TO VOLTAGE (WITH 18 BIT SETTING)

| Input Voltage<br>[V <sub>IN</sub> + - V <sub>IN</sub> -] • PGA] | Digital Output Code                     | MSB<br>(sign bit) | Example of Converting Output Codes to Input Voltage                                                                                                                |

|-----------------------------------------------------------------|-----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ≥ V <sub>REF</sub>                                              | 0111111111111111111                     | 0                 | $(2^{16}+2^{15}+2^{14}+2^{13}+2^{12}+2^{11}+2^{10}+2^{9}+2^{8}+2^{7}+2^{6}+2^{5}+2^{4}+2^{3}+2^{2}+2^{1}+2^{0})$ x LSB(15.625 $\mu$ V)/PGA = 2.048 (V) for PGA = 1 |

| V <sub>REF</sub> - 1 LSB                                        | 0111111111111111111                     | 0                 | $(2^{16}+2^{15}+2^{14}+2^{13}+2^{12}+2^{11}+2^{10}+2^{9}+2^{8}+2^{7}+2^{6}+2^{5}+2^{4}+2^{3}+2^{2}+2^{1}+2^{0})$ x LSB(15.625 $\mu$ V)/PGA = 2.048 (V) for PGA = 1 |

| 2 LSB                                                           | 000000000000000000000000000000000000000 | 0                 | $(0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+2^{1}+0) x$<br>LSB(15.625 $\mu$ V)/PGA = 31.25 ( $\mu$ V) for PGA = 1                                                              |

| 1 LSB                                                           | 0000000000000000001                     | 0                 | $(0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+2^0) x$<br>LSB(15.625 $\mu$ V)/PGA = 15.625 ( $\mu$ V) for PGA = 1                                                             |

| 0                                                               | 0000000000000000000                     | 0                 | (0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0) x<br>LSB(15.625 $\mu$ V)/PGA = 0 V (V) for PGA = 1                                                                           |

| -1 LSB                                                          | 1111111111111111111                     | 1                 | -(0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+                                                                                                                           |

| -2 LSB                                                          | 11111111111111111110                    | 1                 | $-(0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+2^{1}+0) x$<br>LSB(15.625 $\mu$ V)/PGA = - 31.25 ( $\mu$ V) for PGA = 1                                                           |

| - V <sub>REF</sub>                                              | 10000000000000000000                    | 1                 | $-(2^{17}+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0$                                                                                                                   |

| ≤ -V <sub>REF</sub>                                             | 100000000000000000000000000000000000000 | 1                 | $-(2^{17}+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0+0$                                                                                                                   |

#### 5.0 USING THE MCP3421 DEVICE

#### 5.1 Operating Modes

The user operates the device by setting up the device configuration register using a write command (see Figure 5-2) and reads the conversion data using a read command (see Figure 5-3 and Figure 5-4). The device operates in two modes: (a) Continuous Conversion Mode or (b) One-Shot Conversion Mode (single conversion). This mode selection is made by setting the  $\overline{\rm O}/{\rm C}$  bit in the Configuration Register. Refer to Section 5.2 "Configuration Register" for more information.

## 5.1.1 CONTINUOUS CONVERSION MODE $(\overline{O}/C \text{ BIT} = 1)$

The device performs a Continuous Conversion if the  $\overline{O}/C$  bit is set to logic "high". Once the conversion is completed,  $\overline{RDY}$  bit is toggled to '0' and the result is placed at the output data register. The device immediately begins another conversion and overwrites the output data register with the most recent result. The device clears the data ready flag ( $\overline{RDY}$  bit = 0) when the conversion is completed. The device sets the ready flag bit ( $\overline{RDY}$  bit = 1), if the latest conversion result has been read by the Master.

#### · When writing configuration register:

Setting RDY bit in continuous mode does not affect anything

#### · When reading conversion data:

- RDY bit = 0 means the latest conversion result is ready

- RDY bit = 1 means the conversion result is not updated since the last reading. A new conversion is under processing and the RDY bit will be cleared when the new conversion result is ready

# 5.1.2 ONE-SHOT CONVERSION MODE $(\overline{O}/C \text{ BIT} = 0)$

Once the One-Shot Conversion (single conversion) Mode is selected, the device performs only one conversion, updates the output data register, clears the data ready flag ( $\overline{RDY} = 0$ ), and then enters a low power standby mode. A new One-Shot Conversion is started again when the device receives a new write command with  $\overline{RDY} = 1$ .

#### · When writing configuration register:

- The RDY bit needs to be set to begin a new conversion in one-shot mode

#### · When reading conversion data:

- RDY bit = 0 means the latest conversion result is ready

- RDY bit = 1 means the conversion result is not updated since the last reading. A new conversion is under processing and the RDY bit will be cleared when the new conversion is done

This One-Shot Conversion Mode recommended for low power operating applications where the conversion result is needed by request on demand. During the low current standby mode, the device consumes less than 1 µA maximum (or 300 nA typical). For example, if the user collects 18 bit conversion data once a second in One-Shot Conversion mode, the device draws only about one fourth of its total operating current. In this example, the device consumes approximately 39 µA (145 µA / 3.75 SPS =  $39 \mu A$ ), if the device performs only one conversion per second (1 SPS) in 18-bit conversion mode with 3V power supply.

### 5.2 Configuration Register

The device has an 8-bit wide configuration register to select for: input channel, conversion mode, conversion rate, and PGA gain. This register allows the user to change the operating condition of the device and check the status of the device operation.

The user can rewrite the configuration byte any time during the device operation. Register 5-1 shows the configuration register bits.

#### REGISTER 5-1: CONFIGURATION REGISTER

| R/W-1 | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RDY   | C1    | C0    | O/C   | S1    | S0    | G1    | G0    |

| 1 *   | 0 *   | 0 *   | 1 *   | 0 *   | 0 *   | 0 *   | 0 *   |

| bit 7 |       |       |       |       |       |       | bit 0 |

<sup>\*</sup> Default Configuration after Power-On Reset

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7 RDY: Ready Bit

This bit is the data ready flag. In read mode, this bit indicates if the output register has been updated with a latest conversion result. In One-Shot Conversion mode, writing this bit to "1" initiates a new conversion.

#### Reading RDY bit with the read command:

- 1 = Output register has not been updated.

- 0 = Output register has been updated with the latest conversion result.

#### Writing RDY bit with the write command:

Continuous Conversion mode: No effect

One-Shot Conversion mode:

- 1 = Initiate a new conversion.

- 0 = No effect.

- bit 6-5 **C1-C0:** These bits are not effected for the MCP3421.

- bit 4 O/C: Conversion Mode Bit

- 1 = Continuous Conversion Mode (**Default**). The device performs data conversions continuously.

- 0 = One-Shot Conversion Mode. The device performs a single conversion and enters a low power standby mode until it receives another write or read command.

- bit 3-2 **S1-S0:** Sample Rate Selection Bit

00 = 240 SPS (12 bits) (Default)

01 = 60 SPS (14 bits)

10 = 15 SPS (16 bits)

11 = 3.75 SPS (18 bits)

bit 1-0 G1-G0: PGA Gain Selection Bits

00 = x1 (Default)

01 = x2

10 = x4

11 = x8

If the configuration byte is read repeatedly by clocking continuously after reading the data bytes (i.e., after the 5th byte in the 18-bit conversion mode), the state of the RDY bit indicates whether the device is ready with new conversion result. When the Master finds the RDY bit is cleared, it can send a not-acknowledge (NAK) bit and a stop bit to exit the current read operation and send a new read command for the latest conversion data. Once the conversion data has been read, the ready bit toggles to '1' until the next new conversion data is ready. The conversion data in the output register is overwritten every time a new conversion is completed.

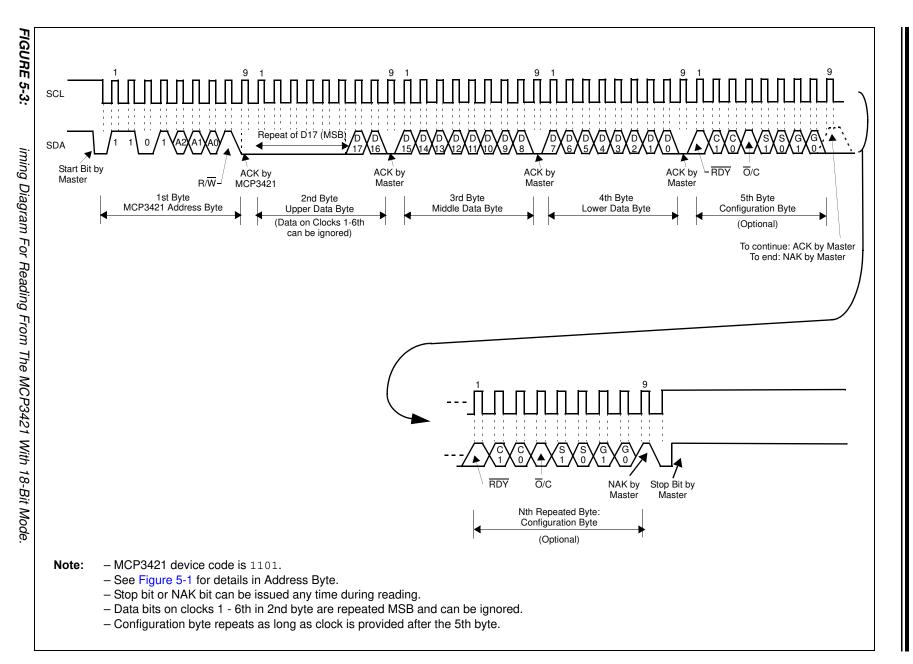

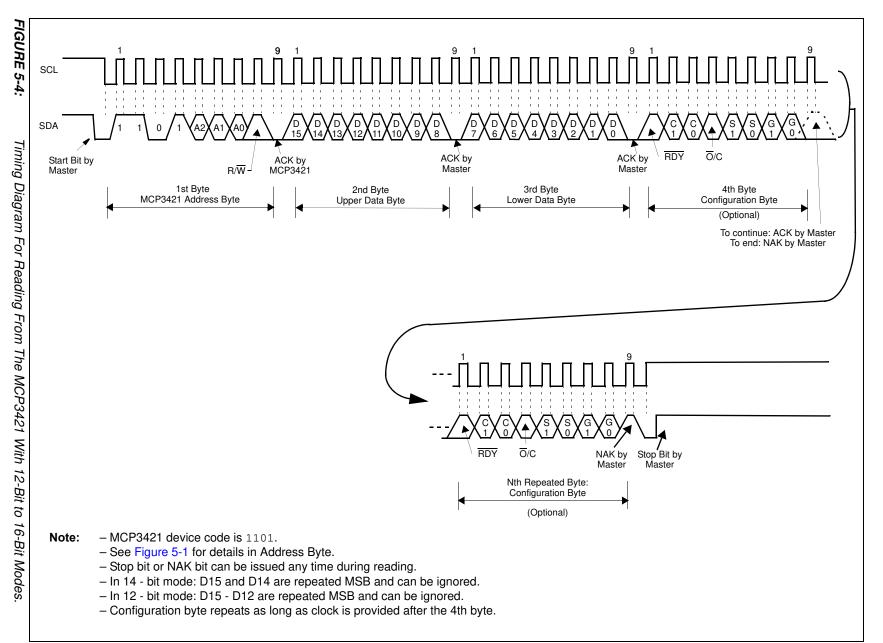

Figure 5-3 and Figure 5-4 show the examples of reading the conversion data. The user can rewrite the configuration byte any time for a new setting.

Table 5-1 and Table 5-2 show the examples of the configuration bit operation.

TABLE 5-1: WRITE CONFIGURATION BITS

| R/W | O/C | RDY | Operation                                                                                          |

|-----|-----|-----|----------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | No effect if all other bits remain<br>the same - operation continues<br>with the previous settings |

| 0   | 0   | 1   | Initiate One-Shot Conversion                                                                       |

| 0   | 1   | 0   | Initiate Continuous Conversion                                                                     |

| 0   | 1   | 1   | Initiate Continuous Conversion                                                                     |

TABLE 5-2: READ CONFIGURATION BITS

| R/W | Ō/C | RDY | Operation                                                                                                                                                                    |

|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0   | 0   | New conversion result in One-Shot conversion mode has just been read. The RDY bit remains low until set by a new write command.                                              |

| 1   | 0   | 1   | One-Shot Conversion is in progress. The conversion result is not updated yet. The RDY bit stays high until the current conversion is completed.                              |

| 1   | 1   | 0   | New conversion result in Continuous Conversion mode has just been read. The RDY bit changes to high after reading the conversion data.                                       |

| 1   | 1   | 1   | The conversion result in Continuous Conversion mode was already read. The next new conversion data is not ready. The RDY bit stays high until a new conversion is completed. |

#### 5.3 I<sup>2</sup>C Serial Communications

The device communicates with Master (microcontroller) through a serial I<sup>2</sup>C (Inter-Integrated Circuit) interface and support standard (100 kbits/sec), fast (400 kbits/sec) and high-speed (3.4 Mbits/sec) modes.

**Note:** The High-Speed mode is not recommended for V<sub>DD</sub> less than 2.7V.

The serial I<sup>2</sup>C is a bidirectional 2-wire data bus communication protocol using open-drain SCL and SDA lines.

The device can only be addressed as a slave. Once addressed, it can receive configuration bits with a write command or transmit the latest conversion results with a read command. The serial clock pin (SCL) is an input only and the serial data pin (SDA) is bidirectional. The Master starts communication by sending a START bit and terminates the communication by sending a STOP bit. In read mode, the device releases the SDA line after receiving NAK and STOP bits.

An example of a hardware connection diagram is shown in Figure 6-1. More details of the I<sup>2</sup>C bus characteristic is described in **Section 5.6** "I<sup>2</sup>C Bus Characteristics".

#### 5.3.1 I<sup>2</sup>C DEVICE ADDRESSING

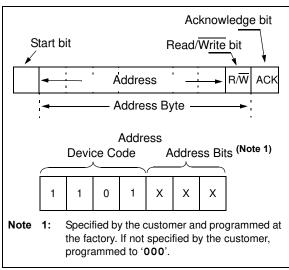

The first byte after the START bit is always the address byte of the device, which includes the device code (4 bits), address bits (3 bits), and R/W bit. The device code of the MCP3421 is 1101, which is programmed at the factory. The device code is followed by three address bits (A2, A1, A0) which are also programmed at the factory. The three address bits allow up to eight MCP3421 devices on the same data bus line.

The  $(R/\overline{W})$  bit determines if the Master device wants to read the conversion data or write to the Configuration register. If the  $(R/\overline{W})$  bit is set (read mode), the device outputs the conversion data in the following clocks. If the  $(R/\overline{W})$  bit is cleared (write mode), the device expects a configuration byte in the following clocks. When the device receives the correct address byte, it outputs an acknowledge bit after the  $R/\overline{W}$  bit.

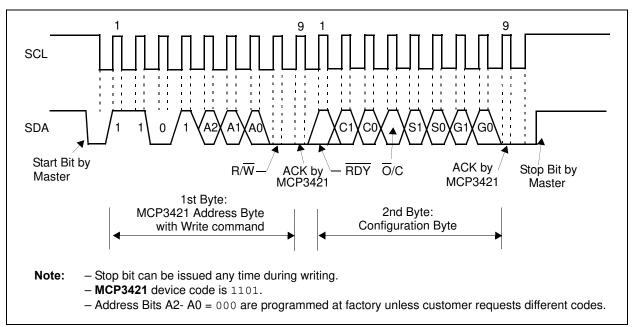

Figure 5-1 shows the address byte. Figure 5-2 through Figure 5-4 show how to write the configuration register bits and read the conversion results.

# 5.3.2 WRITING A CONFIGURATION BYTE TO THE DEVICE

When the Master sends an address byte with the  $R/\overline{W}$  bit low ( $R/\overline{W}=0$ ), the MCP3421 expects one configuration byte following the address. Any byte sent after this second byte will be ignored. The user can change the operating mode of the device by writing the configuration register bits.

If the device receives a write command with a new configuration setting, the device immediately begins a new conversion and updates the conversion data.

FIGURE 5-1: MCP3421 Address Byte.

FIGURE 5-2: Timing Diagram For Writing To The MCP3421.

# 5.3.3 READING OUTPUT CODES AND CONFIGURATION BYTE FROM THE DEVICE

When the Master sends a read command  $(R/\overline{W}=1)$ , the device outputs both the conversion data and configuration bytes. Each byte consists of 8 bits with one acknowledge (ACK) bit. The ACK bit after the address byte is issued by the device and the ACK bits after each conversion data bytes are issued by the Master.

When the device is configured for 18-bit conversion mode, it outputs three data bytes followed by a configuration byte. The first 6 data bits in the first data byte are repeated MSB (= sign bit) of the conversion data. The user can ignore the first 6 data bits, and take the 7th data bit (D17) as the MSB of the conversion data. The LSB of the 3rd data byte is the LSB of the conversion data (D0).

If the device is configured for 12, 14, or 16 bit-mode, the device outputs two data bytes followed by a configuration byte. In 16 bit-conversion mode, the MSB (= sign bit) of the first data byte is D15. In 14-bit conversion mode, the first two bits in the first data byte are repeated MSB bits and can be ignored, and the 3rd bit (D13) is the MSB (= sign bit) of the conversion data. In 12-bit conversion mode, the first four bits are repeated MSB bits and can be ignored. The 5th bit (D11) of the byte represents the MSB (= sign bit) of the conversion data. Table 5-3 summarizes the conversion data output of each conversion mode.

The configuration byte follows the output data bytes. The device repeatedly outputs the configuration byte only if the Master sends clocks repeatedly after the data bytes.

The device terminates the current outputs when it receives a Not-Acknowledge (NAK), a repeated start or a stop bit at any time during the output bit stream. It is not required to read the configuration byte. However, the  $\underline{\text{Master}}$  may read the configuration byte to check the  $\overline{\text{RDY}}$  bit condition. The Master may continuously send clock (SCL) to repeatedly read the configuration byte (to check the  $\overline{\text{RDY}}$  bit status).

Figures 5-3 and 5-4 show the timing diagrams of the reading.

TABLE 5-3: OUTPUT CODES OF EACH RESOLUTION OPTION

| Conversion<br>Option | Digital Output Codes                                                                              |

|----------------------|---------------------------------------------------------------------------------------------------|

| 18-bits              | MMMMMMD17D16 (1st data byte) - D15 ~ D8 (2nd data byte) - D7 ~ D0 (3rd data byte) - Configuration |

|                      | byte. (Note 1)                                                                                    |

| 16-bits              | D15 ~ D8 (1st data byte) - D7 ~ D0 (2nd data byte) - Configuration byte. (Note 2)                 |

| 14-bits              | MMD13D ~ D8 (1st data byte) - D7 ~ D0 (2nd data byte) - Configuration byte. (Note 3)              |

| 12-bits              | MMMMD11 ~ D8 (1st data byte) - D7 ~ D0 (2nd data byte) - Configuration byte. (Note 4)             |

Note 1: D17 is MSB (= sign bit), M is repeated MSB of the data byte.

- 2: D15 is MSB (= sign bit).

- 3: D13 is MSB (= sign bit), M is repeated MSB of the data byte.

- 4: D11 is MSB (= sign bit), M is repeated MSB of the data byte.

© 2009 Microchip Technology Inc

DS22003E-page 21

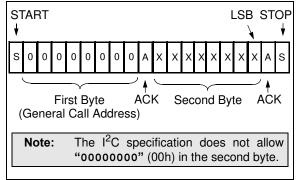

#### 5.4 General Call

The device acknowledges the general call address (0x00 in the first byte). The meaning of the general call address is always specified in the second byte. Refer to Figure 5-5. The device supports the following two general calls.

For more information on the general call, or other I<sup>2</sup>C modes, please refer to the Phillips I<sup>2</sup>C specification.

#### 5.4.1 GENERAL CALL RESET

The general call reset occurs if the second byte is '00000110' (06h). At the acknowledgement of this byte, the device will abort current conversion and perform an internal reset similar to a Power-On-Reset (POR). All configuration and data register bits are reset to default values.

#### 5.4.2 GENERAL CALL CONVERSION

The general call conversion occurs if the second byte is '00001000' (08h). All devices on the bus initiate a conversion simultaneously. When the device receives this command, the configuration will be set to the One-Shot Conversion mode and a single conversion will be performed. The PGA and data rate settings are unchanged with this general call.

FIGURE 5-5: General Call Address Format.

### 5.5 High-Speed (HS) Mode

The I<sup>2</sup>C specification requires that a high-speed mode device must be 'activated' to operate in high-speed mode. This is done by sending a special address byte of "00001xxx" following the START bit. The "xxx" bits are unique to the High-Speed (HS) mode Master. This byte is referred to as the High-Speed (HS) Master Mode Code (HSMMC). The MCP3421 device does not acknowledge this byte. However, upon receiving this code, the device switches on its HS mode filters and communicates up to 3.4 MHz on SDA and SCL bus lines. The device will switch out of the HS mode on the next STOP condition.

For more information on the HS mode, or other I<sup>2</sup>C modes, please refer to the Phillips I<sup>2</sup>C specification.

### 5.6 I<sup>2</sup>C Bus Characteristics

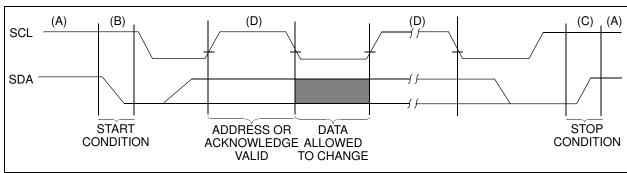

The I<sup>2</sup>C specification defines the following bus protocol:

- Data transfer may be initiated only when the bus is not busy

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition

Accordingly, the following bus conditions have been defined using Figure 5-6.

#### 5.6.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

#### 5.6.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 5.6.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations can be ended with a STOP condition.

#### 5.6.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition.

#### 5.6.5 ACKNOWLEDGE AND NON-ACKNOWLEDGE

The Master (microcontroller) and the slave (MCP3421) use an acknowledge pulse as a hand shake of communication for each byte. The ninth clock pulse of each byte is used for the acknowledgement. The clock pulse is always provided by the Master (microcontroller) and the acknowledgement is issued by the receiving device of the byte (Note: The transmitting device must release the SDA line during the acknowledge pulse.). The acknowledgement is achieved by pulling-down the SDA line "LOW" during the 9th clock pulse by the receiving device.

During reads, the Master (microcontroller) can terminate the current read operation by not providing an acknowledge bit (not Acknowledge (NAK)) on the last byte. In this case, the MCP3421 device releases the SDA line to allow the Master (microcontroller) to generate a STOP or repeated START condition.

The non-acknowledgement (NAK) is issued by providing the SDA line to "HIGH" during the 9th clock pulse.

FIGURE 5-6: Data Transfer Sequence on I<sup>2</sup>C Serial Bus.

TABLE 5-4: I<sup>2</sup>C SERIAL TIMING SPECIFICATIONS

**Electrical Specifications:** Unless otherwise specified, all limits are specified for  $T_A = -40$  to  $+85^{\circ}$ C,  $V_{IN}^{+} = V_{IN}^{-} = V_{REF}/2$ ,  $V_{SS} = 0$ V,  $V_{DD} = +2.7$ V to +5.0V.

| V <sub>IN</sub> T = V <sub>IN</sub> T = V <sub>REF</sub> /2, V <sub>SS</sub> = 0V, V <sub>DD</sub> = 72.7V to 73.0V. |                     |            |     |      |       |                                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------|------------|-----|------|-------|--------------------------------------------------|--|--|--|

| Parameters                                                                                                           | Sym                 | Min        | Тур | Max  | Units | Conditions                                       |  |  |  |

| Standard Mode (100 kHz)                                                                                              |                     |            |     |      |       |                                                  |  |  |  |

| Clock frequency                                                                                                      | f <sub>SCL</sub>    | _          | 1   | 100  | kHz   |                                                  |  |  |  |

| Clock high time                                                                                                      | T <sub>HIGH</sub>   | 4000       |     | _    | ns    |                                                  |  |  |  |

| Clock low time                                                                                                       | T <sub>LOW</sub>    | 4700       |     | _    | ns    |                                                  |  |  |  |

| SDA and SCL rise time                                                                                                | TR                  |            | _   | 1000 | ns    | From V <sub>IL</sub> to V <sub>IH</sub> (Note 1) |  |  |  |

| SDA and SCL fall time                                                                                                | T <sub>F</sub>      | _          |     | 300  | ns    | From V <sub>IH</sub> to V <sub>IL</sub> (Note 1) |  |  |  |

| START condition hold time                                                                                            | T <sub>HD:STA</sub> | 4000       | _   | _    | ns    |                                                  |  |  |  |

| START (Repeated) condition setup time                                                                                | T <sub>SU:STA</sub> | 4700       |     | _    | ns    |                                                  |  |  |  |

| Data hold time                                                                                                       | T <sub>HD:DAT</sub> | 0          |     | 3450 | ns    | (Note 3)                                         |  |  |  |

| Data input setup time                                                                                                | T <sub>SU:DAT</sub> | 250        |     | _    | ns    |                                                  |  |  |  |

| STOP condition setup time                                                                                            | T <sub>SU:STO</sub> | 4000       | _   | _    | ns    |                                                  |  |  |  |

| Output valid from clock                                                                                              | T <sub>AA</sub>     | 0          | _   | 3750 | ns    | (Note 2, Note 3)                                 |  |  |  |

| Bus free time                                                                                                        | T <sub>BUF</sub>    | 4700       | _   | _    | ns    | Time between START and STOP conditions.          |  |  |  |

| Fast Mode (400 kHz)                                                                                                  |                     |            |     |      |       |                                                  |  |  |  |

| Clock frequency                                                                                                      | T <sub>SCL</sub>    | _          | _   | 400  | kHz   |                                                  |  |  |  |

| Clock high time                                                                                                      | T <sub>HIGH</sub>   | 600        | _   | _    | ns    |                                                  |  |  |  |

| Clock low time                                                                                                       | T <sub>LOW</sub>    | 1300       | _   | _    | ns    |                                                  |  |  |  |

| SDA and SCL rise time                                                                                                | T <sub>R</sub>      | 20 + 0.1Cb | _   | 300  | ns    | From V <sub>IL</sub> to V <sub>IH</sub> (Note 1) |  |  |  |

| SDA and SCL fall time                                                                                                | T <sub>F</sub>      | 20 + 0.1Cb | _   | 300  | ns    | From V <sub>IH</sub> to V <sub>IL</sub> (Note 1) |  |  |  |

| START condition hold time                                                                                            | T <sub>HD:STA</sub> | 600        | _   | _    | ns    |                                                  |  |  |  |

| START (Repeated) condition setup time                                                                                | T <sub>SU:STA</sub> | 600        | _   | _    | ns    |                                                  |  |  |  |

| Data hold time                                                                                                       | T <sub>HD:DAT</sub> | 0          | _   | 900  | ns    | (Note 4)                                         |  |  |  |

| Data input setup time                                                                                                | T <sub>SU:DAT</sub> | 100        | _   | _    | ns    |                                                  |  |  |  |

| STOP condition setup time                                                                                            | T <sub>SU:STO</sub> | 600        | _   | _    | ns    |                                                  |  |  |  |

| Output valid from clock                                                                                              | T <sub>AA</sub>     | 0          | _   | 1200 | ns    | (Note 2, Note 3)                                 |  |  |  |

| Bus free time                                                                                                        | T <sub>BUF</sub>    | 1300       |     | _    | ns    | Time between START and STOP conditions.          |  |  |  |

- Note 1: This parameter is ensured by characterization and not 100% tested.

- 2: This specification is not a part of the  $I^2C$  specification. This specification is equivalent to the Data Hold Time  $(T_{HD:DAT})$  plus SDA Fall (or rise) time:  $T_{AA} = T_{HD:DAT} + T_F$  (OR  $T_R$ ).

- 3: If this parameter is too short, it can create an unintended Start or Stop condition to other devices on the bus line. If this parameter is too long, Clock Low time  $(T_{LOW})$  can be affected.

- **4:** For Data Input: This parameter must be longer than t<sub>SP</sub>. If this parameter is too long, the Data Input Setup (T<sub>SU:DAT</sub>) or Clock Low time (T<sub>LOW</sub>) can be affected. For Data Output: This parameter is characterized, and tested indirectly by testing T<sub>AA</sub> parameter.

### TABLE 5-4: I<sup>2</sup>C SERIAL TIMING SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all limits are specified for  $T_A = -40$  to  $+85^{\circ}$ C,  $V_{IN}^{+} = V_{IN}^{-} = V_{REF}^{-}/2$ ,  $V_{SS} = 0$ V,  $V_{DD} = +2.7$ V to +5.0V.

| Parameters                                                            | Sym                  | Min   | Тур | Max | Units    | Conditions                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------|----------------------|-------|-----|-----|----------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| High-Speed Mode (3.4 MHz): Not recommended for V <sub>DD</sub> < 2.7V |                      |       |     |     |          |                                                                                                     |  |  |  |  |

| Clock frequency                                                       | f <sub>SCL</sub>     | _     | _   | 3.4 | MHz      | C <sub>b</sub> = 100 pF                                                                             |  |  |  |  |

|                                                                       |                      | _     | _   | 1.7 | MHz      | C <sub>b</sub> = 400 pF                                                                             |  |  |  |  |

| Clock high time                                                       | T <sub>HIGH</sub>    | 60    | _   | _   | ns       | $C_b = 100 \text{ pF}, f_{SCL} = 3.4 \text{ MHz}$                                                   |  |  |  |  |

|                                                                       |                      | 120   | _   | _   | ns       | $C_b = 400 \text{ pF}, f_{SCL} = 1.7 \text{ MHz}$                                                   |  |  |  |  |

| Clock low time                                                        | T <sub>LOW</sub>     | 160   | _   | _   | ns       | $C_b = 100 \text{ pF}, f_{SCL} = 3.4 \text{ MHz}$                                                   |  |  |  |  |

|                                                                       |                      | 320   | _   | _   | ns       | $C_b = 400 \text{ pF}, f_{SCL} = 1.7 \text{ MHz}$                                                   |  |  |  |  |

| SCL rise time                                                         | $T_{R}$              | _     | _   | 40  | ns       | From V <sub>IL</sub> to V <sub>IH</sub> ,                                                           |  |  |  |  |

| (Note 1)                                                              |                      |       |     |     |          | $C_b = 100 \text{ pF}, f_{SCL} = 3.4 \text{ MHz}$                                                   |  |  |  |  |

|                                                                       |                      | _     | _   | 80  | ns       | From V <sub>IL</sub> to V <sub>IH</sub> ,                                                           |  |  |  |  |

| 221 ( 11 11                                                           | _                    |       |     |     |          | $C_b = 400 \text{ pF, } f_{SCL} = 1.7 \text{ MHz}$                                                  |  |  |  |  |

| SCL fall time<br>(Note 1)                                             | T <sub>F</sub>       | _     | _   | 40  | ns       | From $V_{IH}$ to $V_{IL}$ ,<br>$C_b = 100 \text{ pF}$ , $f_{SCL} = 3.4 \text{ MHz}$                 |  |  |  |  |

| (Note 1)                                                              |                      |       |     | 80  | ns       | From $V_{IH}$ to $V_{II}$ ,                                                                         |  |  |  |  |

|                                                                       |                      |       |     |     | 113      | $C_b = 400 \text{ pF, } f_{SCL} = 1.7 \text{ MHz}$                                                  |  |  |  |  |

| SDA rise time                                                         | T <sub>R: DAT</sub>  | DAT — | _   | 80  | ns       | From V <sub>II</sub> to V <sub>IH</sub> ,                                                           |  |  |  |  |

| (Note 1)                                                              | 11. 5711             |       |     |     |          | $C_b = 100 \text{ pF, } f_{SCL} = 3.4 \text{ MHz}$                                                  |  |  |  |  |

|                                                                       |                      | _     | _   | 160 | ns       | From V <sub>IL</sub> to V <sub>IH</sub> ,                                                           |  |  |  |  |

|                                                                       |                      |       |     |     |          | $C_b = 400 \text{ pF}, f_{SCL} = 1.7 \text{ MHz}$                                                   |  |  |  |  |

| SDA fall time                                                         | T <sub>F: DATA</sub> | _     | _   | 80  | ns       | From V <sub>IH</sub> to V <sub>IL</sub> ,                                                           |  |  |  |  |

| (Note 1)                                                              |                      |       |     | 100 |          | $C_b = 100 \text{ pF, } f_{SCL} = 3.4 \text{ MHz}$                                                  |  |  |  |  |