Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 200 Msps, 16-/14-Bit Low-Power ADC with 8-Channel MUX

#### **Features**

- · Sample Rates:

- 200 Msps for single-channel mode

- 200 Msps/number of channels used

- SNR with  $f_{IN}$  = 15 MHz and -1 dBFS:

- 74.7 dBFS (typical) at 200 Msps

- SFDR with f<sub>IN</sub> = 15 MHz and -1 dBFS:

- 90 dBc (typical) at 200 Msps

- · Power Dissipation with LVDS Digital I/O:

- 490 mW at 200 Msps

- · Power Dissipation with CMOS Digital I/O:

- 436 mW at 200 Msps, Output Clock = 100 MHz

- · Power Dissipation Excluding Digital I/O:

- 390 mW at 200 Msps

- · Power-Saving Modes:

- 144 mW during Standby

- 28 mW during Shutdown

- · Supply Voltage:

- Digital Section: 1.2V, 1.8V

- Analog Section: 1.2V, 1.8V

- Selectable Full-Scale Input Range: up to 2.975 V<sub>P-P</sub>

- · Input Channel Bandwidth: 500 MHz

- Channel-to-Channel Crosstalk in Multi-Channel Mode (Input = 15 MHz, -1 dBFS): >95 dB

- · Output Data Format:

- Parallel CMOS, DDR LVDS

- Serialized DDR LVDS (16-bit, octal-channel mode)

- · Optional Output Data Randomizer

- · Serial Peripheral Interface (SPI)

- Digital Signal Post-Processing (DSPP) Options:

- Decimation filters for improved SNR

- Fractional Delay Recovery (FDR) for timedelay corrections in multi-channel operations (dual-/octal-channel modes)

- Phase, Offset and Gain adjust of individual channels

- Digital Down-Conversion (DDC) with I/Q or f<sub>S</sub>/8 output (MCP37D31/21-200)

- Continuous wave beamforming for octalchannel mode (MCP37D31/21-200)

- · Built-In ADC Linearity Calibration Algorithms:

- Harmonic Distortion Correction (HDC)

- DAC Noise Cancellation (DNC)

- Dynamic Element Matching (DEM)

- Flash Error Calibration

- AutoSync Mode to Synchronize Multiple Devices to the Same Clock

- Package Options:

- VTLA-124 (9 mm x 9 mm x 0.9 mm)

- TFBGA-121 (8 mm x 8 mm x 1.08 mm)

- No External Reference Decoupling Capacitor Required for TFBGA Package

- Industrial Temperature Range: -40°C to +85°C

#### **Typical Applications**

- · Communication Instruments

- · Cellular Base Stations

- Radar

- · Ultrasound and Sonar Imaging

- · Scanners and Low-Power Portable Instruments

- · Industrial and Consumer Data Acquisition System

### MCP372XX/MCP37DXX Family Comparison(1):

|              |             |            | •                                    |                                           |                                  |                                             |

|--------------|-------------|------------|--------------------------------------|-------------------------------------------|----------------------------------|---------------------------------------------|

| Part Number  | Sample Rate | Resolution | Digital<br>Decimation <sup>(2)</sup> | Digital<br>Down-Conversion <sup>(3)</sup> | CW<br>Beamforming <sup>(4)</sup> | Noise-Shaping<br>Requantizer <sup>(2)</sup> |

| MCP37231-200 | 200 Msps    | 16         | Yes                                  | No                                        | No                               | No                                          |

| MCP37221-200 | 200 Msps    | 14         | Yes                                  | No                                        | No                               | No                                          |

| MCP37211-200 | 200 Msps    | 12         | Yes                                  | No                                        | No                               | Yes                                         |

| MCP37D31-200 | 200 Msps    | 16         | Yes                                  | Yes                                       | Yes                              | No                                          |

| MCP37D21-200 | 200 Msps    | 14         | Yes                                  | Yes                                       | Yes                              | No                                          |

| MCP37D11-200 | 200 Msps    | 12         | Yes                                  | Yes                                       | Yes                              | Yes                                         |

- Note 1: Devices in the same package type are pin-to-pin compatible.

- 2: Available in single- and dual-channel mode.

- 3: Available in single- and dual-channel mode, and octal-channel mode when CW beamforming is enabled.

- 4: Available in octal-channel mode.

#### **Functional Block Diagram** $AV_{DD18}$ $DV_{DD18}$ **GND** $DV_{DD12}$ $AV_{DD12}$ **Duty Cycle** DLL CLK+ Clock Correction Selection CLK-**PLL** DCLK+ **Output Clock Control** DCLK-A<sub>IN0</sub>+ Digital Signal Post-Processing: Input Multiplexer A<sub>IN0</sub>-- FDR, Decimation Pipelined ADC - Phase/Offset/Gain Adj. - DDC, CW Beamforming A<sub>IN7</sub>+ (MCP37D31/21-200) A<sub>IN7</sub>-**WCK** $V_{\mathsf{REF}}$ $V_{REF-}$ **OVR Output Control:** $V_{\mathsf{CM}}$ - CMOS, DDR LVDS - Serialized LVDS Reference Q[15:0] SENSE Generator Internal Registers $V_{BG}$ **SLAVE** REF1+ REF1- REF0+ REF0-SDIO SCLK CS SYNC

#### **Description**

The MCP37231/21-200 is Microchip's baseline 16-/14-bit 200 Msps pipelined ADC family, featuring built-in high-order digital decimation filters, gain and offset adjustment per channel and fractional delay recovery.

The MCP37D31/21-200 device family features digital down-conversion and CW beamforming capability, in addition to the features offered by the MCP37231/21-200.

All devices feature harmonic distortion correction and DAC noise cancellation that enable high-performance specifications with SNR of 74.7 dBFS (typical), and SFDR of 90 dBc (typical).

These A/D converters exhibit industry-leading low-power performance with only 490 mW operation while using the LVDS interface at 200 Msps. This superior low-power operation coupled with high dynamic performance makes these devices ideal for various high-performance, high-speed data acquisition systems, including communications equipment, radar and portable instrumentation.

The output decimation filter option improves SNR performance up to 93.5 dBFS with the 512x decimation setting. The digital down-conversion option, in conjunction with the decimation and quadrature output options, offers great flexibility in digital communication system design, including cellular base-stations and narrow-band communications. Gain, phase and DC offset can be adjusted independently for each input channel, allowing for simplified implementation of CW beamforming and ultrasound Doppler imaging applications.

These devices can have up to eight differential input channels through an input MUX. The sampling rate is up to 200 Msps when a single channel is used, or 25 Msps per channel when all eight input channels are used.

In dual or octal-channel mode, the Fractional Delay Recovery (FDR) feature digitally corrects the difference in sampling instance between different channels, so that all inputs appear to have been sampled at the same time.

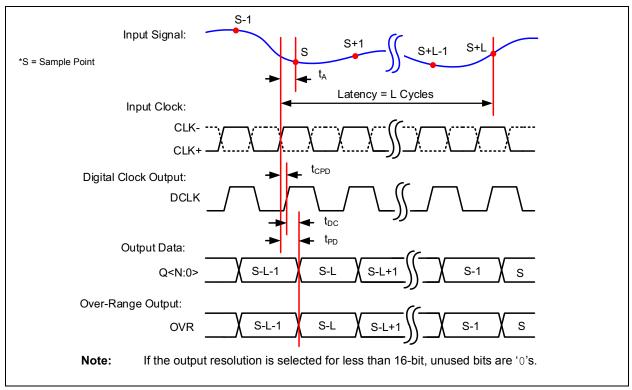

The device samples the analog input on the rising edge of the clock. The digital output code is available after 28 clock cycles of data latency. Latency will increase if any of the digital signal post-processing (DSPP) options are enabled.

AutoSync mode offers a great design flexibility when multiple devices are used in applications. It allows multiple devices to sample input synchronously at the same clock. The differential full-scale analog input range is programmable up to 2.975  $V_{P-P}$ . The ADC output data can be coded in two's complement or offset binary representation, with or without the data randomizer option. The output data is available as full-rate CMOS or Double-Data-Rate (DDR) LVDS. Additionally, a serialized LVDS option is also available for the 16-bit octal-channel mode.

These devices also include various features designed to maximize flexibility in the user's applications and minimize system cost, such as a programmable PLL clock, output data rate control and phase alignment and programmable digital pattern generation. The device's operational modes and feature sets are configured by setting up the user-programmable registers.

The device is available in Pb-free VTLA-124 and TFBGA-121 packages. The device operates over the commercial temperature range of -40°C to +85°C.

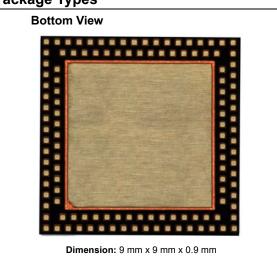

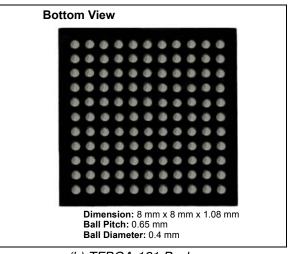

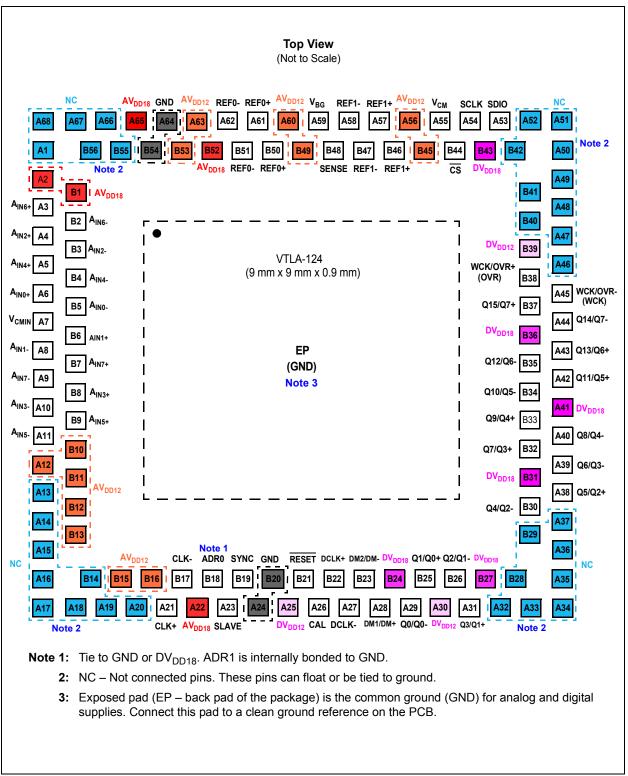

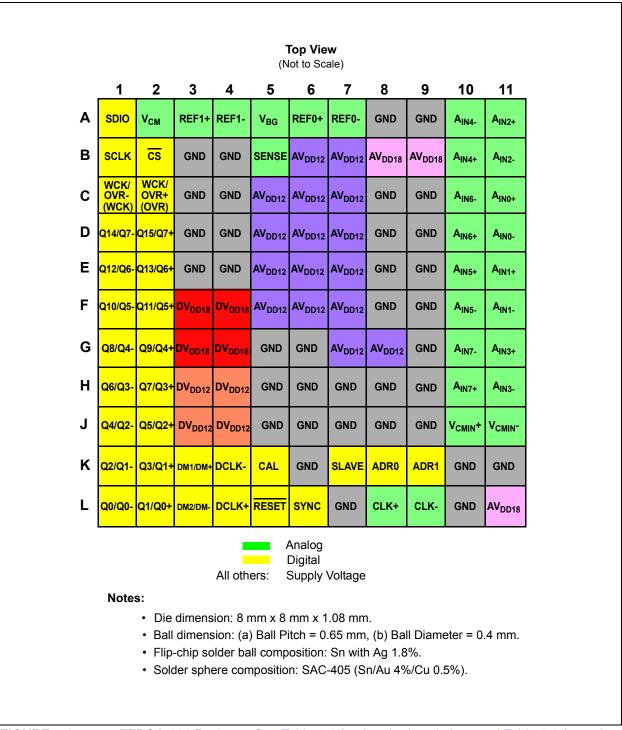

#### **Package Types**

(a) VTLA-124 Package.

(b) TFBGA-121 Package.

| VICE ST Z |  | 01001 | <br><u>,</u> |

|-----------|--|-------|--------------|

| OTES:     |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

|           |  |       |              |

# 1.0 PACKAGE PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

**FIGURE 1-1:** VTLA-124 Package. See Table 1-1 for the pin descriptions and Table 1-3 for active and inactive ADC output pins for various ADC resolution modes.

TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124

| Pin No.                                                                  | Name               | I/O Type         | Description                                                                                                        |

|--------------------------------------------------------------------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| Power Supply Pin                                                         | s                  |                  |                                                                                                                    |

| A2, A22, A65, B1,<br>B52                                                 | AV <sub>DD18</sub> | Supply           | Supply voltage input (1.8V) for analog section                                                                     |

| A12, A56, A60,<br>A63, B10, B11, B12,<br>B13, B15, B16,<br>B45, B49, B53 | AV <sub>DD12</sub> |                  | Supply voltage input (1.2V) for analog section                                                                     |

| A25, A30, B39                                                            | DV <sub>DD12</sub> |                  | Supply voltage input (1.2V) for digital section                                                                    |

| A41, B24, B27,<br>B31, B36, B43                                          | DV <sub>DD18</sub> |                  | Supply voltage input (1.8V) for digital section and all digital I/O                                                |

| EP                                                                       | GND                |                  | Exposed pad: Common ground pin for digital and analog sections                                                     |

| ADC Analog Input                                                         | Pins               |                  |                                                                                                                    |

| A3                                                                       | A <sub>IN6+</sub>  | Analog           | Channel 6 differential analog input (+)                                                                            |

| B2                                                                       | A <sub>IN6-</sub>  | Input            | Channel 6 differential analog input (-)                                                                            |

| A4                                                                       | A <sub>IN2+</sub>  |                  | Channel 2 differential analog input (+)                                                                            |

| В3                                                                       | A <sub>IN2-</sub>  |                  | Channel 2 differential analog input (-)                                                                            |

| A5                                                                       | A <sub>IN4+</sub>  |                  | Channel 4 differential analog input (+)                                                                            |

| B4                                                                       | A <sub>IN4-</sub>  |                  | Channel 4 differential analog input (-)                                                                            |

| A6                                                                       | A <sub>IN0+</sub>  |                  | Channel 0 differential analog input (+)                                                                            |

| B5                                                                       | A <sub>IN0-</sub>  |                  | Channel 0 differential analog input (-)                                                                            |

| B6                                                                       | A <sub>IN1+</sub>  |                  | Channel 1 differential analog input (+)                                                                            |

| A8                                                                       | A <sub>IN1-</sub>  |                  | Channel 1 differential analog input (-)                                                                            |

| B7                                                                       | A <sub>IN7+</sub>  |                  | Channel 7 differential analog input (+)                                                                            |

| A9                                                                       | A <sub>IN7-</sub>  |                  | Channel 7 differential analog input (-)                                                                            |

| B8                                                                       | A <sub>IN3+</sub>  |                  | Channel 3 differential analog input (+)                                                                            |

| A10                                                                      | A <sub>IN3-</sub>  |                  | Channel 3 differential analog input (-)                                                                            |

| B9                                                                       | A <sub>IN5+</sub>  |                  | Channel 5 differential analog input (+)                                                                            |

| A11                                                                      | A <sub>IN5-</sub>  |                  | Channel 5 differential analog input (-)                                                                            |

| A21                                                                      | CLK+               |                  | Differential clock input (+)                                                                                       |

| B17                                                                      | CLK-               |                  | Differential clock input (-)                                                                                       |

| Reference Pins <sup>(1)</sup>                                            |                    | •                |                                                                                                                    |

| A57, B46                                                                 | REF1+              | Analog           | Differential reference 1 (+) voltage                                                                               |

| A58, B47                                                                 | REF1-              | Output           | Differential reference 1 (-) voltage                                                                               |

| A61, B50                                                                 | REF0+              | 1                | Differential reference 0 (+) voltage                                                                               |

| A62, B51                                                                 | REF0-              | 1                | Differential reference 0 (-) voltage                                                                               |

| SENSE, Bandgap                                                           | and Commo          | n-Mode Volta     | ge Pins                                                                                                            |

| B48                                                                      | SENSE              | Analog<br>Input  | Analog input full-scale range selection. See Table 4-2 for SENSE voltage settings.                                 |

| A59                                                                      | $V_{BG}$           | Analog<br>Output | Internal bandgap output voltage<br>Connect a decoupling capacitor (2.2 µF)                                         |

| A7                                                                       | V <sub>CMIN</sub>  | Analog<br>Input  | Common-mode voltage input for auto-calibration Connect V <sub>CM</sub> voltage <sup>(2)</sup>                      |

| A55                                                                      | $V_{CM}$           |                  | Common-mode output voltage (900 mV) for analog input signal Connect a decoupling capacitor (0.1 µF) <sup>(3)</sup> |

### TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124 (CONTINUED)

|                  |       |                          | · · · · · · · · · · · · · · · · · · ·                                                                                               |

|------------------|-------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.          | Name  | I/O Type                 | Description                                                                                                                         |

| Digital I/O Pins |       |                          |                                                                                                                                     |

| B18              | ADR0  | Digital Input            | SPI address selection pin (A0 bit). Tie to GND or DV <sub>DD18</sub> . <sup>(4)</sup>                                               |

| A23              | SLAVE |                          | Slave or Master selection pin in AutoSync <sup>(12)</sup> . If not used, tie to GND.                                                |

| B19              | SYNC  | Digital Input/<br>Output | Digital synchronization pin for AutoSync (12) If not used, leave it floating.                                                       |

| B21              | RESET | Digital Input            | Reset control input: <b>High:</b> Normal operating mode <b>Low:</b> Reset mode <sup>(5)</sup>                                       |

| A26              | CAL   | Digital<br>Output        | Calibration status flag digital output: <b>High:</b> Calibration is complete <b>Low:</b> Calibration is not complete <sup>(6)</sup> |

| B22              | DCLK+ |                          | LVDS: Differential digital clock output (+) CMOS: Digital clock output <sup>(7)</sup>                                               |

| A27              | DCLK- |                          | LVDS: Differential digital clock output (-) CMOS: Unused (leave floating)                                                           |

TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124 (CONTINUED)

| Pin No.        | Name              | I/O Type | Description                                                                                                                                     |

|----------------|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC Output Pin | ıs <sup>(8)</sup> |          |                                                                                                                                                 |

| B23            | DM2/DM-           | Digital  | 18-bit mode: Digital data output (last two LSb bits) <sup>(9)</sup>                                                                             |

| A28            | DM1/DM+           | Output   | Other modes: Not used                                                                                                                           |

| A29            | Q0/Q0-            |          | Digital data output: CMOS = Q0 DDR LVDS = Q0- (Even bit first), Q8- (MSb byte first) Serialized LVDS = Q- for the last selected channel (n) = 8 |

| B25            | Q1/Q0+            |          | Digital data output: CMOS = Q1 DDR LVDS = Q0+ (Even bit first), Q8+ (MSb byte first) Serialized LVDS = Q+ for the last selected channel (n) = 8 |

| B26            | Q2/Q1-            |          | Digital data output: CMOS = Q2 DDR LVDS = Q1- (Even bit first), Q9- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 7             |

| A31            | Q3/Q1+            |          | Digital data output: CMOS = Q3 DDR LVDS = Q1+ (Even bit first), Q9+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 7             |

| B30            | Q4/Q2-            |          | Digital data output: CMOS = Q4 DDR LVDS = Q2- (Even bit first), Q10- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 6            |

| A38            | Q5/Q2+            |          | Digital data output: CMOS = Q5 DDR LVDS = Q2+ (Even bit first), Q10+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 6            |

| A39            | Q6/Q3-            |          | Digital data output: CMOS = Q6 DDR LVDS = Q3- (Even bit first), Q11- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 5            |

| B32            | Q7/Q3+            |          | Digital data output: CMOS = Q7 DDR LVDS = Q3+ (Even bit first), Q11+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 5            |

| A40            | Q8/Q4-            |          | Digital data output: CMOS = Q8 DDR LVDS = Q4- (Even bit first), Q12- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 4            |

| B33            | Q9/Q4+            |          | Digital data output: CMOS = Q9 DDR LVDS = Q4+ (Even bit first), Q12+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 4            |

| B34            | Q10/Q5-           |          | Digital data output: CMOS = Q10 DDR LVDS = Q5- (Even bit first), Q13- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 3           |

TABLE 1-1: PIN FUNCTION TABLE FOR VTLA-124 (CONTINUED)

| Pin No.                                                                                            | Name              | I/O Type                 | Description                                                                                                                                        |

|----------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| A42                                                                                                | Q11/Q5+           | Digital<br>Output        | Digital data output: CMOS = Q11  DDR LVDS = Q5+ (Even bit first), Q13+ (MSb byte first)  Serialized LVDS = Q+ for channel order (n) = 3            |

| B35                                                                                                | Q12/Q6-           |                          | Digital data output: CMOS = Q12 DDR LVDS = Q6- (Even bit first), Q14- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 2              |

| A43                                                                                                | Q13/Q6+           |                          | Digital data output: CMOS = Q13 DDR LVDS = Q6+ (Even bit first), Q14+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 2              |

| A44                                                                                                | Q14/Q7-           |                          | Digital data output: CMOS = Q14 DDR LVDS = Q7- (Even bit first), Q15- (MSb byte first) Serialized LVDS = Q- for the first selected channel (n) = 1 |

| B37                                                                                                | Q15/Q7+           |                          | Digital data output: CMOS = Q15 DDR LVDS = Q7+ (Even bit first), Q15+ (MSb byte first) Serialized LVDS = Q+ for the first selected channel (n) = 1 |

| B38                                                                                                | WCK/OVR+<br>(OVR) |                          | WCK: Word clock sync digital output  OVR: Input overrange indication digital output <sup>(11)</sup>                                                |

| A45                                                                                                | WCK/OVR-<br>(WCK) |                          |                                                                                                                                                    |

| SPI Interface Pins                                                                                 |                   |                          |                                                                                                                                                    |

| A53                                                                                                | SDIO              | Digital Input/<br>Output | SPI data input/output                                                                                                                              |

| A54                                                                                                | SCLK              | Digital                  | SPI serial clock input                                                                                                                             |

| B44                                                                                                | <del>CS</del>     | Input                    | SPI Chip Select input                                                                                                                              |

| Not Connected Pi                                                                                   | ns                |                          |                                                                                                                                                    |

| A1, A13 - A20, A32<br>- A37, A46 - A52,<br>A66 - A68, B14,<br>B28, B29, B40,<br>B41, B42, B55, B56 | NC                |                          | These pins can be tied to ground or left floating.                                                                                                 |

| Pins that need to                                                                                  | be grounded       |                          |                                                                                                                                                    |

| A24, A64, B20, B54                                                                                 | GND               |                          | These pins are not supply pins, but need to be tied to ground.                                                                                     |

#### Notes:

- These pins are for the internal reference voltage outputs. They should not be driven. External decoupling circuits

are required. See Section 4.5.3, "Decoupling Circuits for Internal Voltage Reference and Bandgap Output"

for details.

- V<sub>CMIN</sub> is used for Auto-Calibration only. V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- should be tied together always. There should be no voltage difference between the two pins. Typically both V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- are tied to the V<sub>CM</sub> output pin together, but they can be tied to another common-mode voltage if external V<sub>CM</sub> is used. This pin has High Z input in Shutdown, Standby and Reset modes.

- 3. When the  $V_{CM}$  output is used for the common-mode voltage of analog inputs (i.e. by connecting to the centertap of a balun), the  $V_{CM}$  pin should be decoupled with a 0.1  $\mu$ F capacitor, and should be directly tied to the  $V_{CMIN}$ + and  $V_{CMIN}$  pins.

- 4. ADR1 (for A1 bit) is internally bonded to GND ('0'). If ADR0 is dynamically controlled, ADR0 must be held constant while CS is "Low".

- 5. The device is in Reset mode while this pin stays "Low". On the rising edge of RESET, the device exits Reset mode, initializes all internal user registers to default values, and begins power-up calibration.

- 6. CAL pin stays "Low" at power-up until the first power-up calibration is completed. When the first calibration has completed, this pin has "High" output. It stays "High" until the internal calibration is restarted by hardware or a soft reset command. In Reset mode, this pin is "Low". In Standby and Shutdown modes, this pin will maintain the prior condition.

- 7. The phase of DCLK relative to the data output bits may be adjusted depending on the operating mode. This is controlled differently depending on the configuration of the digital signal post-processing, PLL and/or DLL. See also Addresses 0x52, 0x64 and 0x6D (Registers 5-7, 5-22 and 5-28) for more details.

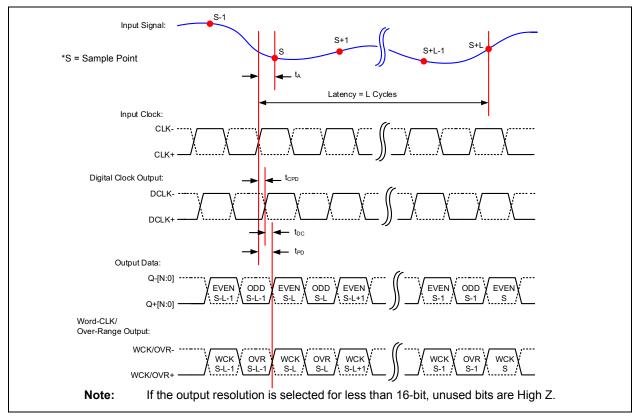

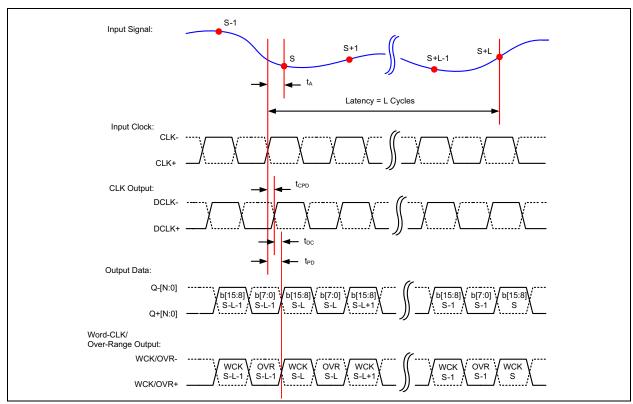

- 8. **DDR LVDS:** Two data bits are multiplexed onto each differential output pair. The output pins shown here are for the "Even bit first", which is the default setting of OUTPUT\_MODE<1:0> in Address 0x62 (Register 5-20). The even data bits (Q0, Q2, Q4, Q6, Q8, Q10, Q12, Q14) appear when DCLK+ is "High". The odd data bits (Q1, Q3, Q5, Q7, Q9, Q11, Q13, Q15) appear when DCLK+ is "Low". See Addresses 0x65 (Register 5-23) and 0x68 (Register 5-26) for output polarity control. See Figures 2-2 to 2-6 for LVDS output timing diagrams.

- Available for the MCP37231-200 and MCP37D31-200 devices only.

Leave these pins floating (No Connect) if not used.

- 10. 18-bit mode: DM1/DM+ and DM2/DM- are the last LSb bits. DM2/DM- is the LSb. In LVDS output, DM1/DM+ and DM2/DM- are the LSb pair. DM1/DM+ appears at the falling edge and DM2/DM- is at the rising edge of the DCLK+. Other than 18-bit mode: DM1/DM+ and DM2/DM- are High Z in LVDS mode.

- 11. CMOS output mode: WCK/OVR- is WCK and WCK/OVR+ is OVR.

- DDR LVDS output mode: The rising edge of DCLK+ is WCK and the falling edge is OVR.

- **OVR:** OVR will be held "High" when analog input overrange is detected. Digital signal post-processing will cause OVR to assert early relative to the output data. See Figure 2-2 for LVDS timing of these bits.

- **WCK:** WCK is normally "Low". WCK is "High" while data from the first channel is sent out. In single-channel mode, WCK stays "High" except when in I/Q output mode. In serialized LVDS (octal) output mode, the WCK output is asserted "High" on the MSb bit. See **Section 4.12.5** "Word Clock (WCK)" for further WCK description.

- 12. (a) SLAVE = "High": The device is selected as slave and the SYNC pin becomes input pin.

(b) SLAVE = "Low": The device is selected as master and the SYNC pin becomes output pin. In SL

- (b) SLAVE = "Low": The device is selected as master and the SYNC pin becomes output pin. In SLAVE/SYNC operation, master and slave devices are synchronized to the same clock.

**FIGURE 1-2:** TFBGA-121 Package. See <u>Table 1-2</u> for the pin descriptions and <u>Table 1-3</u> for active and inactive ADC output pins for various ADC resolution modes.

TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121

| Ball No.   | Name               | I/O Type                 | Description                                                                                                                     |

|------------|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| A1         | SDIO               | Digital Input/<br>Output | SPI data input/output                                                                                                           |

| A2         | V <sub>CM</sub>    | Analog<br>Output         | Common-mode output voltage (900 mV) for analog input signal Connect a decoupling capacitor (0.1 µF) <sup>(1)</sup>              |

| A3         | REF1+              |                          | Differential reference voltage 1 (+/-). Decoupling capacitors are embedded in                                                   |

| A4         | REF1-              |                          | the TFBGA package. Leave these pins floating.                                                                                   |

| A5         | V <sub>BG</sub>    |                          | Internal bandgap output voltage A decoupling capacitor (2.2 $\mu$ F) is embedded in the TFBGA package. Leave this pin floating. |

| A6         | REF0+              |                          | Differential reference 0 (+/-) voltage. Decoupling capacitors are embedded in                                                   |

| A7         | REF0-              |                          | the TFBGA package. Leave these pins floating.                                                                                   |

| A8         | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| A9         |                    |                          |                                                                                                                                 |

| A10        | A <sub>IN4-</sub>  | Analog Input             | Channel 4 differential analog input (-)                                                                                         |

| A11        | A <sub>IN2+</sub>  |                          | Channel 2 differential analog input (+)                                                                                         |

| B1         | SCLK               | Digital Input            | SPI serial clock input                                                                                                          |

| B2         | CS                 |                          | SPI Chip Select input                                                                                                           |

| В3         | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| B4         | =                  | ,                        |                                                                                                                                 |

| B5         | SENSE              | Analog<br>Input          | Analog input range selection. See Table 4-2 for SENSE voltage settings.                                                         |

| B6         | AV <sub>DD12</sub> | Supply                   | Supply voltage input (1.2V) for analog section                                                                                  |

| B7         | 1 1 00 12          | 3 3 4 4 5                |                                                                                                                                 |

| B8         | AV <sub>DD18</sub> |                          | Supply voltage input (1.8V) for analog section                                                                                  |

| B9         | 1 10010            |                          | - sepp., samge repair (see system and see see                                                                                   |

| B10        | A <sub>IN4+</sub>  | Analog Input             | Channel 4 differential analog input (+)                                                                                         |

| B11        | A <sub>IN2-</sub>  | Analog Input             | Channel 2 differential analog input (-)                                                                                         |

| C1         | WCK/OVR-<br>(WCK)  | Digital<br>Output        | WCK: Word clock sync digital output  OVR: Input overrange indication digital output <sup>(2)</sup>                              |

| C2         | WCK/OVR+<br>(OVR)  |                          |                                                                                                                                 |

| C3         | GND                | Supply                   | Common ground for analog and digital sections                                                                                   |

| C4         |                    |                          |                                                                                                                                 |

| C5         | AV <sub>DD12</sub> |                          | Supply voltage input (1.2V) for analog section                                                                                  |

| C6         |                    |                          |                                                                                                                                 |

| C7         |                    |                          |                                                                                                                                 |

| C8         | GND                |                          | Common ground pin for analog and digital sections                                                                               |

| C9         |                    |                          |                                                                                                                                 |

| C10        | A <sub>IN6-</sub>  | Analog Innut             | Channel 6 differential analog input (-)                                                                                         |

| C11        | A <sub>IN0+</sub>  | Analog Input             | Channel 0 differential analog input (+)                                                                                         |

| D1         | Q14/Q7-            | Digital<br>Output        | Digital data output <sup>(3)</sup> CMOS = Q14 DDR LVDS = Q7- (Even bit first), Q15- (MSb byte first)                            |

| <b>D</b> 2 | 0.45105            |                          | Serialized LVDS = Q- for the first selected channel (n = 1)                                                                     |

| D2         | Q15/Q7+            |                          | Digital data output <sup>(3)</sup>                                                                                              |

|            |                    |                          | CMOS = Q15<br>DDR LVDS = Q7+ (Even bit first), Q15+ (MSb byte first)                                                            |

|            |                    | i .                      | 11/1/15 1 VIOU = 577 1 U VEH DIL 1118D. 57 10T UVIOU DVIE 1118D                                                                 |

TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121 (CONTINUED)

| Ball No. | Name               | I/O Type          | Description                                                                                                                                         |

|----------|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| D3       | GND                | Supply            | Common ground for analog and digital sections                                                                                                       |

| D4       | OND                | Guppiy            | Common ground for analog and digital sections                                                                                                       |

| D5       | AV <sub>DD12</sub> | Supply            | Supply voltage input (1.2V) for analog section                                                                                                      |

| D6       | 7 10012            | Сарріу            | Capply voltage input (1.2 v) for analog occurr                                                                                                      |

| D7       |                    |                   |                                                                                                                                                     |

| D8       | GND                | -                 | Common ground for analog and digital sections                                                                                                       |

| D9       |                    |                   |                                                                                                                                                     |

| D10      | A <sub>IN6+</sub>  | Analaa Innut      | Channel 6 differential analog input (+)                                                                                                             |

| D11      | A <sub>IN0-</sub>  | Analog Input      | Channel 0 differential analog input (-)                                                                                                             |

| E1       | Q12/Q6-            | Digital<br>Output | Digital data output <sup>(3)</sup> CMOS = Q12 DDR LVDS = Q6- (Even bit first), Q14- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 2 |

| E2       | Q13/Q6+            |                   | Digital data output <sup>(3)</sup> CMOS = Q13 DDR LVDS = Q6+ (Even bit first), Q14+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 2 |

| E3       | GND                | Supply            | Common ground for analog and digital sections                                                                                                       |

| E4       |                    |                   |                                                                                                                                                     |

| E5       | $AV_{DD12}$        |                   | Supply voltage input (1.2V) for analog section                                                                                                      |

| E6       |                    |                   |                                                                                                                                                     |

| E7       | OND                | -                 | Occurred to an also and digital as attacks                                                                                                          |

| E8<br>E9 | GND                |                   | Common ground for analog and digital sections                                                                                                       |

|          | Δ                  |                   | Channel 5 differential analog input (+)                                                                                                             |

| E10      | A <sub>IN5+</sub>  | Analog Input      |                                                                                                                                                     |

| E11      | A <sub>IN1+</sub>  | 5                 | Channel 1 differential analog input (+)                                                                                                             |

| F1       | Q10/Q5-            | Digital<br>Output | Digital data output <sup>(3)</sup> CMOS = Q10 DDR LVDS = Q5- (Even bit first), Q13- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 3 |

| F2       | Q11/Q5+            |                   | Digital data output <sup>(3)</sup> CMOS = Q11 DDR LVDS = Q5+ (Even bit first), Q13+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 3 |

| F3<br>F4 | DV <sub>DD18</sub> | Supply            | Supply voltage input (1.8V) for digital section. All digital input pins are driven by the same DV <sub>DD18</sub> potential.                        |

| F5       | AV <sub>DD12</sub> |                   | Supply voltage input (1.2V) for analog section                                                                                                      |

| F6       |                    |                   |                                                                                                                                                     |

| F7       |                    |                   |                                                                                                                                                     |

| F8       | GND                |                   | Common ground for analog and digital sections                                                                                                       |

| F9       |                    |                   |                                                                                                                                                     |

| F10      | A <sub>IN5-</sub>  | Analog Input      | Channel 5 differential analog input (-)                                                                                                             |

| F11      | A <sub>IN1-</sub>  | 1, alalog lilput  | Channel 1 differential analog input (-)                                                                                                             |

TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121 (CONTINUED)

| Ball No.             | Name               | I/O Type          | Description                                                                                                                                                                                                                                                                                           |

|----------------------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G1                   | Q8/Q4-             | Digital<br>Output | Digital data output <sup>(3)</sup> CMOS = Q8 DDR LVDS = Q4- (Even bit first), Q12- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 4                                                                                                                                                    |

| G2                   | Q9/Q4+             |                   | Digital data output <sup>(3)</sup> CMOS = Q9 DDR LVDS = Q4+ (Even bit first), Q12+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 4                                                                                                                                                    |

| G3<br>G4             | DV <sub>DD18</sub> | Supply            | Supply voltage input (1.8V) for digital section All digital input pins are driven by the same DV <sub>DD18</sub> potential                                                                                                                                                                            |

| G5<br>G6             | GND                |                   | Common ground for analog and digital sections                                                                                                                                                                                                                                                         |

| G7<br>G8             | AV <sub>DD12</sub> | Supply            | Supply voltage input (1.2V) for analog section                                                                                                                                                                                                                                                        |

| G9                   | GND                |                   | Common ground for analog and digital sections                                                                                                                                                                                                                                                         |

| G10                  | A <sub>IN7-</sub>  | Analog Input      | Channel 7 differential analog input (-)                                                                                                                                                                                                                                                               |

| G11                  | A <sub>IN3+</sub>  |                   | Channel 3 differential analog input (+)                                                                                                                                                                                                                                                               |

| H1                   | Q6/Q3-             | Digital<br>Output | Digital data output <sup>(3)</sup> CMOS = Q6 DDR LVDS = Q3- (Even bit first), Q11- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 5                                                                                                                                                    |

| H2                   | Q7/Q3+             |                   | Digital data output <sup>(3)</sup> CMOS = Q7 DDR LVDS = Q3+ (Even bit first), Q11+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 5                                                                                                                                                    |

| H3<br>H4             | DV <sub>DD12</sub> | Supply            | Supply voltage input (1.2V) for digital section                                                                                                                                                                                                                                                       |

| H5<br>H6<br>H7<br>H8 | GND                |                   | Common ground for analog and digital sections                                                                                                                                                                                                                                                         |

| H9                   | Λ                  |                   | Channel 7 differential analog input (+)                                                                                                                                                                                                                                                               |

| H10                  | A <sub>IN7+</sub>  | Analog Input      |                                                                                                                                                                                                                                                                                                       |

| H11                  | A <sub>IN3-</sub>  | D: a:1-1          | Channel 3 differential analog input (-)                                                                                                                                                                                                                                                               |

| J1<br>J2             | Q4/Q2-<br>Q5/Q2+   | Digital<br>Output | Digital data output <sup>(3)</sup> CMOS = Q4 DDR LVDS = Q2- (Even bit first), Q10- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 6 Digital data output <sup>(3)</sup> CMOS = Q5 DDR LVDS = Q2+ (Even bit first), Q10+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 6 |

| J3                   | DV <sub>DD12</sub> | Supply            | DC supply voltage input pin for digital section (1.2V)                                                                                                                                                                                                                                                |

| J4                   | 0012               |                   |                                                                                                                                                                                                                                                                                                       |

| J5                   | GND                |                   | Common ground for analog and digital sections                                                                                                                                                                                                                                                         |

| J6                   |                    |                   |                                                                                                                                                                                                                                                                                                       |

| J7                   |                    |                   |                                                                                                                                                                                                                                                                                                       |

| J8                   |                    |                   |                                                                                                                                                                                                                                                                                                       |

| J9                   |                    |                   |                                                                                                                                                                                                                                                                                                       |

TABLE 1-2: PIN FUNCTION TABLE FOR TFBGA-121 (CONTINUED)

| Ball No. | Name                | I/O Type                 | Description                                                                                                                                                 |

|----------|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J10      | V <sub>CMIN+</sub>  | Analog Input             | Common-mode voltage input for auto-calibration <sup>(4)</sup>                                                                                               |

| J11      | V <sub>CMIN</sub> - | -                        | These two pins should be tied together and connected to V <sub>CM</sub> voltage.                                                                            |

| K1       | Q2/Q1-              | Digital<br>Output        | Digital data output <sup>(3)</sup> CMOS = Q2 DDR LVDS = Q1- (Even bit first), Q9- (MSb byte first) Serialized LVDS = Q- for channel order (n) = 7           |

| K2       | Q3/Q1+              |                          | Digital data output <sup>(3)</sup> CMOS = Q3 DDR LVDS = Q1+ (Even bit first), Q9+ (MSb byte first) Serialized LVDS = Q+ for channel order (n) = 7           |

| K3       | DM1/DM+             |                          | <b>18-bit mode:</b> Digital data output. DM1 and DM2 are the last two LSb bits <sup>(5)</sup> <b>Other modes:</b> Not used                                  |

| K4       | DCLK-               |                          | LVDS: Differential digital clock output (-) CMOS: Not used (leave floating)                                                                                 |

| K5       | CAL                 | Digital<br>Output        | Calibration status flag digital output <sup>(6)</sup> <b>High:</b> Calibration is complete <b>Low:</b> Calibration is not complete                          |

| K6       | GND                 | Supply                   | Common ground pin for analog and digital sections                                                                                                           |

| K7       | SLAVE               | Digital Input            | Slave or Master selection pin in AutoSync <sup>(10)</sup> . If not used, tie to GND.                                                                        |

| K8       | ADR0                |                          | SPI address selection pin (A0 bit). Tie to GND or DVDD18 <sup>(7)</sup>                                                                                     |

| K9       | ADR1                |                          | SPI address selection pin (A1 bit). Tie to GND or DVDD18 <sup>(7)</sup>                                                                                     |

| K10      | GND                 | Supply                   | Common ground for analog and digital sections                                                                                                               |

| K11      |                     |                          |                                                                                                                                                             |

| L1       | Q0/Q0-              | Digital<br>Output        | Digital data output <sup>(3)</sup> CMOS = Q0 DDR LVDS = Q0- (Even bit first), Q8- (MSb byte first) Serialized LVDS = Q- for the last selected channel (n=8) |

| L2       | Q1/Q0+              |                          | Digital data output <sup>(8)</sup> CMOS = Q1 DDR LVDS = Q0+ (Even bit first), Q8+ (MSb byte first) Serialized LVDS = Q+ for the last selected channel (n=8) |

| L3       | DM2/DM-             |                          | <b>18-bit mode:</b> Digital data output. DM1 and DM2 are the last two LSb bits <sup>(5)</sup> <b>Other modes:</b> Not used                                  |

| L4       | DCLK+               |                          | LVDS: Differential digital clock output (+) CMOS: Digital clock output <sup>(8)</sup>                                                                       |

| L5       | RESET               | Digital Input            | Reset control input: <b>High</b> : Normal operating mode <b>Low:</b> Reset mode <sup>(9)</sup>                                                              |

| L6       | SYNC                | Digital Input/<br>Output | Digital synchronization pin for AutoSync <sup>(10)</sup> If not used, leave it floating.                                                                    |

| L7       | GND                 | Supply                   | Common ground for analog and digital sections                                                                                                               |

| L8       | CLK+                | Analog Input             | Differential clock input (+)                                                                                                                                |

| L9       | CLK-                |                          | Differential clock input (-)                                                                                                                                |

| L10      | GND                 | Supply                   | Common ground for analog and digital sections                                                                                                               |

| L11      | AV <sub>DD18</sub>  | Analog Input             | Supply voltage input (1.8V) for analog section                                                                                                              |

#### Notes:

- 1. When the  $V_{CM}$  output is used for the common-mode voltage of analog inputs (i.e. by connecting to the center-tap of a balun), the  $V_{CM}$  pin should be decoupled with a 0.1  $\mu$ F capacitor, and should be directly tied to the  $V_{CMIN}$ + and  $V_{CMIN}$ -pins.

- CMOS output mode: WCK/OVR- is WCK and WCK/OVR+ is OVR.

DDR LVDS output mode: The rising edge of DCLK+ is WCK and the falling edge is OVR.

- **OVR:** OVR will be held "High" when analog input overrange is detected. Digital signal post-processing will cause OVR to assert early relative to the output data. See Figure 2-2 for LVDS timing of these bits.

- **WCK:** WCK is normally "Low". WCK is "High" while data from the first channel is sent out. In single-channel mode, WCK stays "High" except when in I/Q output mode. In serialized LVDS (octal) output mode, the WCK output is asserted "High" on the MSb bit. See **Section 4.12.5** "Word Clock (WCK)" for further WCK description.

- 3. **DDR LVDS:** Two data bits are multiplexed onto each differential output pair. The output pins shown here are for the "Even bit first", which is the default setting of OUTPUT\_MODE<1:0> in Address 0x62 (Register 5-20). The even data bits (Q0, Q2, Q4, Q6, Q8, Q10, Q12, Q14) appear when DCLK+ is "High". The odd data bits (Q1, Q3, Q5, Q7, Q9, Q11, Q13, Q15) appear when DCLK+ is "Low". See Addresses 0x65 (Register 5-23) and 0x68 (Register 5-26) for output polarity control. See Figures 2-2 to 2-6 for LVDS output timing diagrams.

- 4. V<sub>CMIN</sub> is used for Auto-Calibration only. V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- should be tied together always. There should be no voltage difference between the two pins. Typically both V<sub>CMIN</sub>+ and V<sub>CMIN</sub>- are tied to the V<sub>CM</sub> output pin together, but they can be tied to another common-mode voltage if external V<sub>CM</sub> is used. This pin has High Z input in Shutdown, Standby and Reset modes.

- 5. Available for the MCP37231-200 and MCP37D31-200 devices only. Leave these pins floating (No Connect) if not used.

- **18-bit mode:** DM1/DM+ and DM2/DM- are the last LSb bits. DM2/DM- is the LSb. In LVDS output, DM1/DM+ and DM2/DM- are the LSb pair. DM1/DM+ appears at the falling edge and DM2/DM- is at the rising edge of the DCLK+. **Other than 18-bit mode:** DM1/DM+ and DM2/DM- are High Z in LVDS mode.

- 6. CAL pin stays "Low" at power-up until the first power-up calibration is completed. When the first calibration has completed, this pin has "High" output. It stays "High" until the internal calibration is restarted by hardware or a soft reset command. In Reset mode, this pin is "Low". In Standby and Shutdown modes, this pin will maintain the prior condition.

- 7. If the SPI address is dynamically controlled, the Address pin must be held constant while  $\overline{\mathsf{CS}}$  is "Low".

- 8. The phase of DCLK relative to the data output bits may be adjusted depending on the operating mode. This is controlled differently depending on the configuration of the digital signal post-processing, PLL and/or DLL. See also Addresses 0x52, 0x64 and 0x6D (Registers 5-7, 5-22 and 5-28) for more details.

- 9. The device is in Reset mode while this pin stays "Low". On the rising edge of RESET, the device exits Reset mode, initializes all internal user registers to default values, and begins power-up calibration.

- 10. (a) SLAVE = "High": The device is selected as slave and the SYNC pin becomes input pin.(b) SLAVE = "Low": The device is selected as master and the SYNC pin becomes output pin. In SLAVE/SYNC operation, master and slave devices are synchronized to the same clock.

TABLE 1-3: DATA OUTPUT PINS FOR EACH RESOLUTION OPTION

| ADC                        | Output Pin Name |                                                        |             |             |             |             |            |            |            |            |                         |            |            |            |            |            |             |             |

|----------------------------|-----------------|--------------------------------------------------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|-------------------------|------------|------------|------------|------------|------------|-------------|-------------|

| Resolution                 | Q15/<br>Q7+     | Q14/<br>Q7-                                            | Q13/<br>Q6+ | Q12/<br>Q6- | Q11/<br>Q5+ | Q10/<br>Q5- | Q9/<br>Q4+ | Q8/<br>Q4- | Q7/<br>Q3+ | Q6/<br>Q3- | Q5/<br>Q2+              | Q4/<br>Q2- | Q3/<br>Q1+ | Q2/<br>Q1- | Q1/<br>Q0+ | Q0/<br>Q0- | DM1/<br>DM+ | DM2<br>/DM- |

| 18-bit mode                |                 | Q15 pin is MSb (bit 17), and DM2 is LSb (bit 0)        |             |             |             |             |            |            |            |            |                         |            |            |            |            |            |             |             |

| 16-bit mode                |                 | Q15 pin is MSb, and Q0 is LSb Notused <sup>(2)</sup>   |             |             |             |             |            |            |            |            | sed <sup>(2)</sup>      |            |            |            |            |            |             |             |

| 14-bit mode <sup>(1)</sup> |                 | Q15 pin is MSb, and Q2 is LSb Not used <sup>(2)</sup>  |             |             |             |             |            |            |            |            |                         |            |            |            |            |            |             |             |

| 12-bit mode                |                 | Q15 pin is MSb, and Q4 is LSb  Not used <sup>(2)</sup> |             |             |             |             |            |            |            |            |                         |            |            |            |            |            |             |             |

| 10-bit mode                |                 | Q15 pin is MSb, and Q6 is LSb                          |             |             |             |             |            |            |            |            | Not used <sup>(2)</sup> |            |            |            |            |            |             |             |

- **Note 1:** The MCP37221-200 and MCP37D21-200 devices have the 14-bit mode option only, while the MCP37231-200 and MCP37D31-200 have all listed resolution options.

- 2: Output condition at "not-used" output pin:

- '0' in CMOS mode. Leave these pins floating.

- High Z state in LVDS mode

### 2.0 ELECTRICAL SPECIFICATIONS

### 2.1 Absolute Maximum Ratings†

| Analog and digital supply voltage (AV <sub>DD12</sub> , DV <sub>DD12</sub> ) | 0.3V to 1.32V                                  |

|------------------------------------------------------------------------------|------------------------------------------------|

| Analog and digital supply voltage (AV <sub>DD18</sub> , DV <sub>DD18</sub> ) | 0.3V to 1.98V                                  |

| All inputs and outputs with respect to GND                                   | 0.3V to AV <sub>DD18</sub> + 0.3V              |

| Differential input voltage                                                   | AV <sub>DD18</sub> - GND                       |

| Current at input pins                                                        | ±2 mA                                          |

| Current at output and supply pins                                            | ±250 mA                                        |

| Storage temperature                                                          | 65°C to +150°C                                 |

| Ambient temperature with power applied (T <sub>A</sub> )                     | 55°C to +125°C                                 |

| Maximum junction temperature (T <sub>J</sub> )                               | +150°C                                         |

| ESD protection on all pins                                                   | 2 kV HBM                                       |

| Solder reflow profile                                                        | See Microchip Application Note AN233 (DS00233) |

**Notice†**: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 2.2 Electrical Specifications

#### TABLE 2-1: ELECTRICAL CHARACTERISTICS

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $AV_{DD18} = DV_{DD18} = 1.8V$ ,  $AV_{DD12} = DV_{DD12} = 1.2V$ , GND = 0V,  $SENSE = AV_{DD12}$ , Single-channel mode, Differential Analog Input  $(A_{IN}) = Sine$  wave with amplitude of -1 dBFS,  $f_{IN} = 70$  MHz, Clock Input = 200 MHz,  $f_S = 200$  Msps (ADC Core), Resolution = 16-bit, PLL and decimation filters are disabled, Output load: CMOS data pin = 10 pF,  $LVDS = 100\Omega$  termination, LVDS driver current setting = 3.5 mA,  $+25^{\circ}\text{C}$  is applied for typical value.

| Parameters                               | Sym.                     | Min.                               | Тур. | Max. | Units | Conditions                                  |

|------------------------------------------|--------------------------|------------------------------------|------|------|-------|---------------------------------------------|

| Power Supply Requirem                    | ents                     |                                    |      |      | •     |                                             |

| Analog Supply Voltage                    | AV <sub>DD18</sub>       | 1.71                               | 1.8  | 1.89 | V     |                                             |

|                                          | AV <sub>DD12</sub>       | 1.14                               | 1.2  | 1.26 | V     |                                             |

| Digital Supply Voltage                   | DV <sub>DD18</sub>       | 1.71                               | 1.8  | 1.89 | V     | Note 1                                      |

|                                          | DV <sub>DD12</sub>       | 1.14                               | 1.2  | 1.26 | V     |                                             |

| <b>Analog Supply Current</b>             |                          |                                    |      |      |       |                                             |

| Analog Supply Current                    | I <sub>DD_A18</sub>      | _                                  | 27   | 46   | mA    | at AV <sub>DD18</sub> pin                   |

| During Conversion                        | I <sub>DD_A12</sub>      | _                                  | 185  | 252  | mA    | at AV <sub>DD12</sub> pin                   |

| Digital Supply Current                   |                          |                                    |      |      |       |                                             |

| Digital Supply Current During Conversion | I <sub>DD_D12</sub>      | _                                  | 97   | 226  | mA    | at DV <sub>DD12</sub> pin                   |

| Digital I/O Current in CMOS Output Mode  | I <sub>DD_D18</sub>      | _                                  | 27   | _    | mA    | at DV <sub>DD18</sub> pin<br>DCLK = 100 MHz |

| Digital I/O Current in                   | I <sub>DD_D18</sub>      | Measured at DV <sub>DD18</sub> Pin |      |      |       | •                                           |

| LVDS Mode                                | _                        |                                    | 55   | 81   | mA    | 3.5 mA mode                                 |

|                                          |                          | _                                  | 39   | _    | mA    | 1.8 mA mode                                 |

|                                          |                          |                                    | 69   |      |       | 5.4 mA mode                                 |

| Supply Current during P                  | ower-Saving M            | odes                               |      | •    | •     |                                             |

| During Standby Mode                      | I <sub>STANDBY_AN</sub>  | _                                  | 84   | _    | mA    | Address $0x00<4:3>=1,1(2)$                  |

|                                          | I <sub>STANDBY_DIG</sub> | _                                  | 36   | _    |       |                                             |

| During Shutdown Mode                     | I <sub>DD SHDN</sub>     | _                                  | 23   | _    | mA    | Address $0x00<7,0>=1,1(3)$                  |

### TABLE 2-1: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all parameters apply for  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $AV_{DD18} = DV_{DD18} = 1.8V$ ,  $AV_{DD12} = DV_{DD12} = 1.2V$ , GND = 0V,  $SENSE = AV_{DD12}$ , Single-channel mode, Differential Analog Input  $(A_{IN}) = Sine$  wave with amplitude of -1 dBFS,  $f_{IN} = 70$  MHz, Clock Input = 200 MHz,  $f_S = 200$  Msps (ADC Core), Resolution = 16-bit, PLL and decimation filters are disabled, Output load: CMOS data pin = 10 pF,  $LVDS = 100\Omega$  termination, LVDS driver current setting = 3.5 mA,  $+25^{\circ}\text{C}$  is applied for typical value.

| Parameters                                                      | Sym.                      | Min. | Тур.                      | Max.               | Units | Conditions                                                          |  |  |  |