## mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **MCP3918**

### **3V Single-Channel Analog Front End**

#### Features:

- One 24-bit Resolution Delta-Sigma A/D Converter

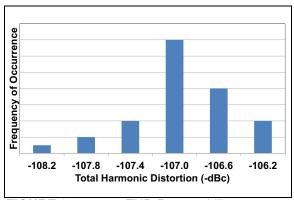

- 93.5 dB SINAD, -107 dBc Total Harmonic Distortion (THD) (up to 35<sup>th</sup> harmonic), 112 dB Spurious-Free Dynamic Range (SFDR)

- Flexible Serial Interface that Includes Both SPI and a Simple 2-Wire Interface Ideal for Polyphase Shunt Energy Meters

- Advanced Security Features:

- 16-bit Cyclic Redundancy Check (CRC) Checksum on All Communications for Secure Data Transfers

- 16-bit CRC Checksum and Interrupt Alert for Register-Map Configuration

- Register-Map Lock with 8-bit Secure Key

- 2.7V 3.6V AV<sub>DD</sub>, DV<sub>DD</sub>

- Programmable Data Rate, up to 125 ksps:

- 4 MHz Maximum Sampling Frequency

- 16 MHz Maximum Master Clock

- Oversampling Ratio, up to 4096

- Ultra Low-Power Shutdown Mode with < 10 μA

- Low-Drift 1.2V Internal Voltage Reference: 9 ppm/°C

- Differential Voltage Reference Input Pins

- High-Gain Programmable Gain Amplifier (PGA) (up to 32 V/V)

- Phase Delay Compensation with 1 µs Time Resolution

- Separate Data Ready Pin for Easy Synchronization

- Individual 24-bit Digital Offset and Gain Error Correction

- High-Speed 20 MHz SPI Interface with Mode 0,0 and 1,1 Compatibility

- Continuous Read/Write Modes for Minimum Communication with Dedicated 16-/32-bit Modes

- Available in 20-lead QFN and SSOP Packages

- Extended Temperature Range: -40°C to +125°C (all specifications are valid down to -45°C)

#### **Description:**

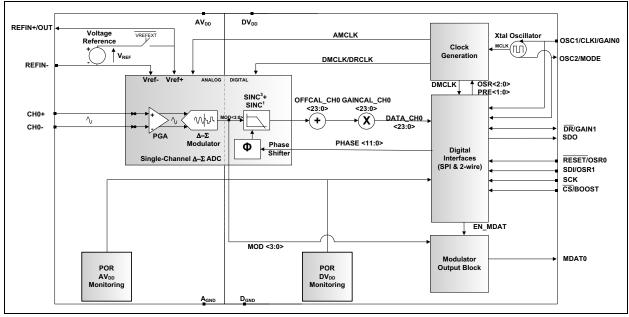

The MCP3918 is a 3V single-channel Analog Front End (AFE), containing one delta-sigma, Analog-to-Digital Converter (ADC), one programmable gain amplifier (PGA), phase delay compensation block, low-drift internal voltage reference, digital offset and gain errors calibration registers, and high-speed 20 MHz SPI-compatible serial interface.

The MCP3918 ADC is fully configurable with features such as: 16-/24-bit resolution, Oversampling Ratio (OSR) from 32 to 4096, gain from 1x to 32x, independent Shutdown and Reset, dithering and auto-zeroing. Communication is largely simplified with 8-bit commands, including various continuous read/write modes and 16-/24-/32-bit data formats that can be accessed by the Direct Memory Access (DMA) of an 8-/16-/32-bit MCU, and with the separate Data Ready pin that can be directly connected to an Interrupt Request (IRQ) input of an MCU.

The MCP3918 includes advanced security features to secure the communications and the configuration settings, such as a CRC-16 checksum on both serial data outputs and on the register-map static configuration. It also includes a register-map lock through an 8-bit password to avoid the processing of any unwanted write commands.

For polyphase shunt-based energy meters, the MCP3918 2-Wire serial interface greatly reduces system cost, requiring only a single bidirectional isolator per phase.

The MCP3918 is capable of interfacing a variety of voltage and current sensors, including shunts, current transformers, Rogowski coils and Hall effect sensors.

#### **Applications:**

- Single-Phase and Polyphase Energy Meters

- Energy Metering and Power Measurement

- Automotive

- Portable Instrumentation

- Medical and Power Monitoring

- Audio/Voice Recognition

- Isolator Sensor Application

## MCP3918

#### **Functional Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| V <sub>DD</sub>                                |                               |

|------------------------------------------------|-------------------------------|

| Digital inputs and outputs w.r.t. AGND         |                               |

| Analog input w.r.t. A <sub>GND</sub>           | 2V to +2V                     |

| V <sub>REF</sub> input w.r.t. A <sub>GND</sub> | 0.6V to V <sub>DD</sub> +0.6V |

| Storage temperature                            | 65°C to +150°C                |

| Ambient temp. with power applied               | 65°C to +125°C                |

| Soldering temperature of leads (10 secon       | nds)+300°C                    |

| ESD on the analog inputs (HBM, MM)             | 4.0 kV, 200V                  |

| ESD on all other pins (HBM, MM)                | 4.0 kV, 200V                  |

#### 1.1 Electrical Specifications

# **† Notice**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operational listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 1-1:ANALOG SPECIFICATIONS

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 3V$ , MCLK = 4 MHz; PRE<1:0> = 00; OSR = 256; GAIN = 1; VREFEXT = 0, CLKEXT = 1, DITHER<1:0> = 11; BOOST<1:0> = 10, V<sub>CM</sub> = 0V; T<sub>A</sub> = -40°C to +125°C (Note 1); V<sub>IN</sub> = 1.2 V<sub>PP</sub> = -0.5 dBFS @ 50/60 Hz on all channels.

| Characteristic                                  | Characteristic Sym.                   |           | Тур. | Max.      | Units  | Conditions                                                   |

|-------------------------------------------------|---------------------------------------|-----------|------|-----------|--------|--------------------------------------------------------------|

| ADC Performance                                 | •                                     |           |      | •         | •      | ·                                                            |

| Resolution<br>(No Missing Codes)                |                                       | 24        | —    | —         | bits   | OSR = 256 or greater                                         |

| Sampling Frequency                              | f <sub>S</sub> (DMCLK)                | —         | 1    | 4         | MHz    | For maximum condition,<br>BOOST<1:0> = 11                    |

| Output Data Rate                                | f <sub>D</sub> (DRCLK)                | —         | 4    | 125       | ksps   | For maximum condition,<br>BOOST<1:0> = 11,<br>OSR = 32       |

| Analog Input Absolute<br>Voltage on CH0+/- pins | CH0+/-                                | -1        | —    | +1        | V      | All analog input channels, measured to A <sub>GND</sub>      |

| Analog Input<br>Leakage Current                 | I <sub>IN</sub>                       | —         | +/-1 | —         | nA     | RESET<0> = 1,<br>MCLK running continuously                   |

| Differential Input<br>Voltage Range             | (CH <sub>0+</sub> -CH <sub>0-</sub> ) | -600/GAIN | _    | +600/GAIN | mV     | V <sub>REF</sub> = 1.2V,<br>proportional to V <sub>REF</sub> |

| Offset Error                                    | V <sub>OS</sub>                       | -1        | 0.2  | 1         | mV     | Note 5                                                       |

| Offset Error Drift                              |                                       | _         | 0.5  | _         | µV/°C  |                                                              |

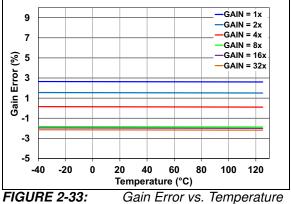

| Gain Error                                      | GE                                    | -4        | _    | +4        | %      | Note 5                                                       |

| Gain Error Drift                                |                                       |           | 1    | —         | ppm/°C |                                                              |

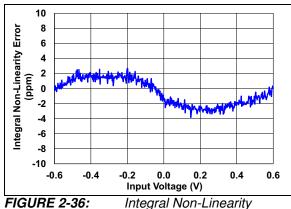

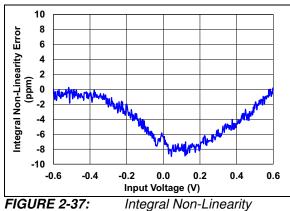

| Integral Non-Linearity                          | INL                                   | _         | 5    | _         | ppm    |                                                              |

Note 1: All specifications are valid down to -45°C.

- 2: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic Performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V @ 50/60 Hz. See Section 4.0 "Terminology and Formulas" for definition. This parameter is established by characterization and not 100% tested.

- **3:** For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 0, RESET<0> = 0, VREFEXT = 0, CLKEXT = 0.

- 4: For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 1, VREFEXT = 1, CLKEXT = 1.

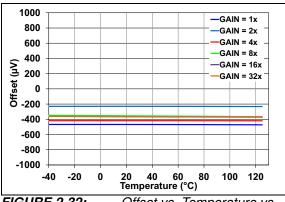

- 5: Applies to all gains. Offset and gain errors depend on the PGA gain setting. See Section 2.0 "Typical Performance Curves" for typical performance.

- 6: Outside this range, the ADC accuracy is not specified. An extended input range of +/-2V can be applied continuously to the part, with no damage.

- 7: For proper operation and for optimizing the ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2, as a function of the BOOST and PGA setting chosen. MCLK can take larger values as long as the prescaler settings (PRE<1:0>) limit AMCLK = MCLK/PRESCALE within the defined range in Table 5-2.

#### TABLE 1-1: ANALOG SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 3V$ , MCLK = 4 MHz; PRE<1:0> = 00; OSR = 256; GAIN = 1; VREFEXT = 0, CLKEXT = 1, DITHER<1:0> = 11; BOOST<1:0> = 10, V\_{CM} = 0V; T\_A = -40°C to +125°C (Note 1); V\_{IN} = 1.2 V\_{PP} = -0.5 dBFS @ 50/60 Hz on all channels.

| $V_{CM} = 0V$ , $T_A = -40$ C to +125 C (Note 1), $V_{IN} = 1.2$ $V_{PP} = -0.5$ dBFS @ 50/60 Hz off all challes. |                 |      |      |      |       |                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                                                    | Sym.            | Min. | Тур. | Max. | Units | Conditions                                                                                                                                                                    |

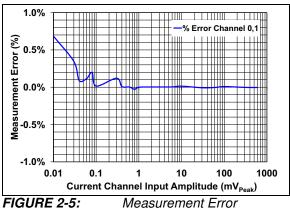

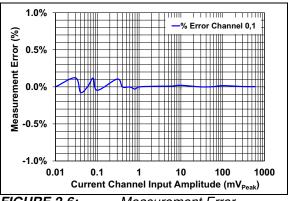

| Measurement Error                                                                                                 | ME              | _    | 0.1  | _    | %     | Measured with a 10,000:1<br>dynamic range (from<br>$600 \text{ mVPeak}$ to 6 $\mu$ VPeak),<br>$AV_{DD} = DV_{DD} = 3V$ ,<br>measurement points averaging<br>time: 20 seconds. |

| Differential Input                                                                                                | Z <sub>IN</sub> | 232  | —    |      | kΩ    | G = 1, proportional to 1/AMCLK                                                                                                                                                |

| Impedance                                                                                                         |                 | 142  | —    |      | kΩ    | G = 2, proportional to 1/AMCLK                                                                                                                                                |

|                                                                                                                   |                 | 72   | —    |      | kΩ    | G = 4, proportional to 1/AMCLK                                                                                                                                                |

|                                                                                                                   |                 | 38   | —    |      | kΩ    | G = 8, proportional to 1/AMCLK                                                                                                                                                |

|                                                                                                                   |                 | 36   | —    |      | kΩ    | G = 16, proportional to 1/AMCLK                                                                                                                                               |

|                                                                                                                   |                 | 33   | —    | _    | kΩ    | G = 32, proportional to 1/AMCLK                                                                                                                                               |

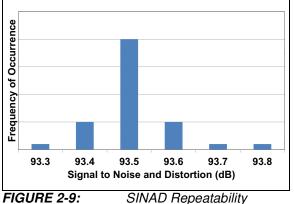

| Signal-to-Noise and<br>Distortion Ratio (Note 2)                                                                  | SINAD           | 92   | 93.5 | _    | dB    |                                                                                                                                                                               |

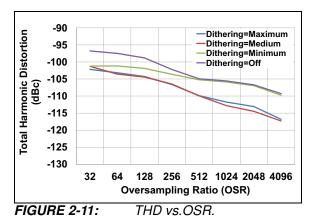

| Total Harmonic Distor-<br>tion (Note 2)                                                                           | THD             | _    | -107 | -103 | dBc   | Includes the first<br>35 harmonics                                                                                                                                            |

| Signal-to-Noise Ratio (Note 2)                                                                                    | SNR             | 92   | 94   | _    | dB    |                                                                                                                                                                               |

| Spurious-Free Dynamic<br>Range (Note 2)                                                                           | SFDR            | —    | 112  | _    | dBFS  |                                                                                                                                                                               |

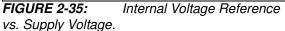

| AC Power Supply<br>Rejection                                                                                      | AC PSRR         | —    | -73  | _    | dB    | AV <sub>DD</sub> = DV <sub>DD</sub> = 3V + 0.6V <sub>PP</sub><br>50/60 Hz, 100/120 Hz                                                                                         |

| DC Power Supply<br>Rejection                                                                                      | DC PSRR         | —    | -73  | —    | dB    | $AV_{DD} = DV_{DD} = 2.7V$ to 3.6V                                                                                                                                            |

| DC Common Mode<br>Rejection                                                                                       | DC CMRR         | —    | -105 | _    | dB    | V <sub>CM</sub> from -1V to +1V                                                                                                                                               |

**Note 1:** All specifications are valid down to -45°C.

2: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic Performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V @ 50/60 Hz. See Section 4.0 "Terminology and Formulas" for definition. This parameter is established by characterization and not 100% tested.

**3:** For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 0, RESET<0> = 0, VREFEXT = 0, CLKEXT = 0.

4: For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 1, VREFEXT = 1, CLKEXT = 1.

5: Applies to all gains. Offset and gain errors depend on the PGA gain setting. See Section 2.0 "Typical Performance Curves" for typical performance.

6: Outside this range, the ADC accuracy is not specified. An extended input range of +/-2V can be applied continuously to the part, with no damage.

7: For proper operation and for optimizing the ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2, as a function of the BOOST and PGA setting chosen. MCLK can take larger values as long as the prescaler settings (PRE<1:0>) limit AMCLK = MCLK/PRESCALE within the defined range in Table 5-2.

#### TABLE 1-1: ANALOG SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 3V$ , MCLK = 4 MHz; PRE<1:0> = 00; OSR = 256; GAIN = 1; VREFEXT = 0, CLKEXT = 1, DITHER<1:0> = 11; BOOST<1:0> = 10, V\_{CM} = 0V; T\_A = -40°C to +125°C (Note 1); V\_{IN} = 1.2 V\_{PP} = -0.5 dBFS @ 50/60 Hz on all channels.

| Characteristic                                                               | Sym.                 | Min.                    | Тур. | Max.                    | Units  | Conditions                                                         |

|------------------------------------------------------------------------------|----------------------|-------------------------|------|-------------------------|--------|--------------------------------------------------------------------|

| Internal Voltage Reference                                                   | ce                   |                         |      |                         |        |                                                                    |

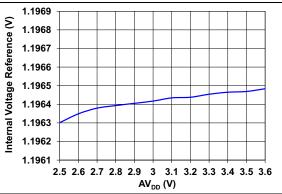

| Tolerance                                                                    | V <sub>REF</sub>     | 1.176                   | 1.2  | 1.224                   | V      | VREFEXT = 0,<br>T <sub>A</sub> = +25°C only                        |

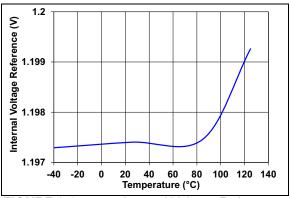

| Temperature Coefficient                                                      | TCV <sub>REF</sub>   | —                       | 9    | —                       | ppm/°C | T <sub>A</sub> = -40°C to +125°C,<br>VREFEXT = 0                   |

| Output Impedance                                                             | ZOUTV <sub>REF</sub> | —                       | 0.6  | —                       | kΩ     | VREFEXT = 0                                                        |

| Internal Voltage Refer-<br>ence Operating Current                            | $AI_{DD}V_{REF}$     | _                       | 54   | _                       | μA     | VREFEXT = 0,<br>SHUTDOWN<0> = 1                                    |

| Voltage Reference Input                                                      |                      |                         |      |                         |        |                                                                    |

| Input Capacitance                                                            |                      | —                       | —    | 10                      | pF     |                                                                    |

| Differential Input Voltage<br>Range (V <sub>REF+</sub> – V <sub>REF-</sub> ) | V <sub>REF</sub>     | 1.1                     | _    | 1.3                     | V      | VREFEXT = 1                                                        |

| Absolute Voltage<br>on REFIN+ pin                                            | V <sub>REF+</sub>    | V <sub>REF-</sub> + 1.1 | -    | V <sub>REF-</sub> + 1.3 | V      | VREFEXT = 1                                                        |

| Absolute Voltage<br>on REFIN- pin                                            | V <sub>REF-</sub>    | -0.1                    | _    | +0.1                    | V      | REFIN- should be connected to<br>A <sub>GND</sub> when VREFEXT = 0 |

| Master Clock Input                                                           |                      |                         |      | •                       | •      |                                                                    |

| Master Clock Input<br>Frequency Range                                        | f <sub>MCLK</sub>    |                         | _    | 20                      | MHz    | CLKEXT = 1 (Note 7)                                                |

| Crystal Oscillator<br>Operating Frequency<br>Range                           | f <sub>XTAL</sub>    | 1                       | _    | 20                      | MHz    | CLKEXT = 0 (Note 7)                                                |

| Analog Master Clock                                                          | AMCLK                | —                       |      | 16                      | MHz    | Note 7                                                             |

| Crystal Oscillator<br>Operating Current                                      | DIDDXTAL             | _                       | 80   | _                       | μA     | CLKEXT = 0                                                         |

| Power Supply                                                                 |                      |                         |      |                         |        |                                                                    |

| Operating Voltage, Analog                                                    | $AV_{DD}$            | 2.7                     | _    | 3.6                     | V      |                                                                    |

| Operating Voltage, Digital                                                   | $DV_DD$              | 2.7                     | —    | 3.6                     | V      |                                                                    |

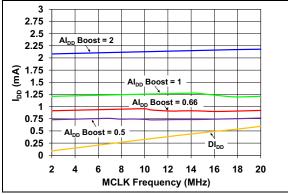

| OperatingCurrent, Analog                                                     | I <sub>DD,A</sub>    | —                       | 0.8  | 1                       | mA     | BOOST<1:0> = 00                                                    |

| (Note 3)                                                                     |                      |                         | 1    | 1.2                     | mA     | BOOST<1:0> = 01                                                    |

|                                                                              |                      |                         | 1.3  | 1.7                     | mA     | BOOST<1:0> = 10                                                    |

|                                                                              |                      |                         | 2.2  | 2.9                     | mA     | BOOST<1:0> = 11                                                    |

Note 1: All specifications are valid down to -45°C.

- 2: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic Performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V @ 50/60 Hz. See Section 4.0 "Terminology and Formulas" for definition. This parameter is established by characterization and not 100% tested.

- **3:** For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 0, RESET<0> = 0, VREFEXT = 0, CLKEXT = 0.

- 4: For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 1, VREFEXT = 1, CLKEXT = 1.

- 5: Applies to all gains. Offset and gain errors depend on the PGA gain setting. See Section 2.0 "Typical Performance Curves" for typical performance.

- 6: Outside this range, the ADC accuracy is not specified. An extended input range of +/-2V can be applied continuously to the part, with no damage.

- 7: For proper operation and for optimizing the ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2, as a function of the BOOST and PGA setting chosen. MCLK can take larger values as long as the prescaler settings (PRE<1:0>) limit AMCLK = MCLK/PRESCALE within the defined range in Table 5-2.

#### TABLE 1-1: ANALOG SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 3V$ , MCLK = 4 MHz; PRE<1:0> = 00; OSR = 256; GAIN = 1; VREFEXT = 0, CLKEXT = 1, DITHER<1:0> = 11; BOOST<1:0> = 10, V\_{CM} = 0V; T\_A = -40°C to +125°C (Note 1); V\_{IN} = 1.2 V\_{PP} = -0.5 dBFS @ 50/60 Hz on all channels.

|                                                           |                    | // IN        |      | •    |                                       |                                        |  |  |

|-----------------------------------------------------------|--------------------|--------------|------|------|---------------------------------------|----------------------------------------|--|--|

| Characteristic                                            | Sym.               | Min.         | Тур. | Max. | Units                                 | Conditions                             |  |  |

| Operating Current, Digital                                | I <sub>DD,D</sub>  | — 0.2 0.3 m/ |      | mA   | MCLK = 4 MHz,<br>proportional to MCLK |                                        |  |  |

|                                                           |                    | —            | 0.7  | —    | mA                                    | MCLK = 16 MHz,<br>proportional to MCLK |  |  |

| Shutdown Current, Analog                                  | I <sub>DDS,A</sub> | -            | _    | 1    | μA                                    | AV <sub>DD</sub> pin only (Note 4)     |  |  |

| Shutdown Current, Digital                                 | I <sub>DDS,D</sub> | -            | _    | 2    | μA                                    | DV <sub>DD</sub> pin only (Note 4)     |  |  |

| Pull-Down Current<br>on OSC2 Pin<br>(External Clock Mode) | I <sub>OSC2</sub>  | _            | 35   |      | μA                                    | CLKEXT = 1                             |  |  |

Note 1: All specifications are valid down to -45°C.

2: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic Performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V @ 50/60 Hz. See Section 4.0 "Terminology and Formulas" for definition. This parameter is established by characterization and not 100% tested.

- **3:** For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 0, RESET<0> = 0, VREFEXT = 0, CLKEXT = 0.

- 4: For these operating currents, the following configuration bit settings apply: SHUTDOWN<0> = 1, VREFEXT = 1, CLKEXT = 1.

- 5: Applies to all gains. Offset and gain errors depend on the PGA gain setting. See Section 2.0 "Typical Performance Curves" for typical performance.

- 6: Outside this range, the ADC accuracy is not specified. An extended input range of +/-2V can be applied continuously to the part, with no damage.

- 7: For proper operation and for optimizing the ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2, as a function of the BOOST and PGA setting chosen. MCLK can take larger values as long as the prescaler settings (PRE<1:0>) limit AMCLK = MCLK/PRESCALE within the defined range in Table 5-2.

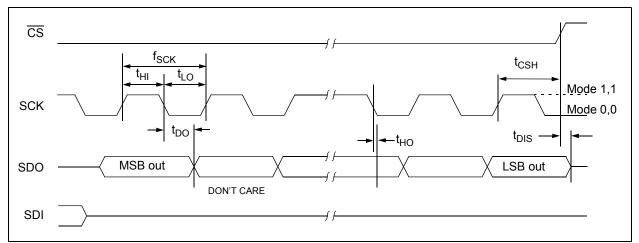

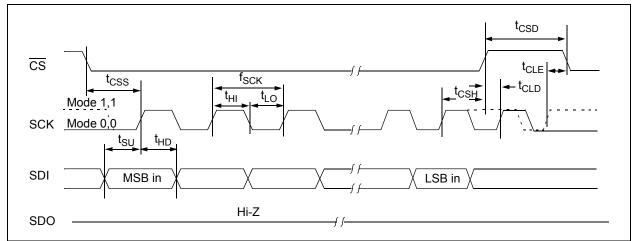

#### **1.2 Serial Interface Characteristics**

#### TABLE 1-2: SERIAL DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $DV_{DD} = 2.7$  to 3.6 V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  (**Note 1**),  $C_{LOAD} = 30$  pF, applies to all digital I/O.

| Characteristic                                   | Sym.             | Min.                   | Тур. | Max.                         | Units | Conditions                                                                                                 |

|--------------------------------------------------|------------------|------------------------|------|------------------------------|-------|------------------------------------------------------------------------------------------------------------|

| High-Level Input Voltage                         | V <sub>IH</sub>  | 0.7 DV <sub>DD</sub>   | —    | -                            | V     | Schmitt-Triggered                                                                                          |

| Low-Level Input Voltage                          | V <sub>IL</sub>  | —                      | —    | $0.3  \text{DV}_{\text{DD}}$ | V     | Schmitt-Triggered                                                                                          |

| Input Leakage Current                            | ILI              | —                      |      | ±1                           | μA    | $\overline{CS} = DV_{DD},$<br>$V_{IN} = D_{GND} \text{ to } DV_{DD}$                                       |

| Output Leakage Current                           | I <sub>LO</sub>  | _                      | _    | ±1                           | μA    | $\overline{\text{CS}} = \text{DV}_{\text{DD}},$<br>V <sub>OUT</sub> = D <sub>GND</sub> or DV <sub>DD</sub> |

| Hysteresis<br>of Schmitt-Triggered Inputs        | V <sub>HYS</sub> | —                      | 300  | —                            | mV    | DV <sub>DD</sub> = 3.3V only (Note 3)                                                                      |

| Low-Level Output Voltage                         | V <sub>OL</sub>  | _                      | _    | 0.4V                         | V     | I <sub>OL</sub> = +1.7 mA, DV <sub>DD</sub> = 3.3V                                                         |

| High-Level Output Voltage                        | V <sub>OH</sub>  | DV <sub>DD</sub> - 0.5 | —    | _                            | V     | I <sub>OH</sub> = -1.7 mA, DV <sub>DD</sub> = 3.3V                                                         |

| Internal Capacitance<br>(All Inputs and Outputs) | C <sub>INT</sub> |                        | _    | 7                            | pF    | T <sub>A</sub> = +25°C, SCK = 1.0 MHz,<br>DV <sub>DD</sub> = 3.3V ( <b>Note 2</b> )                        |

Note 1: All specifications are valid down to -45°C.

- 2: This parameter is periodically sampled and not 100% tested.

- **3:** This parameter is established by characterization and not production tested.

| <b>Electrical Specifications:</b> Unless otherwise indicated, all parameters apply at $DV_{DD}$ = 2.7 to 3.6 V, $T_A$ = -40°C to +125°C (Note 1), GAIN = 1, $C_{LOAD}$ = 30 pF. |                    |     |               |     |       |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|---------------|-----|-------|------------|

| Characteristic                                                                                                                                                                  | Sym                | Min | Тур           | Max | Units | Conditions |

| Serial Clock Frequency                                                                                                                                                          | f <sub>SCK</sub>   |     |               | 20  | MHz   |            |

| CS Setup Time                                                                                                                                                                   | t <sub>CSS</sub>   | 25  |               |     | ns    |            |

| CS Hold Time                                                                                                                                                                    | t <sub>CSH</sub>   | 50  | —             | _   | ns    |            |

| CS Disable Time                                                                                                                                                                 | t <sub>CSD</sub>   | 50  | —             | —   | ns    |            |

| Data Setup Time                                                                                                                                                                 | t <sub>SU</sub>    | 5   | _             | —   | ns    |            |

| Data Hold Time                                                                                                                                                                  | t <sub>HD</sub>    | 10  | _             | _   | ns    |            |

| Serial Clock High Time                                                                                                                                                          | t <sub>HI</sub>    | 20  | _             | _   | ns    |            |

| Serial Clock Low Time                                                                                                                                                           | t <sub>LO</sub>    | 20  | _             | _   | ns    |            |

| Serial Clock Delay Time                                                                                                                                                         | t <sub>CLD</sub>   | 50  | _             | _   | ns    |            |

| Serial Clock Enable Time                                                                                                                                                        | t <sub>CLE</sub>   | 50  | _             | _   | ns    |            |

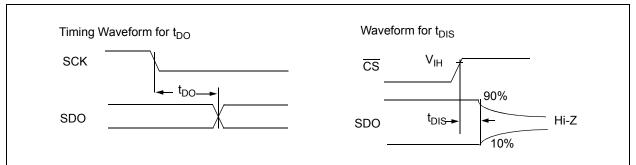

| Output Valid from SCK Low                                                                                                                                                       | t <sub>DO</sub>    |     | _             | 25  | ns    |            |

| Output Hold Time                                                                                                                                                                | t <sub>HO</sub>    | 0   | _             | _   | ns    |            |

| Output Disable Time                                                                                                                                                             | t <sub>DIS</sub>   | _   | _             | 25  | ns    |            |

| Reset Pulse Width (RESET)                                                                                                                                                       | t <sub>MCLR</sub>  | 100 | _             | _   | ns    |            |

| Data Transfer Time to DR<br>(Data Ready)                                                                                                                                        | t <sub>DODR</sub>  | _   | —             | 25  | ns    | Note 2     |

| Modulator Mode Entry to<br>Modulator Data Present                                                                                                                               | t <sub>MODSU</sub> |     | _             | 100 | ns    |            |

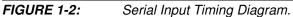

| Data Ready Pulse Low Time                                                                                                                                                       | t <sub>DRP</sub>   | _   | 1/(2 x DMCLK) |     | μs    |            |

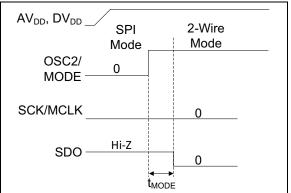

| 2-Wire Mode Enable Time                                                                                                                                                         | t <sub>MODE</sub>  |     |               | 50  | ns    |            |

| 2-Wire Mode<br>Watchdog Timer                                                                                                                                                   | t <sub>WATCH</sub> | 3.5 | _             | 35  | μs    |            |

#### TABLE 1-3: SERIAL AC CHARACTERISTICS

**Note 1:** All specifications are valid down to -45°C.

2: This parameter is established by characterization and not production tested.

#### TABLE 1-4: TEMPERATURE SPECIFICATIONS

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = 2.7$  to 3.6V,  $DV_{DD} = 2.7$  to 3.6V.

| D V DD - 2.7 to 0.0 V.          | DVDD - 2.1 (0 0.0 V. |      |      |      |       |                |

|---------------------------------|----------------------|------|------|------|-------|----------------|

| Parameters                      | Sym.                 | Min. | Тур. | Max. | Units | Conditions     |

| Temperature Ranges              |                      |      |      |      |       |                |

| Operating Temperature Range     | T <sub>A</sub>       | -40  | _    | +125 | °C    | Note 1, Note 2 |

| Storage Temperature Range       | T <sub>A</sub>       | -65  | _    | +150 | °C    |                |

| Thermal Package Resistances     |                      |      |      |      |       |                |

| Thermal Resistance, 20L 4x4 QFN | $\theta_{JA}$        | —    | 46.2 | —    | °C/W  |                |

| Thermal Resistance, 20L SSOP    | $\theta_{JA}$        | _    | 87.3 | —    | °C/W  |                |

|                                 |                      |      |      | •    |       |                |

**Note 1:** The internal junction temperature  $(T_J)$  must not exceed the absolute maximum specification of +150°C.

2: All specifications are valid down to -45°C.

## MCP3918

FIGURE 1-4:

Timing Diagrams, continued.

**FIGURE 1-5:** Entering 2-Wire Interface Mode Timing Diagram.

NOTES:

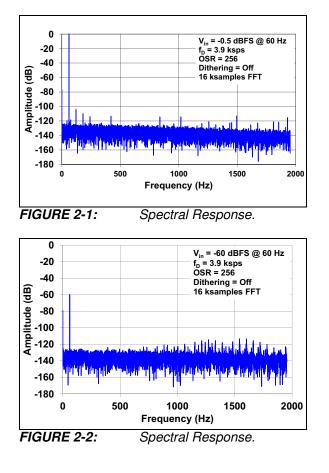

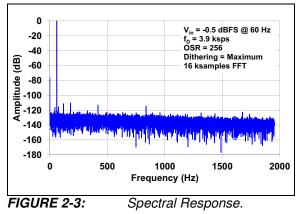

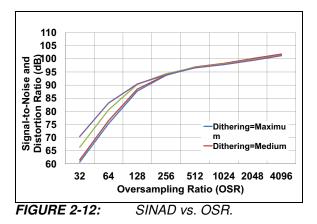

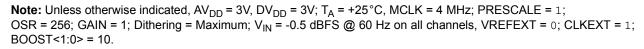

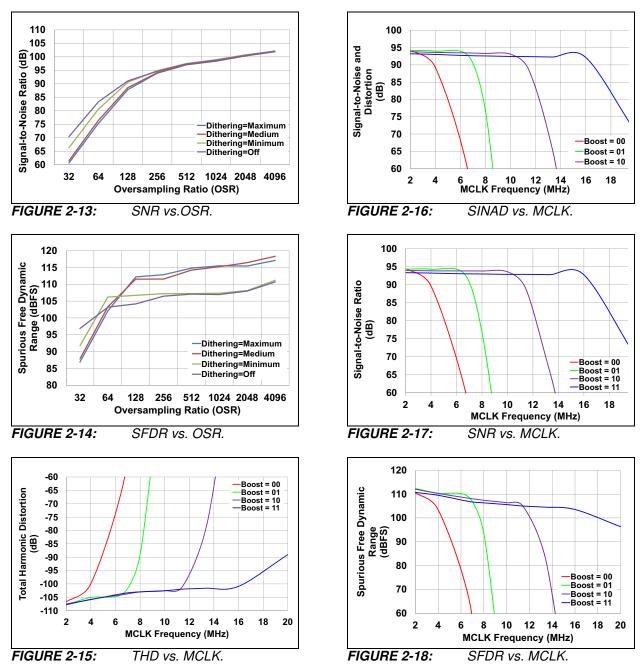

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

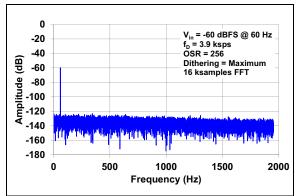

FIGURE 2-4: Spectral Response.

with 1-Point Calibration.

FIGURE 2-6: Measurement Error with 2-Point Calibration.

FIGURE 2-7: THD Repeatability Histogram.

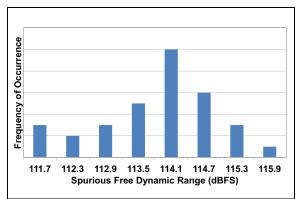

FIGURE 2-8: Spurious-Free Dynamic Range Repeatability Histogram.

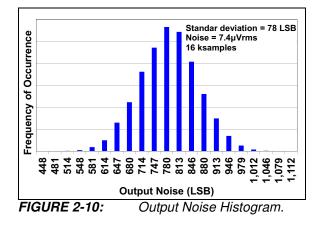

Histogram.

## MCP3918

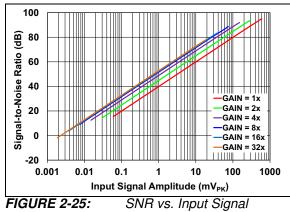

Amplitude.

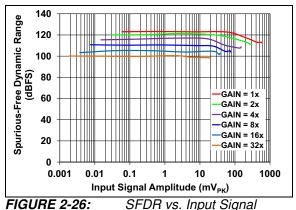

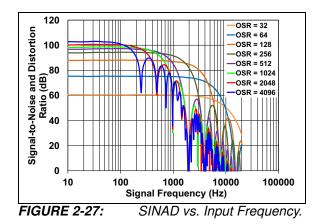

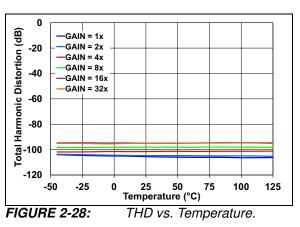

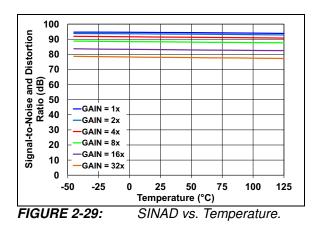

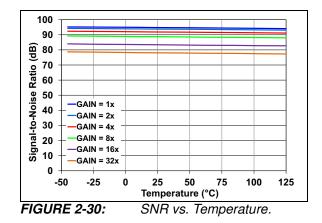

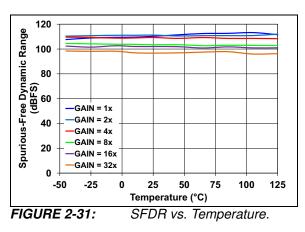

**Note:** Unless otherwise indicated,  $AV_{DD} = 3V$ ,  $DV_{DD} = 3V$ ;  $T_A = +25$ °C, MCLK = 4 MHz; PRESCALE = 1; OSR = 256; GAIN = 1; Dithering = Maximum;  $V_{IN} = -0.5$  dBFS @ 60 Hz on all channels, VREFEXT = 0; CLKEXT = 1; BOOST<1:0> = 10.

Amplitude.

Amplitude.

FIGURE 2-32: Offset vs. Temperature vs. Gain.

vs. Gain.

**FIGURE 2-34:** Internal Voltage Reference vs. Temperature.

(Dithering Maximum).

**Note:** Unless otherwise indicated,  $AV_{DD} = 3V$ ,  $DV_{DD} = 3V$ ;  $T_A = +25$  °C, MCLK = 4 MHz; PRESCALE = 1; OSR = 256; GAIN = 1; Dithering = Maximum;  $V_{IN} = -0.5$  dBFS @ 60 Hz on all channels, VREFEXT = 0; CLKEXT = 1; BOOST<1:0> = 10.

(Dithering Off).

**FIGURE 2-38:** Operating Current vs. MCLK Frequency vs. Boost, V<sub>DD</sub> = 3.0V.

NOTES:

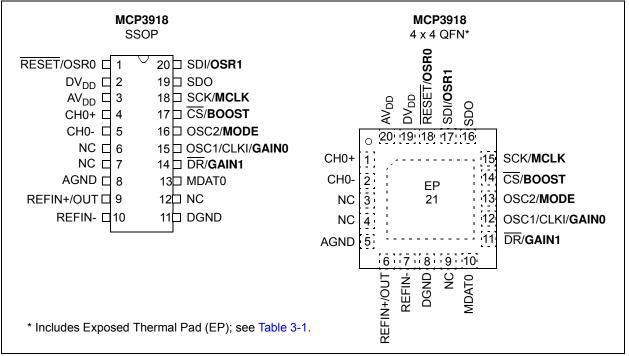

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

| MCP3918<br>SSOP | MCP3918<br>QFN | Symbol           | Function                                                                               |

|-----------------|----------------|------------------|----------------------------------------------------------------------------------------|

| 1               | 18             | RESET/OSR0       | Master Reset Logic Input Pin or OSR0 Logic Input Pin                                   |

| 2               | 19             | DV <sub>DD</sub> | Digital Power Supply Pin                                                               |

| 3               | 20             | AV <sub>DD</sub> | Analog Power Supply Pin                                                                |

| 4               | 1              | CH0+             | Non-Inverting Analog Input Pin for Channel 0                                           |

| 5               | 2              | CH0-             | Inverting Analog Input Pin for Channel 0                                               |

| 6               | 3              | NC               | Not connected                                                                          |

| 7               | 4              | NC               | Not connected                                                                          |

| 8               | 5              | A <sub>GND</sub> | Analog Ground Pin, Return Path for internal analog circuitry                           |

| 9               | 6              | REFIN+/OUT       | Non-Inverting Voltage Reference Input and Internal Reference<br>Output Pin             |

| 10              | 7              | REFIN-           | Inverting Voltage Reference Input Pin                                                  |

| 11              | 8              | D <sub>GND</sub> | Digital Ground Pin, Return Path for internal digital circuitry                         |

| 12              | 9              | NC               | Not connected                                                                          |

| 13              | 10             | MDAT0            | Modulator Data Output Pin for Channel 0                                                |

| 14              | 11             | DR/GAIN1         | Data Ready Signal Output Pin or GAIN1 Logic Input Pin                                  |

| 15              | 12             | OSC1/CLKI/GAIN0  | Oscillator Crystal Connection Pin or External Clock Input Pin or GAIN0 Logic Input Pin |

| 16              | 13             | OSC2/MODE        | Oscillator Crystal Connection Input Pin or Serial Interface Mode<br>Logic Input Pin    |

| 17              | 14             | CS/BOOST         | Serial Interface Chip Select Input Pin or BOOST Logic Input Pin                        |

| 18              | 15             | SCK/MCLK         | Serial Interface Clock Pin or Master Clock Input Pin                                   |

| 19              | 16             | SDO              | Serial Interface Data Input Pin                                                        |

| 20              | 17             | SDI/OSR1         | Serial Interface Data Input Pin or OSR1 Logic Input Pin                                |

| _               | 21             | EP               | Exposed Thermal Pad                                                                    |

#### 3.1 <u>Master Reset/OSR0 Logic Input</u> (RESET/OSR0)

In SPI mode, this pin is active low and places the entire chip in a Reset state when active.

When RESET is logic low, all registers are reset to their default value, no communication can take place, and no clock is distributed inside the part, except in the input structure if MCLK is applied (if MCLK is idle, then no clock is distributed). This state is equivalent to a Power-On Reset (POR) state.

Since the default state of the ADC is on, the analog power consumption when RESET is logic low is equivalent to when RESET is logic high. Only the digital power consumption is largely reduced because this current consumption is essentially dynamic and is reduced drastically when there is no clock running. If MCLK is applied when RESET is logic low, all the analog biases are enabled during a reset, so that the part is fully operational just after a RESET rising edge. If MCLK is not applied, there is a time after a hard reset when the conversion may not accurately correspond to the start-up of the input structure.

This input is Schmitt-triggered.

In 2-Wire Interface mode, this is the OSR0 logic select pin (see Section 7.0 "2-Wire Serial Interface Description" for the logic input table for OSR0 and OSR1). The pin state is latched when the MODE changes to 2-Wire Interface mode, and is relatched at each watchdog timer reset.

#### 3.2 Digital V<sub>DD</sub> (DV<sub>DD</sub>)

$DV_{DD}$  is the power supply voltage for the digital circuitry within the MCP3918. For optimal performance, it is recommended to connect appropriate bypass capacitors (typically a 10  $\mu F$  in parallel with a 0.1  $\mu F$  ceramic).  $DV_{DD}$  should be maintained between 2.7V and 3.6V for specified operation.

#### 3.3 Analog Power Supply (AV<sub>DD</sub>)

$AV_{DD}$  is the power supply voltage for the analog circuitry within the MCP3918. It is recommended to connect appropriate bypass capacitors (typically a 10  $\mu F$  in parallel with a 0.1  $\mu F$  ceramic).  $AV_{DD}$  should be maintained between 2.7V and 3.6V for specified operation.

#### 3.4 ADC Differential Analog Inputs (CH0+/CH0-)

The CH0+/- pins are the fully differential analog voltage inputs for the delta-sigma ADC.

The linear and specified region of the channels is dependent on the PGA gain. This region corresponds to a differential voltage range of  $\pm 600 \text{ mV/GAIN}$  with V<sub>REF</sub> = 1.2V.

The maximum absolute voltage, with respect to  $A_{GND}$ , for each CH0+/- input pin is ±1V with no distortion and ±2V with no breaking after continuous voltage. This maximum absolute voltage is not proportional to the  $V_{REF}$  voltage.

#### 3.5 Analog Ground (A<sub>GND</sub>)

$A_{GND}$  is the ground reference voltage for the analog circuitry within the MCP3918. For optimal performance, it is recommended to connect it to the same ground node voltage as  $D_{GND}$ , preferably with a star connection.

If an analog ground plane is available, it is recommended that these pins be tied to this plane of the Printed Circuit Board (PCB). This plane should also reference all other analog circuitry in the system.

#### 3.6 Non-Inverting Reference Input, Internal Reference Output (REFIN+/OUT)

This pin is the non-inverting side of the differential voltage reference input for the ADC or the internal voltage reference output.

When VREFEXT = 1, an external voltage reference source can be used, and the internal voltage reference is disabled. When using an external differential voltage reference, it should be connected to its  $V_{REF+}$  pin. When using an external single-ended reference, it should be connected to this pin.

When VREFEXT = 0, the internal voltage reference is enabled and connected to this pin through a switch. This voltage reference has minimal drive capability and thus needs proper buffering and bypass capacitances (a 0.1  $\mu$ F ceramic capacitor is sufficient in most cases), if used as a voltage source.

If the voltage reference is only used as an internal  $V_{REF}$ , adding bypass capacitance on REFIN+/OUT is not necessary for keeping ADC accuracy, but a minimal 0.1 µF ceramic capacitance can be connected to avoid EMI/EMC susceptibility issues due to the antenna created by the REFIN+/OUT pin if left floating.

#### 3.7 Inverting Reference Input (REFIN-)

This pin is the inverting side of the differential voltage reference input for the ADC. When using an external differential voltage reference, it should be connected to its  $V_{REF-}$  pin. When using an external single-ended voltage reference, or when VREFEXT = 0 (default) and using the internal voltage reference, the pin should be directly connected to  $A_{GND}$ .

#### 3.8 Digital Ground Connection (D<sub>GND</sub>)

$\mathsf{D}_{\mathsf{GND}}$  is the ground reference voltage for the digital circuitry within the MCP3918. For optimal performance, it is recommended to connect it to the same ground node voltage as  $\mathsf{A}_{\mathsf{GND}}$ , preferably with a star connection.

If a digital ground plane is available, it is recommended that this pin be tied to this plane of the PCB. This plane should also reference all other digital circuitry in the system.

## 3.9 Modulator Output (MDAT0)

MDAT0 is the output pin for the modulator serial bit streams of the ADC. This pin is high-impedance when the EN MDAT bit is logic low. When the EN MDAT bit is enabled, the modulator bit stream of the ADC is present on the pin and updated at the AMCLK frequency (see Section 5.3.5 "Modulator Output **Block**" for a complete description of the modulator output). This pin can be directly connected to an MCU or a DSP when a specific digital filtering is needed. When the MDAT0 output pin is enabled, the DR output is disabled. In 2-Wire Interface mode, this pin is automatically inactive. Its state is high-impedance during the 2-Wire mode (therefore this pin can be left grounded in applications using exclusively the 2-Wire Interface mode; this configuration improves the EMI/EMC susceptibility of the device).

#### 3.10 Data R<u>eady</u> Output/GAIN1 Logic Input (DR/GAIN1)

In SPI mode, the Data Ready pin indicates if a new conversion result is ready to be read. The default state of this pin is logic high when  $DR_HIZ = 1$  and is high-impedance when  $DR_HIZ = 0$  (default). After each conversion is finished, a logic low pulse will take place on the Data Ready pin to indicate the conversion result is ready as an interrupt. This pulse is synchronous with the master clock and has a defined and constant width.

The Data Ready pin is independent from the SPI interface and acts like an interrupt output. The Data Ready pin state is not latched, and the pulse width (and period) are both determined by the MCLK frequency, oversampling rate, and internal clock prescale settings. The Data Ready pulse width is equal to half a DMCLK period and the frequency of the pulses is equal to DRCLK (see Figure 1-3).

In 2-Wire Interface mode, this is the GAIN1 logic select pin. See Section 7.0 "2-Wire Serial Interface Description" for the logic input table for GAIN0 and GAIN1. The pin state is latched when the MODE changes to 2-Wire Interface mode, and is relatched at each watchdog timer reset.

Note: This pin should not be left floating when the DR\_HIZ bit is low; a 100 kΩ pull-up resistor connected to DV<sub>DD</sub> is recommended.

#### 3.11 Crystal Oscillator/Master Clock Input/GAIN0 Logic Input (OSC1/CLKI/GAIN0)

In SPI mode, OSC1/CLKI and OSC2 provide the master clock for the device. When CLKEXT = 0, a resonant crystal or clock source with a similar sinusoidal waveform must be placed across the OSC1 and OSC2 pins to ensure proper operation.

The typical clock frequency specified is 4 MHz. For proper operation and in order to optimize ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2 for the function of the BOOST and PGA setting chosen. MCLK can take larger values as long as the prescaler settings (PRE<1:0>) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-2. Appropriate load capacitance should be connected to these pins for proper operation.

In 2-Wire Interface mode, this is the GAIN0 logic select pin. See Section 7.0 "2-Wire Serial Interface Description" for the logic input table for GAIN0 and GAIN1. The pin state is latched when the MODE changes to 2-Wire Interface mode, and is relatched at each watchdog timer reset.

Note: When CLKEXT = 1, the crystal oscillator is disabled. OSC1 becomes the master clock input CLKI, a direct path for an external clock source. One example would be a clock source generated by an MCU.

#### 3.12 Crystal Oscillator Output/ Interface MODE Logic Input (OSC2/MODE)

When CLKEXT = 0 (default), a resonant crystal or clock source with a similar sinusoidal waveform must be placed across the OSC1 and OSC2 pins to ensure proper operation. Appropriate load capacitance should be connected to these pins for proper operation.

When CLKEXT = 1 (default condition at POR), this pin is the MODE selection pin for the digital interface. When MODE is logic low, the SPI interface is selected (see Section 6.0 "SPI Serial Interface Description"). When MODE is logic high, the 2-Wire interface is selected (see Section 7.0 "2-Wire Serial Interface Description"). The MODE input is latched after a POR, a Master Reset and/or a Watchdog Timer Reset.

#### 3.13 Chip Select/ Boost Logic Input (CS/BOOST)

In SPI mode, this pin is the SPI chip select that enables serial communication. When this pin is logic high, no communication can take place. A chip select falling edge initiates serial communication, and a chip select rising edge terminates the communication. No communication can take place even when  $\overline{CS}$  is logic low, if  $\overline{RESET}$  is also logic low.

This input is Schmitt-triggered.

In the 2-Wire Interface mode, this is the Boost logic select pin. See Section 7.0 "2-Wire Serial Interface Description" for the logic input table for Boost. The pin state is latched when the mode changes to 2-Wire Interface mode, and is re-latched at each watchdog timer reset.

#### 3.14 Serial Data Clock/ Master Clock Input (SCK/MCLK)

In SPI mode, this is the serial clock pin for SPI communication. Data is clocked into the device on the rising edge of SCK. Data is clocked out of the device on the falling edge of SCK.

The MCP3918 SPI interface is compatible with SPI 0,0 and 1,1 modes. SPI modes can be changed during a  $\overline{\text{CS}}$  high time.

The maximum clock speed specified is 20 MHz. SCK and MCLK are two different and asynchronous clocks; SCK is only required when a communication happens, while MCLK is continuously required when the part is converting analog inputs.

This input is Schmitt-triggered.

In the 2-Wire Interface mode, this pin is defining the master clock of the device (MCLK) and the serial clock (SCK) for the interface simultaneously. In this mode, the clock has to be provided continuously to ensure proper operation. See **Section 7.0** "2-Wire Serial **Interface Description**" for more information and timing diagrams of the 2-Wire interface protocol.

#### 3.15 Serial Data Output (SDO)

This is the SPI data output pin. Data is clocked out of the device on the falling edge of SCK.

This pin remains in a high-impedance state during the command byte. It also stays high-impedance during the entire communication for Write commands and when the CS pin is logic high or when the RESET pin is logic low. This pin is active only when a Read command is processed. The interface is half-duplex (inputs and outputs do not happen at the same time).

In the 2-Wire Interface Mode, this pin is the only digital output pin, and sends synchronous frames at each data ready with data bits clocked out on the falling edge of SCK.

#### 3.16 Serial Data/OSR1 Logic Input (SDI/OSR1)

In SPI mode, this is the SPI data input pin. Data is clocked into the device on the rising edge of SCK. When  $\overline{CS}$  is logic low, this pin is used to communicate with 8-bit commands followed by data bytes that can be 16-/24- or 32-bit wide. The interface is half-duplex (inputs and outputs do not happen at the same time).

Each communication starts with a chip select falling edge followed by an 8-bit command word, entered through the SDI pin. Each command is either a Read or a Write command. Toggling SDI during a Read command has no effect.

This input is Schmitt-triggered.

In 2-Wire Interface mode, this is the OSR1 logic select pin. See **Section 7.0 "2-Wire Serial Interface Description**" for the logic input table for OSR0 and OSR1. The pin state is latched when the mode changes to 2-Wire Interface Mode, and is relatched at each watchdog timer reset.

#### 3.17 Exposed Pad (EP)

Exposed Thermal Pad. This pin must be connected to  $A_{GND}$  for optimal accuracy and thermal performance. This pad can also be left floating if necessary. Connecting it to  $A_{GND}$  is preferable for the lowest noise performance and best thermal behavior.

#### 4.0 **TERMINOLOGY AND** FORMULAS

This section defines the terms and formulas used throughout this data sheet. The following terms are defined:

- MCLK Master Clock

- AMCLK Analog Master Clock

- DMCLK Digital Master Clock

- DRCLK Data Rate Clock

- OSR Oversampling Ratio

- Offset Error

- Gain Error

- Integral Non-Linearity Error

- Signal-to-Noise Ratio (SNR)

- Signal-to-Noise and Distortion Ratio (SINAD)

- Total Harmonic Distortion (THD)

- Spurious-Free Dynamic Range (SFDR)

- MCP3918 Delta-Sigma Architecture

- Idle Tones

- Dithering

- PSRR

- CMRR

- ADC Reset Mode

- Hard Reset Mode (RESET = 0)

- ADC Shutdown Mode

- Full Shutdown Mode

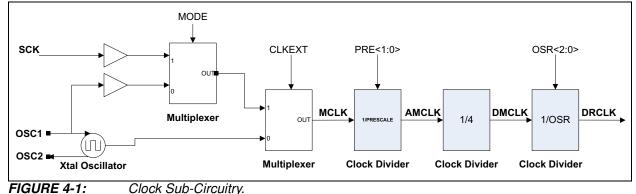

#### MCLK – Master Clock 4.1

This is the fastest clock present on the device. This is the frequency of the crystal placed at the OSC1/OSC2 inputs when CLKEXT = 0 or the frequency of the clock input at the OSC1/CLKI when CLKEXT = 1. In the 2-Wire mode, this is the frequency present at the SCK input pin. See Figure 4-1.

#### 4.2 AMCLK – Analog Master Clock

AMCLK is the clock frequency that is present on the analog portion of the device, after prescaling has occurred via the PRE<1:0> bits in the CONFIG0 register (see Equation 4-1). The analog portion includes the PGA and one delta-sigma modulator.

#### EQUATION 4-1:

| AMCLK = | MCLK     |

|---------|----------|

| AMCLK - | PRESCALE |

#### **TABLE 4-1:** MCP3918 OVERSAMPLING **RATIO SETTINGS**

| CON | IFIG0 | Analog Master Clock      |  |  |  |

|-----|-------|--------------------------|--|--|--|

| PRE | <1:0> | Prescale                 |  |  |  |

| 0   | 0     | AMCLK = MCLK/1 (default) |  |  |  |

| 0   | 1     | AMCLK = MCLK/2           |  |  |  |

| 1   | 0     | AMCLK = MCLK/4           |  |  |  |

| 1   | 1     | AMCLK = MCLK/8           |  |  |  |

FIGURE 4-1:

#### 4.3 DMCLK – Digital Master Clock

This is the clock frequency that is present on the digital portion of the device, after prescaling and division by four (Equation 4-2). This is also the sampling frequency, which is the rate at which the modulator outputs are refreshed. Each period of this clock corresponds to one sample and one modulator output. See Figure 4-1.

#### **EQUATION 4-2:**

$$DMCLK = \frac{AMCLK}{4} = \frac{MCLK}{4 \times PRESCALE}$$

#### DRCLK – Data Rate Clock 4.4

This is the output data rate, i.e. the rate at which the ADC outputs new data. Each new data is signaled by a Data Ready pulse on the Data Ready pin.

This data rate is dependent on the OSR and the prescaler with the formula in Equation 4-3.

#### **EQUATION 4-3:**

$$DRCLK = \frac{DMCLK}{OSR} = \frac{AMCLK}{4 \times OSR} = \frac{MCLK}{4 \times OSR \times PRESCALE}$$

Since this is the output data rate, and because the decimation filter is a sinc (or notch) filter, there is a notch in the filter transfer function at each integer multiple of this rate.

Table 4-2 describes the various combinations of OSR and PRESCALE, and their associated AMCLK, DMCLK and DRCLK rates.

| <b>TABLE 4-2:</b> | DEVICE DATA RATES IN FUNCTION OF MCLK, OSR AND PRESCALE, |

|-------------------|----------------------------------------------------------|

|                   | MCLK = 4 MHZ                                             |

| PRE<1:0> |   | OSR<2:0> |   | OSR | AMCLK | DMCLK  | DRCLK   | DRCLK<br>(ksps) | SINAD<br>(dB)<br>Note 1 | ENOB<br>from<br>SINAD<br>(bits)<br>Note 1 |      |

|----------|---|----------|---|-----|-------|--------|---------|-----------------|-------------------------|-------------------------------------------|------|

| 1        | 1 | 1        | 1 | 1   | 4096  | MCLK/8 | MCLK/32 | MCLK/131072     | 0.035                   | 102.5                                     | 16.7 |

| 1        | 1 | 1        | 1 | 0   | 2048  | MCLK/8 | MCLK/32 | MCLK/65536      | 0.061                   | 100                                       | 16.3 |

| 1        | 1 | 1        | 0 | 1   | 1024  | MCLK/8 | MCLK/32 | MCLK/32768      | 0.122                   | 97                                        | 15.8 |

| 1        | 1 | 1        | 0 | 0   | 512   | MCLK/8 | MCLK/32 | MCLK/16384      | 0.244                   | 96                                        | 15.6 |

| 1        | 1 | 0        | 1 | 1   | 256   | MCLK/8 | MCLK/32 | MCLK/8192       | 0.488                   | 95                                        | 15.5 |

| 1        | 1 | 0        | 1 | 0   | 128   | MCLK/8 | MCLK/32 | MCLK/4096       | 0.976                   | 90                                        | 14.7 |

| 1        | 1 | 0        | 0 | 1   | 64    | MCLK/8 | MCLK/32 | MCLK/2048       | 1.95                    | 83                                        | 13.5 |

| 1        | 1 | 0        | 0 | 0   | 32    | MCLK/8 | MCLK/32 | MCLK/1024       | 3.9                     | 70                                        | 11.3 |

| 1        | 0 | 1        | 1 | 1   | 4096  | MCLK/4 | MCLK/16 | MCLK/65536      | 0.061                   | 102.5                                     | 16.7 |

| 1        | 0 | 1        | 1 | 0   | 2048  | MCLK/4 | MCLK/16 | MCLK/32768      | 0.122                   | 100                                       | 16.3 |

| 1        | 0 | 1        | 0 | 1   | 1024  | MCLK/4 | MCLK/16 | MCLK/16384      | 0.244                   | 97                                        | 15.8 |

| 1        | 0 | 1        | 0 | 0   | 512   | MCLK/4 | MCLK/16 | MCLK/8192       | 0.488                   | 96                                        | 15.6 |

| 1        | 0 | 0        | 1 | 1   | 256   | MCLK/4 | MCLK/16 | MCLK/4096       | 0.976                   | 95                                        | 15.5 |

| 1        | 0 | 0        | 1 | 0   | 128   | MCLK/4 | MCLK/16 | MCLK/2048       | 1.95                    | 90                                        | 14.7 |

| 1        | 0 | 0        | 0 | 1   | 64    | MCLK/4 | MCLK/16 | MCLK/1024       | 3.9                     | 83                                        | 13.5 |

| 1        | 0 | 0        | 0 | 0   | 32    | MCLK/4 | MCLK/16 | MCLK/512        | 7.8125                  | 70                                        | 11.3 |

| 0        | 1 | 1        | 1 | 1   | 4096  | MCLK/2 | MCLK/8  | MCLK/32768      | 0.122                   | 102.5                                     | 16.7 |

| 0        | 1 | 1        | 1 | 0   | 2048  | MCLK/2 | MCLK/8  | MCLK/16384      | 0.244                   | 100                                       | 16.3 |

| 0        | 1 | 1        | 0 | 1   | 1024  | MCLK/2 | MCLK/8  | MCLK/8192       | 0.488                   | 97                                        | 15.8 |

| 0        | 1 | 1        | 0 | 0   | 512   | MCLK/2 | MCLK/8  | MCLK/4096       | 0.976                   | 96                                        | 15.6 |

| 0        | 1 | 0        | 1 | 1   | 256   | MCLK/2 | MCLK/8  | MCLK/2048       | 1.95                    | 95                                        | 15.5 |

| 0        | 1 | 0        | 1 | 0   | 128   | MCLK/2 | MCLK/8  | MCLK/1024       | 3.9                     | 90                                        | 14.7 |

| 0        | 1 | 0        | 0 | 1   | 64    | MCLK/2 | MCLK/8  | MCLK/512        | 7.8125                  | 83                                        | 13.5 |

| 0        | 1 | 0        | 0 | 0   | 32    | MCLK/2 | MCLK/8  | MCLK/256        | 15.625                  | 70                                        | 11.3 |

| 0        | 0 | 1        | 1 | 1   | 4096  | MCLK   | MCLK/4  | MCLK/16384      | 0.244                   | 102.5                                     | 16.7 |

| 0        | 0 | 1        | 1 | 0   | 2048  | MCLK   | MCLK/4  | MCLK/8192       | 0.488                   | 100                                       | 16.3 |

| 0        | 0 | 1        | 0 | 1   | 1024  | MCLK   | MCLK/4  | MCLK/4096       | 0.976                   | 97                                        | 15.8 |

| 0        | 0 | 1        | 0 | 0   | 512   | MCLK   | MCLK/4  | MCLK/2048       | 1.95                    | 96                                        | 15.6 |

| 0        | 0 | 0        | 1 | 1   | 256   | MCLK   | MCLK/4  | MCLK/1024       | 3.9                     | 95                                        | 15.5 |

| 0        | 0 | 0        | 1 | 0   | 128   | MCLK   | MCLK/4  | MCLK/512        | 7.8125                  | 90                                        | 14.7 |

| 0        | 0 | 0        | 0 | 1   | 64    | MCLK   | MCLK/4  | MCLK/256        | 15.625                  | 83                                        | 13.5 |

| 0        | 0 | 0        | 0 | 0   | 32    | MCLK   | MCLK/4  | MCLK/128        | 31.25                   | 70                                        | 11.3 |

Note 1: For OSR = 32 and 64, DITHER = None. For OSR = 128 and higher, DITHER = Maximum. The SINAD values are given for GAIN = 1.

#### 4.5 OSR – Oversampling Ratio

This is the ratio of the sampling frequency to the output data rate: OSR = DMCLK/DRCLK. The default OSR is 256, with MCLK = 4 MHz, PRESCALE = 1, AMCLK = 4 MHz,  $f_S = 1$  MHz, and  $f_D = 3.90625$  ksps. The bits in Table 4-3, available in the CONFIG0 register, are used to change the oversampling ratio (OSR).

TABLE 4-3: MCP3918 OVERSAMPLING RATIO SETTINGS

|   | CONFIG  | 0 | Oversampling Ratio |  |  |

|---|---------|---|--------------------|--|--|

|   | OSR<2:0 | > | (OSR)              |  |  |

| 0 | 0       | 0 | 32                 |  |  |

| 0 | 0       | 1 | 64                 |  |  |

| 0 | 1       | 0 | 128                |  |  |

| 0 | 1       | 1 | 256 (Default)      |  |  |

| 1 | 0       | 0 | 512                |  |  |

| 1 | 0       | 1 | 1024               |  |  |

| 1 | 1       | 0 | 2048               |  |  |

| 1 | 1       | 1 | 4096               |  |  |

#### 4.6 Offset Error

This is the error induced by the ADC when the inputs are shorted together ( $V_{IN} = 0V$ ). The specification incorporates both PGA and ADC offset contributions. This error varies with PGA and OSR settings. The offset is different on each channel and varies from chip to chip. The offset is specified in  $\mu V$ . The offset error can be digitally compensated independently on each channel through the OFFCAL\_CH0 register with a 24-bit calibration word.

The offset on the MCP3918 has a low temperature coefficient.

#### 4.7 Gain Error

This is the error induced by the ADC on the slope of the transfer function. It is the deviation expressed in %, compared to the ideal transfer function defined in Equation 5-3. The specification incorporates both PGA and ADC gain error contributions, but not the  $V_{REF}$  contribution (it is measured with an external  $V_{REF}$ ).

This error varies with PGA and OSR settings. The gain error can be digitally compensated independently on each channel through the GAINCAL\_CH0 register with a 24-bit calibration word.

The gain error on the MCP3918 has a low temperature coefficient.

#### 4.8 Integral Non-Linearity Error

Integral non-linearity error is the maximum deviation of an ADC transition point from the corresponding point of an ideal transfer function, with the offset and gain errors removed, or with the end points equal to zero.

It is the maximum remaining error after calibration of offset and gain errors for a DC input signal.

#### 4.9 Signal-to-Noise Ratio (SNR)

For the MCP3918 ADC, the signal-to-noise ratio is a ratio of the output fundamental signal power to noise power (not including the harmonics of the signal), when the input is a sine wave at a predetermined frequency (see Equation 4-4). It is measured in dB. Usually, only the maximum signal-to-noise ratio is specified. The SNR figure depends mainly on the OSR and DITHER settings of the device.

#### EQUATION 4-4: SIGNAL-TO-NOISE RATIO

$$SNR(dB) = 10log\left(\frac{SignalPower}{NoisePower}\right)$$

#### 4.10 Signal-to-Noise and Distortion Ratio (SINAD)

The most important figure of merit for the analog performance of the ADC present on the MCP3918 is the Signal-to-Noise and Distortion (SINAD) specification.

The Signal-to-Noise and Distortion ratio is similar to signal-to-noise ratio, with the exception that you must include the harmonics power in the noise power calculation (see Equation 4-5). The SINAD specification depends mainly on the OSR and DITHER settings.

#### EQUATION 4-5: SINAD EQUATION

$$SINAD(dB) = 10log\left(\frac{SignalPower}{Noise + HarmonicsPower}\right)$$

The calculated combination of SNR and THD per the following formula also yields SINAD (see Equation 4-6).

#### EQUATION 4-6: SINAD, THD AND SNR RELATIONSHIP

$$SINAD(dB) = 10log\left[10^{\left(\frac{SNR}{10}\right)} + 10^{\left(\frac{-THD}{10}\right)}\right]$$