Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 7/8-Bit Quad I<sup>2</sup>C Digital POT with Nonvolatile Memory

#### **Features**

- · Quad Resistor Network

- · Potentiometer or Rheostat configuration options

- · Resistor Network Resolution

- 7-bit: 128 Resistors (129 Taps)

- 8-bit: 256 Resistors (257 Taps)

- R<sub>AB</sub> Resistances options of:

- 5 kΩ

- 10 kΩ

- 50 kO

- 100 kO

- · Zero Scale to Full Scale Wiper operation

- Low Wiper Resistance: 75 Ω (typical)

- · Low Tempco:

- Absolute (Rheostat): 50 ppm typical (0°C to 70°C)

- Ratiometric (Potentiometer): 15 ppm typical

- · Nonvolatile Memory

- Automatic Recall of Saved Wiper Setting

- WiperLock™ Technology

- 5 General Purpose Memory Locations

- I<sup>2</sup>C Serial Interface

- 100 kHz, 400 kHz, and 3.4 MHz support

- · Serial protocol allows:

- High-Speed Read/Write to wiper

- Read/Write to EEPROM

- Write Protect to be enabled/disable

- WiperLock to be enabled/disabled

- Resistor Network Terminal Disconnect Feature via Terminal Control (TCON) Register

- · Reset input pin

- · Write Protect Feature:

- Hardware Write Protect (WP) Control pin

- Software Write Protect (WP) Configuration bit

- Brown-out reset protection (1.5V typical)

- Serial Interface Inactive current (2.5 uA typical)

- · High-Voltage Tolerant Digital Inputs: Up to 12.5V

- · Supports Split Rail Applications

- Internal weak pull-up on all digital inputs (except SCL and SDA)

- · Wide Operating Voltage:

- 2.7V to 5.5V Device Characteristics Specified

- 1.8V to 5.5V Device Operation

- · Wide Bandwidth (-3 dB) Operation:

- 2 MHz (typical) for 5.0 kΩ device

- Extended temperature range (-40°C to +125°C)

- Package Types: 4x4 QFN-20, TSSOP-20 and TSSOP-14

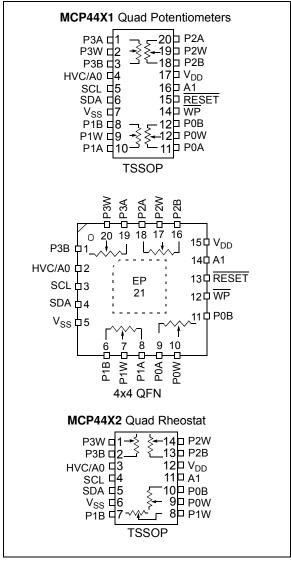

#### Package Types (Top View)

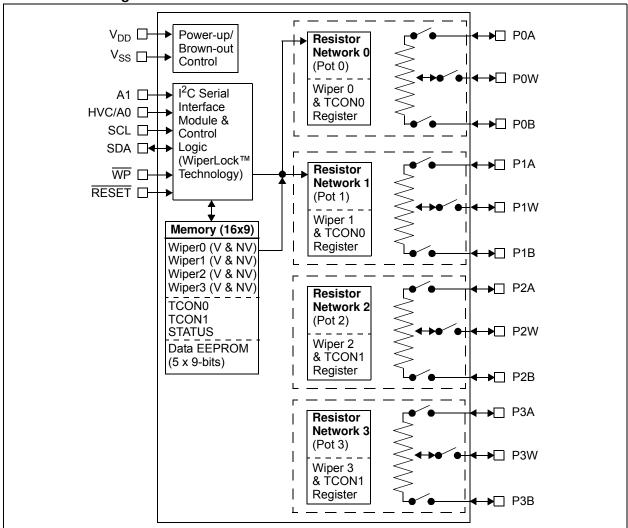

#### **Device Block Diagram**

#### **Device Features**

|                        | Ts        |                              | -                | у              | ock<br>logy             | oer<br>g             | Resistance (typic            | cal)                       | SC        | v                                                    |  |

|------------------------|-----------|------------------------------|------------------|----------------|-------------------------|----------------------|------------------------------|----------------------------|-----------|------------------------------------------------------|--|

| Device                 | # of POTs | Wiper<br>Configuration       | Control          | Memory<br>Type | WiperLock<br>Technology | POR Wiper<br>Setting | R <sub>AB</sub> Options (kΩ) | Wiper - $R_W$ ( $\Omega$ ) | # of Taps | V <sub>DD</sub><br>Operating<br>Range <sup>(2)</sup> |  |

| MCP4431 <sup>(3)</sup> | 4         | Potentiometer (1)            | I <sup>2</sup> C | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0       | 75                         | 129       | 1.8V to 5.5V                                         |  |

| MCP4432 <sup>(3)</sup> | 4         | Rheostat                     | I <sup>2</sup> C | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0       | 75                         | 129       | 1.8V to 5.5V                                         |  |

| MCP4441                | 4         | Potentiometer (1)            | I <sup>2</sup> C | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0       | 75                         | 129       | 2.7V to 5.5V                                         |  |

| MCP4442                | 4         | Rheostat                     | I <sup>2</sup> C | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0       | 75                         | 129       | 2.7V to 5.5V                                         |  |

| MCP4451 <sup>(3)</sup> | 4         | Potentiometer <sup>(1)</sup> | I <sup>2</sup> C | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0       | 75                         | 257       | 1.8V to 5.5V                                         |  |

| MCP4452 <sup>(3)</sup> | 4         | Rheostat                     | I <sup>2</sup> C | RAM            | No                      | Mid-Scale            | 5.0, 10.0, 50.0, 100.0       | 75                         | 257       | 1.8V to 5.5V                                         |  |

| MCP4461                | 4         | Potentiometer <sup>(1)</sup> | I <sup>2</sup> C | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0       | 75                         | 257       | 2.7V to 5.5V                                         |  |

| MCP4462                | 4         | Rheostat                     | I <sup>2</sup> C | EE             | Yes                     | NV Wiper             | 5.0, 10.0, 50.0, 100.0       | 75                         | 257       | 2.7V to 5.5V                                         |  |

- Note 1: Floating either terminal (A or B) allows the device to be used as a Rheostat (variable resistor).

- 2: Analog characteristics only tested from 2.7V to 5.5V unless otherwise noted.

- 3: Please check Microchip web site for device release and availability.

# 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                           |

|-------------------------------------------------------------------------------------------------|

| $(V_1 < 0, V_1 > V_{DD}, V_1 > V_{PP} \text{ on HV pins})$ ±20 mA                               |

| Output clamp current, I <sub>OK</sub>                                                           |

| $(V_O < 0 \text{ or } V_O > V_{DD})$ ±20 mA                                                     |

| Maximum output current sunk by any Output pin                                                   |

| 25 mA                                                                                           |

| Maximum output current sourced by any Output pin ed                                             |

| 25 mA                                                                                           |

| Maximum current out of V <sub>SS</sub> pin100 mA                                                |

| Maximum current into V <sub>DD</sub> pin100 mA                                                  |

| Maximum current into PxA, PxW & PxB pins±2.5 mA                                                 |

| Storage temperature65°C to +150°C                                                               |

| Ambient temperature with power applied                                                          |

| -40°C to +125°C                                                                                 |

| Package power dissipation ( $T_A = +50$ °C, $T_J = +150$ °C)                                    |

| TSSOP-141000 mW                                                                                 |

| TSSOP-201110 mW                                                                                 |

| QFN-20 (4x4)2320 mW                                                                             |

| Soldering temperature of leads (10 seconds)+300°C ESD protection on all pins $\geq$ 4 kV (HBM), |

| ≥ 300V (MM)                                                                                     |

| Maximum Junction Temperature (T <sub>J</sub> )+150°C                                            |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **AC/DC CHARACTERISTICS**

| DC Characteristics                                                                      | 3                 | Operating All parame V <sub>DD</sub> = +2. | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +125^{\circ}\text{C}$ (extended) All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_{\text{A}}$ = +25°C. |                           |       |                                            |                                                                                                                                                   |  |  |  |  |

|-----------------------------------------------------------------------------------------|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameters                                                                              | Sym               | Min                                        | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                 | Max                       | Units |                                            | Conditions                                                                                                                                        |  |  |  |  |

| Supply Voltage                                                                          | $V_{DD}$          | 2.7                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.5                       | V     |                                            |                                                                                                                                                   |  |  |  |  |

|                                                                                         |                   | 1.8                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.7                       | V     | -                                          | nterface only.                                                                                                                                    |  |  |  |  |

| HVC/A0, SDA,<br>SCL, A1, WP,                                                            | $V_{HV}$          | V <sub>SS</sub>                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.5V                     | V     | V <sub>DD</sub> ≥<br>4.5V                  | The HVC/A0 pin will be at one of three input levels                                                                                               |  |  |  |  |

| RESET pin Voltage Range                                                                 |                   | V <sub>SS</sub>                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>DD</sub> +<br>8.0V | V     | V <sub>DD</sub> < 4.5V                     | (V <sub>IL</sub> , V <sub>IH</sub> or V <sub>IHH</sub> ). ( <b>Note 6</b> )                                                                       |  |  |  |  |

| V <sub>DD</sub> Start Voltage<br>to ensure Wiper<br>Reset                               | $V_{BOR}$         | _                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.65                      | V     | RAM re                                     | tention voltage (V <sub>RAM</sub> ) < V <sub>BOR</sub>                                                                                            |  |  |  |  |

| V <sub>DD</sub> Rise Rate to<br>ensure Power-on<br>Reset                                | $V_{DDRR}$        |                                            | (Note 9)                                                                                                                                                                                                                                                                                                                                                                                                                            |                           | V/ms  |                                            |                                                                                                                                                   |  |  |  |  |

| Delay after device<br>exits the reset<br>state<br>(V <sub>DD</sub> > V <sub>BOR</sub> ) | T <sub>BORD</sub> | _                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                        | μs    |                                            |                                                                                                                                                   |  |  |  |  |

| Supply Current (Note 10)                                                                | I <sub>DD</sub>   | -                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 600                       | μA    | HVC/A0<br>Write al                         | nterface Active,<br>0 = V <sub>IH</sub> (or V <sub>IL</sub> ) ( <b>Note 11</b> )<br>1 0's to volatile Wiper 0<br>5.5V, F <sub>SCL</sub> @ 3.4 MHz |  |  |  |  |

|                                                                                         |                   | _                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 250                       | μA    | HVC/A0<br>Write al                         | nterface Active,<br>0 = V <sub>IH</sub> (or V <sub>IL</sub> ) ( <b>Note 11</b> )<br>1 0's to volatile Wiper 0<br>5.5V, F <sub>SCL</sub> @ 100 kHz |  |  |  |  |

|                                                                                         |                   | _                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                   | 575                       | μА    | (Nonvol<br>V <sub>DD</sub> = 5<br>Write al | e Current (Write Cycle) latile device only), 5.5V, F <sub>SCL</sub> = 400 kHz, 1 0's to Nonvolatile Wiper 0 V <sub>IL</sub> or V <sub>IH</sub>    |  |  |  |  |

|                                                                                         |                   | _                                          | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                         | μA    | (Stop co                                   | nterface Inactive,<br>condition, SCL = SDA = V <sub>IH</sub> ),<br>c 0<br>c.5V, HVC/A0 = V <sub>IH</sub>                                          |  |  |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes V<sub>WZSE</sub> and V<sub>WFSE</sub>.

- **5:** Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- 6: This specification by design.

- **7:** Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

|                        |                          | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended)                                                                                           |                         |       |        |                                                |                                            |  |  |  |

|------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|--------|------------------------------------------------|--------------------------------------------|--|--|--|

| DC Characteristic      | s                        | All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |                         |       |        |                                                |                                            |  |  |  |

| Parameters             | Sym                      | Min                                                                                                                                                                                                                                                   | Тур                     | Max   | Units  |                                                | Conditions                                 |  |  |  |

| Resistance             | R <sub>AB</sub>          | 4.0                                                                                                                                                                                                                                                   | 5                       | 6.0   | kΩ     | -502 de                                        | vices (Note 1)                             |  |  |  |

| (± 20%)                |                          | 8.0                                                                                                                                                                                                                                                   | 10                      | 12.0  | kΩ     | -103 de                                        | vices (Note 1)                             |  |  |  |

|                        |                          | 40.0                                                                                                                                                                                                                                                  | 50                      | 60.0  | kΩ     | -503 de                                        | vices (Note 1)                             |  |  |  |

|                        |                          | 80.0                                                                                                                                                                                                                                                  | 100                     | 120.0 | kΩ     | -104 de                                        | vices (Note 1)                             |  |  |  |

| Resolution             | N                        |                                                                                                                                                                                                                                                       | 257                     |       | Taps   | 8-bit                                          | No Missing Codes                           |  |  |  |

|                        |                          |                                                                                                                                                                                                                                                       | 129                     |       | Taps   | 7-bit                                          | No Missing Codes                           |  |  |  |

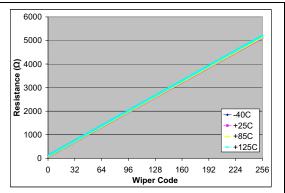

| Step Resistance        | R <sub>S</sub>           | _                                                                                                                                                                                                                                                     | R <sub>AB</sub> / (256) | _     | Ω      | 8-bit                                          | Note 6                                     |  |  |  |

|                        |                          | _                                                                                                                                                                                                                                                     | R <sub>AB</sub> / (128) | _     | Ω      | 7-bit                                          | Note 6                                     |  |  |  |

| Nominal                | (  R <sub>ABWC</sub> -   | _                                                                                                                                                                                                                                                     | 0.2                     | 1.50  | %      | 5 kΩ                                           | MCP44X1 devices only                       |  |  |  |

| Resistance Match       | R <sub>ABMEAN</sub>  ) / | _                                                                                                                                                                                                                                                     | 0.2                     | 1.25  | %      | 10 kΩ                                          |                                            |  |  |  |

|                        | R <sub>ABMEAN</sub>      | _                                                                                                                                                                                                                                                     | 0.2                     | 1.0   | %      | 50 kΩ                                          |                                            |  |  |  |

|                        |                          | _                                                                                                                                                                                                                                                     | 0.2                     | 1.0   | %      | 100 kΩ                                         |                                            |  |  |  |

|                        | (  R <sub>BWWC</sub> -   | _                                                                                                                                                                                                                                                     | 0.25                    | 1.75  | %      | $5~\mathrm{k}\Omega$                           | Code = Full Scale                          |  |  |  |

|                        | R <sub>BWMEAN</sub>  ) / | _                                                                                                                                                                                                                                                     | 0.25                    | 1.50  | %      | 10 kΩ                                          |                                            |  |  |  |

|                        | R <sub>BWMEAN</sub>      | _                                                                                                                                                                                                                                                     | 0.25                    | 1.25  | %      | 50 kΩ                                          |                                            |  |  |  |

|                        |                          | _                                                                                                                                                                                                                                                     | 0.25                    | 1.25  | %      | 100 kΩ                                         |                                            |  |  |  |

| Wiper Resistance       | $R_W$                    | _                                                                                                                                                                                                                                                     | 75                      | 160   | Ω      |                                                | 5.5 V, I <sub>W</sub> = 2.0 mA, code = 00h |  |  |  |

| (Note 3, Note 4)       |                          | _                                                                                                                                                                                                                                                     | 75                      | 300   | Ω      |                                                | 2.7 V, I <sub>W</sub> = 2.0 mA, code = 00h |  |  |  |

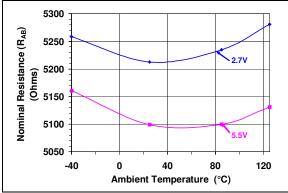

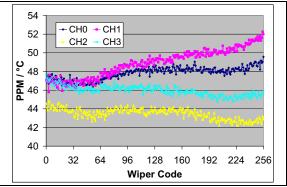

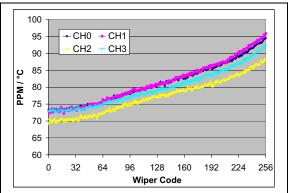

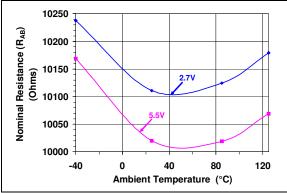

| Nominal                | $\Delta R_{AB}/\Delta T$ | _                                                                                                                                                                                                                                                     | 50                      | _     | ppm/°C |                                                | 0°C to +70°C                               |  |  |  |

| Resistance             |                          | _                                                                                                                                                                                                                                                     | 100                     | _     | ppm/°C | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$  |                                            |  |  |  |

| Tempco                 |                          | _                                                                                                                                                                                                                                                     | 150                     | _     | ppm/°C | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                                            |  |  |  |

| Ratiometeric<br>Tempco | ΔV <sub>WB</sub> /ΔT     |                                                                                                                                                                                                                                                       | 15                      |       | ppm/°C |                                                | Midscale (80h or 40h)                      |  |  |  |

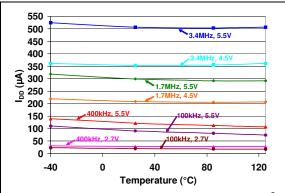

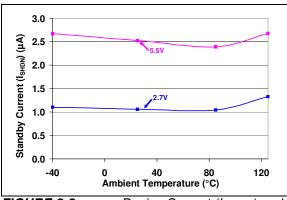

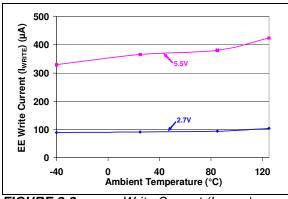

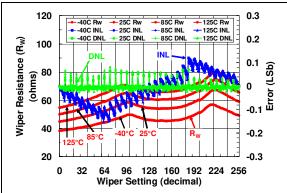

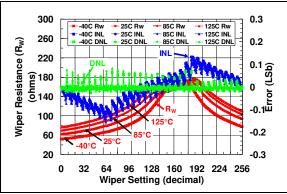

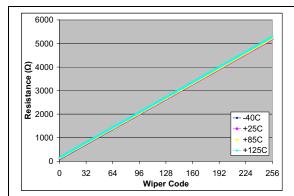

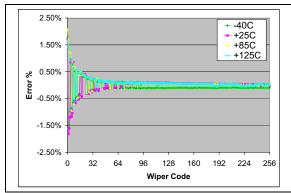

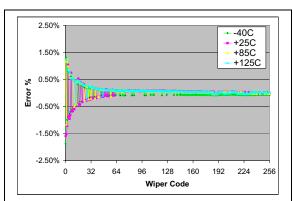

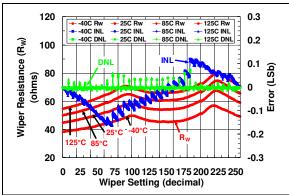

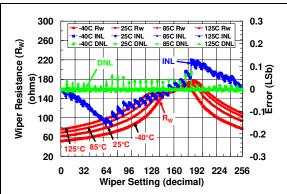

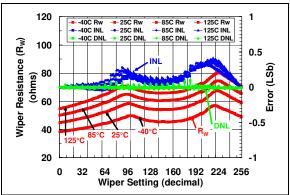

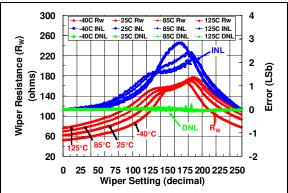

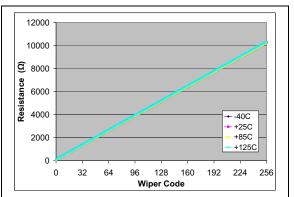

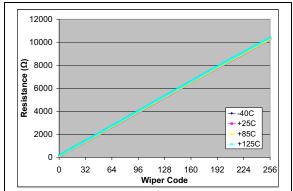

| Resistance<br>Tracking | ΔR <sub>TRACK</sub>      | S                                                                                                                                                                                                                                                     | ection 2.0              |       | ppm/°C |                                                | oical Performance Curves                   |  |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- 5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- 6: This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- **9:** POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

|                                                                       | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended) |                                                                                                                                                                                                                                                       |     |                 |       |                                                                                                                         |                                          |  |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|

| DC Characteristics                                                    | 5                                                                                                                                                            | All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |     |                 |       |                                                                                                                         |                                          |  |  |  |  |

| Parameters                                                            | Sym                                                                                                                                                          | Min                                                                                                                                                                                                                                                   | Тур | Max             | Units | Con                                                                                                                     | ditions                                  |  |  |  |  |

| Resistor Terminal<br>Input Voltage<br>Range (Terminals<br>A, B and W) | $V_{A,}V_{W,}V_{B}$                                                                                                                                          | Vss                                                                                                                                                                                                                                                   | _   | V <sub>DD</sub> | V     | Note 5, Note 6                                                                                                          |                                          |  |  |  |  |

| Maximum current through A, W or B                                     | I <sub>W</sub>                                                                                                                                               | _                                                                                                                                                                                                                                                     | _   | 2.5             | mA    | Terminal A I <sub>AW</sub> ,<br>W = Full Scale (Fa                                                                      |                                          |  |  |  |  |

| (Note 6)                                                              |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | _   | 2.5             | mA    | Terminal B                                                                                                              | I <sub>BW</sub> ,<br>W = Zero Scale (ZS) |  |  |  |  |

|                                                                       |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | _   | 2.5             | mA    | Terminal W                                                                                                              | $I_{AW}$ (W = FS) or $I_{BW}$ (W = ZS)   |  |  |  |  |

| Maximum R <sub>AB</sub>                                               | I <sub>AB</sub>                                                                                                                                              | _                                                                                                                                                                                                                                                     | _   | 1.38            | mA    | $V_B = 0V, V_A = 5.5V$                                                                                                  | $I/R_{AB(MIN)} = 4000\Omega$             |  |  |  |  |

| current (I <sub>AB</sub> )                                            |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | _   | 0.688           | mA    | $V_B = 0V, V_A = 5.5V$                                                                                                  | $V_{\rm AB(MIN)} = 8000\Omega$           |  |  |  |  |

| (Note 6)                                                              |                                                                                                                                                              | _                                                                                                                                                                                                                                                     |     | 0.138           | mA    | $V_B = 0V, V_A = 5.5V$                                                                                                  | $I/R_{AB(MIN)} = 40000\Omega$            |  |  |  |  |

|                                                                       |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | _   | 0.069           | mA    | $V_B = 0V, V_A = 5.5V$                                                                                                  | $I/R_{AB(MIN)} = 80000\Omega$            |  |  |  |  |

| Leakage current                                                       | $I_{WL}$                                                                                                                                                     | _                                                                                                                                                                                                                                                     | 100 | _               | nA    | MCP44X1 PxA = I                                                                                                         | $PxW = PxB = V_{SS}$                     |  |  |  |  |

| into A, W or B                                                        |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | 100 | _               | nA    | MCP44X2 PxB = I                                                                                                         | $PxW = V_{SS}$                           |  |  |  |  |

|                                                                       |                                                                                                                                                              | _                                                                                                                                                                                                                                                     | 100 | _               | nA    | Terminals Disconnected<br>(R0A = R0W = R0B = 0;<br>R1A = R1W = R1B = 0;<br>R2A = R2W = R2B = 0;<br>R3A = R3W = R3B = 0) |                                          |  |  |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- 5: Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- **6:** This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 = V<sub>IHH</sub>, the I<sub>DD</sub> current is less due to current into the HVC/A0 pin. See I<sub>PU</sub> specification.

|                    |            |                 | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ (extended) |             |           |                                                                                              |  |  |  |  |  |

|--------------------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| DC Characteristics | S          | $V_{DD} = +2.7$ | 7V to 5.5V                                                                                                                                                          | ⁄, 5 kΩ, 10 | kΩ, 50 kΩ | d operating ranges unless noted.<br>2, 100 kΩ devices.<br>or $V_{DD}$ = 5.5V, $T_A$ = +25°C. |  |  |  |  |  |

| Doromotoro         | Conditions |                 |                                                                                                                                                                     |             |           |                                                                                              |  |  |  |  |  |

|                                         |            | . , p.oui op |        | o roproco |       | טט י   | 0.0 V, 1 <sub>A</sub> | - 20 0.                      |

|-----------------------------------------|------------|--------------|--------|-----------|-------|--------|-----------------------|------------------------------|

| Parameters                              | Sym        | Min          | Тур    | Max       | Units |        | Con                   | ditions                      |

| Full Scale Error                        | $V_{WFSE}$ | -6.0         | -0.1   | _         | LSb   | 5 kΩ   | 8-bit                 | $3.0V \le V_{DD} \le 5.5V$   |

| (MCP44X1 only)                          |            | -4.0         | -0.1   | _         | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

| (8-bit code = 100h,                     |            | -3.5         | -0.1   | _         | LSb   | 10 kΩ  | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

| 7-bit code = 80h)                       |            | -2.0         | -0.1   | 1         | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | -0.8         | -0.1   |           | LSb   | 50 kΩ  | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | -0.5         | -0.1   | _         | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | -0.5         | -0.1   |           | LSb   | 100 kΩ | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | -0.5         | -0.1   | 1         | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

| Zero Scale Error                        | $V_{WZSE}$ | _            | +0.1   | +6.0      | LSb   | 5 kΩ   | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

| (MCP44X1 only)                          |            | _            | +0.1   | +3.0      | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

| (8-bit code = 00h,<br>7-bit code = 00h) |            | _            | +0.1   | +3.5      | LSb   | 10 kΩ  | 8-bit                 | $3.0V \le V_{DD} \le 5.5V$   |

| 7-bit code – boli)                      |            | _            | +0.1   | +2.0      | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | _            | +0.1   | +0.8      | LSb   | 50 kΩ  | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | _            | +0.1   | +0.5      | LSb   |        | 7-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | _            | +0.1   | +0.5      | LSb   | 100 kΩ | 8-bit                 | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                         |            | _            | +0.1   | +0.5      | LSb   |        | 7-bit                 | $3.0V \le V_{DD} \le 5.5V$   |

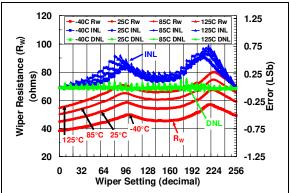

| Potentiometer                           | INL        | -1           | ±0.5   | +1        | LSb   | 8-bit  | $3.0V \leq V_D$       |                              |

| Integral<br>Non-linearity               |            | -0.5         | ±0.25  | +0.5      | LSb   | 7-bit  | MCP44X1<br>(Note 2)   | devices only                 |

| Potentiometer                           | DNL        | -0.5         | ±0.25  | +0.5      | LSb   | 8-bit  | $3.0V \leq V_{D}$     |                              |

| Differential Non-<br>linearity          |            | -0.25        | ±0.125 | +0.25     | LSb   | 7-bit  | MCP44X1<br>(Note 2)   | devices only                 |

| Bandwidth -3 dB                         | BW         | _            | 2      |           | MHz   | 5 kΩ   | 8-bit                 | Code = 80h                   |

| (See Figure 2-72,                       |            | _            | 2      | _         | MHz   |        | 7-bit                 | Code = 40h                   |

| load = 30 pF)                           |            |              | 1      |           | MHz   | 10 kΩ  | 8-bit                 | Code = 80h                   |

|                                         |            |              | 1      |           | MHz   |        | 7-bit                 | Code = 40h                   |

|                                         |            | _            | 200    | _         | kHz   | 50 kΩ  | 8-bit                 | Code = 80h                   |

|                                         |            |              | 200    |           | kHz   |        | 7-bit                 | Code = 40h                   |

|                                         |            | _            | 100    |           | kHz   | 100 kΩ | 8-bit                 | Code = 80h                   |

|                                         |            |              | 100    | _         | kHz   |        | 7-bit                 | Code = 40h                   |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- **5:** Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- **6:** This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

|                                                      |       | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended)                                                                                           |               |                |            |        |       |                                                                                     |  |  |  |

|------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|------------|--------|-------|-------------------------------------------------------------------------------------|--|--|--|

| DC Characteristics                                   | •     | All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |               |                |            |        |       |                                                                                     |  |  |  |

| Parameters                                           | Sym   | Min                                                                                                                                                                                                                                                   | Тур           | Max            | Units      |        | Cor   | nditions                                                                            |  |  |  |

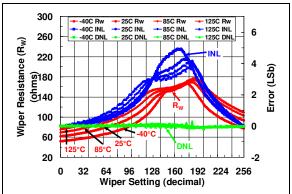

| Rheostat Integral<br>Non-linearity<br>MCP44X1        | R-INL | -1.5<br>-8.25                                                                                                                                                                                                                                         | ±0.5<br>+4.5  | +1.5<br>+8.25  | LSb<br>LSb | 5 kΩ   | 8-bit | 5.5V, I <sub>W</sub> = 900 μA<br>3.0V, I <sub>W</sub> = 480 μA<br>( <b>Note 7</b> ) |  |  |  |

| (Note 4, Note 8)<br>MCP44X2 devices<br>only (Note 4) |       | -1.125<br>-6.0                                                                                                                                                                                                                                        | ±0.5<br>+4.5  | +1.125<br>+6.0 | LSb<br>LSb | 1      | 7-bit | 5.5V, I <sub>W</sub> = 900 μA<br>3.0V, I <sub>W</sub> = 480 μA<br>( <b>Note 7</b> ) |  |  |  |

|                                                      |       | -1.5<br>-5.5                                                                                                                                                                                                                                          | ±0.5<br>+2.5  | +1.5<br>+5.5   | LSb<br>LSb | 10 kΩ  | 8-bit | 5.5V, I <sub>W</sub> = 450 μA<br>3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> ) |  |  |  |

|                                                      |       | -1.125<br>-4.0                                                                                                                                                                                                                                        | ±0.5<br>+2.5  | +1.125<br>+4.0 | LSb<br>LSb |        | 7-bit | 5.5V, I <sub>W</sub> = 450 μA<br>3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> ) |  |  |  |

|                                                      |       | -1.5<br>-2.0                                                                                                                                                                                                                                          | ±0.5<br>+1    | +1.5 +2.0      | LSb<br>LSb | 50 kΩ  | 8-bit | 5.5V, I <sub>W</sub> = 90 μA<br>3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )   |  |  |  |

|                                                      |       | -1.125<br>-1.5                                                                                                                                                                                                                                        | ±0.5<br>+1    | +1.125<br>+1.5 | LSb<br>LSb |        | 7-bit | 5.5V, I <sub>W</sub> = 90 μA<br>3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )   |  |  |  |

|                                                      |       | -1.0<br>-1.5                                                                                                                                                                                                                                          | ±0.5<br>+0.25 | +1.0 +1.5      | LSb<br>LSb | 100 kΩ | 8-bit | 5.5V, I <sub>W</sub> = 45 μA<br>3.0V, I <sub>W</sub> = 24 μA<br>( <b>Note 7</b> )   |  |  |  |

|                                                      |       | -0.8<br>-1.125                                                                                                                                                                                                                                        | ±0.5<br>+0.25 | +0.8           | LSb<br>LSb | -      | 7-bit | 5.5V, I <sub>W</sub> = 45 μA<br>3.0V, I <sub>W</sub> = 24 μA<br>( <b>Note 7</b> )   |  |  |  |

- Note 1: Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes V<sub>WZSE</sub> and V<sub>WFSE</sub>.

- **5:** Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- 6: This specification by design.

- 7: Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

|                                             |                 | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}\text{C} \le T_{\text{A}} \le +125^{\circ}\text{C}$ (extended)                                                                                              |               |              |            |         |                             |                                                                |  |  |  |

|---------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|------------|---------|-----------------------------|----------------------------------------------------------------|--|--|--|

| DC Characteristics                          | S               | All parameters apply across the specified operating ranges unless noted.<br>$V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices.<br>Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |               |              |            |         |                             |                                                                |  |  |  |

| Parameters                                  | Sym             | Min                                                                                                                                                                                                                                                         | Тур           | Max          | Units      |         | Con                         | ditions                                                        |  |  |  |

| Rheostat Differential Non- linearity        | R-DNL           | -0.5<br>-1.0                                                                                                                                                                                                                                                | ±0.25<br>+0.5 | +0.5<br>+1.0 | LSb<br>LSb | 5 kΩ    | 8-bit                       | 5.5V, I <sub>W</sub> = 900 μA<br>3.0V, I <sub>W</sub> = 480 μA |  |  |  |

| MCP44X1                                     |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         | 7-bit                       | (Note 7)<br>5.5V, I <sub>W</sub> = 900 μA                      |  |  |  |

| (Note 4, Note 8)<br>MCP44X2 devices<br>only |                 | -0.75                                                                                                                                                                                                                                                       | +0.5          | +0.75        | LSb        | -       |                             | 3.0V, I <sub>W</sub> = 480 μA<br>( <b>Note 7</b> )             |  |  |  |

| (Note 4)                                    |                 | -0.5                                                                                                                                                                                                                                                        | ±0.25         | +0.5         | LSb        | 10 kΩ   | 8-bit                       | 5.5V, I <sub>W</sub> = 450 μA                                  |  |  |  |

| ,                                           |                 | -1.0                                                                                                                                                                                                                                                        | +0.25         | +1.0         | LSb        |         |                             | 3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> )             |  |  |  |

|                                             |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         | 7-bit                       | 5.5V, I <sub>W</sub> = 450 μA                                  |  |  |  |

|                                             |                 | -0.75                                                                                                                                                                                                                                                       | +0.5          | +0.75        | LSb        |         |                             | 3.0V, I <sub>W</sub> = 240 μA<br>( <b>Note 7</b> )             |  |  |  |

|                                             |                 | -0.5                                                                                                                                                                                                                                                        | ±0.25         | +0.5         | LSb        | 50 kΩ   | 8-bit                       | 5.5V, I <sub>W</sub> = 90 μA                                   |  |  |  |

|                                             |                 | -0.5                                                                                                                                                                                                                                                        | ±0.25         | +0.5         | LSb        |         |                             | 3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )              |  |  |  |

|                                             |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         | 7-bit                       | 5.5V, I <sub>W</sub> = 90 μA                                   |  |  |  |

|                                             |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         |                             | 3.0V, I <sub>W</sub> = 48 μA<br>( <b>Note 7</b> )              |  |  |  |

|                                             |                 | -0.5                                                                                                                                                                                                                                                        | ±0.25         | +0.5         | LSb        | 100 kΩ  | 8-bit                       | 5.5V, I <sub>W</sub> = 45 μA                                   |  |  |  |

|                                             |                 | -0.5                                                                                                                                                                                                                                                        | ±0.25         | +0.5         | LSb        |         |                             | 3.0V, I <sub>W</sub> = 24 μA<br>( <b>Note 7</b> )              |  |  |  |

|                                             |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         | 7-bit                       | 5.5V, $I_W = 45 \mu A$                                         |  |  |  |

|                                             |                 | -0.375                                                                                                                                                                                                                                                      | ±0.25         | +0.375       | LSb        |         |                             | 3.0V, I <sub>W</sub> = 24 μA<br>( <b>Note 7</b> )              |  |  |  |

| Capacitance (P <sub>A</sub> )               | C <sub>AW</sub> | _                                                                                                                                                                                                                                                           | 75            | _            | pF         | -       |                             | Full Scale                                                     |  |  |  |

| Capacitance (P <sub>w</sub> )               | C <sub>W</sub>  | _                                                                                                                                                                                                                                                           | 120           | _            | pF         |         | f =1 MHz, Code = Full Scale |                                                                |  |  |  |

| Capacitance (P <sub>B</sub> )               | $C_{BW}$        | _                                                                                                                                                                                                                                                           | 75            | _            | pF         | f =1 MH | z, Code =                   | Full Scale                                                     |  |  |  |

- **Note 1:** Resistance is defined as the resistance between terminal A to terminal B.

- 2: INL and DNL are measured at  $V_W$  with  $V_A = V_{DD}$  and  $V_B = V_{SS}$ .

- 3: MCP44X1 only.

- 4: MCP44X2 only, includes  $V_{WZSE}$  and  $V_{WFSE}$ .

- **5:** Resistor terminals A, W and B's polarity with respect to each other is not restricted.

- 6: This specification by design.

- **7:** Non-linearity is affected by wiper resistance (R<sub>W</sub>), which changes significantly over voltage and temperature.

- 8: The MCP44X1 is externally connected to match the configurations of the MCP44X2, and then tested.

- 9: POR/BOR is not rate dependent.

- **10:** Supply current is independent of current through the resistor network.

- 11: When HVC/A0 =  $V_{IHH}$ , the  $I_{DD}$  current is less due to current into the HVC/A0 pin. See  $I_{PU}$  specification.

|                    |     | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ (extended)                                                                                 |     |       |            |  |  |  |  |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|--|--|--|

| DC Characteristics | S   | All parameters apply across the specified operating ranges unless noted. $V_{DD}$ = +2.7V to 5.5V, 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ devices. Typical specifications represent values for $V_{DD}$ = 5.5V, $T_A$ = +25°C. |     |       |            |  |  |  |  |

| Parameters         | Min | Тур                                                                                                                                                                                                                                                   | Max | Units | Conditions |  |  |  |  |

| Parameters                                 | Sym                | Min                           | Тур                | Max                             | Units |                                            | Con                                              | ditions                         |  |

|--------------------------------------------|--------------------|-------------------------------|--------------------|---------------------------------|-------|--------------------------------------------|--------------------------------------------------|---------------------------------|--|

| Digital Inputs/Outp                        | uts (HVC/A0,       | A1, SDA, S                    | CL, WP, I          | RESET)                          |       |                                            |                                                  |                                 |  |

| Schmitt Trigger<br>High Input<br>Threshold | V <sub>IH</sub>    | 0.45 V <sub>DD</sub>          | _                  | _                               | V     | All<br>Inputs<br>except                    | 2.7V ≤ V <sub>C</sub><br>(Allows 2.<br>5V Analog | 7V Digital V <sub>DD</sub> with |  |

|                                            |                    | 0.5 V <sub>DD</sub>           |                    | _                               | V     | SDA<br>and<br>SCL                          | 1.8V ≤ V <sub>□</sub>                            | $_{DD} \leq 2.7V$               |  |

|                                            |                    | 0.7 V <sub>DD</sub>           | _                  | $V_{MAX}$                       | V     | SDA                                        | 100 kHz                                          |                                 |  |

|                                            |                    | 0.7 V <sub>DD</sub>           |                    | $V_{MAX}$                       | V     | SDA<br>and                                 | 400 kHz                                          |                                 |  |

|                                            |                    | 0.7 V <sub>DD</sub>           | _                  | $V_{MAX}$                       | V     | SCL                                        | 1.7 MHz                                          |                                 |  |

|                                            |                    | 0.7 V <sub>DD</sub>           | _                  | $V_{MAX}$                       | V     |                                            | 3.4 Mhz                                          |                                 |  |

| Schmitt Trigger                            | $V_{IL}$           |                               | _                  | 0.2V <sub>DD</sub>              | V     | All inpu                                   |                                                  | DA and SCL                      |  |

| Low Input<br>Threshold                     |                    | -0.5                          | _                  | 0.3V <sub>DD</sub>              | V     | SDA                                        | 100 kHz                                          |                                 |  |

| Tillesilolu                                |                    | -0.5                          | _                  | 0.3V <sub>DD</sub>              | V     | and                                        | 400 kHz                                          |                                 |  |

|                                            |                    | -0.5                          | _                  | 0.3V <sub>DD</sub>              | V     | SCL                                        | 1.7 MHz                                          |                                 |  |

|                                            |                    | -0.5                          | _                  | 0.3V <sub>DD</sub>              | V     |                                            | 3.4 Mhz                                          |                                 |  |

| Hysteresis of                              | $V_{HYS}$          | _                             | 0.1V <sub>DD</sub> | _                               | V     | All inpu                                   | ts except S                                      | DA and SCL                      |  |

| Schmitt Trigger Inputs                     |                    | N.A.                          |                    | _                               | V     |                                            | 100 kHz                                          | V <sub>DD</sub> < 2.0V          |  |

| Inputs                                     |                    | N.A.                          | _                  | _                               | V     | SDA                                        |                                                  | $V_{DD} \ge 2.0V$               |  |

|                                            |                    | 0.1 V <sub>DD</sub>           |                    | _                               | V     | and                                        | 400 kHz                                          | V <sub>DD</sub> < 2.0V          |  |

|                                            |                    | $0.05~\mathrm{V}_\mathrm{DD}$ | _                  | _                               | V     | SCL                                        |                                                  | $V_{DD} \ge 2.0V$               |  |

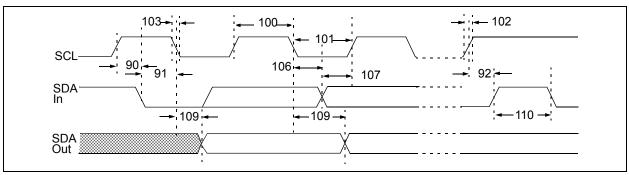

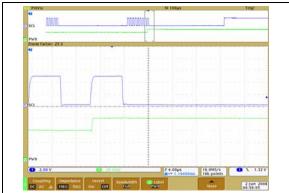

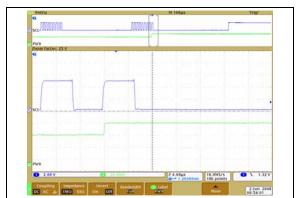

|                                            |                    | 0.1 V <sub>DD</sub>           | _                  | _                               | V     |                                            | 1.7 MHz                                          |                                 |  |