# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **MCP4728**

# 12-Bit, Quad Digital-to-Analog Converter with EEPROM Memory

#### Features

- 12-Bit Voltage Output DAC with Four Buffered Outputs

- On-Board Nonvolatile Memory (EEPROM) for DAC Codes and I<sup>2</sup>C<sup>™</sup> Address Bits

- Internal or External Voltage Reference Selection

- Output Voltage Range:

- Using Internal V<sub>REF</sub> (2.048V):

- 0.000V to 2.048V with Gain Setting = 1

- 0.000V to 4.096V with Gain Setting = 2

- Using External V<sub>REF</sub> (V<sub>DD</sub>):

0.000V to V<sub>DD</sub>

- ±0.2 Least Significant Bit (LSB) Differential Nonlinearity (DNL) (typical)

- Fast Settling Time: 6 µs (typical)

- Normal or Power-Down Mode

- Low Power Consumption

- Single-Supply Operation: 2.7V to 5.5V

- I<sup>2</sup>C Interface:

- Address bits: User Programmable to EEPROM

- Standard (100 kbps), Fast (400 kbps) and High Speed (HS) Mode (3.4 Mbps)

- 10-Lead MSOP Package

- Extended Temperature Range: -40°C to +125°C

#### Applications

- · Set Point or Offset Adjustment

- Sensor Calibration

- Closed-Loop Servo Control

- Low Power Portable Instrumentation

- PC Peripherals

- Programmable Voltage and Current Source

- Industrial Process Control

- Instrumentation

- · Bias Voltage Adjustment for Power Amplifiers

#### Description

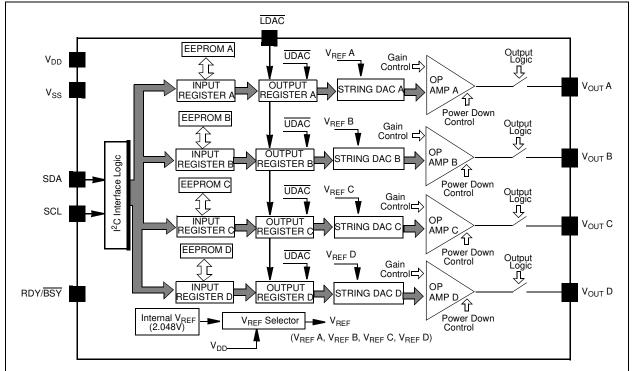

The MCP4728 device is a quad, 12-bit voltage output Digital-to-Analog Convertor (DAC) with nonvolatile memory (EEPROM). Its on-board precision output amplifier allows it to achieve rail-to-rail analog output swing.

The DAC input codes, device configuration bits, and  $I^2C$  address bits are programmable to the nonvolatile memory (EEPROM) by using  $I^2C$  serial interface commands. The nonvolatile memory feature enables the DAC device to hold the DAC input codes during power-off time, allowing the DAC outputs to be available immediately after power-up with the saved settings. This feature is very useful when the DAC device is used as a supporting device for other devices in the application's network.

The MCP4728 device has a high precision internal voltage reference ( $V_{REF} = 2.048V$ ). The user can select the internal reference or external reference ( $V_{DD}$ ) for each channel individually.

Each channel can be operated in Normal mode or Power-Down mode individually by setting the configuration register bits. In Power-Down mode, most of the internal circuits in the powered down channel are turned off for power savings, and the output amplifier can be configured to present a known low, medium, or high resistance output load.

The MCP4728 device includes a Power-on Reset (POR) circuit to ensure reliable power-up and an on-board charge pump for the EEPROM programming voltage.

The MCP4728 has a two-wire  $I^2C$  compatible serial interface for standard (100 kHz), fast (400 kHz), or high speed (3.4 MHz) mode.

The MCP4728 DAC is an ideal device for applications requiring design simplicity with high precision, and for applications requiring the DAC device settings to be saved during power-off time.

The MCP4728 device is available in a 10-lead MSOP package and operates from a single 2.7V to 5.5V supply voltage.

# **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings†

| V <sub>DD</sub><br>All inputs and outputs w.r.t V <sub>SS</sub> |                  |

|-----------------------------------------------------------------|------------------|

| Current at Input Pins                                           | 00               |

| Current at Supply Pins                                          | ±110 mA          |

| Current at Output Pins                                          | ±25 mA           |

| Storage Temperature                                             | 65°C to +150°C   |

| Ambient Temp. with Power Applied                                | 55°C to +125°C   |

| ESD protection on all pins $\geq 4 \text{ k}$                   | V HBM, ≥ 400V MM |

| Maximum Junction Temperature (T <sub>J</sub> )                  | +150°C           |

# **ELECTRICAL CHARACTERISTICS**

**†** Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Electrical Specifications: Unless otherwise indicated, all parameters apply at $V_{DD}$ = +2.7V to                                                                  | 5.5V, V <sub>SS</sub> = 0V,  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $B_{\rm r} = 5 \text{ kO}$ C <sub>r</sub> = 100 pF G <sub>V</sub> = 1 T <sub>e</sub> = -40°C to +125°C Typical values are at +25°C V <sub>w</sub> = V <sub>pp</sub> | $V_{\mu} = V_{\alpha\alpha}$ |

| Parameter                                                                  | Symbol              | Min | Typical | Max  | Units | Conditions                                                                              |  |  |  |

|----------------------------------------------------------------------------|---------------------|-----|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|--|

| Power Requirements                                                         |                     |     |         |      |       |                                                                                         |  |  |  |

| Operating Voltage                                                          | V <sub>DD</sub>     | 2.7 |         | 5.5  | V     |                                                                                         |  |  |  |

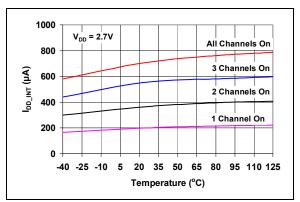

| Supply Current with<br>External Reference                                  | I <sub>DD_EXT</sub> |     | 800     | 1400 | μΑ    | $V_{REF} = V_{DD}, V_{DD} = 5.5V$<br>All 4 channels are in Normal mode.                 |  |  |  |

| (V <sub>REF</sub> = V <sub>DD</sub> )<br>(Note 1)                          |                     |     | 600     | _    | μΑ    | 3 channels are in Normal mode,<br>1 channel is powered down.                            |  |  |  |

|                                                                            |                     |     | 400     | —    | μΑ    | 2 channels are in Normal mode,<br>2 channel are powered down.                           |  |  |  |

|                                                                            |                     | _   | 200     | _    | μΑ    | 1 channel is in Normal mode,<br>3 channels are powered down.                            |  |  |  |

| Power-Down Current with<br>External Reference                              | I <sub>PD_EXT</sub> |     | 40      | —    | nA    | All 4 channels are powered down. $(V_{REF} = V_{DD})$                                   |  |  |  |

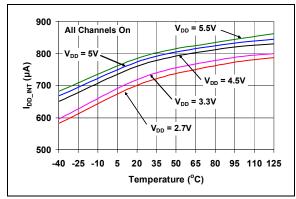

| Supply Current with<br>Internal Reference<br>(V <sub>REF</sub> = Internal) | I <sub>DD_INT</sub> | —   | 800     | 1400 | μA    | $V_{REF}$ = Internal Reference<br>$V_{DD}$ = 5.5V<br>All 4 channels are in normal mode. |  |  |  |

| (Note 1)                                                                   |                     | _   | 600     | —    | μA    | 3 channels are in Normal mode,<br>1 channel is powered down.                            |  |  |  |

|                                                                            |                     | _   | 400     | —    | μA    | 2 channels are in Normal mode,<br>2 channels are powered down.                          |  |  |  |

|                                                                            |                     |     | 200     | _    | μΑ    | 1 channel is in Normal mode,<br>3 channels are powered down.                            |  |  |  |

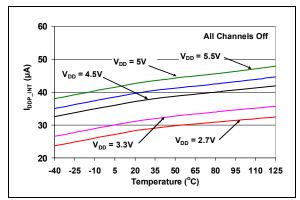

| Power-Down Current with<br>Internal Reference                              | I <sub>PD_INT</sub> | _   | 45      | 60   | μΑ    | All 4 channels are powered down.<br>V <sub>REF</sub> = Internal Reference               |  |  |  |

**Note 1:** All digital input pins (SDA, SCL,  $\overline{\text{LDAC}}$ ) are tied to "High", Output pins are unloaded, code = 0 x 000.

- 2: The power-up ramp rate measures the rise of V<sub>DD</sub> over time.

- 3: This parameter is ensured by design and not 100% tested.

- 4: This parameter is ensured by characterization and not 100% tested.

- 5: Test code range: 100 4000 codes,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5.5V$ .

- 6: Time delay to settle to a new reference when switching from external to internal reference or vice versa.

- 7: This parameter is indirectly tested by Offset and Gain error testing.

- 8: Within 1/2 LSB of the final value when code changes from 1/4 of to 3/4 of full scale.

- **9:** This time delay is measured from the falling edge of ACK pulse in I<sup>2</sup>C command to the beginning of V<sub>OUT</sub>. This time delay is not included in the output settling time specification.

# ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $V_{DD} = +2.7V$  to 5.5V,  $V_{SS} = 0V$ ,  $R_L = 5 k\Omega$ ,  $C_L = 100 \text{ pF}$ ,  $G_X = 1$ ,  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . Typical values are at  $+25^{\circ}\text{C}$ ,  $V_{IH} = V_{DD}$ ,  $V_{IL} = V_{SS}$ .

| Parameter                            | Symbol                                  | Min    | Typical | Мах   | Units             | $\mathbf{C}, \mathbf{v}_{\text{IH}} = \mathbf{v}_{\text{DD}}, \mathbf{v}_{\text{IL}} = \mathbf{v}_{\text{SS}}.$ |

|--------------------------------------|-----------------------------------------|--------|---------|-------|-------------------|-----------------------------------------------------------------------------------------------------------------|

| Power-on Reset                       |                                         |        | 2.2     | max   | V                 |                                                                                                                 |

| Threshold Voltage                    | V <sub>POR</sub>                        | _      | 2.2     | _     | v                 | All circuits, including EEPROM, are ready to operate.                                                           |

| Power-Up Ramp Rate                   | V <sub>RAMP</sub>                       | 1      |         |       | V/s               | Note 2, Note 4                                                                                                  |

| DC Accuracy                          | * RAMP                                  |        |         |       | 1/0               |                                                                                                                 |

| Resolution                           | n                                       | 12     | _       |       | Bits              | Code Change: 000h to FFFh                                                                                       |

| Integral Nonlinearity (INL)<br>Error | INL                                     |        | ±2      | ±13   | LSB               | Note 5                                                                                                          |

| DNL Error                            | DNL                                     | -0.75  | ±0.2    | ±0.75 | LSB               | Note 5                                                                                                          |

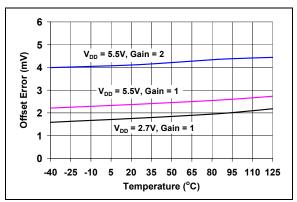

| Offset Error                         | V <sub>OS</sub>                         | _      | 5       | 20    | mV                | Code = 000h<br>See Figure 2-24                                                                                  |

| Offset Error Drift                   | ∆V <sub>OS</sub> /°C                    | _      | ±0.16   | _     | ppm/°C            | -45°C to +25°C                                                                                                  |

|                                      |                                         | _      | ±0.44   | _     | ppm/°C            | +25°C to +125°C                                                                                                 |

| Gain Error                           | G <sub>E</sub>                          | -1.25  | 0.4     | +1.25 | % of<br>FSR       | Code = FFFh,<br>Offset error is not included.<br>Typical value is at room<br>temperature<br>See Figure 2-25     |

| Gain Error Drift                     | ∆G <sub>E</sub> /°C                     | _      | -3      | _     | ppm/°C            |                                                                                                                 |

| Internal Voltage Reference           | e (V <sub>REF</sub> ), ( <mark>N</mark> | ote 3) |         |       |                   |                                                                                                                 |

| Internal Voltage Reference           | V <sub>REF</sub>                        | 2.007  | 2.048   | 2.089 | V                 |                                                                                                                 |

| Temperature Coefficient              | $\Delta V_{REF} / ^{\circ}C$            | _      | 125     | _     | ppm/°C            | -40 to 0°C                                                                                                      |

|                                      |                                         | _      | 0.25    | _     | LSB/°C            |                                                                                                                 |

|                                      |                                         | _      | 45      |       | ppm/°C            | 0 to +125°C                                                                                                     |

|                                      |                                         | _      | 0.09    |       | LSB/°C            |                                                                                                                 |

| Reference Output Noise               | E <sub>NREF</sub>                       | _      | 290     | _     | μV <sub>p-p</sub> | Code = FFFh,<br>0.1 – 10 Hz, G <sub>x</sub> = 1                                                                 |

| Output Noise Density                 | e <sub>NREF</sub>                       |        | 1.2     |       |                   | Code = FFFh, 1 kHz, G <sub>x</sub> = 1                                                                          |

|                                      |                                         | _      | 1.0     |       | μŴ√Hz             | Code = FFFh, 10 kHz, G <sub>x</sub> = 1                                                                         |

| 1/f Corner Frequency                 | f <sub>CORNER</sub>                     |        | 400     |       | Hz                |                                                                                                                 |

**Note 1:** All digital input pins (SDA, SCL,  $\overline{\text{LDAC}}$ ) are tied to "High", Output pins are unloaded, code = 0 x 000.

- 2: The power-up ramp rate measures the rise of V<sub>DD</sub> over time.

- 3: This parameter is ensured by design and not 100% tested.

- 4: This parameter is ensured by characterization and not 100% tested.

- 5: Test code range: 100 4000 codes,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5.5V$ .

- 6: Time delay to settle to a new reference when switching from external to internal reference or vice versa.

- 7: This parameter is indirectly tested by Offset and Gain error testing.

- 8: Within 1/2 LSB of the final value when code changes from 1/4 of to 3/4 of full scale.

- **9:** This time delay is measured from the falling edge of ACK pulse in I<sup>2</sup>C command to the beginning of V<sub>OUT</sub>. This time delay is not included in the output settling time specification.

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Electrical Specifications:<br>$R_L = 5 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ , $G_X$ |                       |     |                      |      |               | $V_{DD} = +2.7V \text{ to } 5.5V, V_{SS} = 0V,$<br>$P^{\circ}C, V_{IH} = V_{DD}, V_{IL} = V_{SS}.$ |

|------------------------------------------------------------------------------------------|-----------------------|-----|----------------------|------|---------------|----------------------------------------------------------------------------------------------------|

| Parameter                                                                                | Symbol                | Min | Typical              | Max  | Units         | Conditions                                                                                         |

| Analog Output (Output Ar                                                                 | nplifier)             |     | 1 1                  |      |               | •                                                                                                  |

| Output Voltage Swing                                                                     | V <sub>OUT</sub>      |     | FSR                  | _    | V             | Note 7                                                                                             |

| Full Scale Range<br>(Note 7)                                                             | FSR                   | _   | V <sub>DD</sub>      | —    | V             | V <sub>REF</sub> = V <sub>DD</sub><br>FSR = from 0.0V to V <sub>DD</sub>                           |

|                                                                                          |                       | —   | V <sub>REF</sub>     | —    | V             | V <sub>REF</sub> = Internal, G <sub>x</sub> = 1,<br>FSR = from 0.0 V to V <sub>REF</sub>           |

|                                                                                          |                       | —   | 2 * V <sub>REF</sub> |      | V             | V <sub>REF</sub> = Internal, G <sub>x</sub> = 2,<br>FSR = from 0.0V to 2 * V <sub>REF</sub>        |

| Output Voltage<br>Settling Time                                                          | T <sub>SETTLING</sub> |     | 6                    |      | μs            | Note 8                                                                                             |

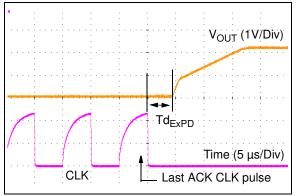

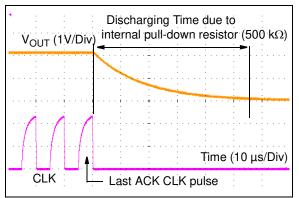

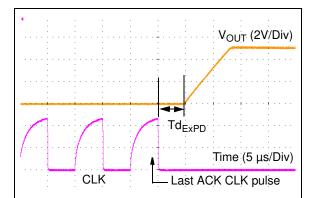

| Analog Output Time Delay<br>from Power-Down Mode                                         | Td <sub>ExPD</sub>    | —   | 4.5                  | —    | μs            | V <sub>DD</sub> = 5V,<br>Note 4, Note 9                                                            |

| Time delay to settle to new reference                                                    | Td <sub>REF</sub>     | _   | 26                   | _    | μs            | From External to Internal<br>Reference                                                             |

| (Note 4, Note 6)                                                                         |                       |     | 44                   |      | μs            | From Internal to External Reference                                                                |

| Power Supply Rejection                                                                   | PSRR                  | —   | -57                  | —    | dB            | V <sub>DD</sub> = 5V ±10%, V <sub>REF</sub> = Internal                                             |

| Capacitive Load Stability                                                                | CL                    | _   | —                    | 1000 | pF            | $R_L = 5 k\Omega$<br>No oscillation, <b>Note 4</b>                                                 |

| Slew Rate                                                                                | SR                    | _   | 0.55                 |      | V/µs          |                                                                                                    |

| Phase Margin                                                                             | р <sub>М</sub>        | _   | 66                   | _    | Degree<br>(°) | $C_L = 400 \text{ pF}, R_L = \infty$                                                               |

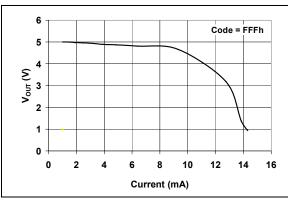

| Short Circuit Current                                                                    | I <sub>SC</sub>       | _   | 15                   | 24   | mA            | $V_{DD} = 5V$ ,<br>All $V_{OUT}$ Pins = Grounded.<br>Tested at room temperature.                   |

| Short Circuit Current<br>Duration                                                        | T <sub>SC_DUR</sub>   |     | Infinite             |      | hours         | Note 4                                                                                             |

| DC Output Impedance                                                                      | R <sub>OUT</sub>      | —   | 1                    | —    | Ω             | Normal mode                                                                                        |

| (Note 4)                                                                                 |                       |     | 1                    | _    | kΩ            | Power-Down mode 1<br>(PD1:PD0 = 0:1), V <sub>OUT</sub> to V <sub>SS</sub>                          |

|                                                                                          |                       | —   | 100                  | —    | kΩ            | Power-Down mode 2<br>(PD1:PD0 = 1:0), V <sub>OUT</sub> to V <sub>SS</sub>                          |

|                                                                                          |                       | —   | 500                  | —    | kΩ            | Power-Down mode 3<br>(PD1:PD0 = 1:1), V <sub>OUT</sub> to V <sub>SS</sub>                          |

**Note 1:** All digital input pins (SDA, SCL,  $\overline{\text{LDAC}}$ ) are tied to "High", Output pins are unloaded, code = 0 x 000.

- 2: The power-up ramp rate measures the rise of V<sub>DD</sub> over time.

- 3: This parameter is ensured by design and not 100% tested.

- 4: This parameter is ensured by characterization and not 100% tested.

- **5**: Test code range: 100 4000 codes,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5.5V$ .

- 6: Time delay to settle to a new reference when switching from external to internal reference or vice versa.

- 7: This parameter is indirectly tested by Offset and Gain error testing.

- 8: Within 1/2 LSB of the final value when code changes from 1/4 of to 3/4 of full scale.

- **9:** This time delay is measured from the falling edge of ACK pulse in I<sup>2</sup>C command to the beginning of V<sub>OUT</sub>. This time delay is not included in the output settling time specification.

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| <b>Electrical Specifications:</b><br>$R_L = 5 k\Omega$ , $C_L = 100 pF$ , $G_2$ |                  |                    |         |                    |       | $V_{DD}$ = +2.7V to 5.5V, $V_{SS}$ = 0V,<br>5°C, $V_{IH}$ = $V_{DD}$ , $V_{IL}$ = $V_{SS}$ . |

|---------------------------------------------------------------------------------|------------------|--------------------|---------|--------------------|-------|----------------------------------------------------------------------------------------------|

| Parameter                                                                       | Symbol           | Min                | Typical | Max                | Units | Conditions                                                                                   |

| Dynamic Performance (N                                                          | lote 4)          | •                  |         |                    |       |                                                                                              |

| Major Code Transition<br>Glitch                                                 |                  | —                  | 45      | —                  | nV-s  | 1 LSB code change around major<br>carry (from 7FFh to 800h)                                  |

| Digital Feedthrough                                                             |                  | —                  | <10     | —                  | nV-s  |                                                                                              |

| Analog Crosstalk                                                                |                  | —                  | <10     | _                  | nV-s  |                                                                                              |

| DAC-to-DAC Crosstalk                                                            |                  | —                  | <10     | _                  | nV-s  |                                                                                              |

| Digital Interface                                                               |                  |                    |         |                    |       |                                                                                              |

| Output Low Voltage                                                              | V <sub>OL</sub>  | —                  | —       | 0.4                | V     | I <sub>OL</sub> = 3 mA<br>SDA and RDY/BSY pins                                               |

| Schmitt Trigger<br>Low Input                                                    | V <sub>IL</sub>  | —                  | —       | 0.3V <sub>DD</sub> | V     | V <sub>DD</sub> > 2.7V.<br>SDA, SCL, LDAC pins                                               |

| Threshold Voltage                                                               |                  | _                  | —       | 0.2V <sub>DD</sub> | V     | $V_{DD} \le 2.7V.$<br>SDA, SCL, LDAC pins                                                    |

| Schmitt Trigger<br>High Input<br>Threshold Voltage                              | V <sub>IH</sub>  | 0.7V <sub>DD</sub> | —       | _                  | V     | SDA, SCL, LDAC pins                                                                          |

| Input Leakage                                                                   | ILI              | —                  | —       | ±1                 | μA    | $SCL = SDA = \overline{LDAC} = V_{DD,}$<br>$SCL = SDA = \overline{LDAC} = V_{SS}$            |

| Pin Capacitance                                                                 | C <sub>PIN</sub> | _                  | _       | 3                  | pF    | Note 4                                                                                       |

| EEPROM                                                                          | •                | -                  |         | -                  | •     | •                                                                                            |

| EEPROM Write Time                                                               | TWRITE           |                    | 25      | 50                 | ms    | EEPROM write time                                                                            |

| Data Retention                                                                  |                  | —                  | 200     |                    | Years | At +25°C, Note 3                                                                             |

| LDAC Input                                                                      |                  |                    |         |                    |       |                                                                                              |

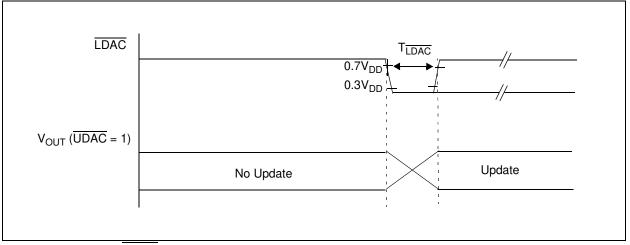

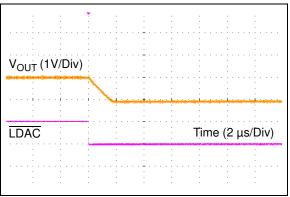

| LDAC Low Time                                                                   | TLDAC            | 210                | _       | _                  | ns    | Updates analog outputs (Note 3)                                                              |

**Note 1:** All digital input pins (SDA, SCL,  $\overline{\text{LDAC}}$ ) are tied to "High", Output pins are unloaded, code = 0 x 000.

2: The power-up ramp rate measures the rise of V<sub>DD</sub> over time.

3: This parameter is ensured by design and not 100% tested.

4: This parameter is ensured by characterization and not 100% tested.

**5**: Test code range: 100 - 4000 codes,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5.5V$ .

6: Time delay to settle to a new reference when switching from external to internal reference or vice versa.

7: This parameter is indirectly tested by Offset and Gain error testing.

8: Within 1/2 LSB of the final value when code changes from 1/4 of to 3/4 of full scale.

**9:** This time delay is measured from the falling edge of ACK pulse in I<sup>2</sup>C command to the beginning of V<sub>OUT</sub>. This time delay is not included in the output settling time specification.

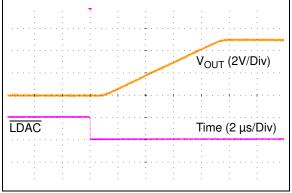

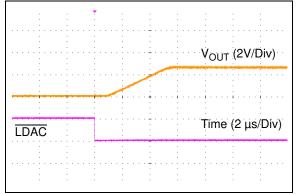

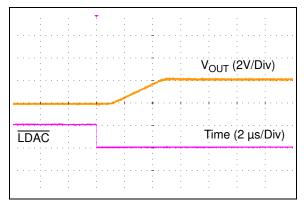

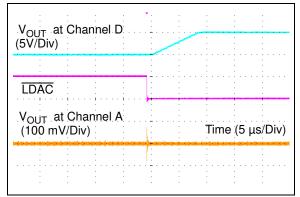

FIGURE 1-2: LDAC Pin Timing vs. V<sub>OUT</sub> Update.

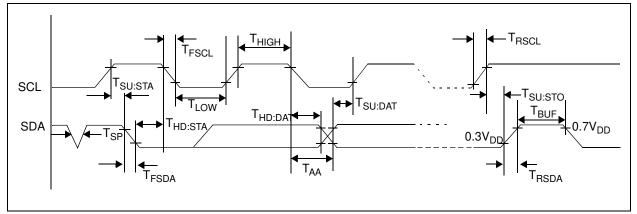

# I<sup>2</sup>C SERIAL TIMING SPECIFICATIONS

|                                                       | dard and Fa         | vise specified<br>st Mode: V <sub>D</sub><br>e: V <sub>DD</sub> = +4. | <sub>D</sub> = +2.7V | to +5.5V | l for T <sub>A</sub> = | -40 to +125°C, V <sub>SS</sub> = 0V,                                       |

|-------------------------------------------------------|---------------------|-----------------------------------------------------------------------|----------------------|----------|------------------------|----------------------------------------------------------------------------|

| Parameters                                            | Sym                 | Min                                                                   | Тур                  | Мах      | Units                  | Conditions                                                                 |

| Clock Frequency                                       | f <sub>SCL</sub>    | 0                                                                     | —                    | 100      | kHz                    | Standard Mode<br>C <sub>b</sub> = 400 pF, 2.7V – 5.5V                      |

|                                                       |                     | 0                                                                     | —                    | 400      | kHz                    | Fast Mode<br>C <sub>b</sub> = 400 pF, 2.7V – 5.5V                          |

|                                                       |                     | 0                                                                     | —                    | 1.7      | MHz                    | High Speed Mode 1.7<br>$C_b = 400 \text{ pF}, 4.5 \text{V} - 5.5 \text{V}$ |

|                                                       |                     | 0                                                                     | —                    | 3.4      | MHz                    | High Speed Mode 3.4 $C_b = 100 \text{ pF}, 4.5 \text{V} - 5.5 \text{V}$    |

| Bus Capacitive Loading                                | Cb                  |                                                                       | —                    | 400      | pF                     | Standard Mode<br>2.7V – 5.5V                                               |

|                                                       |                     | —                                                                     | —                    | 400      | pF                     | Fast Mode<br>2.7V – 5.5V                                                   |

|                                                       |                     | _                                                                     |                      | 400      | pF                     | High Speed Mode 1.7<br>4.5V – 5.5V                                         |

|                                                       |                     | —                                                                     | —                    | 100      | pF                     | High Speed Mode 3.4<br>4.5V – 5.5V                                         |

| Start Condition Setup Time<br>(Start, Repeated Start) | T <sub>SU:STA</sub> | 4700                                                                  |                      | —        | ns                     | Standard Mode                                                              |

|                                                       |                     | 600                                                                   | —                    | —        | ns                     | Fast Mode                                                                  |

|                                                       |                     | 160                                                                   | —                    | —        | ns                     | High Speed Mode 1.7                                                        |

|                                                       |                     | 160                                                                   | —                    | —        | ns                     | High Speed Mode 3.4                                                        |

| Start Condition Hold Time                             | T <sub>HD:STA</sub> | 4000                                                                  |                      | —        | ns                     | Standard Mode                                                              |

|                                                       |                     | 600                                                                   | —                    |          | ns                     | Fast Mode                                                                  |

|                                                       |                     | 160                                                                   | —                    |          | ns                     | High Speed Mode 1.7                                                        |

|                                                       |                     | 160                                                                   | —                    |          | ns                     | High Speed Mode 3.4                                                        |

| Stop Condition Setup Time                             | T <sub>SU:STO</sub> | 4000                                                                  |                      |          | ns                     | Standard Mode                                                              |

|                                                       |                     | 600                                                                   | —                    |          | ns                     | Fast Mode                                                                  |

|                                                       |                     | 160                                                                   |                      | —        | ns                     | High Speed Mode 1.7                                                        |

|                                                       |                     | 160                                                                   |                      | —        | ns                     | High Speed Mode 3.4                                                        |

| Clock High Time                                       | THIGH               | 4000                                                                  |                      | —        | ns                     | Standard Mode                                                              |

|                                                       |                     | 600                                                                   | —                    | —        | ns                     | Fast Mode                                                                  |

|                                                       |                     | 120                                                                   |                      | —        | ns                     | High Speed Mode 1.7                                                        |

|                                                       |                     | 60                                                                    |                      | —        | ns                     | High Speed Mode 3.4                                                        |

| Clock Low Time                                        | TLOW                | 4700                                                                  | _                    | —        | ns                     | Standard Mode                                                              |

|                                                       |                     | 1300                                                                  |                      | —        | ns                     | Fast Mode                                                                  |

|                                                       |                     | 320                                                                   |                      | —        | ns                     | High Speed Mode 1.7                                                        |

|                                                       | [                   | 160                                                                   | _                    | _        | ns                     | High Speed Mode 3.4                                                        |

Note 1: This parameter is ensured by characterization and is not 100% tested.

2: After a Repeated Start condition or an Acknowledge bit.

If this parameter is too short, it can create an unintentional Start or Stop condition to other devices on the I<sup>2</sup>C bus line. If 3: this parameter is too long, the Data Input Setup ( $T_{SU:DAT}$ ) or Clock Low time ( $T_{LOW}$ ) can be affected. Data Input: This parameter must be longer than t<sub>SP</sub>.

**Data Output:** This parameter is characterized, and tested indirectly by testing  $T_{AA}$  parameter.

4: This specification is not a part of the I<sup>2</sup>C specification. This specification is equivalent to the Data Hold Time (T<sub>HD:DAT</sub>) plus SDA Fall (or rise) time:  $T_{AA} = T_{HD:DAT} + T_{FSDA}$  (OR  $T_{RSDA}$ ). Time between Start and Stop conditions.

5:

# I<sup>2</sup>C SERIAL TIMING SPECIFICATIONS (CONTINUED)

| Hiç                       | h Speed Mo          | de: V <sub>DD</sub> = +4. | 5V to +5.5 | V.   | 1     | Γ                               |

|---------------------------|---------------------|---------------------------|------------|------|-------|---------------------------------|

| Parameters                | Sym                 | Min                       | Тур        | Max  | Units | Conditions                      |

| SCL Rise Time             | TRSCL               | —                         | —          | 1000 | ns    | Standard Mode                   |

| (Note 1)                  |                     | 20 + 0.1Cb                | _          | 300  | ns    | Fast Mode                       |

|                           |                     | 20                        | _          | 80   | ns    | High Speed Mode 1.7             |

|                           |                     | 20                        | _          | 160  | ns    | High Speed Mode 1.7<br>(Note 2) |

|                           |                     | 10                        | —          | 40   | ns    | High Speed Mode 3.4             |

|                           |                     | 10                        | —          | 80   | ns    | High Speed Mode 3.4 (Note 2)    |

| SDA Rise Time             | T <sub>RSDA</sub>   | —                         | _          | 1000 | ns    | Standard Mode                   |

| (Note 1)                  |                     | 20 + 0.1Cb                |            | 300  | ns    | Fast Mode                       |

|                           |                     | 20                        | _          | 80   | ns    | High Speed Mode 1.7             |

|                           |                     | 10                        | _          | 40   | ns    | High Speed Mode 3.4             |

| SCL Fall Time<br>(Note 1) | T <sub>FSCL</sub>   | —                         |            | 300  | ns    | Standard Mode                   |

|                           |                     | 20 + 0.1Cb                | _          | 300  | ns    | Fast Mode                       |

|                           |                     | 20                        | —          | 80   | ns    | High Speed Mode 1.7             |

|                           |                     | 10                        |            | 40   | ns    | High Speed Mode 3.4             |

| SDA Fall Time             | T <sub>FSDA</sub>   |                           | _          | 300  | ns    | Standard Mode                   |

| (Note 1)                  |                     | 20 + 0.1Cb                | _          | 300  | ns    | Fast Mode                       |

|                           |                     | 20                        |            | 160  | ns    | High Speed Mode 1.7             |

|                           |                     | 10                        | _          | 80   | ns    | High Speed Mode 3.4             |

| Data Input Setup Time     | T <sub>SU:DAT</sub> | 250                       | _          | _    | ns    | Standard Mode                   |

|                           |                     | 100                       |            | _    | ns    | Fast Mode                       |

|                           |                     | 10                        | _          | —    | ns    | High Speed Mode 1.7             |

|                           |                     | 10                        |            | _    | ns    | High Speed Mode 3.4             |

| Data Hold Time            | T <sub>HD:DAT</sub> | 0                         |            | 3450 | ns    | Standard Mode                   |

| (Input, Output)           |                     | 0                         |            | 900  | ns    | Fast Mode                       |

| (Note 3)                  |                     | 0                         |            | 150  | ns    | High Speed Mode 1.7             |

|                           |                     | 0                         |            | 70   | ns    | High Speed Mode 3.4             |

| Output Valid from Clock   | T <sub>AA</sub>     | 0                         | _          | 3750 | ns    | Standard Mode                   |

| (Note 4)                  |                     | 0                         |            | 1200 | ns    | Fast Mode                       |

|                           |                     | 0                         |            | 310  | ns    | High Speed Mode 1.7             |

|                           |                     | 0                         | _          | 150  | ns    | High Speed Mode 3.4             |

Note 1: This parameter is ensured by characterization and is not 100% tested.

2: After a Repeated Start condition or an Acknowledge bit.

If this parameter is too short, it can create an unintentional Start or Stop condition to other devices on the I<sup>2</sup>C bus line. If 3: this parameter is too long, the Data Input Setup ( $T_{SU:DAT}$ ) or Clock Low time ( $T_{LOW}$ ) can be affected. Data Input: This parameter must be longer than t<sub>SP</sub>. **Data Output:** This parameter is characterized, and tested indirectly by testing  $T_{AA}$  parameter.

4: This specification is not a part of the I<sup>2</sup>C specification. This specification is equivalent to the Data Hold Time (T<sub>HD:DAT</sub>) plus SDA Fall (or rise) time:  $T_{AA} = T_{HD:DAT} + T_{FSDA}$  (OR  $T_{RSDA}$ ). Time between Start and Stop conditions.

5:

# I<sup>2</sup>C SERIAL TIMING SPECIFICATIONS (CONTINUED)

| <b>Electrical Specifications:</b> Unless otherwise specified, all limits are specified for $T_A = -40$ to $+125$ °C, $V_{SS} = 0$ V,<br>Standard and Fast Mode: $V_{DD} = +2.7$ V to $+5.5$ V<br>High Speed Mode: $V_{DD} = +4.5$ V to $+5.5$ V. |                 |      |     |     |       |                                   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----|-----|-------|-----------------------------------|--|--|

| Parameters                                                                                                                                                                                                                                       | Sym             | Min  | Тур | Max | Units | Conditions                        |  |  |

| Bus Free Time                                                                                                                                                                                                                                    | TBUF            | 4700 | _   | —   | ns    | Standard Mode                     |  |  |

| (Note 5)                                                                                                                                                                                                                                         |                 | 1300 | —   | —   | ns    | Fast Mode                         |  |  |

|                                                                                                                                                                                                                                                  |                 | _    | —   | —   | ns    | High Speed Mode 1.7               |  |  |

|                                                                                                                                                                                                                                                  |                 |      | —   | —   | ns    | High Speed Mode 3.4               |  |  |

| Input Filter<br>Spike Suppression<br>(SDA and SCL)<br>(Not Tested)                                                                                                                                                                               | T <sub>SP</sub> | _    | —   | —   | ns    | Standard Mode<br>(Not Applicable) |  |  |

|                                                                                                                                                                                                                                                  |                 | _    | 50  | —   | ns    | Fast Mode                         |  |  |

|                                                                                                                                                                                                                                                  |                 | _    | 10  | —   | ns    | High Speed Mode 1.7               |  |  |

|                                                                                                                                                                                                                                                  |                 |      | 10  | _   | ns    | High Speed Mode 3.4               |  |  |

Note 1: This parameter is ensured by characterization and is not 100% tested.

2: After a Repeated Start condition or an Acknowledge bit.

3: If this parameter is too short, it can create an unintentional Start or Stop condition to other devices on the I<sup>2</sup>C bus line. If this parameter is too long, the Data Input Setup ( $T_{SU:DAT}$ ) or Clock Low time ( $T_{LOW}$ ) can be affected. Data Input: This parameter must be longer than t<sub>SP</sub>. Data Output: This parameter is characterized, and tested indirectly by testing T<sub>AA</sub> parameter.

4: This specification is not a part of the I<sup>2</sup>C specification. This specification is equivalent to the Data Hold Time (T<sub>HD:DAT</sub>) plus SDA Fall (or rise) time:  $T_{AA} = T_{HD:DAT} + T_{FSDA}$  (OR  $T_{RSDA}$ ). Time between Start and Stop conditions.

5:

# **TEMPERATURE CHARACTERISTICS**

| Electrical Specifications: Unless | otherwise i    | ndicated, | $V_{DD} = +2$ | .7V to +5 | 5.5V, V <sub>SS</sub> : | = GND.     |

|-----------------------------------|----------------|-----------|---------------|-----------|-------------------------|------------|

| Parameters                        | Symbol         | Min       | Typical       | Мах       | Units                   | Conditions |

| Temperature Ranges                |                |           |               |           |                         |            |

| Specified Temperature Range       | T <sub>A</sub> | -40       | —             | +125      | °C                      |            |

| Operating Temperature Range       | T <sub>A</sub> | -40       | —             | +125      | °C                      |            |

| Storage Temperature Range         | T <sub>A</sub> | -65       | —             | +150      | °C                      |            |

| Thermal Package Resistances       |                |           |               |           |                         |            |

| Thermal Resistance, 10L-MSOP      | $\theta_{JA}$  |           | 202           |           | °C/W                    |            |

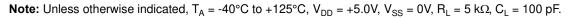

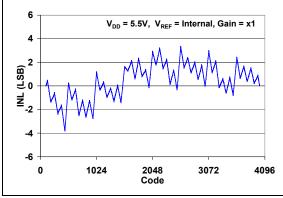

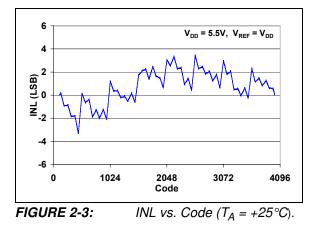

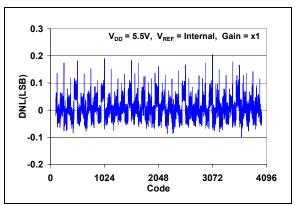

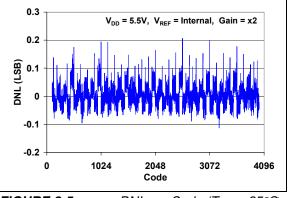

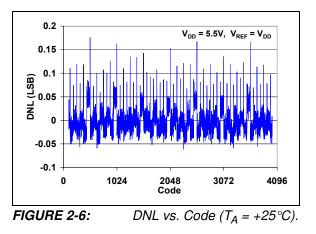

#### 2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

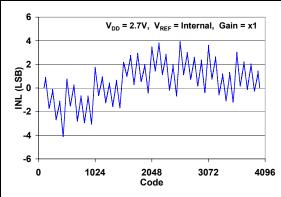

INL vs. Code ( $T_A = +25^{\circ}C$ ). FIGURE 2-1:

FIGURE 2-2:

FIGURE 2-4:

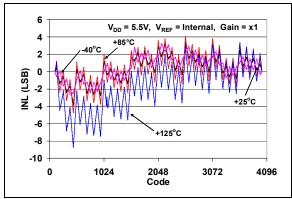

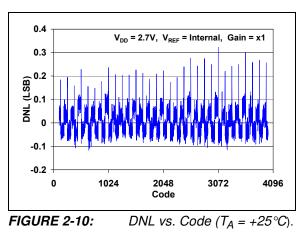

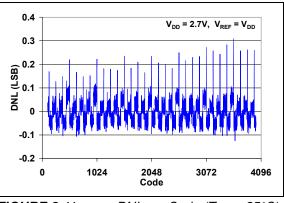

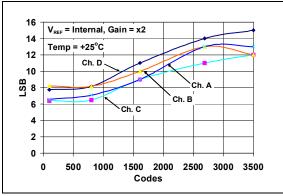

DNL vs. Code ( $T_A = +25 \circ C$ ).

FIGURE 2-5: DNL vs. Code ( $T_A = +25 \circ C$ ).

Note: Unless otherwise indicated, T<sub>A</sub> = -40°C to +125°C, V<sub>DD</sub> = +5.0V, V<sub>SS</sub> = 0V, R<sub>L</sub> = 5 kΩ, C<sub>L</sub> = 100 pF.

INL vs. Code ( $T_A = +25^{\circ}C$ ).

**FIGURE 2-8:** INL vs. Code  $(T_A = +25^{\circ}C)$ .

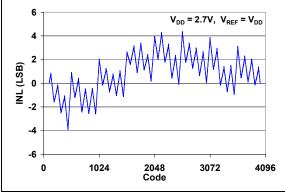

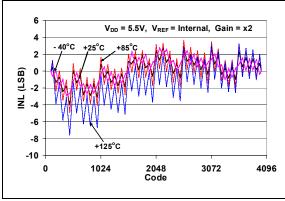

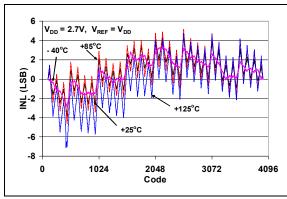

FIGURE 2-9: INL vs. Code and Temperature.

**FIGURE 2-11:** DNL vs. Code  $(T_A = +25 \degree C)$ .

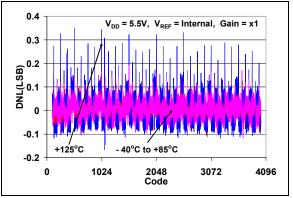

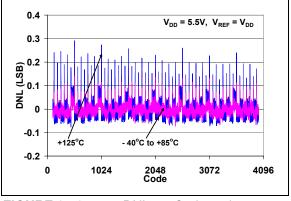

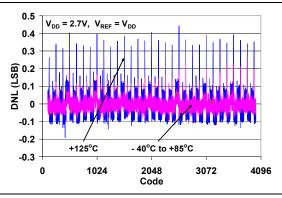

FIGURE 2-12: DNL vs. Code and Temperature.

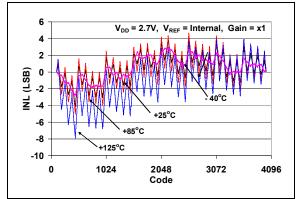

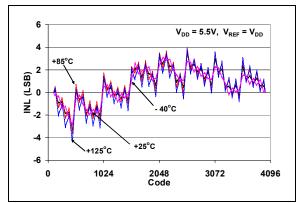

FIGURE 2-14: INL vs. Code and Temperature.

FIGURE 2-15: INL vs. Code and Temperature.

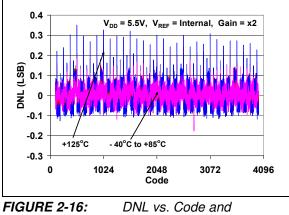

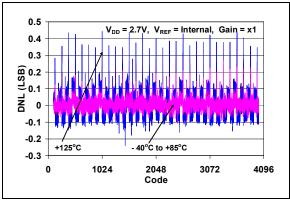

FIGURE 2-16: DNL vs. Code Temperature.

FIGURE 2-17: DNL vs. Code and Temperature.

FIGURE 2-18: DNL vs. Code and Temperature.

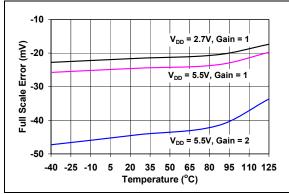

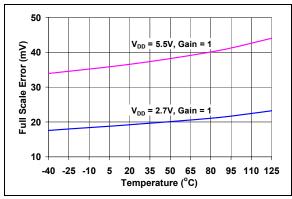

**FIGURE 2-20:** Full Scale Error vs. Temperature (Code = FFFh, V<sub>RFF</sub> = Internal).

FIGURE 2-21:Full Scale Error vs.Temperature (Code = FFFh,  $V_{REF} = V_{DD}$ ).

FIGURE 2-22: DNL vs. Code and Temperature.

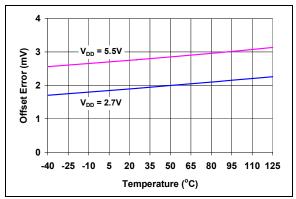

**FIGURE 2-23:** Zero Scale Error vs. Temperature (Code = 000h, V<sub>REF</sub> = Internal).

FIGURE 2-24: Offset Error (Zero Scale Error).

**FIGURE 2-25:** Absolute DAC Output Error  $(V_{DD} = 5.5V)$ .

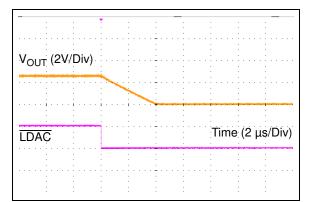

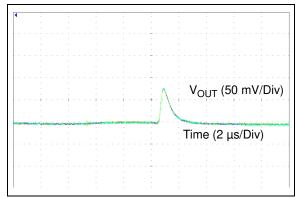

**FIGURE 2-26:** Full <u>Scale</u> Settling Time  $(V_{REF} = V_{DD}, V_{DD} = 5V, UDAC = 1, Code Change: 000h to FFFh).$

**FIGURE 2-27:** Half Scale Settling Time  $(V_{REF} = V_{DD}, V_{DD} = 5V, UDAC = 1, Code Change: 000h to 7FFh).$

**FIGURE 2-28:** Full Scale Settling Time  $(V_{REF} = Internal, V_{DD} = 5V, UDAC = 1, Gain = x1, Code Change: 000h to FFFh).$

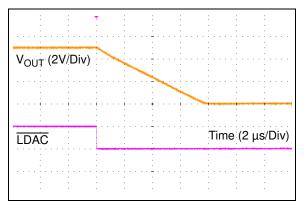

**FIGURE 2-29:** Full <u>Scale</u> Settling Time  $(V_{REF} = V_{DD}, V_{DD} = 5V, UDAC = 1, Code Change: FFFh to 000h).$

**FIGURE 2-30:** Half <u>Scale</u> Settling Time  $(V_{REF} = V_{DD}, V_{DD} = 5V, UDAC = 1,$ Code Change: 7FFh to 000h).

**FIGURE 2-31:** Full Scale Settling Time  $(V_{REF} = Internal, V_{DD} = 5V, UDAC = 1, Gain = x1, Code Change: FFFh to 000h).$

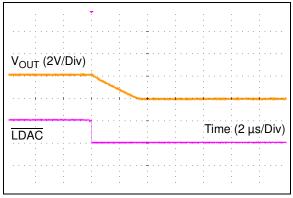

**FIGURE 2-32:** Half Scale Settling Time  $(V_{REF} = Internal, V_{DD} = 5V, UDAC = 1, Gain = x1, Code Change: 000h to 7FFh).$

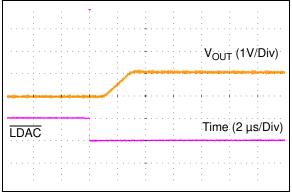

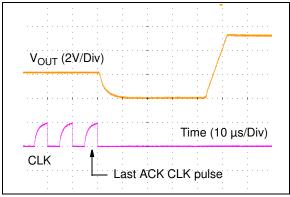

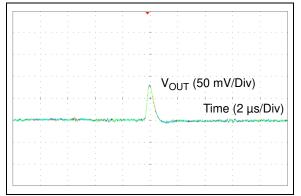

**FIGURE 2-33:** Exiting Power Down Mode (Code: FFFh,  $V_{REF}$  = Internal,  $V_{DD}$  = 5V, Gain = x1, for all Channels.).

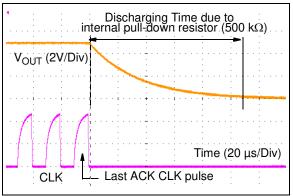

**FIGURE 2-34:** Entering Power Down Mode (Code: FFFh,  $V_{REF}$  = Internal,  $V_{DD}$  = 5V, Gain = x1, PD1 = PD0 = 1, No External Load).

**FIGURE 2-35:** Half Scale Settling Time  $(V_{REF} = Internal, V_{DD} = 5V, UDAC = 1, Gain = x1, Code Change: 7FFh to 000h).$

**FIGURE 2-36:** Exiting Power Down Mode (Code: FFFh,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5V$ , for all Channels).

**FIGURE 2-37:** Entering Power Down Mode (Code: FFFh,  $V_{REF} = V_{DD}$ ,  $V_{DD} = 5V$ , PD1= PD0 = 1, No External Load).

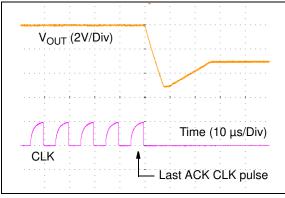

**FIGURE 2-38:**  $V_{OUT}$  Time Delay when  $V_{REF}$  changes from Internal Reference to  $V_{DD}$ .

FIGURE 2-39: $V_{OUT}$  Time Delay when $V_{REF}$  changes from  $V_{DD}$  to Internal Reference.

**FIGURE 2-40:** Channel Cross Talk  $(V_{REF} = V_{DD}, V_{DD} = 5V).$

**FIGURE 2-41:** Code Change Glitch  $(V_{REF} = External, V_{DD} = 5V, No External Load), Code Change: 800h to 7FFh.$

**FIGURE 2-42:** Code Change Glitch  $(V_{REF} = Internal, V_{DD} = 5V, Gain = 1, No External Load), Code Change: 800h to 7FFh.$

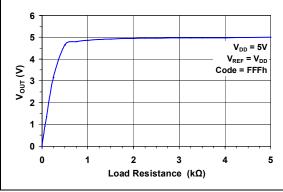

FIGURE 2-43:

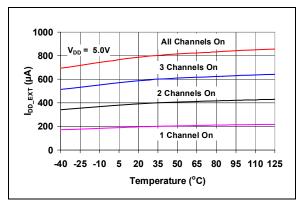

**FIGURE 2-44:**  $I_{DD}$  vs. Temperature  $(V_{REF} = VDD, V_{DD} = 5V, Code = FFFh).$

**FIGURE 2-45:**  $I_{DD}$  vs. Temperature  $(V_{REF} = V_{DD}, V_{DD} = 2.7V, Code = FFFh).$

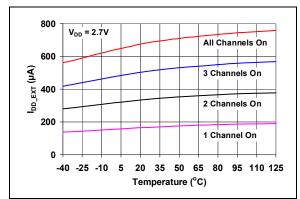

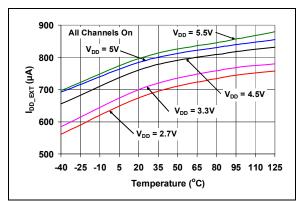

**FIGURE 2-46:**  $I_{DD}$  vs. Temperature ( $V_{REF} = V_{DD}$ , All channels are in Normal Mode, Code = FFFh).

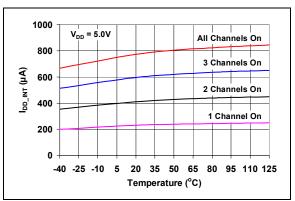

**FIGURE 2-47:**  $I_{DD}$  vs. Temperature ( $V_{REF}$  = Internal,  $V_{REF}$  = 5V, Code = FFFh).

**FIGURE 2-48:**  $I_{DD}$  vs. Temperature  $(V_{REF} = Internal, V_{DD} = 2.7V, Code = FFFh).$

**FIGURE 2-49:**  $I_{DD}$  vs. Temperature ( $V_{REF}$  = Internal, All Channels are in Normal Mode, Code = FFFh).

**FIGURE 2-50:**  $I_{DD}$  vs. Temperature  $(V_{REF} = Internal, All Channels are in Powered Down).$

**FIGURE 2-51:** Source Current Capability  $(V_{REF} = V_{DD}, Code = FFFh).$

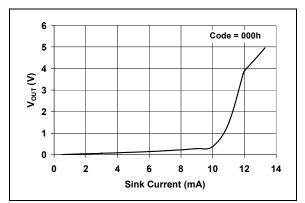

**FIGURE 2-52:** Sink Current Capability  $(V_{REF} = V_{DD}, Code = 000h).$

NOTES:

# 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

| Pin No. | Name               | Pin Type | Function                                                                                                                                                                                                                                                        |

|---------|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>    | Р        | Supply Voltage                                                                                                                                                                                                                                                  |

| 2       | SCL                | OI       | I <sup>2</sup> C Serial Clock Input (Note 1)                                                                                                                                                                                                                    |

| 3       | SDA                | OI/OO    | I <sup>2</sup> C Serial Data Input and Output (Note 1)                                                                                                                                                                                                          |

| 4       | LDAC               | ST       | This pin is used for two purposes:<br>(a) Synchronization Input. It is used to transfer the contents of the DAC input registers to the output registers ( $V_{OUT}$ ).<br>(b) Select the device for reading and writing I <sup>2</sup> C address bits. (Note 2) |

| 5       | RDY/BSY            | 00       | This pin is a status indicator of EEPROM programming activity. An external pull-up resistor (about 100 k $\Omega$ ) is needed from RDY/BSY pin to V <sub>DD</sub> line. (Note 1)                                                                                |

| 6       | V <sub>OUT</sub> A | AO       | Buffered analog voltage output of channel A. The output amplifier has rail-to-rail operation.                                                                                                                                                                   |

| 7       | V <sub>OUT</sub> B | AO       | Buffered analog voltage output of channel B. The output amplifier has rail-to-rail operation.                                                                                                                                                                   |

| 8       | V <sub>OUT</sub> C | AO       | Buffered analog voltage output of channel C. The output amplifier has rail-to-rail operation.                                                                                                                                                                   |

| 9       | V <sub>OUT</sub> D | AO       | Buffered analog voltage output of channel D. The output amplifier has rail-to-rail operation.                                                                                                                                                                   |

| 10      | V <sub>SS</sub>    | Р        | Ground reference.                                                                                                                                                                                                                                               |

#### TABLE 3-1: PIN FUNCTION TABLE

Legend: P = Power, OI = Open-Drain Input, OO = Open-Drain Output, ST = Schmitt Trigger Input Buffer, AO = Analog Output

- Note 1: This pin needs an external pull-up resistor from V<sub>DD</sub> line. Leave this pin float if it is not used.

- 2: This pin can be driven by MCU.

# 3.1 Supply Voltage Pins (V<sub>DD</sub>, V<sub>SS</sub>)

$V_{DD}$  is the power supply pin for the device. The voltage at the  $V_{DD}$  pin is used as a power supply input as well as a DAC external reference. The power supply at the  $V_{DD}$  pin should be as clean as possible for a good DAC performance.

It is recommended to use an appropriate bypass capacitor of about 0.1  $\mu F$  (ceramic) to ground. An additional 10  $\mu F$  capacitor (tantalum) in parallel is also recommended to further attenuate high-frequency noise present in application boards. The supply voltage (V<sub>DD</sub>) must be maintained in the 2.7V to 5.5V range for specified operation.

$V_{\rm SS}$  is the ground pin and the current return path of the device. The user must connect the  $V_{\rm SS}$  pin to a ground plane through a low-impedance connection. If an analog ground path is available in the application printed circuit board (PCB), it is highly recommended that the  $V_{\rm SS}$  pin be tied to the analog ground path, or isolated within an analog ground plane of the circuit board.

# 3.2 Serial Clock Pin (SCL)

SCL is the serial clock pin of the I<sup>2</sup>C interface. The MCP4728 device acts only as a slave and the SCL pin accepts only external input serial clocks. The input data from the Master device is shifted into the SDA pin on the rising edges of the SCL clock, and output from the MCP4728 occurs at the falling edges of the SCL clock.

The SCL pin is an open-drain N-channel driver. Therefore, it needs a pull-up resistor from the  $V_{\rm DD}$  line to the SCL pin.

Refer to **Section 5.0** "I<sup>2</sup>C **Serial Interface Communications**" for more details on I<sup>2</sup>C Serial Interface communication.

Typical range of the pull-up resistor value for SCL and SDA is from 5 k $\Omega$  to 10 k $\Omega$  for Standard (100 kHz) and Fast (400 kHz) modes, and less than 1 k $\Omega$  for High Speed mode (3.4 MHz).

#### 3.3 Serial Data Pin (SDA)

SDA is the serial data pin of the  $I^2C$  interface. The SDA pin is used to write or read the DAC register and EEPROM data. Except for Start and Stop conditions, the data on the SDA pin must be stable during the high duration of the clock pulse. The High or Low state of the SDA pin can only change when the clock signal on the SCL pin is Low.

The SDA pin is an open-drain N-channel driver. Therefore, it needs a pull-up resistor from the  $V_{\text{DD}}$  line to the SDA pin.

Refer to **Section 5.0** "I<sup>2</sup>C **Serial Interface Communications**" for more details on the I<sup>2</sup>C Serial Interface communication.

#### 3.4 LDAC Pin

This pin can be driven by an external control device such as an MCU I/O pin. This pin is used to:

- a) transfer the contents of the input registers to their corresponding DAC output registers and

- b) select a device of interest when reading or writing  $l^2C$  address bits.

For more details on reading and writing the I<sup>2</sup>C address bits, see Section 5.4.4 "General Call Read Address Bits" and Section 5.6.8 "Write Command: Write I2C Address bits (C2=0, C1=1, C0=1)".

When the logic status of the  $\overline{\text{LDAC}}$  pin changes from "High" to "Low", the contents of all input registers (Channels A – D) are transferred to their corresponding output registers, and all analog voltage outputs are updated simultaneously.

If this pin is permanently tied to "Low", the content of the input register is transferred to its output register ( $V_{OUT}$ ) immediately at the last input data byte's acknowledge pulse.

The user can also use the UDAC bit instead. However, the UDAC bit updates a selected channel only. See **Section 4.8 "Output Voltage Update**" for more information on the LDAC pin and UDAC bit functions.

#### 3.5 RDY/BSY Status Indicator Pin

This pin is a status indicator of EEPROM programming activity. This pin is "High" when the EEPROM has no programming activity, and "Low" when the EEPROM is in programming mode. It goes "High" when the EEPROM program is completed.

The RDY/BSY pin is an open-drain N-channel driver. Therefore, it needs a pull-up resistor (about 100 k $\Omega$ ) from the V<sub>DD</sub> line to the RDY/BSY pin. Let this pin float if it is not used.

#### 3.6 Analog Output Voltage Pins (V<sub>OUT</sub> A, V<sub>OUT</sub> B, V<sub>OUT</sub> C, V<sub>OUT</sub> D)

The device has four analog voltage output (V<sub>OUT</sub>) pins. Each output is driven by its own output buffer with a gain of 1 or 2, depending on the gain and V<sub>REF</sub> selection bit settings. In Normal mode, the DC impedance of the output pin is about 1 $\Omega$ . In Power-Down mode, the output pin is internally connected to 1 k $\Omega$ , 100 k $\Omega$ , or 500 k $\Omega$ , depending on the Power-Down selection bit settings.

The  $V_{OUT}$  pin can drive up to 1000 pF of capacitive load. It is recommended to use a load with  $R_L$  greater than 5 k $\Omega.$

### 4.0 THEORY OF DEVICE OPERATION

The MCP4728 device is a 12-bit 4-channel buffered voltage output DAC with nonvolatile memory (EEPROM). The user can program the EEPROM with  $I^2C$  address bits, configuration and DAC input data of each channel. The device has an internal charge pump circuit to provide the programming voltage of the EEPROM.

When the device is first powered-up, it automatically loads the stored data in its EEPROM to the DAC input and output registers, and provides analog outputs with the saved settings immediately. This event does not require an LDAC or UDAC bit condition. After the device is powered-up, the user can update the input registers using  $I^2C$  write commands. The analog <u>outputs</u> can be updated with new register values if the LDAC pin or UDAC bit is low. The DAC output of each channel is buffered with a low power and precision output amplifier. This amplifier provides a rail-to-rail output with low offset voltage and low noise.

The device uses a resistor string architecture. The resistor ladder DAC can be driven from  $V_{DD}$  or internal  $V_{REF}$ , depending on the reference selection. The user can select internal (2.048V) or external reference ( $V_{DD}$ ) for each DAC channel individually by software control. The  $V_{DD}$  is used as the external reference. Each channel is controlled and operated independently.

The device has a Power-Down mode feature. Most of the circuit in each powered down channel are turned off. Therefore, operating power can be saved significantly by putting any unused channel to the Power-Down mode.

#### 4.1 Power-on Reset (POR)

The device contains an internal Power-on Reset (POR) circuit that monitors power supply voltage ( $V_{DD}$ ) during operation. This circuit ensures correct device start-up at system power-up and power-down events.

If the power supply voltage is less than the POR threshold ( $V_{POR} = 2V$ , typical), all circuits are disabled and there will be no analog output. When the  $V_{DD}$  increases above the  $V_{POR}$ , the device takes a reset state. During the reset period, each channel uploads all configuration and DAC input codes from EEPROM, and analog output ( $V_{OUT}$ ) will be available accordingly. This enables the device to return to the same state that it was at the last write to the EEPROM, before it was powered off. The POR status is monitored by the POR status bit by using the I<sup>2</sup>C read command. See Figure 5-15 for the details of the POR status bit.

#### 4.2 Reset Conditions

The device can be reset by two independent events:

- a) by Power-on Reset

- b) by I<sup>2</sup>C General Call Reset Command

Under the reset conditions, the device uploads the EEPROM data into both of the DAC input and output registers simultaneously. The analog output voltage of each channel is available immediately, regardless of the LDAC and UDAC bit conditions.

The factory default settings for the EEPROM prior to the device shipment are shown in Table 4-2.

# 4.3 Output Amplifier

The DAC output is buffered with a low power precision amplifier. This amplifier provides low offset voltage and low noise, as well as rail-to-rail output.

The output amplifier can drive the resistive and high capacitive loads without oscillation. The amplifier can provide a maximum load current of 24 mA, which is enough for most of programmable voltage reference applications. Refer to **Section 1.0 "Electrical Characteristics**" for the specifications of the output amplifier.

#### 4.3.1 PROGRAMMABLE GAIN BLOCK

The rail-to-rail output amplifier of each channel has configurable gain option. When the internal voltage reference is selected, the output amplifier gain has two selection options: Gain of 1 or Gain of 2.

When the external reference is selected ( $V_{REF} = V_{DD}$ ), the Gain of 2 option is disabled, and only the Gain of 1 is used by default.

#### 4.3.1.1 Resistive and Capacitive Loads

The analog output (V<sub>OUT</sub>) pin is capable of driving capacitive loads up to 1000 pF in parallel with 5 k $\Omega$  load resistance. Figure 2-43 shows the V<sub>OUT</sub> vs. Resistive Load.

#### 4.4 DAC Input Registers and Non-Volatile EEPROM Memory

Each channel has its own volatile DAC input register and EEPROM. The details of the input registers and EEPROM are shown in Table 4-1 and Table 4-2, respectively.

| TABLE 4-1: | INPUT REGISTER MAP (VOLATILE) |

|------------|-------------------------------|

|------------|-------------------------------|

|                 | Configuration Bits |                                              |    |    |      |      |                            | DAC Input Data (12 bits) |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

|-----------------|--------------------|----------------------------------------------|----|----|------|------|----------------------------|--------------------------|-----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Bit             | <u>RDY</u><br>/BSY | A2                                           | A1 | A0 | VREF | DAC1 | DAC0                       | PD1                      | PD0 | Gx | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Name            | /B21               |                                              |    |    |      |      |                            |                          |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

| Bit<br>Function | (Note 1)           | I <sup>2</sup> C<br>Address Bits<br>(Note 2) |    |    |      |      | Gain<br>Select<br>(Note 2) | (Note 2)                 |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

| CH. A           |                    |                                              |    |    |      |      |                            |                          |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

| CH. B           |                    |                                              |    |    |      |      |                            |                          |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

| CH. C           |                    |                                              |    |    |      |      |                            |                          |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

| CH. D           |                    |                                              |    |    |      |      |                            |                          |     |    |     |     |    |    |    |    |    |    |    |    |    |    |

**Note 1:** EEPROM write status indication bit (flag).

2: Loaded from EEPROM during power-up, or can be updated by the user.

#### TABLE 4-2: EEPROM MEMORY MAP AND FACTORY DEFAULT SETTINGS

|                 | Configuration Bits                        |    |    |                            |              |     |    |     | DAC Input Data (12 bits) |    |    |    |    |    |    |    |    |    |    |

|-----------------|-------------------------------------------|----|----|----------------------------|--------------|-----|----|-----|--------------------------|----|----|----|----|----|----|----|----|----|----|

| Bit Name        | A2                                        | A1 | A0 | VREF                       | PD1          | PD0 | Gx | D11 | D10                      | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Bit<br>Function | I <sup>2</sup> C Address Bits<br>(Note 1) |    |    | Ref.<br>Select<br>(Note 2) | Power<br>Sel |     |    |     |                          |    |    |    |    |    |    |    |    |    |    |

| CH. A           | 0                                         | 0  | 0  | 1                          | 0            | 0   | 0  | 0   | 0                        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| CH. B           |                                           |    |    | 1                          | 0            | 0   | 0  | 0   | 0                        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| CH. C           |                                           |    |    | 1                          | 0            | 0   | 0  | 0   | 0                        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| CH. D           |                                           |    |    | 1                          | 0            | 0   | 0  | 0   | 0                        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

**Note 1:** Device I<sup>2</sup>C address bits. The user can also specify these bits during the device ordering process. The factory default setting is "000". These bits can be reprogrammed by the user using the I<sup>2</sup>C Address Write command.

**2:** Voltage Reference Select: **0** = External  $V_{REF}$  (V<sub>DD</sub>), **1** = Internal  $V_{REF}$  (2.048V).

**3:** Gain Select: **0** = Gain of 1, **1** = Gain of 2.

| Bit Name         | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY/BSY          | This is a status indicator (flag) of EEPROM programming activity:<br><b>1</b> = EEPROM is not in programming mode<br><b>0</b> = EEPROM is in programming mode<br><b>Note:</b> RDY/BSY status can also be monitored at the RDY/BSY pin.                                                                                                                                                                                                                     |

| (A2, A1, A0)     | Device I <sup>2</sup> C address bits. See Section 5.3 "MCP4728 Device Addressing" for more details.                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>REF</sub> | Voltage Reference Selection bit:<br>$0 = V_{DD}$<br>1 = Internal voltage reference (2.048V)<br><b>Note:</b> Internal voltage reference circuit is turned off if all channels select external reference<br>( $V_{REF} = V_{DD}$ ).                                                                                                                                                                                                                          |

| DAC1, DAC0       | DAC Channel Selection bits:<br>00 = Channel A<br>01 = Channel B<br>10 = Channel C<br>11 = Channel D                                                                                                                                                                                                                                                                                                                                                        |

| PD1, PD0         | Power-Down selection bits:<br>00 = Normal Mode<br>01 = $V_{OUT}$ is loaded with 1 k $\Omega$ resistor to ground. Most of the channel circuits are powered off.<br>10 = $V_{OUT}$ is loaded with 100 k $\Omega$ resistor to ground. Most of the channel circuits are powered off.<br>11 = $V_{OUT}$ is loaded with 500 k $\Omega$ resistor to ground. Most of the channel circuits are powered off.<br>Note: See Table 4-7 and Figure 4-1 for more details. |