# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

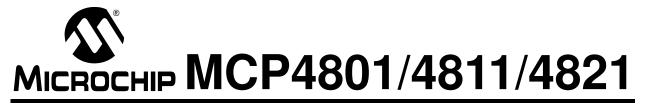

## 8/10/12-Bit Voltage Output Digital-to-Analog Converter with Internal V<sub>REF</sub> and SPI Interface

#### Features

- MCP4801: 8-Bit Voltage Output DAC

- MCP4811: 10-Bit Voltage Output DAC

- MCP4821: 12-Bit Voltage Output DAC

- Rail-to-Rail Output

- · SPI Interface with 20 MHz Clock Support

- Simultaneous Latching of the DAC Output with LDAC Pin

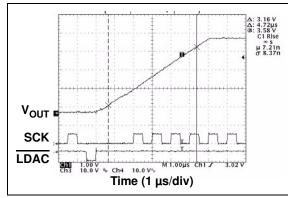

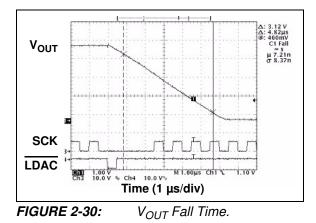

- Fast Settling Time of 4.5 μs

- Selectable Unity or 2x Gain Output

- 2.048V Internal Voltage Reference

- 50 ppm/°C V<sub>REF</sub> Temperature Coefficient

- 2.7V to 5.5V Single-Supply Operation

- Extended Temperature Range: -40°C to +125°C

## Applications

- · Set Point or Offset Trimming

- Sensor Calibration

- Precision Selectable Voltage Reference

- Portable Instrumentation (Battery-Powered)

- · Calibration of Optical Communication Devices

### Related Products<sup>(1)</sup>

| P/N     | DAC<br>Resolution | No. of<br>Channel | Voltage<br>Reference<br>(V <sub>REF</sub> ) |  |  |  |

|---------|-------------------|-------------------|---------------------------------------------|--|--|--|

| MCP4801 | 8                 | 1                 |                                             |  |  |  |

| MCP4811 | 10                | 1                 |                                             |  |  |  |

| MCP4821 | 12                | 1                 | Internal                                    |  |  |  |

| MCP4802 | 8                 | 2                 | (2.048V)                                    |  |  |  |

| MCP4812 | 10                | 2                 |                                             |  |  |  |

| MCP4822 | 12                | 2                 |                                             |  |  |  |

| MCP4901 | 8                 | 1                 |                                             |  |  |  |

| MCP4911 | 10                | 1                 |                                             |  |  |  |

| MCP4921 | 12                | 1                 | External                                    |  |  |  |

| MCP4902 | 8                 | 2                 | External                                    |  |  |  |

| MCP4912 | 10                | 2                 |                                             |  |  |  |

| MCP4922 | 12                | 2                 |                                             |  |  |  |

Note 1: The products listed here have similar AC/DC performances.

## Description

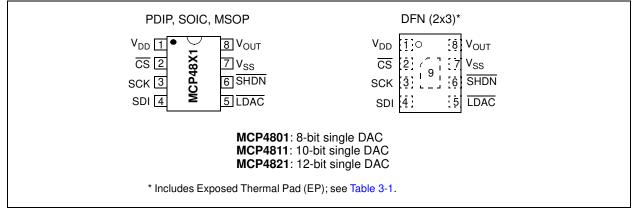

The MCP4801/4811/4821 devices are single channel 8-bit, 10-bit and 12-bit buffered voltage output Digital-to-Analog Converters (DACs), respectively. The devices operate from a single 2.7V to 5.5V supply with an SPI compatible Serial Peripheral Interface.

The devices have a high precision internal voltage reference ( $V_{REF} = 2.048V$ ). The user can configure the full-scale range of the device to be 2.048V or 4.096V by setting the Gain Selection Option bit (gain of 1 of 2).

The devices can be operated in Active or Shutdown mode by setting a Configuration register bit or using the SHDN pin. In Shutdown mode, most of the internal circuits, including the output amplifier, are turned off for power savings, while the amplifier output (V<sub>OUT</sub>) stage is configured to present a known high resistance output load (500 k $\Omega$ , typical).

The devices include double-buffered registers, allowing a synchronous update of the DAC output using the LDAC pin. These devices also incorporate a Power-on Reset (POR) circuit to ensure reliable power-up.

The devices utilize a resistive string architecture, with its inherent advantages of low DNL error, low ratio metric temperature coefficient and fast settling time. These devices are specified over the extended temperature range ( $+125^{\circ}$ C).

The devices provide high accuracy and low noise performance for consumer and industrial applications where calibration or compensation of signals (such as temperature, pressure and humidity) are required.

The MCP4801/4811/4821 devices are available in the PDIP, SOIC, MSOP and DFN packages.

## MCP4801/4811/4821

## **Package Types**

#### **Block Diagram**

## 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| V <sub>DD</sub>                                                    |  |

|--------------------------------------------------------------------|--|

| All inputs and outputs $V_{SS}\!-\!0.3V$ to $V_{DD}\!+\!0.3V$      |  |

| Current at Input Pins±2 mA                                         |  |

| Current at Supply Pins±50 mA                                       |  |

| Current at Output Pins±25 mA                                       |  |

| Storage temperature65°C to +150°C                                  |  |

| Ambient temp. with power applied55°C to +125°C                     |  |

| ESD protection on all pins $\geq 4 \ kV \ (HBM), \geq 400V \ (MM)$ |  |

| Maximum Junction Temperature $(T_J) . \ldots + 150^{\circ}C$       |  |

**†** Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

| Electrical Specifications: Unless<br>Output Buffer Gain (G) = 2x, RL = | s otherwise ind<br>5 k $\Omega$ to GND, | icated, V <sub>E</sub><br>C <sub>L</sub> = 100 | <sub>DD</sub> = 5V, V <sub>SS</sub> = pF, T <sub>A</sub> = -40 f | = 0V, V <sub>RE</sub><br>to +85°C. | <sub>F</sub> = 2.048V,<br>Typical value: | s are at +25°C.                                                                                   |

|------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------|------------------------------------------------------------------|------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|

| Parameters                                                             | Sym                                     | Min                                            | Тур                                                              | Max                                | Units                                    | Conditions                                                                                        |

| Power Requirements                                                     |                                         |                                                |                                                                  |                                    |                                          |                                                                                                   |

| Operating Voltage                                                      | V <sub>DD</sub>                         | 2.7                                            | _                                                                | 5.5                                |                                          |                                                                                                   |

| Operating Current                                                      | I <sub>DD</sub>                         | _                                              | 330                                                              | 400                                | μΑ                                       | All digital inputs are grounded,<br>analog output (V <sub>OUT</sub> ) is<br>unloaded. Code = 000h |

| Hardware Shutdown Current                                              | I <sub>SHDN</sub>                       | —                                              | 0.3                                                              | 2                                  | μA                                       | POR circuit is turned off                                                                         |

| Software Shutdown Current                                              | I <sub>SHDN_SW</sub>                    | —                                              | 3.3                                                              | 6                                  | μA                                       | POR circuit remains turned on                                                                     |

| Power-on Reset Threshold                                               | V <sub>POR</sub>                        | —                                              | 2.0                                                              |                                    | V                                        |                                                                                                   |

| DC Accuracy                                                            |                                         |                                                |                                                                  |                                    |                                          |                                                                                                   |

| MCP4801                                                                |                                         |                                                |                                                                  |                                    |                                          |                                                                                                   |

| Resolution                                                             | n                                       | 8                                              | _                                                                | —                                  | Bits                                     |                                                                                                   |

| INL Error                                                              | INL                                     | -1                                             | ±0.125                                                           | 1                                  | LSb                                      |                                                                                                   |

| DNL                                                                    | DNL                                     | -0.5                                           | ±0.1                                                             | +0.5                               | LSb                                      | Note 1                                                                                            |

| MCP4811                                                                |                                         |                                                |                                                                  |                                    |                                          |                                                                                                   |

| Resolution                                                             | n                                       | 10                                             | —                                                                | —                                  | Bits                                     |                                                                                                   |

| INL Error                                                              | INL                                     | -3.5                                           | ±0.5                                                             | 3.5                                | LSb                                      |                                                                                                   |

| DNL                                                                    | DNL                                     | -0.5                                           | ±0.1                                                             | +0.5                               | LSb                                      | Note 1                                                                                            |

| MCP4821                                                                |                                         |                                                |                                                                  |                                    |                                          |                                                                                                   |

| Resolution                                                             | n                                       | 12                                             | —                                                                | —                                  | Bits                                     |                                                                                                   |

| INL Error                                                              | INL                                     | -12                                            | ±2                                                               | 12                                 | LSb                                      |                                                                                                   |

| DNL                                                                    | DNL                                     | -0.75                                          | ±0.2                                                             | +0.75                              | LSb                                      | Note 1                                                                                            |

| Offset Error                                                           | V <sub>OS</sub>                         | -1                                             | ±0.02                                                            | 1                                  | % of FSR                                 | Code = 0x000h                                                                                     |

| Offset Error Temperature                                               | V <sub>OS</sub> /°C                     | —                                              | 0.16                                                             | —                                  | ppm/°C                                   | -45°C to +25°C                                                                                    |

| Coefficient                                                            | VOS/ C                                  |                                                | -0.44                                                            | —                                  | ppm/°C                                   | +25°C to +85°C                                                                                    |

| Gain Error                                                             | 9e                                      | -2                                             | -0.10                                                            | 2                                  | % of FSR                                 | Code = 0xFFFh,<br>not including offset error                                                      |

| Gain Error Temperature<br>Coefficient                                  | ∆G/°C                                   | —                                              | -3                                                               | —                                  | ppm/°C                                   |                                                                                                   |

Note 1: Guaranteed monotonic by design over all codes.

2: This parameter is ensured by design, and not 100% tested.

## ELECTRICAL CHARACTERISTICS (CONTINUED)

| <b>Electrical Specifications:</b> Unles<br>Output Buffer Gain (G) = 2x, RL = |                                  |       |                                  |       |                   | s are at +25°C.                                                                                 |

|------------------------------------------------------------------------------|----------------------------------|-------|----------------------------------|-------|-------------------|-------------------------------------------------------------------------------------------------|

| Parameters                                                                   | Sym                              | Min   | Тур                              | Max   | Units             | Conditions                                                                                      |

| Internal Voltage Reference (                                                 | V <sub>REF</sub> )               |       |                                  |       |                   |                                                                                                 |

| Internal Reference Voltage                                                   | V <sub>REF</sub>                 | 2.008 | 2.048                            | 2.088 | V                 | V <sub>OUT</sub> when G = 1x and<br>Code = 0xFFFh                                               |

| Temperature Coefficient                                                      |                                  | —     | 125                              | 325   | ppm/°C            | -40°C to 0°C                                                                                    |

| (Note 2)                                                                     | AV /ºC                           | _     | 0.25                             | 0.65  | LSb/°C            | -40°C to 0°C                                                                                    |

|                                                                              | ∆V <sub>REF</sub> /°C            | _     | 45                               | 160   | ppm/°C            | 0°C to +85°C                                                                                    |

|                                                                              |                                  | _     | 0.09                             | 0.32  | LSb/°C            | 0°C to +85°C                                                                                    |

| Output Noise (V <sub>REF</sub> Noise)                                        | E <sub>NREF</sub><br>(0.1-10 Hz) |       | 290                              |       | μV <sub>p-p</sub> | Code = 0xFFFh, G = 1x                                                                           |

| Output Noise Density                                                         | e <sub>NREF</sub><br>(1 kHz)     | —     | 1.2                              | —     | µV/√Hz            | Code = 0xFFFh, G = 1x                                                                           |

|                                                                              | e <sub>NREF</sub><br>(10 kHz)    | —     | 1.0                              | _     | µV/√Hz            | Code = 0xFFFh, G = 1x                                                                           |

| 1/f Corner Frequency                                                         | f <sub>CORNER</sub>              | —     | 400                              | —     | Hz                |                                                                                                 |

| Output Amplifier                                                             |                                  |       |                                  |       |                   |                                                                                                 |

| Output Swing                                                                 | V <sub>OUT</sub>                 | _     | 0.01 to<br>V <sub>DD</sub> -0.04 | _     | V                 | Accuracy is better than 1 LSb<br>for $V_{OUT} = 10 \text{ mV}$ to<br>$(V_{DD} - 40 \text{ mV})$ |

| Phase Margin                                                                 | PM                               | —     | 66                               | _     | Degree (°)        | $C_L = 400 \text{ pF}, R_L = \infty$                                                            |

| Slew Rate                                                                    | SR                               | —     | 0.55                             | —     | V/µs              |                                                                                                 |

| Short Circuit Current                                                        | I <sub>SC</sub>                  | _     | 15                               | 24    | mA                |                                                                                                 |

| Settling Time                                                                | <sup>t</sup> SETTLING            | —     | 4.5                              | —     | μs                | Within 1/2 LSb of final value<br>from 1/4 to 3/4 full-scale range                               |

| Dynamic Performance (Note                                                    | e 2)                             |       |                                  |       |                   |                                                                                                 |

| Major Code Transition Glitch                                                 |                                  | —     | 45                               | —     | nV-s              | 1 LSb change around major<br>carry (01111111 to<br>10000000)                                    |

| Digital Feedthrough                                                          |                                  |       | <10                              |       | nV-s              |                                                                                                 |

Note 1: Guaranteed monotonic by design over all codes.

2: This parameter is ensured by design, and not 100% tested.

## ELECTRICAL CHARACTERISTIC WITH EXTENDED TEMPERATURE

**Electrical Specifications:** Unless otherwise indicated,  $V_{DD} = 5V$ ,  $V_{SS} = 0V$ ,  $V_{REF} = 2.048V$ , Output Buffer Gain (G) = 2x,  $R_L = 5 k\Omega$  to GND,  $C_L = 100 \text{ pF}$ . Typical values are at +125°C by characterization or simulation.

| $R_L = 5 \text{ k}\Omega \text{ to GND}, C_L = 100 \text{ pF}.$ | Typical values a                   | re at +12                             | 5°C by chara | cterizatior           | n or simulatior | 1.                                                                                                |  |  |

|-----------------------------------------------------------------|------------------------------------|---------------------------------------|--------------|-----------------------|-----------------|---------------------------------------------------------------------------------------------------|--|--|

| Parameters                                                      | Sym                                | Min                                   | Тур          | Мах                   | Units           | Conditions                                                                                        |  |  |

| Power Requirements                                              |                                    |                                       |              |                       |                 |                                                                                                   |  |  |

| Operating Voltage                                               | V <sub>DD</sub>                    | 2.7                                   | _            | 5.5                   |                 |                                                                                                   |  |  |

| Operating Current                                               | I <sub>DD</sub>                    | _                                     | 350          | —                     | μA              | All digital inputs are grounded,<br>analog output (V <sub>OUT</sub> ) is<br>unloaded. Code = 000h |  |  |

| Hardware Shutdown<br>Current                                    | I <sub>SHDN</sub>                  | _                                     | 1.5          | —                     | μΑ              | POR circuit is turned off                                                                         |  |  |

| Software Shutdown Current                                       | I <sub>SHDN_SW</sub>               |                                       | 5            | —                     | μA              | POR circuit remains turned on                                                                     |  |  |

| Power-on Reset threshold                                        | V <sub>POR</sub>                   | —                                     | 1.85         | —                     | V               |                                                                                                   |  |  |

| DC Accuracy                                                     |                                    |                                       |              |                       |                 |                                                                                                   |  |  |

| MCP4801                                                         |                                    |                                       |              |                       |                 |                                                                                                   |  |  |

| Resolution                                                      | n                                  | 8                                     | _            | —                     | Bits            |                                                                                                   |  |  |

| INL Error                                                       | INL                                | _                                     | ±0.25        |                       | LSb             |                                                                                                   |  |  |

| DNL                                                             | DNL                                | _                                     | ±0.2         | _                     | LSb             | Note 1                                                                                            |  |  |

| MCP4811                                                         |                                    |                                       |              | •                     |                 | •                                                                                                 |  |  |

| Resolution                                                      | n                                  | 10                                    | _            | —                     | Bits            |                                                                                                   |  |  |

| INL Error                                                       | INL                                | _                                     | ±1           | —                     | LSb             |                                                                                                   |  |  |

| DNL                                                             | DNL                                | _                                     | ±0.2         | _                     | LSb             | Note 1                                                                                            |  |  |

| MCP4821                                                         |                                    |                                       |              |                       |                 |                                                                                                   |  |  |

| Resolution                                                      | n                                  | 12                                    |              |                       | Bits            |                                                                                                   |  |  |

| INL Error                                                       | INL                                | _                                     | ±4           |                       | LSb             |                                                                                                   |  |  |

| DNL                                                             | DNL                                | _                                     | ±0.25        |                       | LSb             | Note 1                                                                                            |  |  |

| Offset Error                                                    | V <sub>OS</sub>                    | _                                     | ±0.02        | _                     | % of FSR        | Code = 0x000h                                                                                     |  |  |

| Offset Error Temperature<br>Coefficient                         | V <sub>OS</sub> /°C                | _                                     | -5           | -                     | ppm/°C          | +25°C to +125°C                                                                                   |  |  |

| Gain Error                                                      | 9e                                 | —                                     | -0.10        | —                     | % of FSR        | Code = 0xFFFh,<br>not including offset error                                                      |  |  |

| Gain Error Temperature<br>Coefficient                           | $\Delta$ G/°C                      |                                       | -3           | _                     | ppm/°C          |                                                                                                   |  |  |

| Internal Voltage Reference                                      | (V <sub>REF</sub> )                |                                       |              |                       |                 |                                                                                                   |  |  |

| Internal Reference Voltage                                      | V <sub>REF</sub>                   |                                       | 2.048        | —                     | V               | V <sub>OUT</sub> when G = 1x and<br>Code = 0xFFFh                                                 |  |  |

| Temperature Coefficient                                         | $\Delta V_{REF}$ /°C               | Ι                                     | 125          | —                     | ppm/°C          | -40°C to 0°C                                                                                      |  |  |

| (Note 2)                                                        |                                    | _                                     | 0.25         | —                     | LSb/°C          | -40°C to 0°C                                                                                      |  |  |

|                                                                 |                                    | _                                     | 45           |                       | ppm/°C          | 0°C to +85°C                                                                                      |  |  |

|                                                                 |                                    | _                                     | 0.09         | _                     | LSb/°C          | 0°C to +85°C                                                                                      |  |  |

| Output Noise (V <sub>REF</sub> Noise)                           | E <sub>NREF</sub><br>(0.1 – 10 Hz) | $-$ 290 $ \mu V_{p-p}$ Code = 0xFFFh, |              | Code = 0xFFFh, G = 1x |                 |                                                                                                   |  |  |

| Output Noise Density                                            | e <sub>NREF</sub><br>(1 kHz)       | —                                     | 1.2          | —                     | µV/√Hz          | Code = 0xFFFh, G = 1x                                                                             |  |  |

|                                                                 | e <sub>NREF</sub><br>(10 kHz)      | —                                     | 1.0          | _                     | µV/√Hz          | Code = $0xFFFh$ , G = $1x$                                                                        |  |  |

| 1/f Corner Frequency                                            | f <sub>CORNER</sub>                | _                                     | 400          | —                     | Hz              |                                                                                                   |  |  |

|                                                                 | •                                  |                                       |              | •                     |                 |                                                                                                   |  |  |

**Note 1:** Guaranteed monotonic by design over all codes.

2: This parameter is ensured by design, and not 100% tested.

## ELECTRICAL CHARACTERISTIC WITH EXTENDED TEMPERATURE (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{DD} = 5V$ ,  $V_{SS} = 0V$ ,  $V_{REF} = 2.048V$ , Output Buffer Gain (G) = 2x,  $R_L = 5 k\Omega$  to GND,  $C_L = 100 pF$ . Typical values are at +125°C by characterization or simulation.

| Parameters                      | Sym                   | Min | Тур                              | Мах | Units      | Conditions                                                                 |

|---------------------------------|-----------------------|-----|----------------------------------|-----|------------|----------------------------------------------------------------------------|

| Output Amplifier                |                       |     |                                  |     |            |                                                                            |

| Output Swing                    | V <sub>OUT</sub>      | —   | 0.01 to<br>V <sub>DD</sub> -0.04 | —   | V          | Accuracy is better than 1 LSb for $V_{OUT}$ = 10 mV to ( $V_{DD}$ – 40 mV) |

| Phase Margin                    | PM                    | —   | 66                               |     | Degree (°) | $C_L = 400 \text{ pF}, R_L = \infty$                                       |

| Slew Rate                       | SR                    | _   | 0.55                             | _   | V/µs       |                                                                            |

| Short Circuit Current           | I <sub>SC</sub>       | _   | 17                               | _   | mA         |                                                                            |

| Settling Time                   | t <sub>SETTLING</sub> | —   | 4.5                              | _   | μs         | Within ½ LSb of final value from<br>¼ to ¾ full-scale range                |

| Dynamic Performance (No         | te 2)                 | •   |                                  |     |            |                                                                            |

| Major Code Transition<br>Glitch |                       | _   | 45                               | —   | nV-s       | 1 LSb change around major<br>carry (01111111 to<br>10000000)               |

| Digital Feedthrough             |                       | —   | <10                              | _   | nV-s       |                                                                            |

Note 1: Guaranteed monotonic by design over all codes.

**2:** This parameter is ensured by design, and not 100% tested.

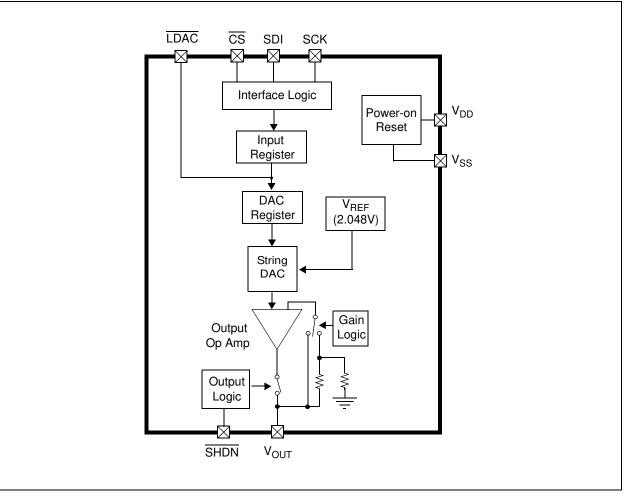

## AC CHARACTERISTICS (SPI TIMING SPECIFICATIONS)

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{DD}$ = 2.7V – 5.5V, $T_A$ = -40 to +125°C. Typical values are at +25°C. |                                       |             |                      |                     |       |                                                                                                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------|----------------------|---------------------|-------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameters                                                                                                                                | Sym                                   | Min         | Тур                  | Мах                 | Units | Conditions                                                                                              |  |  |  |  |  |

| Schmitt Trigger High-Level Input<br>Voltage (All digital input pins)                                                                      | V <sub>IH</sub>                       | 0.7 V<br>DD | —                    | _                   | V     |                                                                                                         |  |  |  |  |  |

| Schmitt Trigger Low-Level Input<br>Voltage (All digital input pins)                                                                       | V <sub>IL</sub>                       |             | —                    | 0.2 V <sub>DD</sub> | V     |                                                                                                         |  |  |  |  |  |

| Hysteresis of Schmitt Trigger Inputs                                                                                                      | V <sub>HYS</sub>                      | _           | 0.05 V <sub>DD</sub> |                     |       |                                                                                                         |  |  |  |  |  |

| Input Leakage Current                                                                                                                     | I <sub>LEAKAGE</sub>                  | -1          | —                    | 1                   | μA    | $\overline{SHDN} = \overline{LDAC} = \overline{CS} = SDI =$<br>SCK = V <sub>DD</sub> or V <sub>SS</sub> |  |  |  |  |  |

| Digital Pin Capacitance<br>(All inputs/outputs)                                                                                           | C <sub>IN</sub> ,<br>C <sub>OUT</sub> | _           | 10                   |                     | pF    | V <sub>DD</sub> = 5.0V, T <sub>A</sub> = +25°C,<br>f <sub>CLK</sub> = 1 MHz <b>(Note 1)</b>             |  |  |  |  |  |

| Clock Frequency                                                                                                                           | F <sub>CLK</sub>                      | _           | —                    | 20                  | MHz   | T <sub>A</sub> = +25°C (Note 1)                                                                         |  |  |  |  |  |

| Clock High Time                                                                                                                           | t <sub>HI</sub>                       | 15          | —                    |                     | ns    | Note 1                                                                                                  |  |  |  |  |  |

| Clock Low Time                                                                                                                            | t <sub>LO</sub>                       | 15          | —                    |                     | ns    | Note 1                                                                                                  |  |  |  |  |  |

| CS Fall to First Rising CLK Edge                                                                                                          | t <sub>CSSR</sub>                     | 40          | —                    |                     | ns    | Applies only when $\overline{CS}$ falls with CLK high. (Note 1)                                         |  |  |  |  |  |

| Data Input Setup Time                                                                                                                     | t <sub>SU</sub>                       | 15          | —                    | _                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

| Data Input Hold Time                                                                                                                      | t <sub>HD</sub>                       | 10          | —                    | _                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

| SCK Rise to CS Rise Hold Time                                                                                                             | t <sub>CHS</sub>                      | 15          | —                    |                     | ns    | Note 1                                                                                                  |  |  |  |  |  |

| CS High Time                                                                                                                              | t <sub>CSH</sub>                      | 15          | —                    | —                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

| LDAC Pulse Width                                                                                                                          | t <sub>LD</sub>                       | 100         | _                    | _                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

| LDAC Setup Time                                                                                                                           | t <sub>LS</sub>                       | 40          | _                    | —                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

| SCK Idle Time before $\overline{CS}$ Fall                                                                                                 | t <sub>IDLE</sub>                     | 40          | —                    | _                   | ns    | Note 1                                                                                                  |  |  |  |  |  |

**Note 1:** This parameter is ensured by design and not 100% tested.

FIGURE 1-1: SPI Input Timing Data.

## **TEMPERATURE CHARACTERISTICS**

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{DD} = +2.7V$ to $+5.5V$ , $V_{SS} = GND$ . |                |     |     |      |       |            |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|--|--|--|--|

| Parameters                                                                                                   | Sym            | Min | Тур | Max  | Units | Conditions |  |  |  |  |  |

| Temperature Ranges                                                                                           |                |     |     |      |       |            |  |  |  |  |  |

| Specified Temperature Range                                                                                  | Τ <sub>Α</sub> | -40 | _   | +125 | °C    |            |  |  |  |  |  |

| Operating Temperature Range                                                                                  | T <sub>A</sub> | -40 | —   | +125 | °C    | Note 1     |  |  |  |  |  |

| Storage Temperature Range                                                                                    | T <sub>A</sub> | -65 | _   | +150 | °C    |            |  |  |  |  |  |

| Thermal Package Resistances                                                                                  |                |     |     |      |       |            |  |  |  |  |  |

| Thermal Resistance, 8L-DFN (2x3)                                                                             | $\theta_{JA}$  | _   | 68  | _    | °C/W  |            |  |  |  |  |  |

| Thermal Resistance, 8L-MSOP                                                                                  | $\theta_{JA}$  |     | 211 | _    | °C/W  |            |  |  |  |  |  |

| Thermal Resistance, 8L-PDIP                                                                                  | $\theta_{JA}$  | _   | 90  | _    | °C/W  |            |  |  |  |  |  |

| Thermal Resistance, 8L-SOIC                                                                                  | $\theta_{JA}$  | _   | 150 |      | °C/W  |            |  |  |  |  |  |

**Note 1:** The MCP4801/4811/4821 devices operate over this extended temperature range, but with reduced performance. Operation in this range must not cause T<sub>J</sub> to exceed the maximum junction temperature of +150°C.

## 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

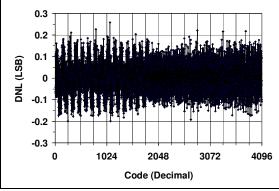

FIGURE 2-1:

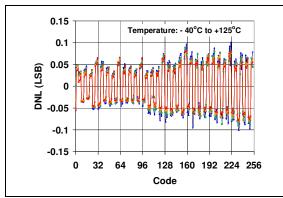

DNL vs. Code (MCP4821).

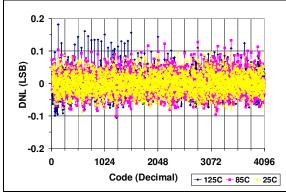

FIGURE 2-2: DNL vs. Code and Temperature (MCP4821).

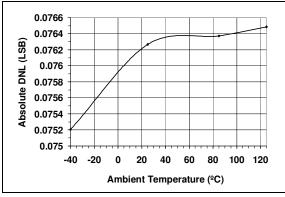

FIGURE 2-3: Absolute DNL vs. Temperature (MCP4821).

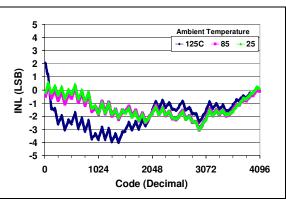

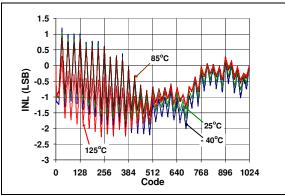

FIGURE 2-4: INL vs. Code and Temperature (MCP4821).

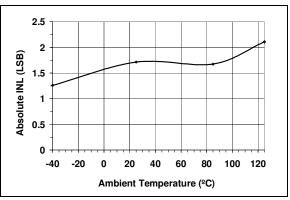

FIGURE 2-5: Absolute INL vs. Temperature (MCP4821).

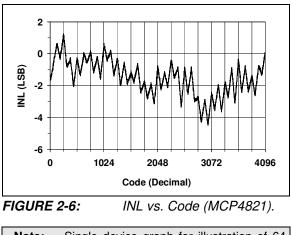

Note: Single device graph for illustration of 64 code effect.

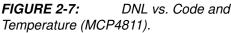

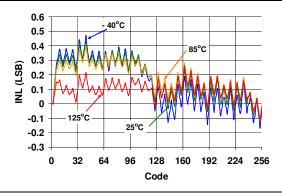

FIGURE 2-8: INL vs. Code and Temperature (MCP4811).

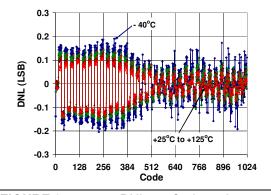

FIGURE 2-9: DNL vs. Code and Temperature (MCP4801).

FIGURE 2-10: INL vs. Code and Temperature (MCP4801).

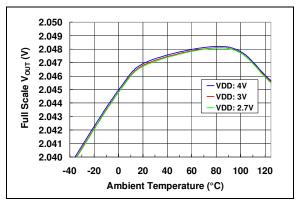

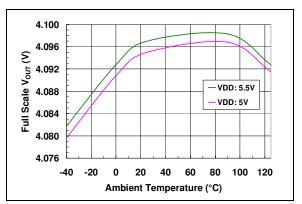

**FIGURE 2-11:** Full-Scale  $V_{OUT}$  vs. Ambient Temperature and  $V_{DD}$ . Gain = 1x.

**FIGURE 2-12:** Full-Scale  $V_{OUT}$  vs. Ambient Temperature and  $V_{DD}$ . Gain = 2x.

## MCP4801/4811/4821

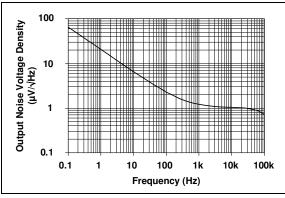

**FIGURE 2-13:** Output Noise Voltage Density ( $V_{REF}$  Noise Density) vs. Frequency. Gain = 1x.

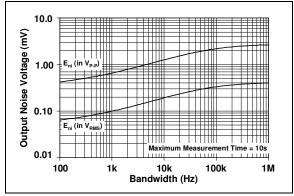

**FIGURE 2-14:** Output Noise Voltage (V<sub>REF</sub> Noise Voltage) vs. Bandwidth. Gain = 2x.

FIGURE 2-15:

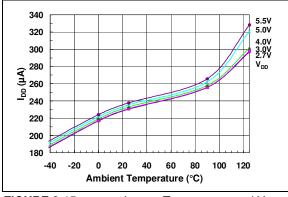

I<sub>DD</sub> vs. Temperature and V<sub>DD</sub>.

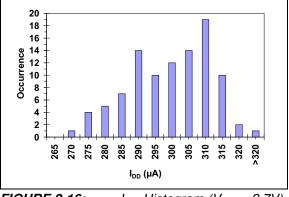

**FIGURE 2-16:**  $I_{DD}$  Histogram ( $V_{DD} = 2.7V$ ).

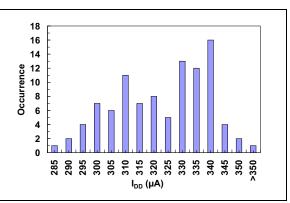

**FIGURE 2-17:**  $I_{DD}$  Histogram ( $V_{DD} = 5.0V$ ).

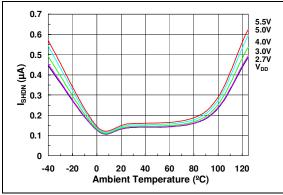

**FIGURE 2-18:** Hardware Shutdown Current vs. Temperature and V<sub>DD</sub>.

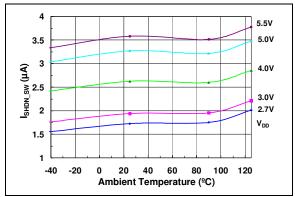

**FIGURE 2-19:** Software Shutdown Current vs. Temperature and V<sub>DD</sub>.

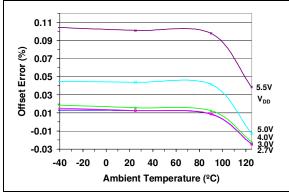

**FIGURE 2-20:** Offset Error vs. Temperature and V<sub>DD</sub>.

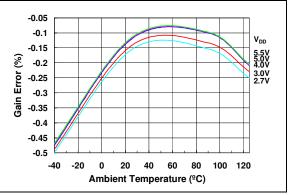

**FIGURE 2-21:** Gain Error vs. Temperature and V<sub>DD</sub>.

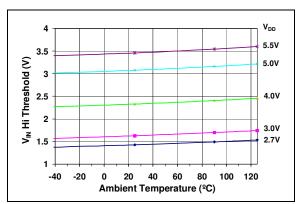

**FIGURE 2-22:**  $V_{IN}$  High Threshold vs. Temperature and  $V_{DD}$ .

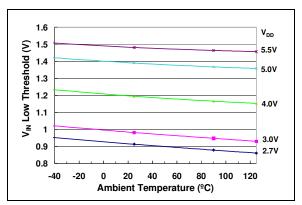

**FIGURE 2-23:**  $V_{IN}$  Low Threshold vs. Temperature and  $V_{DD}$ .

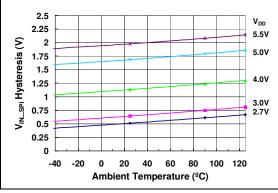

**FIGURE 2-24:** Input Hysteresis vs. Temperature and V<sub>DD</sub>.

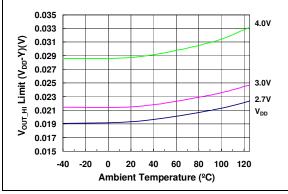

**FIGURE 2-25:**  $V_{OUT}$  High Limit vs. Temperature and  $V_{DD}$ .

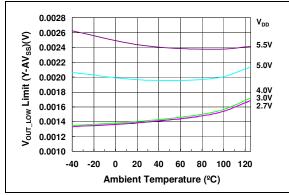

**FIGURE 2-26:** V<sub>OUT</sub> Low Limit vs. Temperature and V<sub>DD</sub>.

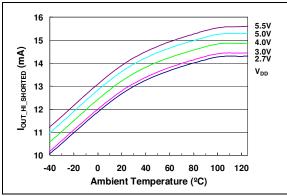

**FIGURE 2-27:**  $I_{OUT}$  High Short vs. Temperature and  $V_{DD}$ .

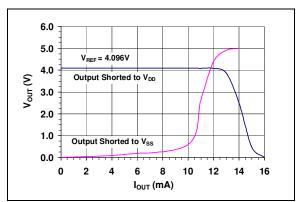

**FIGURE 2-28:**  $I_{OUT}$  vs.  $V_{OUT}$ . Gain = 2x.

## MCP4801/4811/4821

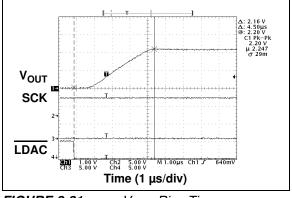

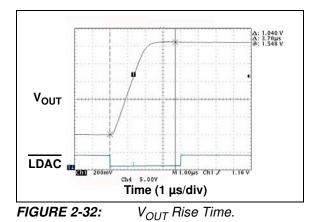

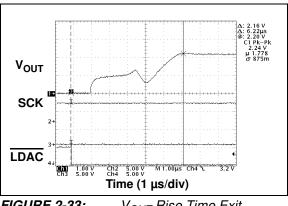

**FIGURE 2-33:** V<sub>OUT</sub> Rise Time Exit Shutdown.

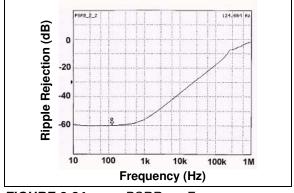

FIGURE 2-34: PSRR vs. Frequency.

NOTES:

## 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

| MCP4801/4811/4821        |     |                  |                                                                                                                                       |

|--------------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| MSOP, PDIP,<br>SOIC, DFN | DFN | Symbol           | Description                                                                                                                           |

| 1                        | 1   | V <sub>DD</sub>  | Supply Voltage Input (2.7V to 5.5V)                                                                                                   |

| 2                        | 2   | CS               | Chip Select Input                                                                                                                     |

| 3                        | 3   | SCK              | Serial Clock Input                                                                                                                    |

| 4                        | 4   | SDI              | Serial Data Input                                                                                                                     |

| 5                        | 5   | LDAC             | DAC Output Synchronization Input. This pin is used to transfer the input register (DAC settings) to the output register ( $V_{OUT}$ ) |

| 6                        | 6   | SHDN             | Hardware Shutdown Input                                                                                                               |

| 7                        | 7   | V <sub>SS</sub>  | Ground reference point for all circuitry on the device                                                                                |

| 8                        | 8   | V <sub>OUT</sub> | DAC Analog Output                                                                                                                     |

| _                        | 9   | EP               | Exposed thermal pad. This pad must be connected to $V_{SS}$ in application                                                            |

## 3.1 Supply Voltage Pins (V<sub>DD</sub>, V<sub>SS</sub>)

$V_{DD}$  is the positive supply voltage input pin. The input supply voltage is relative to  $V_{SS}$  and can range from 2.7V to 5.5V. The power supply at the  $V_{DD}$  pin should be as clean as possible for good DAC performance. Using an appropriate bypass capacitor of about 0.1  $\mu F$  (ceramic) to ground is recommended. An additional 10  $\mu F$  capacitor (tantalum) in parallel is also recommended to further attenuate high-frequency noise present in application boards.

$V_{SS}$  is the analog ground pin and the current return path of the device. The user must connect the  $V_{SS}$  pin to a ground plane through a low-impedance connection. If an analog ground path is available in the application Printed Circuit Board (PCB), it is highly recommended that the  $V_{SS}$  pin be tied to the analog ground path or isolated within an analog ground plane of the circuit board.

## 3.2 Chip Select (CS)

CS is the Chip Select input pin, which requires an active low to enable serial clock and data functions.

## 3.3 Serial Clock Input (SCK)

SCK is the SPI compatible serial clock input pin.

## 3.4 Serial Data Input (SDI)

SDI is the SPI compatible serial data input pin.

## 3.5 Latch DAC Input (LDAC)

$\overline{\text{LDAC}}$  (latch DAC synchronization input) pin is used to transfer the input latch register to the DAC register (output latches, V<sub>OUT</sub>). When this pin is low, V<sub>OUT</sub> is updated with input register content. This pin can be tied to low (V<sub>SS</sub>) if the V<sub>OUT</sub> update is desired at the rising edge of the CS pin. This pin can be driven by an external control device such as an MCU I/O pin.

## 3.6 Analog Output (V<sub>OUT</sub>)

$V_{OUT}$  is the DAC analog output pin. The DAC output has an output amplifier. The full-scale range of the DAC output is from  $V_{SS}$  to  $G^*V_{REF}$ , where G is the gain selection option (1x or 2x). The DAC analog output cannot go higher than the supply voltage ( $V_{DD}$ ).

## 3.7 Exposed Thermal Pad (EP)

There is an internal electrical connection between the exposed thermal pad (EP) and the  $V_{SS}$  pin. They must be connected to the same potential on the PCB.

NOTES:

## 4.0 GENERAL OVERVIEW

The MCP4801, MCP4811 and MCP4821 are single channel voltage-output 8-bit, 10-bit and 12-bit DAC devices, respectively. These devices include rail-to-rail output amplifier, internal voltage reference, shutdown and reset-management circuitry. The devices use an SPI serial communication interface and operate with a single supply voltage from 2.7V to 5.5V.

The DAC input coding of these devices is straight binary. Equation 4-1 shows the DAC analog output voltage calculation.

EQUATION 4-1: ANALOG OUTPUT VOLTAGE (V<sub>OUT</sub>)

$$V_{OUT} = \frac{(2.048V \times D_n)}{2^n} \times G$$

Where:

2.048V = Internal voltage reference

$D_n = DAC$  input code G = Gain selection

= Gain selection =  $2 \text{ for } < \overline{GA} > \text{ bit } = 0$

= 1 for

$$\overline{GA}$$

bit = 1

= DAC Resolution

= 10 for MCP4811

= 12 for MCP4821

The ideal output range of each device is:

#### • MCP4801 (n = 8)

n

(a) 0.0V to 255/256 \* 2.048V when gain setting = 1x.

(b) 0.0V to 255/256 \* 4.096V when gain setting = 2x.

#### • MCP4811 (n = 10)

(a) 0.0V to 1023/1024 \* 2.048V when gain setting = 1x.

(b) 0.0V to 1023/1024 \* 4.096V when gain setting = 2x.

#### • MCP4821 (n = 12)

(a) 0.0V to 4095/4096 \* 2.048V when gain setting = 1x. (b) 0.0V to 4095/4096 \* 4.096V when gain setting = 2x.

Note: See the output swing voltage specification in Section 1.0 "Electrical Characteristics".

1 LSb is the ideal voltage difference between two successive codes. Table 4-1 illustrates the LSb calculation of each device.

TABLE 4-1: LSb OF EACH DEVICE

| Device   | Gain<br>Selection | LSb Size             |  |  |  |  |  |

|----------|-------------------|----------------------|--|--|--|--|--|

| MCP4801  | 1x                | 2.048V/256 = 8 mV    |  |  |  |  |  |

| (n = 8)  | 2x                | 4.096V/256 = 16 mV   |  |  |  |  |  |

| MCP4811  | 1x                | 2.048V/1024 = 2 mV   |  |  |  |  |  |

| (n = 10) | 2x                | 4.096V/1024 = 4 mV   |  |  |  |  |  |

| MCP4821  | 1x                | 2.048V/4096 = 0.5 mV |  |  |  |  |  |

| (n = 12) | 2x                | 4.096V/4096 = 1 mV   |  |  |  |  |  |

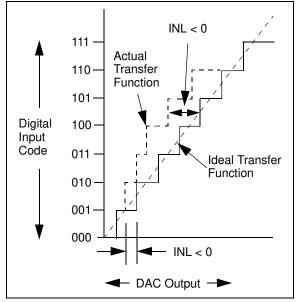

## 4.0.1 INL ACCURACY

Integral Non-Linearity (INL) error is the maximum deviation between an actual code transition point and its corresponding ideal transition point once offset and gain errors have been removed. The two endpoints method (from 0x000 to 0xFFF) is used for the calculation. Figure 4-1 shows the details.

A positive INL error represents transition(s) later than ideal. A negative INL error represents transition(s) earlier than ideal.

FIGURE 4-1: Example for INL Error.

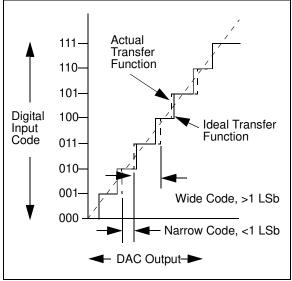

#### 4.0.2 DNL ACCURACY

A Differential Non-Linearity (DNL) error is the measure of the variations in code widths from the ideal code width. A DNL error of zero indicates that every code is exactly 1 LSb wide.

#### 4.0.3 OFFSET ERROR

Offset error is the deviation from zero voltage output when the digital input code is zero.

#### 4.0.4 GAIN ERROR

Gain error is the deviation from the ideal output,  $V_{\text{REF}} - 1$  LSb, excluding the effects of offset error.

## 4.1 Circuit Descriptions

#### 4.1.1 OUTPUT AMPLIFIER

The analog DAC output is buffered with a low-power, precision CMOS amplifier. This amplifier provides low offset voltage and low noise. The output stage enables the device to operate with output voltages close to the power supply rails. Refer to **Section 1.0 "Electrical Characteristics"** for the analog output voltage range and load conditions.

In addition to resistive load-driving capability, the amplifier will also drive high capacitive loads without oscillation. The amplifier's strong output allows  $V_{OUT}$  to be used as a programmable voltage reference in a system.

#### 4.1.1.1 Programmable Gain Block

The rail-to-rail output amplifier has two configurable gain options: a gain of 1x ( $\overline{GA}$ > = 1) or a gain of 2x ( $\overline{GA}$ > = 0). The default setting is a gain of 2x. This results in an ideal full-scale output of 0.000V to 4.096V due to the internal reference ( $V_{REF}$  = 2.048V).

#### 4.1.2 VOLTAGE REFERENCE

The MCP4801/4811/4821 devices utilize internal 2.048V voltage reference. The voltage reference has a low temperature coefficient and low noise characteristics. Refer to **Section 1.0 "Electrical Characteristics"** for the voltage reference specifications.

## 4.1.3 POWER-ON RESET CIRCUIT

The internal Power-on Reset (POR) circuit monitors the power supply voltage (V<sub>DD</sub>) during the device operation. The circuit also ensures that the DAC powers up with high output impedance (<SHDN> = 0, typically 500 kΩ). The devices will continue to have a high-impedance output until a valid write command is received, and the LDAC pin meets the input low threshold.

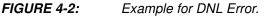

If the power supply voltage is less than the POR threshold ( $V_{POR} = 2.0V$ , typical), the DAC will be held in the Reset state. It will remain in that state until  $V_{DD} > V_{POR}$  and a subsequent write command is received.

Figure 4-3 shows a typical power supply transient pulse and the duration required to cause a reset to occur, as well as the relationship between the duration and trip voltage. A 0.1  $\mu$ F decoupling capacitor, mounted as close as possible to the V<sub>DD</sub> pin, can provide additional transient immunity.

Typical Transient Response.

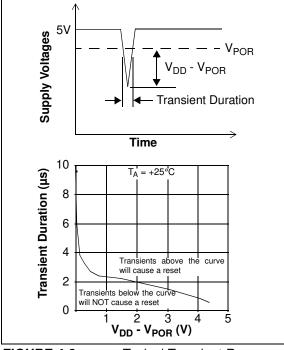

## 4.1.4 SHUTDOWN MODE

The user can shut down the device using a software command ( $\langle SHDN \rangle = 0$ ) or SHDN pin. During shutdown mode, most of the internal circuits, including the output amplifier, are turned off for power savings. The internal reference is not affected by the shutdown command. The serial interface also remains active, allowing a write command to bring the device out of Shutdown mode. There will be no analog output at the V<sub>OUT</sub> pin, which is internally switched to a known resistive load (500 k $\Omega$ , typical). Figure 4-4 shows the analog output stage during Shutdown mode.

The condition of the Power-on Reset circuit during Shutdown is as follows:

- a) Turned off if shutdown occurred from the SHDN pin

- b) Remains turned on if the shutdown occurred through software

The device will remain in Shutdown mode until the <SHDN> bit = 1 is latched into the device or SHDN pin is changed to logic high. When the device is changed from Shutdown to Active mode, the output settling time takes < 10  $\mu$ s, but greater than the standard active mode settling time (4.5  $\mu$ s).

FIGURE 4-4: Output Stage for Shutdown Mode.

NOTES:

## 5.0 SERIAL INTERFACE

#### 5.1 Overview

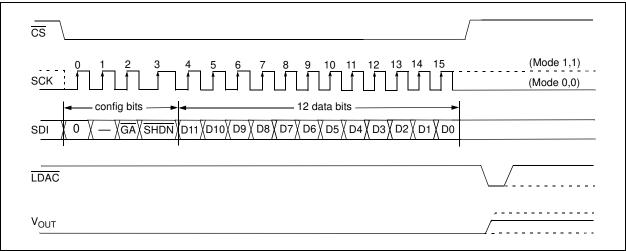

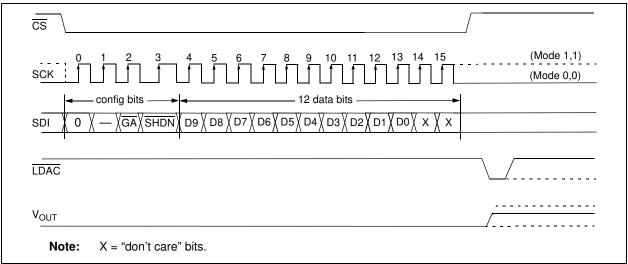

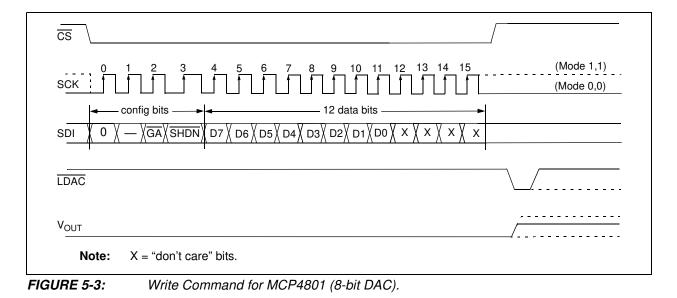

The MCP4801/4811/4821 devices are designed to interface directly with the Serial Peripheral Interface (SPI) port, available on many microcontrollers, and supports Mode 0,0 and Mode 1,1. Commands and data are sent to the device via the SDI pin, with data being clocked-in on the rising edge of SCK. The communications are unidirectional and, thus, data cannot be read out of the MCP4801/4811/4821 devices. The CS pin must be held low for the duration of a write command. The write command consists of 16 bits and is used to configure the DAC's control and data latches. Register 5-1 to Register 5-3 detail the input register that is used to configure and load the DAC register for each device. Figure 5-1 to Figure 5-3 show the write command for each device.

Refer to Figure 1-1 and the SPI Timing Specifications Table for detailed input and output timing specifications for both Mode 0,0 and Mode 1,1 operation.

#### 5.2 Write Command

The write command is initiated by driving the  $\overline{CS}$  pin low, followed by clocking the four Configuration bits and the 12 data bits into the SDI pin on the rising edge of SCK. The  $\overline{CS}$  pin is then raised, causing the data to be latched into the DAC's input register.

The MCP4801/4811/4821 devices utilize a doublebuffered latch structure to allow the DAC output to be synchronized with the LDAC pin, if desired.

By bringing down the  $\overline{\text{LDAC}}$  pin to a low state, the content stored in the DAC's input register is transferred into the DAC's output register (V<sub>OUT</sub>), and V<sub>OUT</sub> is updated.

All writes to the MCP4801/4811/4821 devices are 16-bit words. Any clocks after the first  $16^{th}$  clock will be ignored. The Most Significant four bits are Configuration bits. The remaining 12 bits are data bits. No data can be transferred into the device with  $\overline{CS}$  high. The data transfer will only occur if 16 clocks have been transferred into the device. If the rising edge of  $\overline{CS}$  occurs prior, shifting of data into the input register will be aborted.

|        |     |     |      |     |     |     |     |     |     | •   |     | ,   |     |     |       |

|--------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| W-x    | W-x | W-x | W-0  | W-x   |

| 0      | _   | GA  | SHDN | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0    |

| bit 15 |     |     |      |     |     |     |     |     |     |     |     |     |     |     | bit 0 |

#### REGISTER 5-1: WRITE COMMAND REGISTER FOR MCP4821 (12-BIT DAC)

## REGISTER 5-2: WRITE COMMAND REGISTER FOR MCP4811 (10-BIT DAC)

| W-x    | W-x | W-x | W-0  | W-x   |

|--------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 0      | —   | GA  | SHDN | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | х   | х     |

| bit 15 |     |     |      |     |     |     |     |     |     |     |     |     |     |     | bit 0 |

#### REGISTER 5-3: WRITE COMMAND REGISTER FOR MCP4801 (8-BIT DAC)

| W-x    | W-x | W-x | W-0  | W-x   |

|--------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 0      | —   | GA  | SHDN | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Х   | Х   | х   | х     |

| bit 15 |     |     |      |     |     |     |     |     |     |     |     |     |     |     | bit 0 |

Where:

| bit 15 ( 1) | 0 = Write to DAC register                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 1 = Ignore this command                                                                                                                                          |

| bit 14      | — Don't Care                                                                                                                                                     |

| bit 13      | GA: Output Gain Selection bit                                                                                                                                    |

|             | 1 = 1x ( $V_{OUT} = V_{REF} * D/4096$ )<br>0 = 2x ( $V_{OUT} = 2 * V_{REF} * D/4096$ ), where internal $V_{REF} = 2.048V$ .                                      |

| bit 12      | SHDN: Output Shutdown Control bit                                                                                                                                |

|             | 1 = Active mode operation. Vout is available.<br>0 = Shutdown the device. Analog output is not available. V <sub>OUT</sub> pin is connected to 500 kΩ (typical). |

| bit 11-0    | D11:D0: DAC Input Data bits. Bit x is ignored.                                                                                                                   |

|             |                                                                                                                                                                  |

| Legend      |                                                                                                                                                                  |

| Legend            |                  |                     |                    |

|-------------------|------------------|---------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b | it, read as '0'    |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared  | x = bit is unknown |

Note 1: This bit must be '0'. The device ignores the write command if this MSB bit is not '0'.

FIGURE 5-1: Write Command for MCP4821 (12-bit DAC).

FIGURE 5-2: Write Command for MCP4811 (10-bit DAC).

NOTES:

## 6.0 TYPICAL APPLICATIONS

The MCP4801/4811/4821 family of devices are general purpose, single channel voltage output DACs for various applications where a precision operation with low-power and internal voltage reference is required.

Applications generally suited for the devices are:

- Set Point or Offset Trimming

- Sensor Calibration

- Precision Selectable Voltage Reference

- · Portable Instrumentation (Battery-Powered)

- Calibration of Optical Communication Devices

## 6.1 Digital Interface

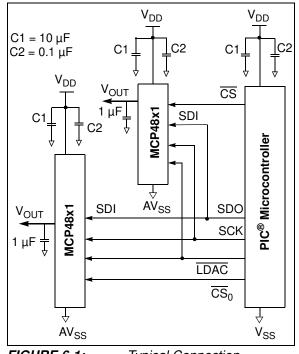

The MCP4801/4811/4821 devices utilize a 3-wire synchronous serial protocol to transfer the DAC's setup and input codes from the digital devices. The serial protocol can be interfaced to SPI or Microwire peripherals which are common on many microcontroller units (MCUs), including Microchip's PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs.

In addition to the three serial connections ( $\overline{CS}$ , SCK and SDI), the LDAC signal synchronizes the DAC output with LDAC pin event. By bringing the LDAC pin down "low", the DAC input codes and settings in the DAC input register are latched into the output register, and the DAC analog output is updated. Figure 6-1 shows an example of the pin connections. Note that the LDAC pin can be tied low (V<sub>SS</sub>) to reduce the required connections from 4 to 3 I/O pins. In this case, the DAC output can be immediately updated when a valid 16 clock transmission has been received and the  $\overline{CS}$  pin has been raised.

## 6.2 Power Supply Considerations

The typical application will require a bypass capacitor to filter out noise in the power supply traces. The noise can be induced onto the power supply's traces from various events such as digital switching or as a result of changes on the DAC's output. The bypass capacitor helps minimize the effect of these noise sources. Figure 6-1 illustrates an appropriate bypass strategy. In this example, two bypass capacitors are used in parallel: (a) 0.1  $\mu$ F (ceramic) and (b)10  $\mu$ F (tantalum). These capacitors should be placed as close to the device power pin (V<sub>DD</sub>) as possible (within 4 mm).

The power source supplying these devices should be as clean as possible. If the application circuit has separate digital and analog power supplies,  $V_{DD}$  and  $V_{SS}$  of the device should reside on the analog plane.

## 6.3 Output Noise Considerations

The voltage noise density (in  $\mu V/\sqrt{Hz}$ ) is illustrated in Figure 2-13. This noise appears at V<sub>OUT</sub>, and is primarily a result of the internal reference voltage. Its 1/f corner (f<sub>CORNER</sub>) is approximately 400 Hz.

Figure 2-14 illustrates the voltage noise (in mV<sub>RMS</sub> or mV<sub>P-P</sub>). A small bypass capacitor on V<sub>OUT</sub> is an effective method to produce a single-pole Low-Pass Filter (LPF) that will reduce this noise. For instance, a bypass capacitor sized to produce a 1 kHz LPF would result in an E<sub>NREF</sub> of about 100  $\mu$ V<sub>RMS</sub>. This would be necessary when trying to achieve the low DNL error performance (at G = 1x) that the MCP4801/4811/4821 devices are capable of. The tested range for stability is .001  $\mu$ F through 4.7  $\mu$ F.

FIGURE 6-1: Typical Connection Diagram.

## 6.4 Layout Considerations

Inductively-coupled AC transients and digital switching noises can degrade the output signal integrity, and potentially reduce the device performance. Careful board layout will minimize these effects and increase the Signal-to-Noise Ratio (SNR). Bench testing has shown that a multi-layer board utilizing a low-inductance ground plane, isolated inputs and isolated outputs with proper decoupling, is critical for the best performance. Particularly harsh environments may require shielding of critical signals.

Breadboards and wire-wrapped boards are not recommended if low noise is desired.