# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Advance Information

# Quad DSI 2.02 Master with Differential Drive and Frequency Spreading

The 33781 is a master device for four differential DSI 2.02 buses. It contains the logic to interface the buses to a standard serial peripheral interface (SPI) port and the analog circuitry to drive data and power over the bus, as well as receive data from the remote slave devices.

The differential mode of the 33781 generates lower electromagnetic interference (EMI) in situations where data rates and wiring make this a problem. Frequency spreading further reduces interference by spreading the energy across many frequencies, reducing the energy in any single frequency.

#### Features

- · Four independent differential DSI (DBUS) channels

- Dual SPI interface

- · Enhanced bus fault performance

- Automatic message cyclical redundancy checking (CRC) generation and checking for each channel

- Enhanced register set with addressable buffer allows queuing of 4 independent slave commands at one time for each channel

- 8- to 16-Bit messages with 0- to 8-Bit CRC

- Independent frequency spreading for each channel

- · Pseudo bus switch feature on channel 0

- Pb-free packaging designated by suffix code EK

Document Number: MC33781 Rev. 5.0, 11/2009

**VRoHS**

# 33781

#### **DIFFERENTIAL DSI 2.02 MASTER**

EK SUFFIX (PB-FREE) 98ASA10556D 32-PIN SOICW EP

#### ORDERING INFORMATION

| Device        | Temperature<br>Range (T <sub>A</sub> ) | Package     |

|---------------|----------------------------------------|-------------|

| MCZ33781EK/R2 | -40°C to 90°C                          | 32 SOICW EP |

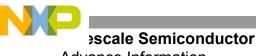

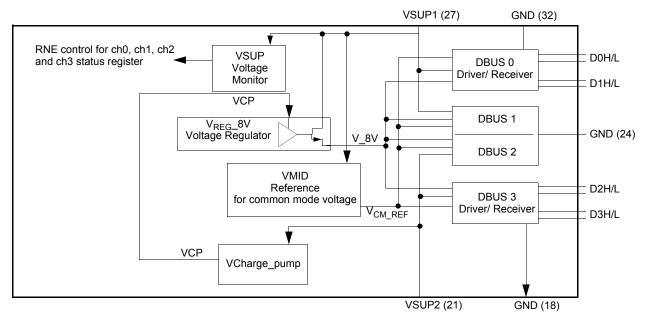

Figure 1. 33781 Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2007-2009. All rights reserved.

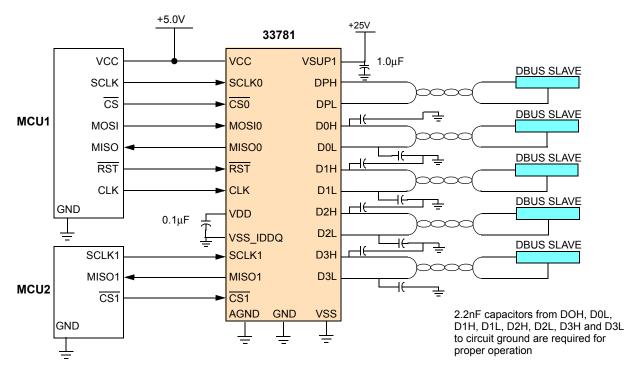

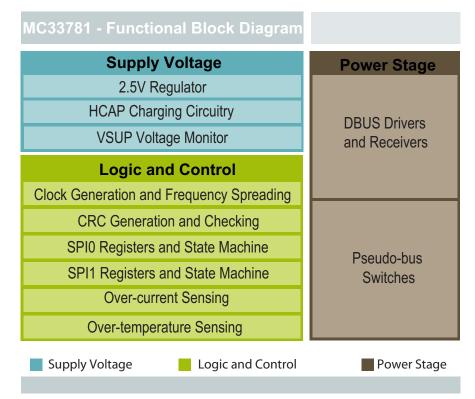

# INTERNAL BLOCK DIAGRAM

Figure 2. 33781 Internal Block Diagram

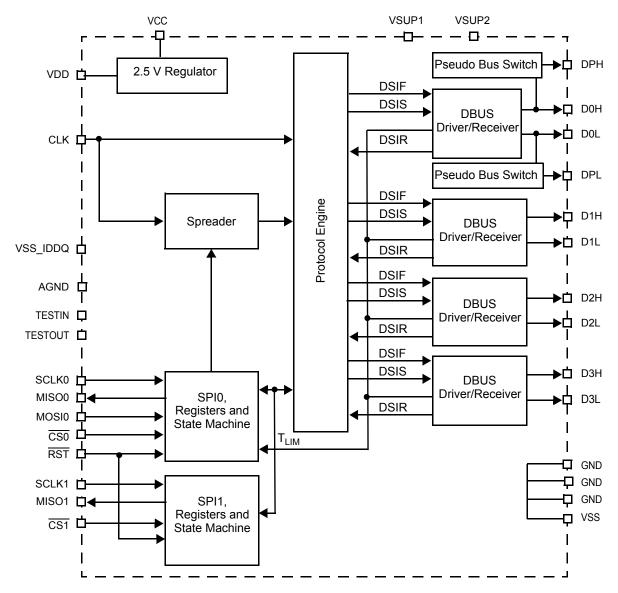

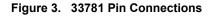

## **PIN CONNECTIONS**

#### Table 1. 33781 Pin Definitions

A functional description of each Pin can be found in the Functional Pin Descriptions section beginning on page 15.

| Pin | Pin Name | Pin Function | Formal Name                 | Definition                                                                                                                                                                                 |

|-----|----------|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RST      | Reset        | IC Reset                    | A low level on this pin returns all registers to a known state as indicated<br>in the sections entitled SPI0 Register and Bit Descriptions and SPI1<br>Communications.                     |

| 2   | SCLK0    | Input        | SPI0 Serial Data Clock      | Clocks data in from and out to SPI0. MISO0 data changes on the negative transition of SCLK0. MOSI0 is sampled on the positive edge of SCLK0.                                               |

| 3   | MOSI0    | Input        | SPI0 Master Out Slave<br>In | SPI data into SPI0. This data input is sampled on the positive edge of SCLK0                                                                                                               |

| 4   | MISO0    | Output       | SPI0 Master In Slave<br>Out | SPI0 data sent to the MCU by this device. This data output changes on the negative edge of SCLK0. When CS0 is high, this Pin is high-impedance.                                            |

| 5   | SCLK1    | Input        | SPI1 Serial Data Clock      | Clocks data out from SPI1. MISO1 data changes on the negative transition of SCLK1.                                                                                                         |

| 6   | MISO1    | Output       | SPI1 Master In Slave<br>Out | SPI1 data sent to the MCU by this device. This data output changes on the negative edge of SCLK1. When $\overline{\text{CS1}}$ is high, this Pin is high-impedance.                        |

| 7   | CS0      | Input        | SPI0 Chip Select            | When this signal is high, SPI signals on SPI0 are ignored. Asserting this pin low starts an SPI0 transaction. The SPI0 transaction is signaled as completed when this signal returns high. |

| 8   | AGND     | Ground       | Analog Ground               | Ground for the analog circuits. This pin is not connected internally to the other grounds on the chip. It should be connected to a quiet ground on the board.                              |

| 9   | CS1      | Input        | SPI1 Chip Select            | When this signal is high, SPI signals on SPI1 are ignored. Asserting this pin low starts an SPI1 transaction. The SPI1 transaction is signaled as completed when this signal returns high. |

| 10  | VSS      | Ground       | Digital Ground              | Digital ground connected internally to the other on-chip grounds. This ground is connected to circuits that will consume current during IDDQ testing.                                      |

| 11  | VDD      | Power        | Digital Voltage             | Output of the Internal 2.5V regulator for the digital circuits. No external current draw is allowed from this pin.                                                                         |

#### Table 1. 33781 Pin Definitions

A functional description of each Pin can be found in the Functional Pin Descriptions section beginning on page 15.

| Pin | Pin Name | Pin Function  | Formal Name                        | Definition                                                                                                                                                         |

|-----|----------|---------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | VPP      | Input         | Test Mode                          | A high-voltage on this pin puts the device in test mode for IC manufacturing test. It must be grounded in the application.                                         |

| 13  | VCC      | Input         | Logic Supply                       | Regulated 5V input                                                                                                                                                 |

| 14  | CLK      | Input         | Clock Input                        | 4.0MHz clock input                                                                                                                                                 |

| 15  | TESTIN   | Test          | Test Input                         | Input pin for device test. This pin must be tied to ground in the application.                                                                                     |

| 16  | TESTOUT  | Test          | Test Output                        | Output pin for device test. This pin is left floating in the application.                                                                                          |

| 17  | VSS_IDDQ | Ground        | Digital Ground and<br>IDDQ Test    | Ground reference for the digital circuits that should not consume current<br>during IDDQ testing. This ground is not connected to the other grounds<br>internally. |

| 18  | GND      | Ground        | Power Ground                       | Bus power return                                                                                                                                                   |

| 19  | D3L      | Output Driver | Low Side Bus 3                     | Bus 3 low side                                                                                                                                                     |

| 20  | D3H      | Output Driver | High Side Bus 3                    | Bus 3 high side                                                                                                                                                    |

| 21  | VSUP2    | Power         | Positive Supply for<br>Bus Outputs | This supply input is used to provide the positive level output of buses 2 and 3.                                                                                   |

| 22  | D2H      | Output Driver | High Side Bus 2                    | Bus 2 high side                                                                                                                                                    |

| 23  | D2L      | Output Driver | Low Side Bus 2                     | Bus 2 low side                                                                                                                                                     |

| 24  | GND      | Ground        | Power Ground                       | Bus power return                                                                                                                                                   |

| 25  | D1L      | Output Driver | Low Side Bus 1                     | Bus 1 low side                                                                                                                                                     |

| 26  | D1H      | Output Driver | High Side Bus 1                    | Bus 1 high side                                                                                                                                                    |

| 27  | VSUP1    | Power         | Positive Supply for<br>Bus Outputs | This supply input is used to provide the positive level output of buses 0 and 1.                                                                                   |

| 28  | D0H      | Output Driver | High Side Bus 0                    | Bus 0 high side                                                                                                                                                    |

| 29  | DPH      | Output Driver | High Side Pseudo Bus               | Pseudo Bus high side                                                                                                                                               |

| 30  | D0L      | Output Driver | Low Side Bus 0                     | Bus 0 low side                                                                                                                                                     |

| 31  | DPL      | Output Driver | Low Side Pseudo Bus                | Pseudo Bus low side                                                                                                                                                |

| 32  | GND      | Ground        | Power Ground                       | Bus power return                                                                                                                                                   |

# **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### Table 2. Maximum Ratings

All voltages are with respect to GND unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                      | Symbol                    | Value                           | Unit |

|----------------------------------------------|---------------------------|---------------------------------|------|

| ELECTRICAL RATINGS                           |                           |                                 |      |

| Supply Voltages                              |                           |                                 | V    |

| VSUPn                                        | $V_{SUP1}$ and $V_{SUP2}$ | -0.3 to 26.5                    |      |

| Load Dump VSUPn (300ms maximum - either pin) | V <sub>SUPLD</sub>        | 40                              |      |

| VCC                                          | V <sub>CC</sub>           | -0.3 to 7.0                     |      |

| VDD                                          | V <sub>DD</sub>           | -0.3 to 3.1                     |      |

| VPP                                          | V <sub>PP</sub>           | -0.3 to 10.0                    |      |

| Maximum Voltage on Logic Input/Output Pins   | _                         | -0.3 to V <sub>CC</sub> +0.3    | V    |

| Maximum Voltage on DBUS Pins                 | V <sub>DBUS</sub>         | -0.3 to V <sub>SUPn</sub> + 0.3 | V    |

| Maximum DBUS Pin Current                     | I <sub>DBUS</sub>         | 400                             | mA   |

| Maximum Logic Pin Current                    | ILOGIC                    | 20                              | mA   |

| ESD Voltage <sup>(1)</sup>                   |                           |                                 | V    |

| Human Body Model (HBM)                       | V <sub>ESD</sub>          | ±2000                           |      |

| Machine Model (MM)                           |                           | ±200                            |      |

| Charge Device Model (CDM)                    |                           |                                 |      |

| Corner pins                                  |                           | ±750                            |      |

| All other pins                               |                           | ±500                            |      |

#### THERMAL RATINGS

| Storage Temperature                                                           | T <sub>STG</sub>    | -55 to 150 | °C   |

|-------------------------------------------------------------------------------|---------------------|------------|------|

| Operating Ambient Temperature                                                 | T <sub>A</sub>      | -40 to 90  | °C   |

| Operating Junction Temperature                                                | TJ                  | -40 to 150 | °C   |

| Thermal Shutdown (Bus Drivers and Pseudo Bus Switch)                          | T <sub>SD</sub>     | 155 to 190 | °C   |

| Resistance, Junction-to-Ambient                                               | R <sub>θJA</sub>    | 71         | °C/W |

| Resistance, Junction-to-Board                                                 | $R_{\theta JB}$     | 6          | °C/W |

| Soldering Reflow Temperature                                                  | T <sub>SOLDER</sub> | 260        | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(2)</sup> , <sup>(3)</sup> | T <sub>PPRT</sub>   | Note 3     | °C   |

Notes

ESD1 testing is performed in accordance with the Human Body Model (HBM) (C<sub>ZAP</sub> = 100pF, R<sub>ZAP</sub> = 1500Ω); ESD2 testing is performed in accordance with the Machine Model (MM) (C<sub>ZAP</sub> = 200pF, R<sub>ZAP</sub> = 0Ω); and Charge Body Model (CBM).

2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

3. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                              | Symbol               | Min                   | Тур | Мах                  | Unit |

|-------------------------------------------------------------|----------------------|-----------------------|-----|----------------------|------|

| POWER INPUT REQUIREMENTS (VSUPn, VCC)                       |                      |                       |     |                      |      |

| I <sub>VSUPT</sub> Supply Current (Test Mode, CLK = 4.0MHz) | IVSUPT               |                       |     |                      | mA   |

| High Z                                                      |                      | -                     | _   | 16                   |      |

| Signal, Idle (Ibus = 0)                                     |                      | -                     | _   | 33                   |      |

| Signal, Idle (Ibus = 10mA on all channels, a total of 40mA) |                      | -                     | -   | 61                   |      |

| I <sub>VCC</sub> Supply Current (CLK = 4.0MHz, RST = high)  | I <sub>VCC</sub>     |                       |     |                      | mA   |

| Signal, Idle (Ibus = 0)                                     |                      | -                     | _   | 10.0                 |      |

| Signal, Idle (Ibus = 10mA on all channels, a total of 40mA) |                      | -                     | _   | 12.0                 |      |

| V <sub>SUPn</sub> Low Detect Threshold                      | V <sub>VSUPnLO</sub> | 9.1                   | I   | 9.9                  | V    |

| Vcc > 4.75V                                                 |                      |                       |     |                      |      |

| V <sub>SUPn</sub> Low Mask Time                             | t <sub>MASK</sub>    | 20                    | -   | 25                   | μs   |

| Vcc > 4.75V                                                 |                      |                       |     |                      |      |

| MICROCONTROLLER INTERFACE (RST, CSn, MOSIO, MISOn, SC       | LKn, and CLK)        |                       |     |                      |      |

| I/O Logic Levels (RST, CSn, MOSI0, SCLKn, and CLK)          |                      |                       |     |                      | V    |

| Input High Voltage                                          | V <sub>IH</sub>      | 2.0                   | -   | V <sub>CC</sub> +0.3 |      |

| Input Low Voltage                                           | V <sub>IL</sub>      | -0.3                  | -   | 1.0                  |      |

| Input Hysteresis <sup>(4)</sup>                             | V <sub>HYST</sub>    | 0.1                   | -   | 0.5                  |      |

| Input Capacitance <sup>(4)</sup>                            | Cl                   |                       |     |                      | pF   |

| CSn, MOSI0, and SCLKn                                       |                      | -                     | _   | 10                   |      |

| RST and CLK                                                 |                      | -                     | _   | 20                   |      |

| Output Low Voltage                                          | V <sub>OL</sub>      |                       |     |                      | V    |

| MISOn Pin = 0.3mA                                           |                      | 0                     | -   | 0.8                  |      |

| Output High Voltage                                         | V <sub>OH</sub>      |                       |     |                      | V    |

| MISOn Pin = -0.3mA                                          |                      | V <sub>CC</sub> - 0.8 | _   | V <sub>CC</sub>      |      |

| Output Leakage Current                                      | I <sub>MISO</sub>    |                       |     |                      | μA   |

| MISOn Pin = 0V                                              |                      | -10                   | _   | 10                   |      |

| MISOn Pin = V <sub>CC</sub>                                 |                      | -10                   | -   | 10                   |      |

| SCLKn, CSn Pull-up Current                                  | I <sub>PU</sub>      |                       |     |                      | μA   |

| VOUT = $V_{CC}$ - 2.0 V                                     |                      | -50                   | -30 | -10                  | ,    |

| RST Pull-down Current                                       | IRSTPD               |                       |     |                      | μA   |

| V <sub>OUT</sub> = 1.0V                                     |                      | 5.0                   | -   | 13                   |      |

| CLK, MOSI0 Pull-down Current                                | I <sub>PD</sub>      |                       |     |                      | μA   |

| V <sub>OUT</sub> = 1.0V                                     |                      | 5.0                   | 10  | 13                   |      |

Notes

4. Not measured in production.

#### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                      | Symbol                                   | Min                          | Тур                  | Max                           | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------|----------------------|-------------------------------|------|

| BUS TRANSMITTER (DnH, DnL)                                                                                                                                          |                                          |                              | •                    |                               |      |

| Output Bus Idle Voltage (Drop)                                                                                                                                      | V <sub>DnD(Drop)</sub> <sup>(7)(8)</sup> |                              |                      |                               | V    |

| I <sub>nH</sub> = -200mA, I <sub>nL</sub> = 200mA <sup>(6)</sup>                                                                                                    |                                          | -                            | -                    | 1.6                           |      |

| Output Signal High Voltage (Differential)                                                                                                                           | V <sub>DnD(HIGH)</sub> <sup>(7)</sup>    |                              |                      |                               | V    |

| -12.5mA $\leq$ InH $~\leq$ 1.0mA, -1.0mA $\leq$ InL $\leq$ 12.5mA $^{(6)}$                                                                                          |                                          | 4.175                        | 4.5                  | 4.825                         |      |

| Output Signal Low Voltage (Differential)                                                                                                                            | V <sub>DnD(LOW)</sub> <sup>(7)</sup>     |                              |                      |                               | V    |

| -12.5mA $\leq$ InH $\leq$ 1.0mA, -1.0mA $\leq$ InL $\leq$ 12.5mA <sup>(6)</sup>                                                                                     | × ,                                      | 1.175                        | 1.5                  | 1.825                         |      |

| Vmid, (DnH + DnL)/2 (Voltage Halfway Between Bus High Side and Bus Low Side                                                                                         | V <sub>MID</sub> <sup>(8)</sup>          | V <sub>SUPn</sub> /<br>2-0.8 | V <sub>SUPn</sub> /2 | V <sub>SUPn</sub> /<br>2 +0.8 | V    |

| VCM Peak to Peak (Maximum Vmid-Minimum Vmid)<br>For Vmid (Idle), Vmid (Signal_H), Vmid (Signal_L) <sup>(5)</sup>                                                    | V <sub>CMP</sub>                         | 0                            | -                    | 30                            | mV   |

| Bus Driver Vmid Peak to Peak, (DnH+DnL)/2 <sup>(5)</sup><br>For Signal to Idle, Idle, Idle to Signal,<br>VmidPP(Idle)=Vmid(Max)- Vmid (Min)                         | V <sub>MIDPP</sub> (IDLE)                | -                            | _                    | 300                           | mV   |

| Bus Driver Vmid Peak to Peak (Dnh+DnL)/2 <sup>(5)</sup><br>For Signal_H to Signal_L, Signal_L, Signal_L to Signal_H, Signal_H<br>VmidPP(Signal)=Vmid(Max)-Vmid(Min) | V <sub>MIDPP</sub> (SIGNAL)              | _                            | -                    | 80                            | mV   |

| Output High Side (DnH) Driver Current Limit                                                                                                                         | I <sub>CL(HIGH)</sub>                    |                              |                      |                               | mA   |

| Fault Condition: DnH = 0V                                                                                                                                           |                                          | -600                         | -                    | -200                          |      |

| Normal Operation<br>Fault Condition: DnH = V <sub>SUPn</sub>                                                                                                        |                                          | -400                         | -                    | -200                          |      |

|                                                                                                                                                                     |                                          | 150                          | -                    | 350                           |      |

| Output Low Side (DnL) Driver Current Limit<br>Fault Condition: DnL = 0V                                                                                             | I <sub>CL(LOW)</sub>                     | 250                          |                      | 450                           | mA   |

| Fault Condition: DnL = V <sub>SUPn</sub>                                                                                                                            |                                          | -350<br>200                  | _                    | -150<br>400                   |      |

| Signal mode Over-current Shutdown                                                                                                                                   | I <sub>SSD</sub>                         | 20                           |                      | 60                            | mA   |

| Disabled High Side (DnH) Bus Leakage (DnL open)                                                                                                                     | I <sub>LK(HIGH)</sub>                    |                              |                      |                               | mA   |

| DnH = 0V                                                                                                                                                            |                                          | -1.0                         | _                    | 1.0                           |      |

| DnH = V <sub>SUPn</sub>                                                                                                                                             |                                          | -1.0                         | -                    | 1.0                           |      |

| Disabled Low Side (DnL) Bus Leakage (DnH open) <sup>(9)</sup>                                                                                                       | I <sub>LK(LOW)</sub>                     |                              |                      |                               | mA   |

| DnL = 0V                                                                                                                                                            | (/                                       | -1.0                         | -                    | 1.0                           |      |

| DnL = V <sub>SUPn</sub>                                                                                                                                             |                                          | -1.0                         | -                    | 1.0                           |      |

Notes

5. Not measured in production.

6. InH=bus current at DnH, InL=bus current at DnL

7.  $V_{DnD}=V_{DnH}-V_{DnL}$

8. Max V<sub>DnD</sub> = VSUPn - 2 \* V<sub>MID\_OFFSET</sub> - V<sub>DnD(Drop)</sub>, V<sub>MID\_OFFSET</sub> = |V<sub>MID</sub> - V<sub>SUPn</sub> / 2|

9. Worst Case Disabled Low Side Bus Leakage for DnL occurs with DnL = V<sub>SUP</sub> and DnH = 0V. In this configuration, the DnL leakage current can exceed 1mA. This is not measured in production.

#### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                    | Symbol               | Min | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------|------|

| BUS TRANSMITTER (DnH, DnL) (CONTINUED)                                                                                            | ·                    |     |     | •    |      |

| High Side Pseudo Bus Switch Resistance<br>I <sub>SWH</sub> =160mA                                                                 | R <sub>SWH</sub>     | -   | 8.0 | 16.0 | Ω    |

| Low Side Pseudo Bus Switch Resistance<br>I <sub>SWL</sub> =160mA                                                                  | R <sub>SWL</sub>     | -   | 8.0 | 16.0 | Ω    |

| Pseudo Bus Switch Matching                                                                                                        | R <sub>PSMATCH</sub> | -   | -   | 1.0  | Ω    |

| High Side Pseudo Bus Switch Leakage Current<br>DPH = Open: CH0 drivers in Idle, DPH = 0V or<br>CH0 drivers in Signal_H, DPH = 25V | I <sub>DPHLK</sub>   | -20 | _   | 20   | μΑ   |

| Low Side Pseudo Bus Switch Leakage Current<br>DPL = Open: CH0 drivers in Idle, DPL = 25V,or<br>CH0 drivers in Signal_H, DPL = 0V  | I <sub>DPLLK</sub>   | -20 | -   | 20   | μΑ   |

| BUS RECEIVER (DnH, DnL)                                                                                                           | ·                    |     |     | •    |      |

| Comparator Trip Point for High Side                                                                                               | COMP <sub>HIGH</sub> | 5.0 | 6.0 | 7.0  | mA   |

| Comparator Trip Point for Low Side                                                                                                | COMPLOW              | 5.0 | 6.0 | 7.0  | mA   |

| Comparator Trip Point for Adder                                                                                                   | COMP <sub>ADD</sub>  | 6.0 | 12  | 18   | mA   |

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                          | Symbol              | Min | Тур | Мах | Unit |

|-------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| сгоск                                                                   |                     |     | I   |     |      |

| CLK Periods (System requirement) <sup>(10)</sup>                        |                     |     |     |     | ns   |

| Time High                                                               | t <sub>CLKHI</sub>  | 75  | -   | _   |      |

| Time Low                                                                | t <sub>CLKLO</sub>  | 75  | -   | _   |      |

| Period                                                                  | t <sub>CLKPER</sub> | 245 | 250 | 255 |      |

| CLK Transition (System requirement) <sup>(10)</sup>                     |                     |     |     |     | ns   |

| Time for Low-to-High Transition of the CLK Input Signal                 | t <sub>CLKLH</sub>  | _   | -   | 100 |      |

| Time for High-to-Low Transition of the CLK Input Signal                 | t <sub>CLKHL</sub>  | _   | -   | 100 |      |

| Reset Low Time                                                          | t <sub>RSTLO</sub>  | 100 | -   | _   | ns   |

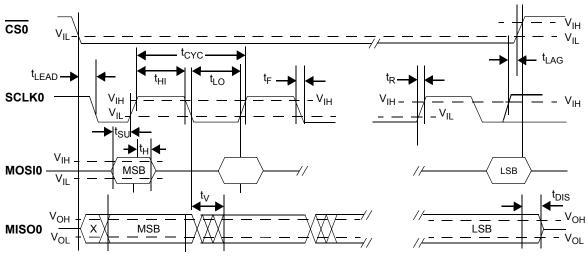

| SPI INTERFACE TIMING                                                    |                     |     |     |     |      |

| SPI Clock Cycle Time                                                    | t <sub>CYC</sub>    | 100 | -   | _   | ns   |

| SPI Clock High Time                                                     | t <sub>HI</sub>     | 40  | -   | -   | ns   |

| SPI Clock Low Time                                                      | t <sub>LO</sub>     | 40  | -   | _   | ns   |

| SPI CSn Lead Time <sup>(11)</sup>                                       | t <sub>LEAD</sub>   | 50  | -   | -   | ns   |

| SPI CSn Lag Time <sup>(11)</sup>                                        | t <sub>LAG</sub>    | 50  | -   | -   | ns   |

| SPI CS0 Time Between Bursts <sup>(10)</sup>                             | t <sub>CS0</sub> HI | 80  | -   | _   | ns   |

| SPI CS1 Time Between Bursts <sup>(10)</sup>                             | t <sub>CS1</sub> HI | 300 | -   | _   | ns   |

| Data Setup Time                                                         | t <sub>SU</sub>     |     |     |     | ns   |

| MOSI0 Valid Before SCLK0 Rising Edge <sup>(11)</sup>                    |                     | 10  | -   | -   |      |

| Data Hold Time                                                          |                     |     |     |     | ns   |

| MOSI0 Valid After SCLK0 Rising Edge <sup>(11),(10)</sup>                | t <sub>H</sub>      | 10  | -   | -   |      |

| Data Valid Time                                                         | t <sub>V</sub>      |     |     |     | ns   |

| SCLKn Falling Edge to MISOn Valid, C = 50pF <sup>(12)</sup>             |                     | -   | -   | 25  |      |

| Output Disable Time                                                     | t <sub>DIS</sub>    |     |     |     | ns   |

| CSn Rise to MISOn Hi-Z                                                  |                     | -   | -   | 50  |      |

| Rise Time (30% V <sub>CC</sub> to 70% V <sub>CC</sub> ) <sup>(10)</sup> | t <sub>R</sub>      |     |     |     | ns   |

| SCLKn, MOSI0                                                            |                     | -   | -   | 10  |      |

| Fall Time (70% V <sub>CC</sub> to 30% V <sub>CC</sub> ) <sup>(10)</sup> | t <sub>F</sub>      |     |     |     | ns   |

| SCLKn, MOSI0                                                            |                     | _   |     | 10  |      |

Notes

10. Not measured in production.

11. SPI signal timing from the production test equipment is programmed to ensure compliance.

12. Conditions are verified indirectly during test.

#### Table 4. Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                         | Symbol                     | Min                                | Тур              | Max                                                            | Unit |

|------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------|------------------|----------------------------------------------------------------|------|

| BUS TRANSMITTER                                                                                                        |                            |                                    |                  |                                                                | •    |

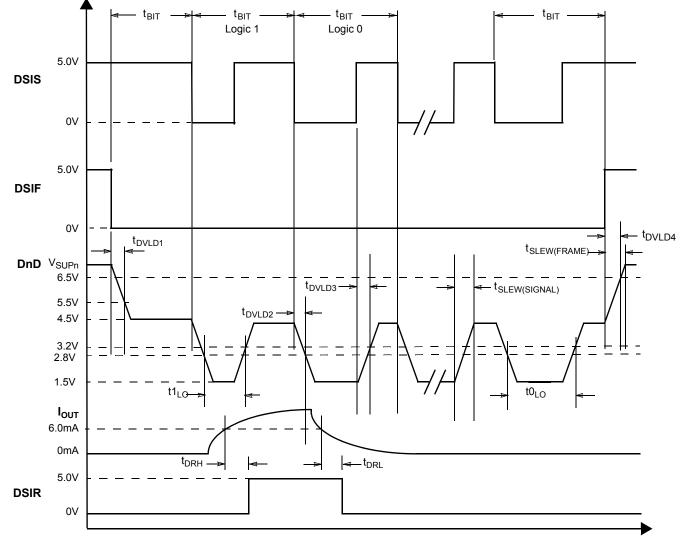

| Idle-to-Signal and Signal-to-Idle Slew Rate <sup>(13)</sup>                                                            | t <sub>SLEW(IDLE)</sub>    | 3.0                                | 6.0              | 8.0                                                            | V/µs |

| Signal High-to-Low and Signal Low-to-High Slew Rate <sup>(13),(14)</sup> (See Data Valid DSIS to DnD Timing)           | t <sub>SLEW</sub> (SIGNAL) | 3.0                                | 6.0              | 8.0                                                            | V/µs |

| Communication Data Rate Capability <sup>(14)</sup> (Ensured by Transmitter Data Valid and Receiver Delay Measurements) | D <sub>RATE</sub>          | 77.1                               | -                | 200                                                            | kbps |

| Data Rate(before frequency spreading)                                                                                  |                            |                                    |                  |                                                                |      |

| Signal Bit Time (1 / D <sub>RATE</sub> ) <sup>(14)</sup><br>The Max value depends on the settings in the FSEL bits     | t <sub>BIT</sub>           | 5.0                                | Η                | -                                                              | μs   |

| DBUS Start Delay, CS0 Rising Edge to DBUS <sup>(14)</sup>                                                              |                            |                                    |                  |                                                                | μs   |

| note: DLY is the inter-message delay selected in the DnCTRL register                                                   | <sup>t</sup> DBUSSTART2    | $2/3t_{BIT}$ + (DLY-2) * $t_{BIT}$ | -                | 5/3t <sub>BIT</sub> + (DLY-2) *<br><sup>t</sup> <sub>BIT</sub> |      |

| Data Valid <sup>(13)</sup>                                                                                             |                            |                                    |                  |                                                                | μs   |

| DSIF = 0.5 * V <sub>CC</sub> to DnD Fall = 5.5 V (9V $\leq$ V <sub>SUPn</sub> $\leq$ 40V)                              | t <sub>DVLD1</sub>         | -                                  | -                | 5.3                                                            |      |

| DSIS = 0.5 * V <sub>CC</sub> to DnD Fall = 2.8V (9V $\leq$ V <sub>SUPn</sub> $\leq$ 40V)                               | t <sub>DVLD2</sub>         | -                                  | -                | 1.0                                                            |      |

| DSIS = 0.5 * V <sub>CC</sub> to DnD Rise = 3.2V (9V $\leq$ V <sub>SUPn</sub> $\leq$ 40V)                               | t <sub>DVLD3</sub>         | -                                  | -                | 1.0                                                            |      |

| DSIF = 0.5 * V <sub>CC</sub> to DnD Rise = 6.5 V (9V $\leq$ V <sub>SUPn</sub> $\leq$ 40V)                              | t <sub>DVLD4</sub>         | -                                  | -                | 1.0                                                            |      |

| Signal mode Over-current Shutdown Delay <sup>(14)</sup>                                                                | toc                        | 3.0                                | 5.0              | 7.0                                                            | μs   |

| Signal Low Time for Logic Zero                                                                                         |                            |                                    |                  |                                                                |      |

| 33.3% Duty Cycle                                                                                                       | t0 <sub>LO</sub>           | 0.6 * t <sub>BIT</sub>             | 2/3 *            | 0.73 * t <sub>BIT</sub>                                        | μs   |

| $(2/3*t_{BIT}) \pm 10\%$ for threshold delta                                                                           |                            |                                    | t <sub>BIT</sub> |                                                                |      |

| Signal Low Time for Logic One                                                                                          |                            |                                    |                  |                                                                |      |

| 66.7% Duty Cycle                                                                                                       | t1 <sub>LO</sub>           | 0.3 * t <sub>BIT</sub>             | 1/3 *            | 0.37 * t <sub>BIT</sub>                                        | μs   |

| $(1/3*t_{BIT}) \pm 10\%$ for threshold delta                                                                           |                            |                                    | t <sub>BIT</sub> |                                                                |      |

Notes

13. C = 2.8nF from DnH to DnL and 2.2nF from DnH and DnL to GND, capacitor tolerance = ±10%.

14. Not measured in production.

#### Table 4. Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions  $4.75V \le V_{CC} \le 5.25V$ ,  $9.0V \le V_{SUPn} \le 25V$ ,  $-40^{\circ}C \le T_A \le 90^{\circ}C$ , unless otherwise noted. Voltages relative to GND, unless otherwise noted. Typical values noted reflect the approximate mean values of the parameter at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                           | Symbol            | Min       | Тур | Мах      | Unit |

|--------------------------------------------------------------------------|-------------------|-----------|-----|----------|------|

| BUS RECEIVER                                                             |                   | •         |     |          |      |

| Receiver Delay Time (I <sub>RSP</sub> = 0mA / 11mA step) <sup>(15)</sup> |                   |           |     |          | ns   |

| $I_{RSP}$ = -6.0mA to DSIR = 0.5 * $V_{CC}$                              | t <sub>DRH</sub>  | -         | -   | 500      |      |

| $I_{RSP}$ = -6.0mA to DSIR = 0.5 * V <sub>CC</sub>                       | t <sub>DRL</sub>  | -         | -   | 500      |      |

| Common Mode Current Noise Rejection (2.5ms max.)                         | I <sub>CMNR</sub> | -50       | -   | +50      | mA   |

| SPREAD SPECTRUM                                                          |                   |           |     |          |      |

| Base Frequency Range                                                     | f <sub>CEN</sub>  | 77.1 - 2% | -   | 200 + 2% | kHz  |

| PSEUDO BUS                                                               |                   |           |     |          |      |

| Pseudo Bus On Delay Time                                                 | t <sub>PBD1</sub> | -         | 5   | 10       | μs   |

| Pseudo Bus Off Delay Time                                                | t <sub>PBD2</sub> | -         | 5   | 10       | μs   |

Notes

15. Not measured in production.

# **TIMING DIAGRAMS**

Figure 4. DBUS Timing Characteristics

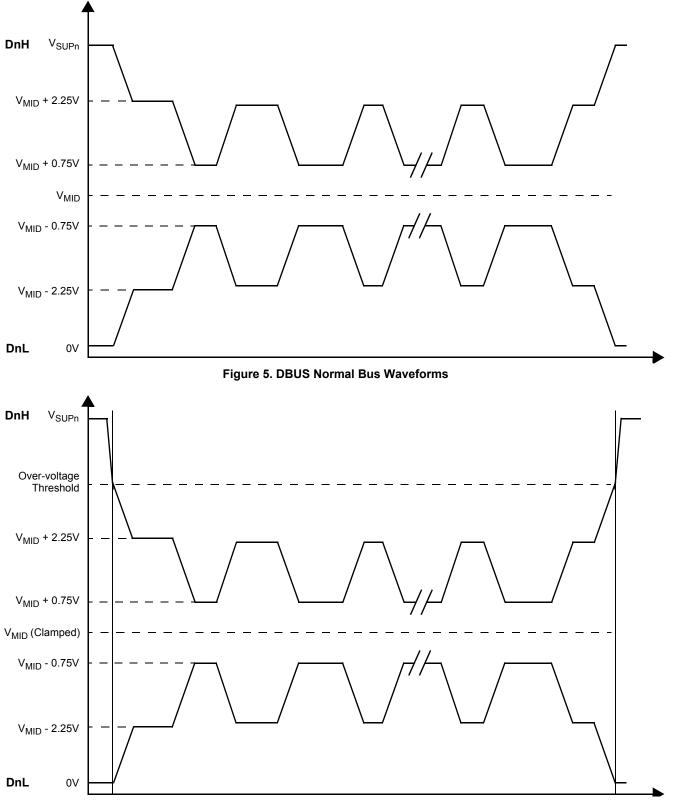

Figure 6. DBUS Over-voltage Bus Waveforms

X = Don't care

$V_{\text{IH}}$  = 70%  $V_{\text{CC},}$   $V_{\text{OH}}$  = 70%  $V_{\text{CC}}$

VIL = 30% VCC, VOL = 30% VCC

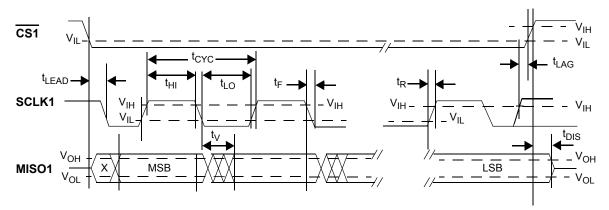

X = Don't care

$V_{IH} = 70\% V_{CC}, V_{OH} = 70\% V_{CC}$ VIL = 30% VCC, VOL = 30% VCC

#### Figure 8. SPI1 Interface Timing

# FUNCTIONAL DESCRIPTIONS

#### **INTRODUCTION**

The 33781 is intended to be used as a master device in a distributed system. It contains both protocol generators and physical interfaces, to allow an MCU to communicate with devices on the bus using two different SPI interfaces. Four differential buses are provided. The physical layer uses a two-wire bus to carry power and signal. The physical layer uses wave-shaped voltage signals for commands from the master and wave-shaped current signals for responses from the slaves. The protocol and physical layer conform to the DSI 2.02 specification.

The equivalent bus capacitance consists of capacitors connected between the two bus wires and capacitors between the bus wires and ground. Because the voltage change on either of the bus wires to ground is only 1/2 the amount of change between the two bus wires, the capacitance to ground only conducts half as much current as it would if connected directly across the bus. The equivalent bus capacitance of a capacitor to ground from the bus wires is one half of the actual amount of the capacitor. The amount of capacitance from either bus wire to ground should be kept the same in order to achieve the lowest radiated EMI energy. The 2.2nF capacitors required between the bus wires and ground result in an equivalent of 1.1nF of capacitance across the bus as seen by either bus wire.

<u>Table 5</u> shows the voltages used for operation. Low side (LS) is the bus wire that is the most negative and high side (HS) is the bus wire that is the most positive. <u>Figure 5</u> shows the bus waveforms in normal operation.

#### Table 5. High Side and Low Side Typical Voltages (Voltage Relative to Ground)

| Low Side |                           |                           |                   | High Side                 |                           |  |

|----------|---------------------------|---------------------------|-------------------|---------------------------|---------------------------|--|

| IDLE     | HIGH                      | LOW                       | IDLE HIGH LOW     |                           |                           |  |

| 0        | Vmid-2.25 <sup>(16)</sup> | Vmid-0.75 <sup>(16)</sup> | V <sub>SUPn</sub> | Vmid+2.25 <sup>(16)</sup> | Vmid+0.75 <sup>(16)</sup> |  |

Notes

16.  $V_{MID} = V_{SUPn}/2$ .

#### FUNCTIONAL PIN DESCRIPTIONS

# RESET (RST)

When pulled low, this will reset all internal registers to a known state as indicated in the section entitled SPI0 Register and Bit Descriptions on page 29.

## CHIP SELECT n (CSn)

This input is used to select the SPIn port when pulled to ground. When high, the associated SPIn port signals are ignored. The SPIn transaction is signaled as completed when this signal returns high.

#### MASTER OUT/SLAVE IN 0 (MOSI0)

This is the SPI data input to the device. This data is sampled on the positive (rising) edge of SCLK0. There is no MOSI pin or function for SPI1.

#### SERIAL CLOCK (SCLKn)

This is the clock signal from the SPIn master device. It controls the clocking of data to SPIn and data reads from the SPIn.

#### MASTER IN/SLAVE OUT (MISOn)

This is the SPIn data from SPIn to the SPIn master. Data changes on the negative (falling) transition of the associated SCLKn.

#### CLOCK (CLK)

This is the main clock source for the internal logic. It must be 4.0 MHz.

#### **GROUND (GND)**

Ground source for DSI/DBUS return.

#### **DIGITAL GROUND (VSS)**

Ground source for logic.

#### DIGITAL GROUND AND IDDQ (VSS\_IDDQ)

Used for IDDQ testing during IC manufacturing test.

#### ANALOG GROUND (AGND)

Ground source for analog circuits.

#### **POWER SOURCE (VCC)**

Nominal +5.0V Regulated Input.

#### DIGITAL REGULATOR OUTPUT (VDD)

Nominal +2.5V internal regulator Pin. This must be bypassed with a small capacitor to ground (100nF)

#### LOW SIDE BUS (DnL)

There are four independent low side outputs, D0L, D1L, D2L and D3L. They comprise the low side differential output signal of the DBUS physical layer as shown in <u>Figure 5</u>. They also provide power to the slave modules during the DBUS idle time. The output of DnL should have a bypass capacitor of 2.2nF to ground.

#### HIGH SIDE BUS (DnH)

There are four independent high side outputs, D0H, D1H, D2H, and D3H. They comprise the high side differential output signal of the DBUS physical layer. They also provide power to the slave modules during the DBUS idle time. See Figure 5. The output of DnH should have a bypass capacitor of 2.2nF to ground.

#### POSITIVE SUPPLY FOR BUS OUTPUT (VSUPn)

This 9.0V to 25V power supply is used to provide power to the slave devices attached to the DBUS. During the bus idle time, the storage capacitors in the slave modules are charged

up to maintain a regulated supply to the slave device. V<sub>SUP1</sub> powers devices DBUS0 and DBUS1, and V<sub>SUP2</sub> powers devices on DBUS2 and DBUS3. See Figure 9.

The two supplies are interdependent internally, however, as can be seen in Figure 9:  $V_{SUP1}$  is used to create the  $V_{CM\_REF}$  voltage for all four driver buffers, and  $V_{SUP2}$  is used to supply the charge pump voltage. Consequently, both  $V_{SUP1}$  and  $V_{SUP2}$  are required for internal functions: for example, the internal voltage regulator  $V_{REG\_8V}$  is supplied from  $V_{SUP1}$ , but uses the  $V_{SUP2}$ -derived charge pump voltage to supply the output NMOS devices.

#### PSEUDO BUS (DPH AND DPL)

These bus high and bus low pins are created by closing the pseudo bus switches attached to the DOH and DOL bus lines internal to the 33781. This allows a second external set of bus lines to communicate over the D0 Channel. The pseudo bus switches are controlled by the system MCU through SPI0.

Figure 9. VSUP Block Diagram

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

#### Figure 10. Block Illustration

The 33781 is controlled by an MCU through the SPI0 interface. It handles the digital and physical layer portions of a DBUS master node. Four separate DBUS channels are included. The physical layer uses a two-wire bus with analog wave-shaped voltage and current signals. Refer to Figure 1.

Major subsystems include the following:

- SPI0 interface and registers to a main MCU

- · SPI1 interface and registers to a second MCU

- · Four channels of DSI 2.02 protocol state logic

- · CRC block for each channel

- · Control and status registers

- Four addressable register sets per channel for queuing up to four commands and data per bus. The addressable buffer acts as a circular buffer for command writes and data reads.

- · Pseudo Bus Switch from D0H/L to DPH/L

#### SPI0 AND REGISTERS

This block contains the SPI0 interface logic and the control and response registers that are written to and read from the SPI interface.

The IC is an SPI slave-type device, so MOSI0 (Master-Out-Slave-In) is an input and MISO0 (Master-In-Slave-Out) is an output.  $\overline{CS0}$  and SCLK0 are also inputs. The SPI0 port can handle 2-byte and 4-byte transfers. It addresses 87 registers. The organization of the registers is described in the section entitled SPI0 Register and Bit Descriptions on page 29.

#### **SPI1 AND REGISTERS**

The 33781 has a second SPI port (called SPI1) that allows valid response data from Bus Channel 2 and 3, along with the slave address, to be read independently by a second MCU. This block contains the SPI1 interface logic and the response registers that are read from the SPI1 interface.

The IC is an SPI slave-type device, so MISO1 (Master-In-Slave-Out) is an output, and CS1 and SCLK1 are inputs. SPI1 does not use the MOSI (Master-Out-Slave-In) pin or function as it does not receive commands.

The SPI1 port handles only 16-bit transfers. It addresses eight registers which are read only.

#### **PROTOCOL ENGINE**

This block converts the data to be transmitted from the registers into the DBUS sequences, and converts DBUS response sequences to data in the registers.

The DBUS transmit protocol uses a return to 1 type data with a duty cycle determined by the logic state. The protocol includes Cyclical Redundancy Check (CRC) generation and validation.

#### **VSUPn VOLTAGE MONITOR**

This function monitors the voltage on the  $V_{SUPn}$  pin. If the voltage on the pin drops below the defined voltage threshold for longer than the voltage threshold mask time, the 33781 will continue to send queued DBUS commands, but not set any RNE bits in the DnSTAT registers to 1, until either the

device is reset by the  $\overrightarrow{\mathsf{RST}}$  pin or the EN bits in the DnEN registers are first set to zero, and then to one (disabled and then enabled). By monitoring the RNE bits the MCU will know that communications have been disrupted and can take the appropriate action.

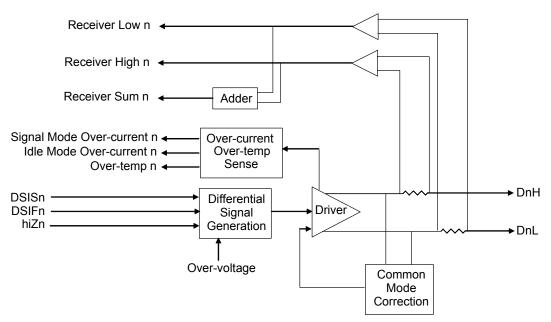

Figure 11. Driver/Receiver Block Diagram

#### DBUS DRIVER/RECEIVER (PHYSICAL LAYER)

There are four independent differential bus driver/receiver blocks on the 33781. These blocks translate the transmit data to the voltage and current needed to drive the DBUS. They also detect the response current from the slave devices and translate that current into digital levels. These circuits can drive their outputs to the levels listed in <u>Table 5</u>.

The DBUS driver/receiver block diagram is shown in <u>Figure 11</u>. The circuit uses a common driver for both the Idle and Signal modes to minimize common mode noise. The drivers are disabled in HiZ.

During Idle mode the driver is required to supply a high current to recharge the Slave device storage capacitors. In both Idle and Signal modes it is required to drive the DBUS load capacitances and control the slew rate over a wide supply voltage range and load conditions. Current limit, overcurrent shutdown and thermal shutdown are included to protect the device from fault conditions. More information can be found in the Protection and Diagnostic Features and SPI0 Register and Bit Descriptions sections.

To ensure stability of the bus drivers, capacitors must be connected between each output and ground. These are the DBUS common mode capacitors. In addition, a bypass capacitor is required at  $V_{SUPn}$ . These capacitors must be located close to the IC Pins and provide a low-impedance path to ground.

The internal signal DSIF controls the Idle to Signalling state change, and internal signal DSIS controls the signal level, high or low. DSIR is the slave device response signal to the logic. This is shown in <u>Table 6</u>.

#### Table 6. Internal Signal Truth Table

| DSIF | DSIS | Τ <sub>S</sub> | DSIR        | DnD            |

|------|------|----------------|-------------|----------------|

| 0    | 0    | 0              | Return Data | Signal Low     |

| 0    | 1    | 0              | Return Data | Signal High    |

| 1    | 0    | 0              | 0           | High-impedance |

| 1    | 1    | 0              | 0           | Idle           |

| Х    | Х    | 1              | 0           | High-impedance |

Bus wire faults on a bus do not disrupt communications on another bus. In addition, each bus channel has independent thermal shutdown protection. Once the channel thermal limit is reached the bus drivers become high-impedance, the TS bit is set to a 1 and the EN bit set to 0 in the channel DEN register. In addition the channel address buffer registers and pointers are reset. There is a 4 usec filter on Tlim to prevent false triggering.

The *Differential Signal Generation* block converts the DSIS signal to the DBUS differential signal voltage levels. This differential signal is buffered and slew rate controlled by

NP

the driver. The over-voltage input causes the driver characteristics to be modified under over-voltage conditions. This is described in more detail in the Load Dump Operation section.

A special requirement of the differential bus is to maintain a low common mode voltage. This is accomplished by monitoring the common mode voltage and modifying the driver slew rates. This is the function of the *Common Mode Correction* block.

Current signals sent by the slave are detected on both the high side and the low side of the bus using a differential current sense architecture. Sense resistors between the Signal driver and the DnH and DnL outputs detect the slave device response current. Sensing the current on both bus lines improves the fault diagnostics of the bus. Also included is an adder circuit which is used to improve the reception of sensor data in the presence of common mode noise. The comparators in the blocks output a high or low value depending on if the input is above or below the signal threshold.

The Receiver High, Receiver Low, and Receiver Sum outputs are sent to the device logic block which is shown in Figure 23. The data is sampled at the falling edge of DSIS. In the presence of faults or common mode noise it is possible that all three receiver circuits will not produce the same bit pattern. To check for this, each of the three receiver filter

outputs is passed to a CRC generation and checking block. A logic block determines which (if any) of the receiver filter blocks has produced the correct result, by comparing the CRC results along with the bit-by-bit XOR of the high side and low side bit pattern. <u>Table 7</u> shows how the logic determines which (if any) receiver outputs contain a valid response. The data is selected from either the Receiver High, Receiver Low or Receiver Sum circuit and the ER bit is set accordingly in the DnRnSTAT register.

If either Receiver High or Receiver Low has all 1's for data, including the CRC bits, then the ER bit will be set. For either of these two conditions, the ER bit will be set regardless of the Receiver Sum data value and regardless of whether or not all the 1's caused a CRC error on the High or Low side.

Note that SPI0 and SPI1 do not use the same sources for their respective output data streams. SPI0 chooses between Receiver High or Receiver Sum0; SPI1 chooses between Receiver Low and Receiver Sum1.

In order to provide the maximum protection against a single-point failure causing a disruption in communication, the decision paths for the two SPI channels are internally independent . For example, Receiver Sum0 and Receiver Sum1 use different holding registers in the Receiver logic. These registers are duplicates, although they will always hold the same data unless there is a fault in one of the data paths.

#### Table 7. Receiver Decision Logic

| Bus Pin<br>Conditions | Receiver<br>High 6 ± 1<br>mA | Receiver<br>Low 6 ± 1<br>mA | Receiver<br>Sum 12 ±<br>6mA | High and<br>Low XOR<br>(bit/bit) | High and<br>Sum XOR<br>(bit/bit) | Low and<br>Sum XOR<br>(bit/bit) | ER Bit | SPI0<br>DnRnxData | SPI1<br>DnRnxData |

|-----------------------|------------------------------|-----------------------------|-----------------------------|----------------------------------|----------------------------------|---------------------------------|--------|-------------------|-------------------|

| Normal                | CRC Ok                       | CRC Ok                      | CRC Ok                      | H*L Ok                           | N/A                              | N/A                             | 0      | Receiver<br>High  | Receiver<br>Low   |

| Normai                | CINC OK                      | CINC OK                     | CINC OK                     | H*L Not OK                       | N/A                              | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

| Out of Spec           | CRC Ok                       | CRC Ok                      | Bad CRC                     | H*L Ok                           | N/A                              | N/A                             | 0      | Receiver<br>High  | Receiver<br>Low   |

| Out of Spec           |                              | CINC OK                     | Bau CRC                     | H*L Not OK                       | N/A                              | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

| Fault                 | CRC Ok                       | Bad CRC                     | CRC Ok                      | N/A                              | H*S Ok                           | N/A                             | 0      | Receiver<br>High  | Receiver<br>Sum1  |

| i aut                 | CINC OK                      | Bau CRC                     | CINC OK                     | N/A                              | H*S Not OK                       | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

| Fault L               | CRC Ok                       | Bad CRC                     | Bad CRC                     | N/A                              | N/A                              | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

| Fault                 | Bad CRC                      | CRC OK                      | CRC OK                      | N/A                              | N/A                              | L*S Ok                          | 0      | Receiver<br>Sum0  | Receiver<br>Low   |

| Fault                 | Bau CRC                      |                             |                             | N/A                              | N/A                              | L*S Not OK                      | 1      | Receiver<br>High  | Receiver<br>Low   |

| Fault H               | Bad CRC                      | CRC Ok                      | Bad CRC                     | N/A                              | N/A                              | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

| Common<br>Mode Noise  | Bad CRC                      | Bad CRC                     | CRC Ok                      | N/A                              | N/A                              | N/A                             | 0      | Receiver<br>Sum0  | Receiver<br>Sum1  |

| Fault                 | Bad CRC                      | Bad CRC                     | Bad CRC                     | N/A                              | N/A                              | N/A                             | 1      | Receiver<br>High  | Receiver<br>Low   |

#### **PSEUDO BUS SWITCHES**

Pseudo Bus Switches are provided on the Channel 0 bus. They allow one channel to communicate via two external bus wire sets (D0H/D0L and DPH/DPL). There is a pseudo bus switch on both the bus high and bus low driver. Upon device reset the bus switches are open. This allows the master to initialize devices on D0H/D0L. After all of these slaves are initialized, the pseudo bus switches can be closed, allowing the devices on DPH/DPL to be initialized.

The Pseudo Bus Switches can only be commanded closed by the BSWH and BSWL bits in the D0EN register. These bits can also open the switch at any time.

The Pseudo Bus Switches have independent thermal shutdown protection. Once the thermal shutdown point is reached, the bus switch is opened (becoming high-impedance) and the BSWH and/or BSWL bit is cleared in the channel 0 DEN register. If this occurs, the Pseudo Bus Switches can only be closed again by setting the BSWH and/ or BSWL bit to a 1 with a write command to the channel 0 DEN register.

#### SPREAD SPECTRUM

The dominant source of radiated electromagnetic interference (EMI) from the DBUS bus is due to the regular periodic frequency of the data bits. At a steady bit rate, the time period for each bit is the same, which results in a steady fundamental frequency plus harmonics. This results in undesired signals appearing at multiples of the frequency that can be strong enough to interfere with a desired signal.

A significant decrease in radiated EMI can be achieved by randomly changing the duration of each bit. This can significantly reduce the amplitude by having the signal spend a much smaller percentage of time at any specific frequency. The signal strength of the fundamental and harmonics are reduced directly by the percentage of time it spends on a specific frequency.

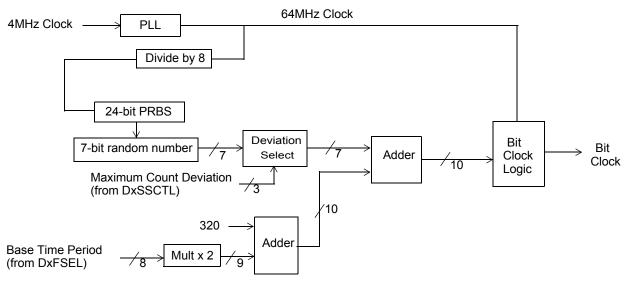

A circuit to do this is included in this IC, and can perform the *spreading* of the signal independently for each channel, while generating the bit clock timing for the channel. This is done in the Spread Spectrum (SS) Block Diagram shown in Figure 12.

To implement the channel bit clock a common 64MHz clock is created from the on board 4MHz oscillator using a digital PLL. Multiples of this clock period (15.625 nsec) are used to select the minimum channel bit time. The Spread

Spectrum block does this by multiplying the 8-bit value in the DxFSEL register by 2 and then adding it to the number 320 (decimal). The user must choose a minimum bit time appropriate for his system. Factors which must be considered are the slave response time, bus wire delays, and the minimum idle time needed to recharge the slave H\_CAPs for the channel.

To spread the spectrum beyond this minimum bit time a random delay based on a multiple of 1/64 MHz periods can be added to each bit. This delay is created by a Pseudo Random Bit Sequence Generator from which a 7-bit random number is created. This number is further qualified by the maximum number of counts (chosen by the DEV[2:0] bits in the DxSSCTL registers) allowed beyond the base time period. The resulting value is added to the minimum bit time and fed to the bit clock logic, which generates the DSI bit clock.

It is important for the user to select a maximum deviation value that is appropriate for the system. A larger maximum deviation results in spreading the bit energy to more frequencies. However, this number also establishes the maximum period for any random bit on that channel. If the system requires that a minimum number of bits be transferred within a fixed time period, then the user must select a minimum base bit time and maximum deviation time that will meet the criteria.

Figure 12. Spread Spectrum Block Diagram

# FUNCTIONAL DEVICE OPERATION

#### LOGIC COMMANDS AND REGISTERS

#### SPI0 COMMUNICATIONS

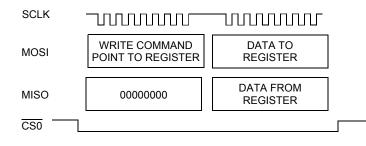

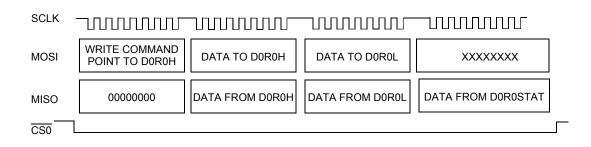

All SPI0 transactions are either 16 or 32-bits long. They start with a command byte and can be followed by 1 or 3 bytes of data. The start of an SPI transaction is signaled by CS0 being asserted low. The first bit sent (bit 7) of the first byte signals a read or write (write = 1) of data. The last seven bits (bits 6–0) of the command set a pointer to the desired register. The 33781 uses 16-bit commands to access control registers, and 32-bit commands to access both control registers, and to queue up transfers over the DBUS. Figure 13 is a diagram of 16-bit transfers and Figure 14 is a diagram of 32-bit transfers. In these multi-byte transfers, as long as CS0 is asserted low, each additional byte sent over the SPI will be a read/write of data to the sequential next register.

33781 utilizes, transmit, and receive addressable FIFOs for sending commands and responses over the DBUS. There are separate command and response registers, and a transmit queue is used to allow up to 4 bus commands to be scheduled for each bus. The transmit queue schedules

commands as a circular buffer, accessing the appropriate command register for the command and data to be sent as the bus becomes available. Data received in response to the commands is queued up for sequential response back to the MCU during the next set of SPI commands. If an SPI0 attempts to write to a transmit register that is not empty the new command will be ignored.

Figure 14 shows an example of a write operation. During the first byte of the SPI transaction, the first MOSI bit is 1 (write), and the last seven are the address of the register to be accessed. During this command byte, MISO returns dummy bits set to all zeros. During the next SPI transactions, MOSI updates the data in the register pointed to in the previous byte with new data, while reading back the old data via MISO.

During an SPI0 transaction the 33781 checks for SPI framing errors. A framing error is defined as any number of clocks received that is not either 16 or 32. If that occurs, all bits sent by the SPI master are discarded and no registers are update.

#### Figure 14. SPI0 32-Bit Burst Transfer Example

The bit definitions for SPI0 depend on the type of SPI transfer, and if the transfer will be to/from the addressable FIFOs, whether the DBUS for that channel is set for Long Words or Enhanced Short words.

# Figure 13 shows the bit encoding for 16-bit SPI0 burst transfers. In this transfer the first byte contains the address of the control register to be written to or read from, and the second byte is the data to be written. The SPI0 response is the data from that register, latched at the falling edge of CS0. If the address pointed to by the first byte is not a control

#### 33781

NP

register, the transfer is considered to have a framing error and no write will occur.

Figure 16 shows the bit encoding for 32-bit SPI0 burst transfers when the DBUS channel is set for long words. In this transfer, the first byte contains the address of the control register to be written to and read from, the second byte is the data to/from that register, and the next two bytes are the data to/from the next numerically successive registers. In the case of reading or writing from the addressable FIFO registers, the 1st data byte would be the DnRnH byte, the next byte would be the DnRnSTAT byte as shown in Figure 15. Notice that in this case, the 4th Tx byte is don't care and is not written. If this transfer would be sent to an address in the control register section of the register bank, the bytes sent and returned would be first the addressed register, and then the next consecutive registers.

Figure 17 shows the bit encoding for 32-bit SPI0 burst transfers when the DBUS channel is set for enhanced short words. This transfer mode is only valid when accessing the

addressable FIFO portion of the register set. In this case, the first byte is again the 1st address of the register to be accessed in this read/write, the second byte contains the upper two bits of the data to be written, and the third byte is the lower 8-bits of data to be written. The SPI0 response encoding begins with the 2nd byte in the transfer with the 4-bit DBUS address of the slave, which sent the data contained in the rest of the word. This is followed by the 10-bits of data from the DBUS slave, and then the value in the DnRnSTAT register.

Although it looks like the read and write for an address are occurring at the same time, the changes caused earlier during the same burst would not be reflected by the data returned, because the DnRnSTAT register is latched at CS0 going low.

Refer to the section SPI0 Register and Bit Descriptions on page 29 for the bit descriptions in Figure 15, Figure 16, and Figure 17.

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| First TX Byte  | R/W   | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

| Second TX Byte | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

| First RX Byte  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Second RX Byte | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| First TX Byte  | R/W   | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

| Second TX Byte | D15   | D14   | D13   | D12   | D11   | D10   | D9    | D8    |

| Third TX Byte  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Fourth TX Byte | х     | х     | х     | х     | х     | х     | х     | х     |

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

| First RX Byte  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Second RX Byte | D15   | D14   | D13   | D12   | D11   | D10   | D9    | D8    |

| Third RX Byte  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Fourth RX Byte | ER    | TE    | SDS   | RNE   | ICL   | 0     | FIX1  | FIX0  |

Figure 16. SPI0 Communications, 32-Bit Burst Transfer Long Word DBUS Transfer Bit Definitions

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| First TX Byte  | R/W   | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

| Second TX Byte | х     | х     | х     | х     | х     | х     | D9    | D8    |

| Third TX Byte  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Fourth TX Byte | х     | х     | х     | х     | х     | х     | х     | х     |

|                | Bit 7 | Bit6  | Blt5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

| First RX Byte  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Second RX Byte | SA3   | SA2   | SA1   | SA0   | 0     | 0     | D9    | D8    |

| Third RX Byte  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Fourth RX Byte | ER    | TE    | SDS   | RNE   | ICL   | 0     | FIX0  | FIX1  |

Figure 17. SPI0 Communications, 32-Bit Burst Transfer Enhanced Short Word DBUS Bit Definitions

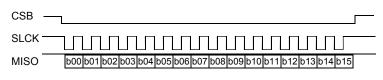

#### **SPI1 COMMUNICATIONS**

All SPI1 transactions are read only, are 16-bits in length, and are asynchronous to SPI0. There is no MOSI pin or function associated with SPI1, since there are no commands sent. Figure 18 shows the signals associated with an SPI1 transfer, and Figure 19 contains the order of bits sent for each SPI1 transaction.