# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **NXP Semiconductors**

**Technical Data**

# Three phase field effect transistor pre-driver

The 33937A is a field effect transistor (FET) pre-drivers designed for three phase motor control and similar applications. It meets the stringent requirements of automotive applications and is fully AEC-Q100 grade 1 qualified.

The IC contains three high-side FET pre-drivers and three low-side FET predrivers. Three external bootstrap capacitors provide gate charge to the highside FETs.

The IC interfaces to a MCU via six direct input control signals, an SPI port for device setup and asynchronous reset, enable and interrupt signals. Both 5.0 and 3.0 V logic level inputs are accepted and 5.0 V logic level outputs are provided. The integrated circuit (IC) uses SMARTMOS technology.

#### Features

- Extended operating range from 6.0 V to 58 V covers 12 V and 42 V systems

- Gate drive capability of 1.0 A to 2.5 A

- Fully specified from 8.0 V to 40 V covers 12 and 24 V automotive systems

- Protection against reverse charge injection from CGD and CGS of external FETs

- · Includes a charge pump to support full FET drive at low battery voltages

- Dead time is programmable via the SPI port

- · Simultaneous output capability enabled via safe SPI command

- AEC-Q100 grade 1 qualified

### 33937A

#### THREE PHASE PRE-DRIVER

#### Applications

Automotive systems

- Cooling fan

- Water pump

- · Actuator controls

- Fuel pump

- Electro-hydraulic and electric power steering

- Engine control

- Motor control

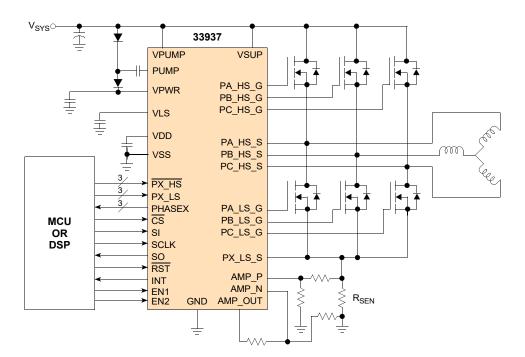

Figure 1. 33937A simplified application diagram

# 1 Orderable parts

#### Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package     |

|----------------------------|-------------------------------|-------------|

| MC33937APEK                | -40 °C to 135 °C              | 54 SOICW-EP |

Notes

1. To order parts in tape and reel, add the R2 suffix to the part number.

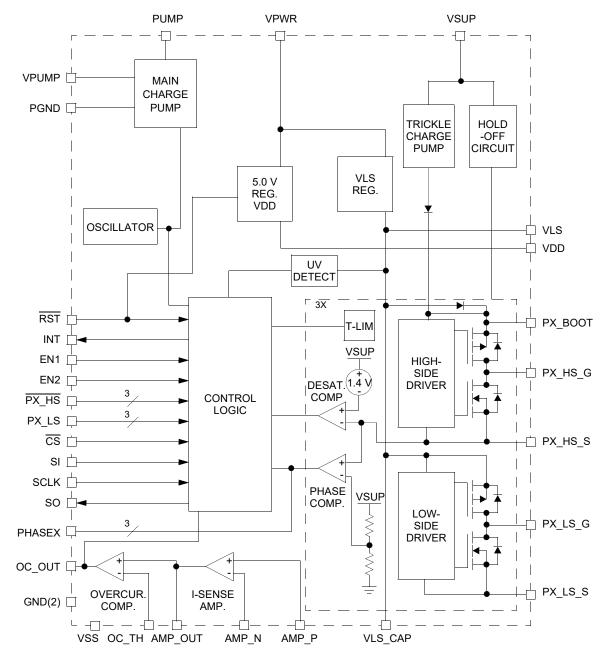

# 2 Internal block diagram

## 3 Pin connections

### 3.1 Pinout diagram

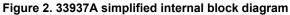

Figure 3. 33937A pin connections

### 3.2 Pin definitions

A functional description of each pin can be found in the Functional pin description section beginning on page 21.

|  | Table 2. | 33937A | pin definitions |

|--|----------|--------|-----------------|

|--|----------|--------|-----------------|

| Pin                      | Pin name | Pin function       | Formal name    | Definition                                                                                                                                          |

|--------------------------|----------|--------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | PHASEA   | Digital Output     | Phase A        | Totem Pole output of Phase A comparator. This output is low when the voltage on PA_HS_S (Source of High-side FET) is less than 50% of $\rm V_{SUP}$ |

| 2                        | PGND     | Ground             | Power Ground   | Power ground for charge pump                                                                                                                        |

| 3                        | EN1      | Digital Input      | Enable 1       | Logic signal input must be high (ANDed with EN2) to enable any gate drive output.                                                                   |

| 4                        | EN2      | Digital Input      | Enable 2       | Logic signal input must be high (ANDed with EN1) to enable any gate drive output                                                                    |

| 5                        | RST      | Digital Input      | Reset          | Reset input                                                                                                                                         |

| 6, 33, 49, 50,<br>52, 53 | N/C      | -                  | No Connect     | Do not connect these pins                                                                                                                           |

| 7                        | PUMP     | Power Drive<br>Out | Pump           | Charge pump output                                                                                                                                  |

| 8                        | VPUMP    | Power Input        | Voltage Pump   | Charge pump supply                                                                                                                                  |

| 9                        | VSUP     | Analog Input       | Supply Voltage | Supply voltage to the load. This pin is to be connected to the common Drains of the external high-side FETs                                         |

#### 33937A

#### Table 2. 33937A pin definitions (continued)

| Pin    | Pin name | Pin function     | Formal name                       | Definition                                                                                                                                          |

|--------|----------|------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | PHASEB   | Digital Output   | Phase B                           | Totem Pole output of Phase B comparator. This output is low when the voltage on PB_HS_S (Source of high-side FET) is less than 50% of $V_{SUP}$     |

| 11     | PHASEC   | Digital Output   | Phase C                           | Totem Pole output of Phase C comparator. This output is low when the voltage on PC_HS_S (Source of high-side FET) is less than 50% of $\rm V_{SUP}$ |

| 12     | PA_HS    | Digital Input    | Phase A High-side                 | Active low input logic signal enables the high-side driver for Phase A                                                                              |

| 13     | PA_LS    | Digital Input    | Phase A Low-side                  | Active high input logic signal enables the low-side driver for Phase A                                                                              |

| 14     | VDD      | Analog<br>Output | VDD Regulator                     | VDD regulator output capacitor connection.                                                                                                          |

| 15     | PB_HS    | Digital Input    | Phase B High-side                 | Active low input logic signal enables the high-side driver for Phase B                                                                              |

| 16     | PB_LS    | Digital Input    | Phase B Low-side                  | Active high input logic signal enables the low-side driver for Phase B                                                                              |

| 17     | INT      | Digital Output   | Interrupt                         | Interrupt pin output                                                                                                                                |

| 18     | CS       | Digital Input    | Chip Select                       | Chip Select input. It frames SPI commands and enables SPI port                                                                                      |

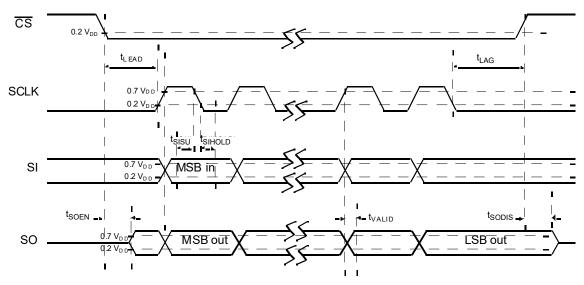

| 19     | SI       | Digital Input    | Serial In                         | Input data for SPI port. Clocked on the falling edge of SCLK, MSB first                                                                             |

| 20     | SCLK     | Digital Input    | Serial Clock                      | Clock for SPI port and typically is 3.0 MHz                                                                                                         |

| 21     | SO       | Digital Output   | Serial Out                        | Output data for SPI port. Tri-state until $\overline{CS}$ becomes low                                                                               |

| 22     | PC_LS    | Digital Input    | Phase C Low-side                  | Active high input logic signal enables the low-side driver for Phase C                                                                              |

| 23     | PC_HS    | Digital Input    | Phase C High-side                 | Active low input logic signal enables the high-side driver for Phase C                                                                              |

| 24     | AMP_OUT  | Analog<br>Output | Amplifier Output                  | Output of the current-sensing amplifier                                                                                                             |

| 25     | AMP_N    | Analog Input     | Amplifier Invert                  | Inverting input of the current-sensing amplifier                                                                                                    |

| 26     | AMP_P    | Analog Input     | Amplifier Non-Invert              | Non-inverting input of the current-sensing amplifier                                                                                                |

| 27     | OC_OUT   | Digital Output   | Overcurrent Out                   | Totem pole digital output of the overcurrent comparator                                                                                             |

| 28     | OC_TH    | Analog Input     | Overcurrent Threshold             | Threshold of the overcurrent detector                                                                                                               |

| 29     | VSS      | Ground           | Voltage Source Supply             | Ground reference for logic interface and power supplies                                                                                             |

| 30, 31 | GND      | Ground           | Ground                            | Substrate and ESD reference, connect to VSS                                                                                                         |

| 32     | VLS_CAP  | Analog<br>Output | VLS Regulator Output<br>Capacitor | VLS Regulator connection for additional output capacitor, providing low-<br>impedance supply source for low-side gate drive                         |

| 34     | PC_LS_S  | Power Input      | Phase C Low-side<br>Source        | Source connection for Phase C low-side FET                                                                                                          |

| 35     | PC_LS_G  | Power Output     | Phase C Low-side<br>Gate Drive    | Gate drive output for Phase C low-side                                                                                                              |

| 36     | PC_HS_S  | Power Input      | Phase C High-side<br>Source       | Source connection for Phase C high-side FET                                                                                                         |

| 37     | PC_HS_G  | Power Output     | Phase C High-side<br>Gate Drive   | Gate Drive for output Phase C high-side FET                                                                                                         |

| 38     | PC_BOOT  | Analog Input     | Phase C Bootstrap                 | Bootstrap capacitor for Phase C                                                                                                                     |

| 39     | PB_LS_S  | Power Input      | Phase B Low-side<br>Source        | Source connection for Phase B low-side FET                                                                                                          |

| 40     | PB_LS_G  | Power Output     | Phase B Low-side<br>Gate Drive    | Gate Drive for output Phase B low-side                                                                                                              |

| 41     | PB_HS_S  | Power Input      | Phase B High-side<br>Source       | Source connection for Phase B high-side FET                                                                                                         |

| 42     | PB_HS_G  | Power Output     | Phase B High-side<br>Gate Drive   | Gate Drive for output Phase B high-side                                                                                                             |

| 43     | PB_BOOT  | Analog Input     | Phase B Bootstrap                 | Bootstrap capacitor for Phase B                                                                                                                     |

| 44     | PA_LS_S  | Power Input      | Phase A Low-side<br>Source        | Source connection for Phase A low-side FET                                                                                                          |

| Table 2. | 33937A | pin | definitions | (continued) |

|----------|--------|-----|-------------|-------------|

|----------|--------|-----|-------------|-------------|

| Pin | Pin name | Pin function     | Formal name                     | Definition                                                                                                                                                                     |

|-----|----------|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45  | PA_LS_G  | Power Output     | Phase A Low-side<br>Gate Drive  | Gate Drive for output Phase A low-side                                                                                                                                         |

| 46  | PA_HS_S  | Power Input      | Phase A High-side<br>Source     | Source connection for Phase A high-side FET                                                                                                                                    |

| 47  | PA_HS_G  | Power Output     | Phase A High-side<br>Gate Drive | Gate Drive for output Phase A high-side                                                                                                                                        |

| 48  | PA_BOOT  | Analog Input     | Phase A Bootstrap               | Bootstrap capacitor for Phase A                                                                                                                                                |

| 51  | VLS      | Analog<br>Output | VLS Regulator                   | VLS regulator output. Power supply for the gate drives                                                                                                                         |

| 54  | VPWR     | Power Input      | Voltage Power                   | Power supply input for gate drives                                                                                                                                             |

|     | EP       | Ground           | Exposed Pad                     | Device will perform as specified with the exposed pad un-terminated (floating) however, it is recommended that the exposed pad be terminated to pin 29 (VSS) and system ground |

# 4 Electrical characteristics

### 4.1 Maximum ratings

#### Table 3. Maximum ratings

All voltages are with respect to V<sub>SS</sub> unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                           | Ratings                                                                                                                                                                         | Value                                                       | Unit | Notes |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-------|

| Electrical rating                                                                | s                                                                                                                                                                               |                                                             |      |       |

| V <sub>SUP</sub>                                                                 | VSUP Supply Voltage<br>• Normal Operation (Steady-state)<br>• Transient Survival                                                                                                | 58<br>-1.5 to 80                                            | V    | (2)   |

| V <sub>PWR</sub>                                                                 | VPWR Supply Voltage <ul> <li>Normal Operation (Steady-state)</li> <li>Transient Survival</li> </ul>                                                                             | 58<br>-1.5 to 80                                            | V    | (2)   |

| V <sub>PUMP</sub>                                                                | Charge Pump (PUMP, VPUMP)                                                                                                                                                       | -0.3 to 40                                                  | V    |       |

| V <sub>LS</sub>                                                                  | VLS Regulator Outputs (VLS, VLS_CAP)                                                                                                                                            | -0.3 to 18                                                  | V    |       |

| V <sub>DD</sub>                                                                  | Logic Supply Voltage                                                                                                                                                            | -0.3 to 7.0                                                 | V    |       |

| V <sub>OUT</sub>                                                                 | Logic Output (INT, SO, PHASEA, PHASEB, PHASEC, OC_OUT)                                                                                                                          | -0.3 to 7.0                                                 | V    | (3)   |

| V <sub>IN</sub>                                                                  | Logic Input Pin Voltage (EN1, EN2, Px_HS, Px_LS, SI, SCLK, CS, RST) 10 mA                                                                                                       | -0.3 to 7.0                                                 | V    |       |

| V <sub>IN_A</sub>                                                                | Amplifier Input Voltage<br>• (Both Inputs-GND), (AMP_P - GND) or (AMP_N - GND) 6.0 mA source or sink                                                                            | -7.0 to 7.0                                                 | V    |       |

| V <sub>OC</sub>                                                                  | Overcurrent comparator threshold 10 mA                                                                                                                                          | -0.3 to 7.0                                                 | V    |       |

| V <sub>BOOT</sub><br>V <sub>HS_G</sub><br>V <sub>LS_G</sub>                      | Driver Output Voltage<br>• High-side bootstrap (PA_BOOT, PB_BOOT, PC_BOOT)<br>• High-side (PA_HS_G, PB_HS_G, PC_HS_G)<br>• Low-side (PA_LS_G, PB_LS_G, PC_LS_G)                 | 75<br>75<br>16                                              | v    | (4)   |

| V <sub>HS_G</sub><br>V <sub>HS_S</sub><br>V <sub>LS_G</sub><br>V <sub>LS_S</sub> | Driver Voltage Transient Survival<br>• High-side (PA_HS_G, PB_HS_G, PC_HS_G, PA_HS_S, PB_HS_S,<br>PC_HS_S)<br>• Low-side (PA_LS_G, PB_LS_G, PC_LS_G, PA_LS_S, PB_LS_S, PC_LS_S) | -7.0 to 75.0<br>-7.0 to 75.0<br>-7.0 to 18.0<br>-7.0 to 7.0 | v    | (5)   |

| V <sub>ESD</sub>                                                                 | ESD Voltage<br>• Human Body Model - HBM (All pins except for the pins listed below)<br>Pins: PA_Boot, PA_HS_S, PA_HS_G, PB_Boot, PB_HS_S, PB_HS_G,                              |                                                             | v    | (6)   |

Notes

2. The device will withstand load dump transient as defined by ISO7637 with peak voltage of 80 V.

3. Short-circuit proof, the device will not be damaged or induce unexpected behavior due to shorts to external sources within this range.

4. This voltage should not be applied without also taking voltage at HS\_S and voltage at PX\_LS\_S into account.

Actual operational limitations may differ from survivability limits. The V<sub>LS</sub> - V<sub>LS\_S</sub> differential and the V<sub>BOOT</sub> - V<sub>HS\_S</sub> differential must be greater than 3.0 V to insure the output gate drive will maintain a commanded OFF condition on the output.

ESD testing is performed in accordance with the Human Body Model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω) and the Charge Device Model (CDM), Robotic (C<sub>ZAP</sub> = 4.0 pF).

#### Table 3. Maximum ratings (continued)

All voltages are with respect to V<sub>SS</sub> unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol          | Ratings | Value | Unit | Notes |

|-----------------|---------|-------|------|-------|

| Thermal ratings |         |       |      |       |

| 0                   |                                          |             |      |     |

|---------------------|------------------------------------------|-------------|------|-----|

| T <sub>STG</sub>    | Storage Temperature                      | -55 to +150 | °C   |     |

| TJ                  | Operating Junction Temperature           | -40 to +150 | °C   |     |

| R <sub>θJC</sub>    | Thermal Resistance<br>• Junction-to-Case | 3.0         | °C/W | (7) |

| T <sub>SOLDER</sub> | Soldering Temperature                    | Note 9      | °C   | (8) |

Notes

7. Case is considered EP - pin 55 under the body of the device. The actual power dissipation of the device is dependent on the operating mode, the heat transfer characteristics of the board and layout and the operating voltage. See Figure 24 and Figure 25 for examples of power dissipation profiles of two common configurations. Operation above the maximum operating junction temperature will result in a reduction in reliability leading to malfunction or permanent damage to the device.

- 8. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to www.nxp.com, search by part number (remove prefixes/suffixes and enter the core ID) to view all orderable parts, and review parametrics.

### 4.2 Static electrical characteristics

#### Table 4. Static electrical characteristics

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol              | Characteristic                                                                                                                     | Min. | Тур.     | Max.    | Unit | Notes |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|------|----------|---------|------|-------|

| Power inputs        |                                                                                                                                    |      |          | 1       | 1    |       |

| V <sub>PWR_ST</sub> | VPWR Supply Voltage Startup Threshold                                                                                              | -    | 6.0      | 8.0     | V    | (10)  |

|                     | VSUP Supply Current, V <sub>PWR</sub> = V <sub>SUP</sub> = 40 V, RST and<br>ENABLE = 5.0 V                                         |      |          |         |      |       |

| I <sub>SUP</sub>    | <ul> <li>No output loads on Gate Drive Pins, No PWM</li> <li>No output loads on Gate Drive Pins, 20 kHz, 50% Duty Cycle</li> </ul> | _    | 1.0<br>- | -<br>10 | mA   |       |

|                     | VPWR Supply Current, V <sub>PWR</sub> = V <sub>SUP</sub> = 40 V, RST and<br>ENABLE = 5.0 V                                         |      |          |         |      |       |

| I <sub>PWR_ON</sub> | No output loads on Gate Drive Pins, No PWM, Outputs initialized                                                                    | _    | 11       | 20      | mA   |       |

|                     | • Output Loads = 620 nC per FET, 20 kHz PWM                                                                                        | -    | -        | 95      |      | (11)  |

|                     | Sleep State Supply Current, RST = 0 V                                                                                              |      |          |         |      |       |

| I <sub>SUP</sub>    | • V <sub>SUP</sub> = 40 V                                                                                                          | _    | 14       | 30      | μA   |       |

| I <sub>PWR</sub>    | • V <sub>PWR</sub> = 40 V                                                                                                          | -    | 56       | 100     |      |       |

| V                   | Sleep State Output Gate Voltage                                                                                                    | _    | _        | 1.3     | V    |       |

| V <sub>GATESS</sub> | • IG < 100 µA                                                                                                                      | _    |          | 1.5     | V    |       |

| V <sub>Boot</sub>   | Trickle Charge Pump (Bootstrap Voltage)<br>• V <sub>SUP</sub> = 14 V                                                               | 22   | 28       | 32      | V    | (15)  |

| V <sub>F</sub>      | Bootstrap Diode Forward Voltage at 10 mA                                                                                           | _    | _        | 1.2     | V    |       |

| /DD internal reg    | ulator                                                                                                                             |      | •        | •       | •    |       |

| V <sub>DD</sub>     | V <sub>DD</sub> Output Voltage, V <sub>PWR</sub> = 8 to 40 V, C = 0.47 μF<br>• External Load I <sub>DD_EXT</sub> = 0 to 1.0 mA     | 4.5  | _        | 5.5     | V    | (12)  |

| I <sub>DD</sub>     | Internal $V_{DD}$ Supply Current, $V_{DD}$ = 5.5 V, No External Load                                                               | _    | -        | 12      | mA   |       |

| /LS regulator       |                                                                                                                                    |      |          |         |      |       |

| I <sub>PEAK</sub>   | Peak Output Current, V <sub>PWR</sub> = 16 V, V <sub>LS</sub> = 10 V                                                               | 350  | 600      | 800     | mA   |       |

| V <sub>LS</sub>     | Linear Regulator Output Voltage, $I_{VLS}$ = 0 to 60 mA, $V_{PWR}$ > $V_{LS}$ + 2.0 V                                              | 13.5 | 15       | 17      | V    | (13)  |

Notes

V<sub>THVLS</sub>

10. Operation with the Charge Pump is recommended when minimum system voltage could be less than 14 V. V<sub>PWR</sub> must exceed this threshold in order for the Charge Pump and V<sub>DD</sub> regulator to startup and drive V<sub>PWR</sub> to > 8.0 V. Once V<sub>PWR</sub> exceeds 8.0 V, the circuits will continue to operate even if system voltage drops below 6.0 V.

8.0

8.5

7.5

V

11. This parameter is guaranteed by design. It is not production tested.

12. Minimum external capacitor for stable  $V_{\text{DD}}$  operation is 0.47  $\mu\text{F}.$

VLS Disable Threshold

13. Recommended external capacitor for the V<sub>LS</sub> regulator is 2.2 µF low ESR at each pin VLS and VLS\_CAP.

14. When V<sub>LS</sub> is less than this value, the outputs are disabled and HOLDOFF circuits are active. Recovery requires initialization when V<sub>LS</sub> rises above this threshold again. A filter delay of approximately 700 ns on the comparator output eliminates responses to spurious transients on V<sub>LS</sub>.

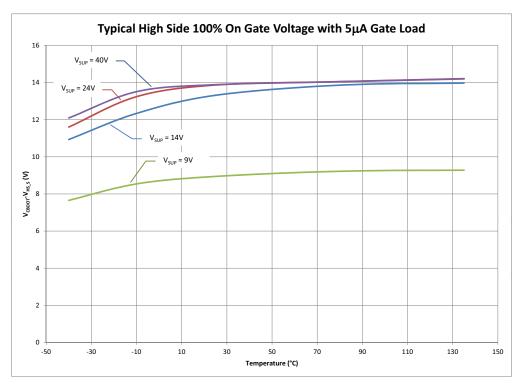

15. See Figure 11 for typical capability to maintain gate voltage with a 5.0 µA load.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                                                          | Min. | Тур. | Max. | Unit | Notes       |

|-----------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|-------------|

| Charge pump                 | 1                                                                                       |      |      |      |      |             |

|                             | Charge Pump                                                                             |      |      |      |      |             |

| R <sub>DS(on)_HS</sub>      | High-side Switch On Resistance                                                          | -    | 6.0  | 10   | Ω    |             |

| R <sub>DS(on)_LS</sub>      | Low-side Switch On Resistance                                                           | -    | 5.0  | 9.4  | Ω    | (4.0) (4.0) |

| V <sub>THREG</sub>          | Regulation Threshold Difference                                                         | 250  | 500  | 900  | mV   | (16), (18)  |

|                             | Charge Pump Output Voltage                                                              |      |      |      |      |             |

| V <sub>CP</sub>             | • I <sub>OUT</sub> = 40 mA, 6.0 V < V <sub>SYS</sub> < 8.0 V                            | 8.5  | 9.5  | _    | V    | (17), (18)  |

|                             | • I <sub>OUT</sub> = 40 mA, V <sub>SYS</sub> > = 8.0 V                                  | 12   | -    | -    |      |             |

| Gate drive                  |                                                                                         |      |      |      | 1    |             |

|                             | High-side Driver On Resistance (Sourcing)                                               |      |      |      |      |             |

| R <sub>DS(on)_H_SRC</sub>   | • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 25 °C | _    | _    | 6.0  | Ω    |             |

| D0(01)_11_01(0              | • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V, 25 °C < T <sub>A</sub> $\leq$ 135 °C      | -    | -    | 8.5  |      |             |

|                             | High-side Driver On Resistance (Sinking)                                                |      |      |      |      |             |

| R <sub>DS(on)_</sub> H_SINK | • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V                                            | -    | -    | 3.0  | Ω    |             |

| I <sub>HS_INJ</sub>         | High-side Current Injection Allowed Without Malfunction                                 | _    | -    | 0.5  | А    | (18), (19)  |

|                             | Low-side Driver On Resistance (Sourcing)                                                |      |      |      |      |             |

| R <sub>DS(on) L SRC</sub>   | • $V_{PWR}$ = $V_{SUP}$ = 16 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 25 °C               | _    | _    | 6.0  | Ω    |             |

| 20(01)_2_0110               | • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V, 25 °C < T <sub>A</sub> $\leq$ 135 °C      | -    | -    | 8.5  |      |             |

| _                           | Low-side Driver On-Resistance (Sinking)                                                 |      |      |      |      |             |

| R <sub>DS(on)_</sub> L_SINK | • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V                                            | -    | -    | 3.0  | Ω    |             |

| I <sub>LS_INJ</sub>         | Low-side Current Injection Allowed Without Malfunction                                  | _    | -    | 0.5  | А    | (18), (19)  |

|                             | Gate Source Voltage, V <sub>PWR</sub> = V <sub>SUP</sub> = 40 V                         |      |      |      |      |             |

| V <sub>GS_H</sub>           | • High-side, I <sub>GATE</sub> = 0                                                      | 13   | 14.8 | 16.5 | V    | (20)        |

| V <sub>GS_L</sub>           | • Low-side, I <sub>GATE</sub> = 0                                                       | 13   | 15.4 | 17   |      |             |

|                             | Reverse High-side Gate Holding Voltage                                                  |      |      |      |      |             |

|                             | Gate Output Holding Current = 2.0 µA                                                    | _    | 10   | 15   |      | (04)        |

| $V_{HS_G_HOLD}$             | Gate Output Holding Current = $5.0 \mu$ A, V <sub>SUP</sub> <26 V                       | _    | 10   | 15   | V    | (21)        |

|                             |                                                                                         | _    | _    | 15   |      |             |

|                             | Gate Output Holding Current = 5.0 μA, V <sub>SUP</sub> <40 V                            |      |      | _    |      |             |

Notes

16. When VLS is this amount below the normal VLS linear regulation threshold, the charge pump is enabled.

17. V<sub>SYS</sub> is the system voltage on the input to the charge pump. Recommended external components: 1.0 µF MLC, MUR 120 diode.

18. This parameter is a design characteristic, not production tested.

19. Current injection only occurs during output switch transitions. The IC is immune to specified injected currents for a duration of approximately 1.0 µs after an output switch transition. 1.0 µs is sufficient for all intended applications of this IC.

20. If a slightly higher gate voltage is required, larger bootstrap capacitors are required. At high duty cycles, the bootstrap voltage may not recover completely, leading to a higher output on-resistance. This effect can be minimized by using low ESR capacitors for the bootstrap and the VLS capacitors.

21. High-side Gate Holding voltage is the voltage between the Gate and Source of the high-side FET when held in an on condition. The trickle charge pump supplies bias and holding current for the High-side FET gate driver and output to maintain voltages after bootstrap events. See Figure 11 for typical 100% high-side gate voltage with a 5.0 μA load. This parameter is a design characteristic, not production tested.

#### 33937A

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                             | Characteristic                                                                                                        | Min.                      | Тур. | Max.                   | Unit  | Notes     |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------------|-------|-----------|

| vercurrent con                     | nparator                                                                                                              |                           |      | -11                    |       |           |

| V <sub>CM</sub>                    | Common Mode Input Range                                                                                               | 2.0                       | _    | V <sub>DD</sub> -0.02  | V     | (23)      |

| V <sub>OS_OC</sub>                 | Input Offset Voltage                                                                                                  | -50                       | _    | 50                     | mV    |           |

| V <sub>OC_HYST</sub>               | Overcurrent Comparator Threshold Hysteresis                                                                           | 50                        |      | 300                    | mV    | (22)      |

| V <sub>OH</sub><br>V <sub>OL</sub> | Output Voltage<br>• High Level at I <sub>OH</sub> = -500 μA<br>• Low Level at I <sub>OL</sub> = 500 μA                | 0.85 V <sub>DD</sub><br>- |      | V <sub>DD</sub><br>0.5 | V     |           |

| old off circuit                    |                                                                                                                       |                           |      |                        |       |           |

| I <sub>HOLD</sub>                  | Hold Off Current (At Each GATE Pin)<br>• 3.0 V < V <sub>SUP</sub> < 40 V, V <sub>GATE</sub> = 1.0 V                   | 10                        | _    | 300                    | μA    | (24)      |

| hase comparat                      | or                                                                                                                    |                           |      | 1 1                    |       |           |

| V <sub>IH_TH</sub>                 | High Level Input Voltage Threshold                                                                                    | 0.5 V <sub>SUP</sub>      | -    | $0.65  V_{SUP}$        | V     |           |

| V <sub>IL_TH</sub>                 | Low Level Input Voltage Threshold                                                                                     | 0.3 V <sub>SUP</sub>      | -    | $0.45  V_{SUP}$        | V     |           |

| V <sub>OH</sub>                    | High Level Output Voltage at I <sub>OH</sub> = -500 µA                                                                | 0.85 V <sub>DD</sub>      | -    | V <sub>DD</sub>        | V     |           |

| V <sub>OL</sub>                    | Low Level Output Voltage at I <sub>OL</sub> = 500 μA                                                                  | -                         | _    | 0.5                    | V     |           |

| R <sub>IN</sub>                    | High-side Source Input Resistance                                                                                     | -                         | 40   | -                      | kΩ    | (22), (27 |

| esaturation de                     | tector                                                                                                                |                           |      |                        |       |           |

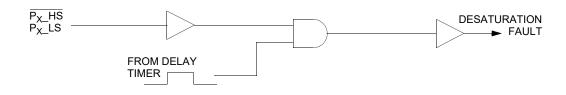

| V <sub>DES_TH</sub>                | Desaturation Detector Threshold                                                                                       | 1.2                       | 1.4  | 1.6                    | V     | (25)      |

| urrent sense a                     | mplifier                                                                                                              | I                         |      |                        |       |           |

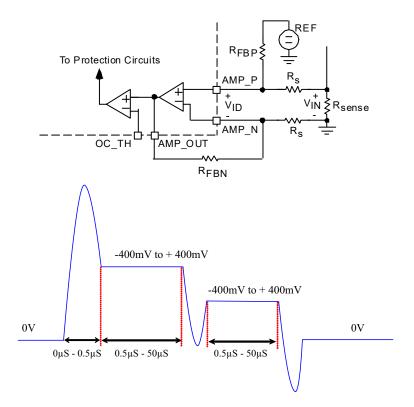

| R <sub>S</sub>                     | Recommended External Series Resistor (See Figure 9)                                                                   | -                         | 1.0  | -                      | kW    |           |

| R <sub>FB</sub>                    | Recommended External Feedback Resistor (See Figure 9) <ul> <li>Limited by the Output Voltage Dynamic Range</li> </ul> | 5.0                       | _    | 15                     | kW    | (28)      |

| V <sub>ID</sub>                    | Maximum Input Differential Voltage (See Figure 9)<br>• V <sub>ID</sub> = V <sub>AMP_P</sub> - V <sub>AMP_N</sub>      | -800                      | _    | +800                   | mV    |           |

| V <sub>CM</sub>                    | Input Common Mode Range                                                                                               | -0.5                      | _    | 3.0                    | V     | (22), (26 |

| V <sub>OS</sub>                    | Input Offset Voltage<br>• $R_S = 1.0 \text{ k}\Omega$ , $V_{CM} = 0.0 \text{ V}$                                      | -15                       | _    | +15                    | mV    |           |

| δV <sub>OS</sub> /δT               | Input Offset Voltage Drift                                                                                            | -                         | -10  | -                      | µV/°C | (22)      |

| I <sub>b</sub>                     | Input Bias Current<br>• V <sub>CM</sub> = 2.0 V                                                                       | -200                      | _    | +200                   | nA    |           |

Notes

22. This parameter is a design characteristic, not production tested.

23. As long as one input is in the common mode range there is no phase inversion on the output.

24. The hold off circuit is designed to operate over the full operating range of V<sub>SUP</sub>. The specification indicates the conditions used in production test. Hold off is activated at V<sub>POR</sub> or V<sub>THVLS</sub>.

25. Desaturation is measured as the voltage drop below V<sub>SUP</sub>, thus the threshold is compared to the drain-source voltage of the external High-side FET. See Figure 5.

26. As long as one input is within V<sub>CM</sub> the output is guaranteed to have the correct phase. Exceeding the common mode rails on one input will not cause a phase inversion on the output.

27. Input resistance is impedance from the high-side source and is referenced to V<sub>SS</sub>. Approximate tolerance is ±20%.

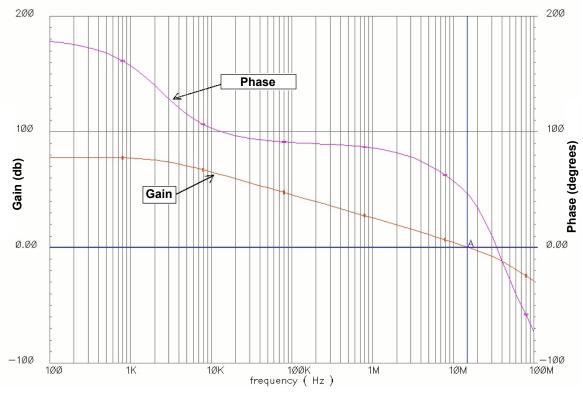

28. The current sense amplifier is unity gain stable with a phase margin of approximately 45°. See Figure 10.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                             | Characteristic                                                                                                                                     | Min.                      | Тур. | Max.                   | Unit  | Notes      |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------------|-------|------------|

| Current sense ar                   | nplifier (continued)                                                                                                                               |                           |      |                        |       |            |

| I <sub>OS</sub>                    | Input Offset Current<br>• I <sub>OS</sub> = I <sub>AMP_P</sub> - I <sub>AMP_N</sub>                                                                | -80                       | _    | +80                    | nA    |            |

| δΙ <sub>ΟS</sub> /δΤ               | Input Offset Current Drift                                                                                                                         | -                         | 40   | _                      | pA/°C | (29)       |

| V <sub>OH</sub><br>V <sub>OL</sub> | Output Voltage<br>• High Level with R <sub>LOAD</sub> = 10 kΩ to V <sub>SS</sub><br>• Low Level with R <sub>LOAD</sub> = 10 kΩ to V <sub>DD</sub>  | V <sub>DD</sub> -0.2<br>- |      | V <sub>DD</sub><br>0.2 | V     |            |

| R <sub>I</sub>                     | Differential Input Resistance                                                                                                                      | 1.0                       | -    | -                      | MΩ    |            |

| I <sub>SC</sub>                    | Output Short-circuit Current                                                                                                                       | 5.0                       | -    | -                      | mA    |            |

| Cl                                 | Common Mode Input Capacitance at 10 kHz                                                                                                            | -                         | -    | 10                     | pF    | (29), (30) |

| CMRR                               | Common Mode Rejection Ratio at DC<br>• CMRR = 20*Log ((V <sub>OUT_DIFF</sub> /V <sub>IN_DIFF</sub> ) * (V <sub>IN_CM</sub> /V <sub>OUT_CM</sub> )) | 60                        | 80   | _                      | dB    |            |

| A <sub>OL</sub>                    | Large Signal Open Loop Voltage Gain (DC)                                                                                                           | _                         | 78   | _                      | dB    | (29), (30) |

| NL                                 | Nonlinearity<br>• RL = 1.0 kΩ, C <sub>L</sub> = 500 pF, 0.3 < V <sub>O</sub> < 4.8 V, Gain = 5.0 to 15                                             | -1.0                      | _    | +1.0                   | %     | (29), (30) |

Notes

29. This parameter is a design characteristic, not production tested.

30. Without considering any offsets such as input offset voltage, internal mismatch and assuming no tolerance error in external resistors.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                             | Characteristic                                                                                                                                  | Min.                 | Тур. | Max.                | Unit | Notes      |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|---------------------|------|------------|

| upervisory and                     | l control circuits                                                                                                                              |                      |      |                     |      |            |

| V <sub>IH</sub><br>V <sub>IL</sub> | Logic Inputs (Px_LS, Px_HS, EN1, EN2) <ul> <li>High Level Input Voltage Threshold</li> <li>Low Level Input Voltage Threshold</li> </ul>         | 2.1                  |      | _<br>0.9            | V    | (32)       |

| V <sub>IH</sub><br>V <sub>IL</sub> | Logic Inputs (SI, SCLK, CS) <ul> <li>High Level Input Voltage Threshold</li> <li>Low Level Input Voltage Threshold</li> </ul>                   | 2.1                  | -    | _<br>0.9            | V    | (31), (32) |

| V <sub>IHYS</sub>                  | Input Logic Threshold Hysteresis<br>• Inputs Px_LS, SI, SCLK, CS, Px_HS, EN1, EN2                                                               | 100                  | 250  | 450                 | mV   | (31)       |

| I <sub>INPD</sub>                  | Input Pull-down Current, (Px_LS, SI, SCLK, EN1, EN2)<br>• 0.3 $V_{DD} \le V_{IN} \le V_{DD}$                                                    | 8.0                  | _    | 18                  | μA   |            |

| I <sub>INPU</sub>                  | Input Pull-up Current, ( $\overline{CS}$ , $\overline{Px_HS}$ )<br>• 0 ≤ V <sub>IN</sub> ≤ 0.7 V <sub>DD</sub>                                  | 10                   | _    | 25                  | μA   | (33)       |

| C <sub>IN</sub>                    | Input Capacitance<br>• 0.0 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V                                                                                | _                    | 15   | -                   | pF   | (31)       |

| V <sub>TH_RST</sub>                | RST Threshold                                                                                                                                   | 1.0                  | -    | 2.1                 | V    | (34)       |

| R <sub>RST</sub>                   | RST Pull-down Resistance• $0.3 V_{DD} \le V_{IN} \le V_{DD}$                                                                                    | 40                   | 60   | 85                  | kW   |            |

| V <sub>POR</sub>                   | Power-OFF RST Threshold, (V <sub>DD</sub> Falling)                                                                                              | 3.4                  | 4.0  | 4.5                 | V    |            |

| V <sub>SOH</sub>                   | SO High Level Output Voltage<br>• I <sub>OH</sub> = 1.0 mA                                                                                      | 0.9 V <sub>DD</sub>  | _    | -                   | V    |            |

| V <sub>SOL</sub>                   | SO Low Level Output Voltage<br>• I <sub>OL</sub> = 1.0 mA                                                                                       | _                    | _    | 0.1 V <sub>DD</sub> | V    |            |

| I <sub>SO_LEAK_T</sub>             | SO Tri-state Leakage Current<br>• $\overline{CS}$ = 0.7 V <sub>DD</sub> . 0.3 V <sub>DD</sub> $\leq$ V <sub>SO</sub> $\leq$ 0.7 V <sub>DD</sub> | -1.0                 | _    | 1.0                 | μA   |            |

| C <sub>SO_T</sub>                  | SO Tri-state Capacitance<br>• 0.0 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V                                                                         | _                    | 15   | -                   | pF   | (31), (35) |

| V <sub>OH</sub>                    | INT High Level Output Voltage<br>• I <sub>OH</sub> = -500 μA                                                                                    | 0.85 V <sub>DD</sub> | _    | V <sub>DD</sub>     | V    |            |

| V <sub>OL</sub>                    | INT Low Level Output Voltage<br>• I <sub>OL</sub> = 500 μA                                                                                      | _                    | _    | 0.5                 | V    |            |

Thermal warning

| T <sub>WARN</sub> | Thermal Warning Temperature | 150 | 170 | 185 | °C | (31), (36) |

|-------------------|-----------------------------|-----|-----|-----|----|------------|

| T <sub>HYST</sub> | Thermal Hysteresis          | 8.0 | 10  | 12  | °C | (31)       |

Notes

31. This parameter is guaranteed by design, not production tested.

32. Logic threshold voltages derived relative to a 3.3 V 10% system.

33. Pull-up circuits will not allow back biasing of V<sub>DD</sub>.

34. There are two elements in the RST circuit: 1) one generally lower threshold enables the internal regulator; 2) the second removes the reset from the internal logic.

35. This parameter applies to the OFF state (tri-stated) condition of SO is guaranteed by design but is not production tested.

36. The Thermal Warning circuit does not force IC shutdown above this temperature. It is possible to set a bit in the MASK register to generate an interrupt when overtemperature is detected, and the status bit will always indicate if any of the three individual Thermal Warning circuits in the IC sense a fault.

### 4.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol              | Characteristic                                                                                           | Min.     | Тур. | Max. | Unit | Notes      |

|---------------------|----------------------------------------------------------------------------------------------------------|----------|------|------|------|------------|

| nternal regulato    | brs                                                                                                      |          | 1    |      |      |            |

| t <sub>PU_VDD</sub> | $V_{DD}$ Power-up Time (Until INT High)<br>• 8.0 V $\leq$ V <sub>PWR</sub>                               | _        | -    | 2.0  | ms   | (37), (39) |

| t <sub>PU_VLS</sub> | VLS Power-up Time<br>• 16 V $\leq$ V <sub>PWR</sub>                                                      | _        | _    | 2.0  | ms   | (38), (39) |

| Charge pump         |                                                                                                          |          |      |      |      |            |

| F <sub>OSC</sub>    | Charge Pump Oscillator Frequency                                                                         | 90       | 125  | 190  | kHz  |            |

| SR <sub>CP</sub>    | Charge Pump Slew Rate                                                                                    | -        | 100  | -    | V/µs | (40)       |

| Gate drive          |                                                                                                          | <b>I</b> |      | I    | 1    |            |

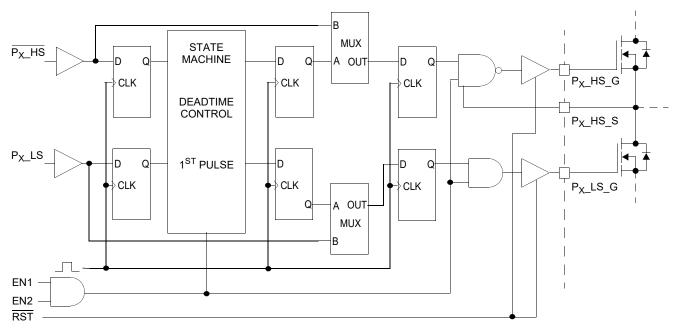

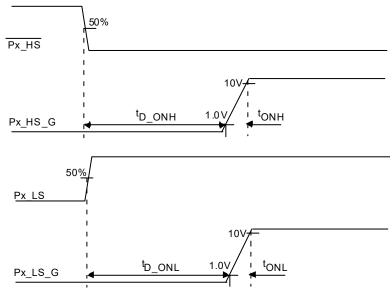

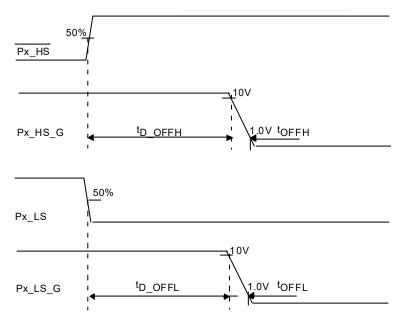

| t <sub>ONH</sub>    | High-side Turn On Time<br>• Transition Time from 1.0 V to 10 V, Load: C = 500 pF, Rg = 0,<br>(Figure 7)  | _        | 20   | 35   | ns   | (41)       |

| t <sub>D_ONH</sub>  | High-side Turn On Delay<br>• Delay from Command to 1.0 V, (Figure 7)                                     | 130      | 265  | 386  | ns   | (42)       |

| t <sub>OFFH</sub>   | High-side Turn Off Time<br>• Transition Time from 10 V to 1.0 V, Load: C = 500 pF, Rg = 0,<br>(Figure 8) | _        | 20   | 35   | ns   | (41)       |

| t <sub>D_OFFH</sub> | High-side Turn Off Delay<br>• Delay from Command to 10 V, (Figure 8)                                     | 130      | 265  | 386  | ns   | (42)       |

| t <sub>ONL</sub>    | Low-side Turn On Time<br>• Transition Time from 1.0 V to 10 V, Load: C = 500 pF, Rg = 0,<br>(Figure 7)   | _        | 20   | 35   | ns   | (41)       |

| t <sub>D_ONL</sub>  | Low-side Turn On Delay<br>• Delay from Command to 1.0 V, (Figure 7)                                      | 130      | 265  | 386  | ns   | (42)       |

| t <sub>OFFL</sub>   | Low-side Turn Off Time<br>• Transition Time from 10 V to 1.0 V, Load: C = 500 pF, Rg = 0,<br>(Figure 8)  | -        | 20   | 35   | ns   | (41)       |

| t <sub>D_OFFL</sub> | Low-side Turn Off Delay<br>• Delay from Command to 10 V, (Figure 8)                                      | 130      | 265  | 386  | ns   | (42)       |

Notes

37. The power-up time of the IC depends in part on the time required for this regulator to charge up the external filter capacitor on V<sub>DD</sub>.

38. The power-up time of the IC depends in part on the time required for this regulator to charge up the external filter capacitors on VLS and VLS\_CAP. This delay includes the expected time for V<sub>DD</sub> to rise.

39. This specification is based on capacitance of 0.47 µF on VDD, 2.2 µF on VLS and 2.2 µF on VLS\_CAP.

40. The charge pump operating at 12 V  $V_{SYS},$  1.0  $\mu F$  pump capacitor, MUR120 diodes and 47  $\mu F$  filter capacitor.

41. This parameter is guaranteed by characterization, not production tested.

42. These delays include all logic delays except deadtime. All internal logic is synchronous with the internal clock. The total delay includes one clock period for state machine decision block, an additional clock period for FULLON mux logic, input synchronization time and output driver propagation delay. Subtract one clock period for operation in FULLON mode which bypasses the state machine decision block. Synchronization time accounts for up to one clock period of variation. See Figure 6.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol              | Characteristic                 | Min. | Тур. | Max.      | Unit | Notes      |

|---------------------|--------------------------------|------|------|-----------|------|------------|

| Gate drive (conti   | nued)                          |      |      |           |      |            |

| t <sub>D_DIFF</sub> | Same Phase Command Delay Match | -20  | 0.0  | +20       | ns   | (43)       |

| t <sub>DUR</sub>    | Thermal Filter Duration        | 8.0  | _    | 30        | μs   | (44)       |

| t <sub>DC</sub>     | Duty Cycle                     | 0.0  | _    | 96        | %    | (45), (46) |

| t <sub>DC</sub>     | 100% Duty Cycle Duration       | _    | _    | Unlimited | S    | (45), (46) |

| t <sub>MAX</sub>    | Maximum Programmable Deadtime  | 10.2 | 15   | 19.6      | μs   | (47)       |

| Overcurrent com     | parator                        |      |      |           |      |            |

#### toc **Overcurrent Protection Filter Time** 0.9 \_ 3.5 μs Rise Time (OC OUT) • 10% - 90% 10 240 t<sub>ROC</sub> ns • $C_1 = 100 \, pF$ Fall Time (OC OUT) • 90% - 10% 10 200 ns t<sub>FOC</sub> • C<sub>L</sub> = 100 pF

#### Desaturation detector and phase comparator

| t <sub>R</sub><br>t <sub>F</sub> | $\begin{array}{l} \mbox{Phase Comparator Propagation Delay Time to 50\% of V_{DD};} \\ \mbox{C}_L \leq 100 \mbox{ pF} \\ \mbox{ \bullet Rising Edge Delay} \\ \mbox{ \bullet Falling Edge Delay} \end{array}$ |     | -   | 200<br>350 | ns |      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------|----|------|

| t <sub>MATCH</sub>               | Phase Comparator Match (Prop Delay Mismatch of Three Phases)<br>• $C_L$ = 100 pF                                                                                                                              | -   | -   | 100        | ns | (45) |

| t <sub>BLANK</sub>               | Desaturation and Phase Error Blanking Time                                                                                                                                                                    | 4.7 | 7.1 | 9.1        | μs | (48) |

| t <sub>FILT</sub>                | Desaturation Filter Time (Filter Time is digital) <ul> <li>Fault Must be Present for This Time to Trigger</li> </ul>                                                                                          | 640 | 937 | 1231       | ns | (45) |

#### Current sense amplifier

| <sup>t</sup> SETTLE | Output Settle Time to 99%<br>• RL = 1.0 k $\Omega$ , C <sub>L</sub> = 500 pF, 0.3 V < V <sub>O</sub> < 4.8 V, Gain = 5 to 15 | _ | 1.0 | 2.0 | μs | (45), (49) |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|----|------------|

|---------------------|------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|----|------------|

Notes

43. The maximum separation or overlap of the High and Low-side gate drives, due to propagation delays when commanding one ON and the other OFF simultaneously, is guaranteed by design.

44. The output of the overtemperature comparator goes through a digital filter before generating a warning or interrupt.

45. This parameter is guaranteed by design, not production tested.

46. As duty cycle approaches the limit of 100% or 0% there is a maximum and minimum which is not achievable due to deadtime, propagation delays, switching times and charge time of the bootstrap capacitor (for the High-side FET). 0% is available by definition (FET always OFF) and unlimited ON (100%) is possible as long as gate charge maintenance current is within the trickle charge pump capacity.

47. A Minimum Deadtime of 0.0 can be set via an SPI command. When Deadtime is set via a DEADTIME command, a minimum of 1 clock cycle duration and a maximum of 255 clock cycles is set using the internal time base clock as a reference. Commands exceeding this value limits at this value.

48. Blanking time, t<sub>BLANK</sub>, is applied to all phases simultaneously when switching ON any output FET. This precludes false errors due to system noise during the switching event.

49. Without considering any offsets such as input offset voltage, internal mismatch and assuming no tolerance error in external resistors.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  40 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  135 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min.           | Тур. | Max. | Unit | Notes |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| Current sense a      | mplifier (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •              |      |      |      | 1     |

| t <sub>IS_RISE</sub> | Output Rise Time to 90%<br>• RL = 1.0 kΩ, $C_L$ = 500 pF, 0.3 V < V <sub>O</sub> < 4.8 V, Gain = 5.0 to 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -              | _    | 1.0  | μs   | (51)  |

| t <sub>IS_FALL</sub> | Output Fall Time to 10%<br>• RL = 1.0 kΩ, C <sub>L</sub> = 500 pF, 0.3 V < V <sub>O</sub> < 4.8 V, Gain = 5.0 to 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -              | _    | 1.0  | μs   | (51)  |