Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

\*scale Semiconductor

Technical Data

Document Number: MC34702

Rev 7.0, 8/2007

ARCHIVE INFORMATION

# 3.0A Switch-Mode Power Supply with Linear Regulator

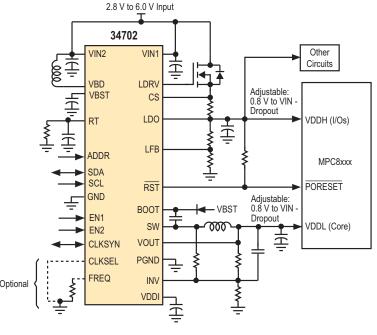

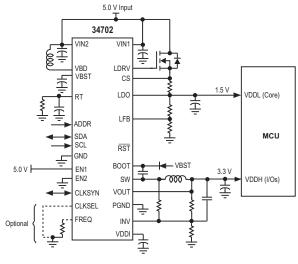

The 34702 provides the means to efficiently supply the Freescale Power QUICC™ I, II, and other families of Freescale microprocessors and DSPs. The 34702 incorporates a high performance switching regulator, providing the direct supply for the microprocessor's core, and a low dropout (LDO) linear regulator control circuit providing the microprocessor I/O and bus voltage.

The switching regulator is a high efficiency synchronous buck regulator with integrated N-channel power MOSFETs to provide protection features and to allow space-efficient, compact design.

The 34702 incorporates many advanced features; e.g., precisely maintained up/down power sequencing, ensuring the proper operation and protection of the CPU and power system.

### **Features**

- · Operating voltage from 2.8V to 6.0V

- · High-accuracy output voltages

- Fast transient response

- Switcher output current up to 3.0A

- Under-voltage lockout and over-current protection

- · Enable inputs and programmable watchdog timer

- Voltage margining via I<sup>2</sup>C<sup>™</sup> bus

- Reset with programmable power-ON delay

- · Pb-free packaging designated by suffix code EW

I<sup>2</sup>C is a trademark of Philips Corporation.

### 34702

### POWER SUPPLY

| ORDERING INFORMATION |                                        |          |  |  |

|----------------------|----------------------------------------|----------|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |  |

| MCZ34702EW/R2        | -40 to 85°C                            | 32 SOICW |  |  |

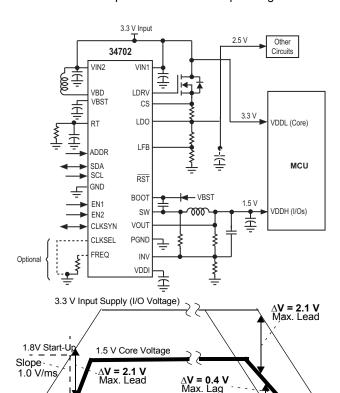

Figure 1. 34702 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

# NP

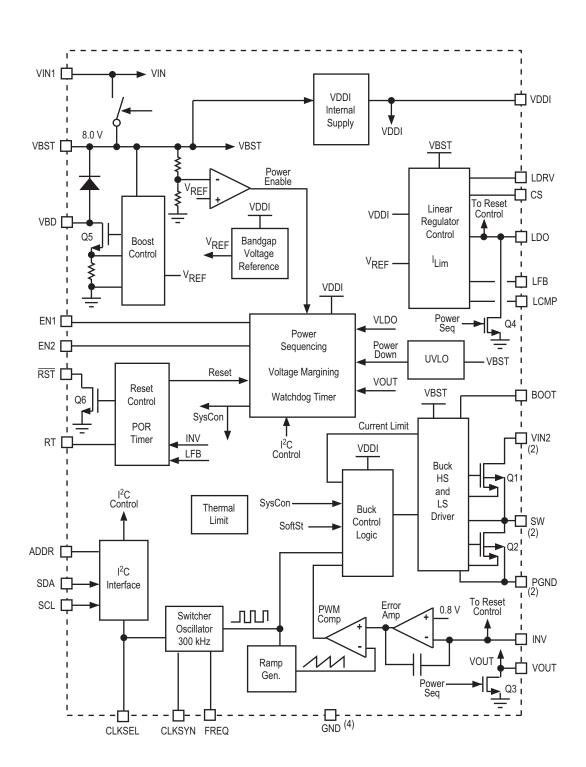

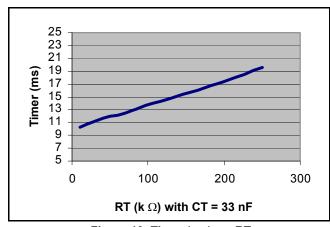

### **INTERNAL BLOCK DIAGRAM**

Figure 2. 34702 Simplified Internal Block Diagram

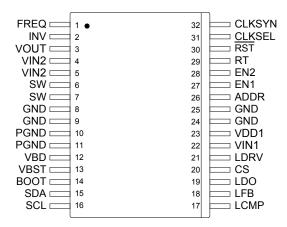

### **PIN CONNECTIONS**

Figure 3. Pin Connections

### Table 1. Pin Function Description

A functional description of each pin can be found in the Functional Pin Description section beginning on page 16.

| Pin            | Pin Name | Formal Name          | Definition                                                                                                                                                                                                                                                                        |

|----------------|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | FREQ     | Oscillator Frequency | This switcher frequency selection pin can be adjusted by connecting external resistor RF to the FREQ pin. The default switching frequency (FREQ pin left open or tied to VDDI) is set to 300kHz.                                                                                  |

| 2              | INV      | Inverting Input      | Buck controller error amplifier inverting input.                                                                                                                                                                                                                                  |

| 3              | VOUT     | Output Voltage       | Output voltage of the buck converter. Input pin of the switching regulator power sequence control circuit.                                                                                                                                                                        |

| 4, 5           | VIN2     | Input Voltage 2      | Buck regulator power input. Drain of the high side power MOSFET.                                                                                                                                                                                                                  |

| 6, 7           | SW       | Switch               | Buck regulator switching node. This pin is connected to the inductor.                                                                                                                                                                                                             |

| 8, 9<br>24, 25 | GND      | Ground               | Analog ground of the IC, thermal heatsinking.                                                                                                                                                                                                                                     |

| 10, 11         | PGND     | Power Ground         | Buck regulator power ground.                                                                                                                                                                                                                                                      |

| 12             | VBD      | Boost Drain          | Drain of the internal boost regulator power MOSFET.                                                                                                                                                                                                                               |

| 13             | VBST     | Boost Voltage        | Internal boost regulator output voltage. The internal boost regulator provides a 20mA output current to supply the drive circuits for the integrated power MOSFETs and the external N-channel power MOSFET of the linear regulator. The voltage at the VBST pin is 7.75V nominal. |

| 14             | воот     | Bootstrap            | Bootstrap capacitor input.                                                                                                                                                                                                                                                        |

| 15             | SDA      | Serial Data          | I <sup>2</sup> C bus pin. Serial data.                                                                                                                                                                                                                                            |

| 16             | SCL      | Serial Clock         | I <sup>2</sup> C bus pin. Serial clock.                                                                                                                                                                                                                                           |

| 17             | LCMP     | Linear Compensation  | Linear regulator compensation pin.                                                                                                                                                                                                                                                |

| 18             | LFB      | Linear Feedback      | Linear regulator feedback pin.                                                                                                                                                                                                                                                    |

| 19             | LDO      | Linear Regulator     | Input pin of the linear regulator power sequence control circuit.                                                                                                                                                                                                                 |

### Table 1. Pin Function Description (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 16.

| Pin | Pin Name | Formal Name                  | Definition                                                                                                                                                                                                                                                                                                  |

|-----|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | cs       | Current Sense                | Current sense pin of the LDO. Over-current protection of the linear regulator external power MOSFET. The voltage drop over the LDO current sense resistor RS is sensed between the CS and LDO pins. The LDO current limit can be adjusted by selecting the proper value of the current sensing resistor RS. |

| 21  | LDRV     | Linear Drive                 | LDO gate drive of the external pass N-channel MOSFET.                                                                                                                                                                                                                                                       |

| 22  | VIN1     | Input Voltage 1              | The input supply pin for the integrated circuit. The internal circuits of the IC are supplied through this pin.                                                                                                                                                                                             |

| 23  | VDDI     | Power Supply                 | Internal supply voltage. A ceramic low ESR 1uF 6V X5R or X7R capacitor is recommended.                                                                                                                                                                                                                      |

| 26  | ADDR     | Address                      | $I^2C$ address selection. This pin can either be left open, tied to VDDI, or grounded through a $10k\Omega$ resistor.                                                                                                                                                                                       |

| 27  | EN1      | Enable 1                     | Enable 1 Input. The combination of the logic state of the Enable 1 and Enable 2 inputs determines operation mode and type of power sequencing of the IC.                                                                                                                                                    |

| 28  | EN2      | Enable 2                     | Enable 2 Input. The combination of the logic state of the Enable 1 and Enable 2 inputs determines operation mode and type of power sequencing of the IC.                                                                                                                                                    |

| 29  | RT       | Reset Timer                  | This pin allows programming of the Power-ON Reset delay by means of an external RC network.                                                                                                                                                                                                                 |

| 30  | RST      | Reset Output<br>(Active LOW) | The reset control circuit monitors both the switching regulator and the LDO feedback voltages. It is an open drain output and has to be pulled up to some supply voltage (e.g., the output of the LDO) by an external resistor.                                                                             |

| 31  | CLKSEL   | Clock Selection              | This pin sets the CLKSYN pin as either an oscillator output or a synchronization input pin. The CLKSEL pin is also used for the I <sup>2</sup> C address selection.                                                                                                                                         |

| 32  | CLKSYN   | Clock Synchronization        | Oscillator output/synchronization input pin.                                                                                                                                                                                                                                                                |

## 34702

### **ELECTRICAL CHARACTERISTICS**

### **MAXIMUM RATINGS**

### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                        | Symbol                | Value       | Unit |

|---------------------------------------------------------------|-----------------------|-------------|------|

| ELECTRICAL RATINGS                                            |                       | -           |      |

| Supply Voltage                                                | $V_{IN1}, V_{IN2}$    | -0.3 to 7.0 | V    |

| Switching Node Voltage                                        | V <sub>SW</sub>       | -1.0 to 7.0 | V    |

| Buck Regulator Bootstrap Input Voltage (BOOT - SW)            | V <sub>IN(BOOT)</sub> | -0.3 to 8.5 | V    |

| Boost Regulator Output Voltage                                | V <sub>BST</sub>      | -0.3 to 8.5 | V    |

| Boost Regulator Drain Voltage                                 | V <sub>BD</sub>       | -0.3 to 9.5 | V    |

| RST Drain Voltage                                             | V <sub>RST</sub>      | -0.3 to 7.0 | V    |

| Enable Pin Voltage at EN1, EN2                                | V <sub>EN</sub>       | -0.3 to 7.0 | V    |

| Logic Pin Voltage at SDA, SCL                                 | V <sub>LOG</sub>      | -0.3 to 7.0 | V    |

| Analog Pin Voltage                                            |                       |             | V    |

| LDO, VOUT, RST                                                | $V_{OUT}$             | -0.3 to 7.0 |      |

| LDRV, LCMP, CS                                                | $V_{LIN}$             | -0.3 to 8.5 |      |

| Pin Voltage at CLKSEL, ADDR, RT, FREQ, VDDI, CLKSYN, INV, LFB | V <sub>LOGIC</sub>    | -0.3 to 3.6 | V    |

| ESD Voltage <sup>(1)</sup>                                    |                       |             | V    |

| Human Body Model                                              | $V_{ESD}$             | ±2000       |      |

| Machine Model                                                 | 202                   | ±200        |      |

### Notes

**ARCHIVE INFORMATION**

1. ESD1 testing is performed in accordance with the Human Body Model (CZAP=100pF, RZAP=1500Ω), ESD2 testing is performed in accordance with the Machine Model (CZAP=2000pF, RZAP=0Ω), and the Charge Device Model.

### Table 2. Maximum Ratings (continued)

Rating

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

**Symbol**

Value

Unit

|                                                                               |                   | IL.        |      |

|-------------------------------------------------------------------------------|-------------------|------------|------|

| THERMAL RATINGS                                                               |                   |            |      |

| Storage Temperature                                                           | T <sub>STG</sub>  | -65 to 150 | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(2)</sup> , <sup>(3)</sup> | T <sub>PPRT</sub> | Note 3     | °C   |

| Maximum Junction Temperature                                                  | T <sub>JMAX</sub> | 125        | °C   |

| Thermal Resistance                                                            | $R_{	hetaJA}$     |            | °C/W |

| Junction to Ambient (Single Layer) <sup>(4)</sup> , <sup>(5)</sup>            |                   | 70         |      |

| Junction to Ambient (Four Layers) <sup>(4)</sup> , <sup>(5)</sup>             |                   | 55         |      |

| Thermal Resistance, Junction to Base <sup>(6)</sup>                           | $R_{	heta JB}$    | 18         | °C/W |

| Operational Package Temperature (Ambient Temperature)                         | T <sub>A</sub>    | -40 to 85  | °C   |

### Notes

- 2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow

Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes

and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics..

- 4. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board and board thermal resistance.

- 5. Per JEDEC JESD51-6 with the board horizontal

- Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

### STATIC ELECTRICAL CHARACTERISTICS

### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figure 33</u>), unless otherwise noted.

| Characteristic                                                                                           | Symbol                    | Min   | Тур   | Max   | Unit |

|----------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------|------|

| GENERAL                                                                                                  |                           |       |       | 1     |      |

| Operating Voltage Range (VIN1, VIN2)                                                                     | V <sub>IN</sub>           | 2.8   | -     | 6.0   | V    |

| Start-up Voltage Threshold (Boost Switching)                                                             | V <sub>ST</sub>           | -     | 1.6   | 1.8   | V    |

| VBST Under-voltage Lockout (VBST rising)                                                                 | V <sub>BST_UVLO</sub>     | 5.5   | _     | 6.5   | V    |

| VBST Under-voltage Lockout Hysterisis                                                                    | V <sub>BST_UVLO_HYS</sub> | 0.5   | -     | 1.5   | V    |

| Input DC Supply Current (Normal Operation Mode, Enabled), Unloaded Outputs                               | IIN                       | -     | 60    | -     | mA   |

| VIN1 Pin Input Supply Current (EN1 = EN2 = 0)                                                            | I <sub>IN1</sub>          | _     | 10    | _     | mA   |

| VIN2 Pin Input Leakage Current (EN1 = EN2 = 0)                                                           | I <sub>IN2</sub>          | _     | 100   | _     | μА   |

| VDDI Internal Supply Voltage                                                                             | V <sub>DDI</sub>          | 2.9   | _     | 3.3   | V    |

| VDDI Maximum Output Current (Externally Loaded)                                                          | I <sub>DDI</sub>          | _     | _     | -10   | mA   |

| BUCK CONVERTER                                                                                           |                           |       |       |       | •    |

| Buck Converter Feedback Voltage <sup>(7), (8)</sup> IVOUT = 15mA to 3.0A. Includes Load Regulation Error | V <sub>INV</sub>          | 0.784 | 0.800 | 0.816 | V    |

| Buck Converter Voltage Margining Step Size                                                               | V <sub>MVO</sub>          | _     | 1.0   | _     | %    |

| Buck Converter Voltage Margining Highest Positive Value                                                  | V <sub>MP</sub>           | 5.9   | 7.0   | 7.9   | %    |

| Buck Converter Voltage Margining Lowest Negative Value                                                   | V <sub>MN</sub>           | -7.9  | 7.0   | -5.9  | %    |

| Buck Converter Line Regulation <sup>(7), (8)</sup> VIN1 = VIN2 = 2.8V to 6.0V, IVOUT = 15mA to 3.0A      | REG <sub>LNVO</sub>       | -1.0  | _     | 1.0   | %    |

| Buck Converter Load Regulation <sup>(7), (8)</sup>                                                       | REG <sub>LDVO</sub>       |       |       |       | %    |

### Notes

- 7. Design information only. This parameter is not production tested.

- 8. VOUT refers to load current on output switcher.

VIN1 = VIN2 = 2.8V to 6.0V, IVOUT = 15mA to 3.0A

**VOUT Input Leakage Current**

**INV Input Leakage Current**

**VOUT = 5.25V**

INV = 0.8V

1.0

1.0

mΑ

μΑ

-1.0

-1.0

3.5

$I_{VOUTLK}$

$INV_{LEAK}$

**VE INFORMATION**

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figure 33</u>), unless otherwise noted.

| Characteristic                                               | Symbol              | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------|---------------------|------|------|------|------|

| BUCK CONVERTER (CONTINUED)                                   |                     |      |      |      |      |

| High Side Power MOSFET Q1 RDS(ON) <sup>(9),(10)</sup>        | R <sub>DS(ON)</sub> |      |      |      | mΩ   |

| ID = 500mA, T <sub>A</sub> = 25°C, VBST = 8.0V               |                     | _    | 60   | _    |      |

| Low Side Power MOSFET Q2 RDS(ON) <sup>(9),(10)</sup>         | R <sub>DS(ON)</sub> |      |      |      | mΩ   |

| ID = 500mA, T <sub>A</sub> = 25°C, VBST = 8.0V               |                     | _    | 65   | _    |      |

| Buck Converter Peak Current Limit (High Level)               | I <sub>LIMH</sub>   | -7.0 | -4.7 | -4.0 | Α    |

| VOUT Pull-down MOSFET Q3 Current Limit                       | I <sub>M3_LIM</sub> |      |      |      | Α    |

| T <sub>A</sub> = 25°C, VBST = 8.0V                           |                     | 0.75 | -    | 2.0  |      |

| VOUT Pull-down MOSFET Q3 R <sub>DS(ON)</sub> <sup>(10)</sup> | R <sub>DS(ON)</sub> |      |      |      | Ω    |

| ID = 1.0A, VBST = 8.0V                                       |                     | _    | _    | 1.9  |      |

| Thermal Shutdown (VOUT Pull-down MOSFET Q3) <sup>(9)</sup>   | T <sub>SD</sub>     | 150  | 170  | 190  | °C   |

| Thermal Shutdown Hysteresis (9)                              | T <sub>SDHYS</sub>  | _    | 10   | 1    | °C   |

### Notes

- 9. Design information only. This parameter is not production tested.

- 10. ID refers to the MOSFET drain current

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figure 33</u>), unless otherwise noted.

| Characteristic                                                                | Symbol              | Min            | Тур  | Max | Unit |

|-------------------------------------------------------------------------------|---------------------|----------------|------|-----|------|

| ERROR AMPLIFIER (BUCK CONVERTER)                                              | 1                   |                |      | l   |      |

| Input Impedance <sup>(11)</sup>                                               | R <sub>OUT</sub>    | _              | 150  | _   | Ω    |

| Output Impedance <sup>(11)</sup>                                              | AVOL                | -              | 80   | _   | dB   |

| DC Open Loop Gain <sup>(11)</sup>                                             | GBW                 | -              | 35   | -   | MHz  |

| Gain Bandwidth Product <sup>(11)</sup>                                        | SR                  | -              | 200  | _   | V/μs |

| Slew Rate <sup>(11)</sup>                                                     | V <sub>EA_OH</sub>  | _              | 2.0  | _   | V    |

| Output Voltage – High Level  VIN1 > 3.3V, IOEA = -1.0mA <sup>(11), (12)</sup> | V <sub>EA_OL</sub>  | _              | 0.4  | -   | V    |

| Output Voltage – Low Level IOEA = -1.0 mA <sup>(11)</sup> , (12)              | V <sub>SCRAMP</sub> | _              | 0.5  | -   | V    |

| Oscillator Ramp <sup>(11)</sup>                                               | V <sub>SCRAMP</sub> | -              | 0.5  | _   | V    |

| OSCILLATOR                                                                    |                     | •              |      |     | •    |

| CLKSYN Pin (open) Low Level Output Voltage IOL = +1.0mA <sup>(13)</sup>       | V <sub>OSC_OL</sub> | _              | _    | 0.4 | V    |

| CLKSYN Pin (open) High Level Output Voltage IOH = -1.0mA <sup>(14)</sup>      | V <sub>OSC_OH</sub> | VDDI<br>-0.4 V | _    | -   | V    |

| CLKSYN Pin (grounded) Input Voltage Threshold                                 | V <sub>OSC_IH</sub> | 1.2            | -    | 2.0 | V    |

| CLKSYN Pin Pullup Resistance                                                  | RPU                 | 60             | -    | 240 | kΩ   |

| Frequency Adjusting Reference Voltage                                         | $V_{FREQ}$          | _              | 1.26 | _   | V    |

| BOOST REGULATOR                                                               | <b>'</b>            | L              | ı    | L   |      |

| Regulator Output Voltage                           | V <sub>BST</sub>    |     |     |      | V  |

|----------------------------------------------------|---------------------|-----|-----|------|----|

| IBST = 20mA, VIN1 = VIN2 = 2.8V to 6.0V            |                     | 7.3 | 7.7 | 8.3  |    |

| Power MOSFET Q5 RDS(ON) <sup>(11)</sup>            | R <sub>DS(ON)</sub> |     |     |      | mΩ |

| IBD = 500mA, T <sub>A</sub> = 25°C                 |                     | -   | 650 | 1000 |    |

| Regulator Recommended Output Capacitor             | CBST                | -   | 10  | -    | μF |

| Regulator Recommended Output Capacitor Maximum ESR | ESRCBST             | _   | 100 | _    | mΩ |

- 11. Design information only. This parameter is not production tested.

- 12. IOEA Refers to Error Amplifier Output Current.

- 13. IOL Refers to IO Low Level Threshold Voltage Current

- 14. IOH Refers to IO High Level Threshold Voltage Current

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figure 33</u>), unless otherwise noted.

| Characteristic                                                                                                                              | Symbol                | Min   | Тур   | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------|-------|------|

| LINEAR REGULATOR (LDO)                                                                                                                      | •                     | •     | •     | 1     | 1    |

| LDO Feedback Voltage <sup>(16)</sup>                                                                                                        | $V_{LFB}$             |       |       |       | V    |

| VIN1 = VIN2 = 2.8V to 6.0V, ILDO = 10mA to 1000mA. Includes Load Regulation Error                                                           |                       | 0.784 | 0.800 | 0.816 |      |

| LDO Voltage Margining Step Size                                                                                                             | $V_{MLDO}$            | _     | 1.0   | _     | %    |

| LDO Voltage Margining Highest Positive Value                                                                                                | V <sub>MP</sub>       | 5.9   | 7.0   | 7.9   | %    |

| LDO Voltage Margining Lowest Negative Value                                                                                                 | V <sub>MN</sub>       | -7.9  | 7.0   | -5.9  | %    |

| LDO Line Regulation <sup>(16)</sup> VIN1 = VIN2 = 2.8V to 6.0V, ILDO = 1000mA                                                               | REG <sub>LNVLDO</sub> | -1.0  | _     | 1.0   | %    |

| LDO Load Regulation <sup>(16)</sup> ILDO = 10mA to 1000mA                                                                                   | REG <sub>LDVLDO</sub> | -1.0  | _     | 1.0   | %    |

| LDO Ripple Rejection, Dropout Voltage <sup>(16)</sup> VDO = 1.0V, VRIPPLE = +1.0V p-p  Sinusoidal, f = 300kHz, ILDO = 500mA <sup>(15)</sup> | V <sub>LDO_RR</sub>   | -     | 40    | -     | dB   |

| LDO Maximum Dropout Voltage (VIN - VLDO), using IRL2703 <sup>(16)</sup> VLDO = 2.5V, ILDO = 1000mA                                          | V <sub>DO</sub>       | _     | 50    | 75    | mV   |

| LDO Current Sense Comparator Threshold Voltage (VCS - VLDO)                                                                                 | V <sub>CSTH</sub>     | 35    | 50    | 65    | mV   |

| LDO Pin Input Current, VLDO = 5.25V                                                                                                         | I <sub>LDO</sub>      | 1.0   | 1.9   | 4.0   | mA   |

| LDO Feedback Input Current (LFB Pin), VLFB = 0.8V                                                                                           | I <sub>LFB</sub>      | -1.0  | _     | 1.0   | μА   |

| LDO Drive Output Current (LDRV Pin), VLDRV = 0V                                                                                             | I <sub>LDRV</sub>     | -5.0  | -3.3  | -2.0  | mA   |

| CS Pin Input Leakage Current<br>VCS = 5.25V                                                                                                 | I <sub>CSLK</sub>     | 50    | _     | 200   | μА   |

| LDO Pull-down MOSFET Q4 Current Limit  T <sub>A</sub> = 25°C, VBST = 8.0V (LDO Pin)                                                         | I <sub>M4_LIM</sub>   | 0.75  | -     | 2.0   | A    |

| LDO Pull-down MOSFET Q4 RDS(ON) ID = 1.0A, VBST = 8.0V                                                                                      | R <sub>DS(ON)</sub>   | _     | _     | 1.9   | Ω    |

| LDO Recommended Output Capacitance                                                                                                          | C <sub>LDO</sub>      | _     | 10    | _     | μF   |

| LDO Recommended Output Capacitor ESR                                                                                                        | E <sub>SRCLDO</sub>   | _     | 5.0   | _     | mΩ   |

| Thermal Shutdown (LDO Pull-down MOSFET Q4) <sup>(15)</sup>                                                                                  | T <sub>SD</sub>       | 150   | 170   | 190   | °C   |

| Thermal Shutdown Hysteresis <sup>(15)</sup>                                                                                                 | T <sub>SDHYS</sub>    | _     | 10    | _     | °C   |

### Notes

- 15. Design information only. This parameter is not production tested.

- 16. IDO refers to Load Current on External LDOFET IRL2703 is the Intersil MOSFET IRL2703

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figure 33</u>), unless otherwise noted.

| Characteristic                                                                           | Symbol               | Min  | Тур | Max  | Unit |

|------------------------------------------------------------------------------------------|----------------------|------|-----|------|------|

| CONTROL AND SUPERVISORY CIRCUITS                                                         |                      |      |     |      |      |

| Enable (EN1, EN2) Input Voltage Threshold                                                | V <sub>TH_EN</sub>   | 1.0  | 1.5 | 2.0  | V    |

| Enable (EN1, EN2) Pull-down Resistance                                                   | R <sub>PU</sub>      | 30   | 55  | 90   | kΩ   |

| RST Low-level Output Voltage, IOL = 5.0mA                                                | V <sub>OL</sub>      | _    | _   | 0.4  | V    |

| RST Leakage Current, OFF State, Pulled Up to 5.25V                                       | I <sub>LKG-RST</sub> | _    | -   | 10   | μА   |

| RST Under-voltage Threshold on VOUT (ΔVOUT/VOUT) <sup>(17)</sup>                         | V <sub>OUTITH</sub>  | -14  | _   | -0.5 | %    |

| RST Over-voltage Threshold on VOUT ( $\Delta$ VOUT/VOUT) <sup>(17)</sup>                 | V <sub>OUTITH</sub>  | 0.5  | -   | 14   | %    |

| RST Under-voltage Threshold on VLDO (ΔVLDO/VLDO) <sup>(17)</sup>                         | V <sub>LDOITH</sub>  | -12  | _   | -4.0 | %    |

| RST Over-voltage Threshold on VLDO (ΔVLDO/VLDO) <sup>(17)</sup>                          | V <sub>LDOITH</sub>  | 4.0  | _   | 12   | %    |

| RST Timer Voltage Threshold                                                              | V <sub>TH-RT</sub>   | 1.0  | 1.2 | 1.5  | V    |

| RST Timer Source Current (RT pin at 0.0V)                                                | I <sub>S-RT</sub>    | -17  | _   | -34  | mA   |

| RST Timer Leakage Current                                                                | I <sub>LKG-RT</sub>  | -1.0 | -   | 1.0  | μА   |

| $\overline{\text{RST}}$ Timer Saturation Voltage, Reset Timer Current = $300\mu\text{A}$ | V <sub>SAT-RT</sub>  | _    | 35  | 100  | mV   |

| Maximum Recommended Value of the Reset Timer Capacitor                                   | C <sub>t</sub>       | -    | -   | 47   | μF   |

| CLKSEL Threshold Voltage                                                                 | V <sub>THCLKS</sub>  | 1.2  | 1.6 | 2.0  | V    |

| CLKSEL Pull-up Resistance                                                                | R <sub>PU-CLKS</sub> | 60   | 120 | 240  | kΩ   |

| ADDR Threshold Voltage <sup>(17)</sup>                                                   | $V_{THADDR}$         | 1.2  | 1.6 | 2.0  | V    |

| ADDR Pull-up Resistance                                                                  | R <sub>PU-ADDR</sub> | 60   | 120 | 240  | kΩ   |

| Thermal Shutdown (IC sensor) <sup>(17)</sup>                                             | T <sub>LIM</sub>     | 150  | 170 | 190  | °C   |

| Thermal Shutdown Hysteresis <sup>(17)</sup>                                              | T <sub>LIMHYS</sub>  | _    | 10  | _    | °C   |

| SDA, SCL PINS I <sup>2</sup> C BUS (STANDARD)                                            | •                    | •    | •   | •    | •    |

| Input Threshold Voltage (Pin SCL), Rising Edge <sup>(17)</sup>                           | $V_{LTH}$            | 1.3  | -   | 1.7  | V    |

| Input Threshold Voltage (Pin SDA)                                                        | $V_{LTH}$            | 1.3  | -   | 1.7  | V    |

| SDA, SCL Input Current, Input Voltage = 5.25V (VIN1)                                     | II                   | _    | 1.0 | 10   | μА   |

| SDA Low-level Output Voltage, 3.0mA Sink Current                                         | V <sub>OL</sub>      | _    | -   | 0.4  | V    |

| SDA, SCL Capacitance <sup>(17)</sup>                                                     | C <sub>INPUT</sub>   | _    | 7.0 | 10   | pF   |

<sup>17.</sup> Design information only. This parameter is not production tested.

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

### Table 4. DYNAMIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figures 33</u>), unless otherwise noted.

| Characteristic                                                                                                                      | Symbol             | Min | Тур | Max | Unit   |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|--------|

| BUCK CONVERTER                                                                                                                      |                    |     |     |     |        |

| Duty Cycle Range (Normal Operation) <sup>(18)</sup>                                                                                 | D                  | 0   | _   | 95  | %      |

| Switching Node SW Rise Time <sup>(18)</sup> VIN = 5.0V, ILOAD = 1.0A                                                                | t <sub>RISE</sub>  | _   | 7.0 | _   | ns     |

| Switching Node SW Fall Time <sup>(18)</sup> VIN = 5.0V, ILOAD = 1.0A                                                                | t <sub>FALL</sub>  | _   | 17  | _   | ns     |

| Maximum Deadtime <sup>(18)</sup>                                                                                                    | t <sub>D</sub>     | _   | 35  | _   | ns     |

| Buck Control Loop Propagation Delay <sup>(18)</sup> VINV < 0.8V to VSW > 90% of High Level or VINV > 0.8V to VSW < 10% of Low Level | t <sub>PD</sub>    | _   | 50  | -   | ns     |

| Soft Start Duration (Power Sequencing Disabled, EN1 = 1, EN2 = 1) <sup>(18)</sup>                                                   | t <sub>SS</sub>    | 200 | 350 | 800 | μS     |

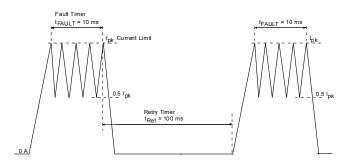

| Fault Condition Time-Out (18)                                                                                                       | t <sub>FAULT</sub> | -   | 10  | _   | ms     |

| Retry Timer Cycle <sup>(18)</sup>                                                                                                   | t <sub>RET</sub>   | _   | 100 | -   | ms     |

| OSCILLATOR                                                                                                                          |                    |     |     |     |        |

| 0                                                                                                                                   |                    |     |     |     | 1.1.1- |

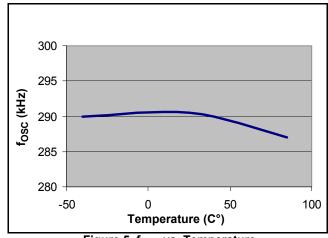

| Oscillator Center Frequency <sup>(20)</sup>                              | f <sub>OSC</sub>  |     |     |     | kHz |

|--------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|

| $RF = 11.3k\Omega$                                                       |                   | 270 | 300 | 330 |     |

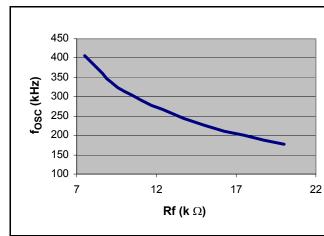

| Oscillator Frequency Range                                               | fosc              | 200 |     | 400 | kHz |

| Oscillator Frequency Adjusting Resistor Range                            | R <sub>FREQ</sub> | 7.0 | _   | 22  | kΩ  |

| Oscillator Frequency Adjustment <sup>(19), (20)</sup>                    | fosc              |     |     |     | kHz |

| $RF = 7.0k\Omega$                                                        |                   | 400 | _   | _   |     |

| Oscillator Frequency Adjustment <sup>(19), (20)</sup>                    | f <sub>OSC</sub>  |     |     |     | kHz |

| $RF = 22k\Omega$                                                         |                   | _   | _   | 200 |     |

| Oscillator Default Frequency (Switching Frequency), FREQ Pin Open        | fosc              | _   | 300 | _   | kHz |

| Oscillator Output Signal Duty Cycle (Square Wave, 180° Out-of-Phase with | D <sub>OSC</sub>  |     |     |     | %   |

| the Internal Suitable Oscillator)                                        |                   | 40  | 50  | 60  |     |

| Synchronization Pulse Minimum Duration <sup>(18)</sup>                   | t <sub>SYNC</sub> | 1.0 | _   | _   | μS  |

- 18. Design information only. This parameter is not production tested.

- 19. see Figure 4 for more details

- 20. RF = RFREQ resistor connected to the FREQ pin.

### Table 4. DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C unless otherwise noted. Input voltages VIN1 = VIN2 = 3.3V using the typical application circuit (see <u>Figures 33</u>), unless otherwise noted.

|                                                                                                                |                        | •   |     |     |      |

|----------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| Characteristic                                                                                                 | Symbol                 | Min | Тур | Max | Unit |

| BOOST REGULATOR                                                                                                |                        |     |     |     |      |

| Boost Regulator MOSFET Maximum ON Time <sup>(21)</sup>                                                         | t <sub>ON</sub>        | _   | 24  | _   | μS   |

| Boost Regulator Control Loop Propagation Delay <sup>(21)</sup>                                                 | t <sub>BST_PD</sub>    | -   | 50  | -   | ns   |

| Boost Switching Node VBD Rise Time <sup>(21)</sup> IBST = 20mA                                                 | t <sub>B_RISE</sub>    | _   | 5.0 |     | ns   |

| Boost Switching Node VBD Fall Time <sup>(21)</sup> IBST = 20mA                                                 | t <sub>B_FALL</sub>    | -   | 3.0 |     | ns   |

| LINEAR REGULATOR (LDO)                                                                                         |                        | •   |     |     | •    |

| Fault Condition Time-Out                                                                                       | t <sub>FAULT</sub>     | 8.0 | 10  | 12  | ms   |

| Retry Timer Cycle                                                                                              | t <sub>RET</sub>       | 80  | 100 | 120 | ms   |

| Reset Monitor (RST)                                                                                            |                        |     |     |     | •    |

| Monitoring LFB Pin Delay                                                                                       | t <sub>D_RST_LFB</sub> | 12  | -   | 28  | μS   |

| Monitoring INV Pin Delay                                                                                       | t <sub>D_RST_INV</sub> | 12  | -   | 28  | μS   |

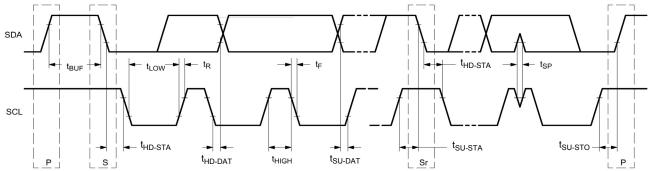

| SCA, SCL PIN, I <sup>2</sup> C BUS (STANDARD)                                                                  |                        |     |     |     | •    |

| SCL Clock Frequency <sup>(21)</sup>                                                                            | f <sub>SCL</sub>       | _   | _   | 100 | kHz  |

| Bus Free Time Between a STOP and a START Condition <sup>(21)</sup>                                             | t <sub>BUF</sub>       | 4.7 | -   | -   | μS   |

| Hold Time (Repeated) START Condition (After this period, the first clock pulse is generated) <sup>(21)</sup>   | t <sub>HD-STA</sub>    | 4.0 | _   | _   | μS   |

| Low Period of the SCL Clock <sup>(21)</sup>                                                                    | t <sub>LOW</sub>       | 4.7 | -   | _   | μS   |

| High Period of the SCL Clock <sup>(21)</sup>                                                                   | t <sub>HIGH</sub>      | 4.0 | _   | _   | μS   |

| SDA Fall Time from VIH_MAX to VIL_MIN, Bus Capacitance 10pF to 400pF, 3.0mA Sink Current <sup>(21), (23)</sup> | t <sub>F</sub>         | _   | _   | 250 | ns   |

| Setup Time for a Repeated START Condition <sup>(21)</sup>                                                      | t <sub>SU-STA</sub>    | 4.7 | -   | -   | μS   |

| Data Hold Time for I <sup>2</sup> C Bus Devices <sup>(21)</sup> , <sup>(22)</sup>                              | t <sub>HD-DAT</sub>    | 0.0 | _   | _   | μS   |

| Data Setup Time <sup>(21)</sup>                                                                                | t <sub>SU-DA</sub> T   | 250 | _   | _   | ns   |

| Setup Time for STOP Condition <sup>(21)</sup>                                                                  | t <sub>SU-STO</sub>    | 4.0 | _   | _   | μS   |

| Capacitive Load for Each Bus Line <sup>(21)</sup>                                                              | СВ                     | -   | -   | 400 | pF   |

|                                                                                                                |                        |     |     | 1   |      |

- 21. Design information only. This parameter is not production tested.

- 22. The device provides an internal hold time of at least 300ns for the SDA signal (refer to the VIH\_MIN of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 23. VIH = High level voltage on I<sup>2</sup>C bus and VIL = Low level voltage on I<sup>2</sup>C bus

### **TIMING DIAGRAM**

Note: Refer to the latest I<sup>2</sup>C bus specification for further details.

Figure 4. Definition of Time on the I<sup>2</sup>C Bus

### **ELECTRICAL PERFORMANCE CURVES**

Figure 5. f<sub>OSC</sub> vs. Temperature

Figure 6. f<sub>OSC</sub> vs. Rf

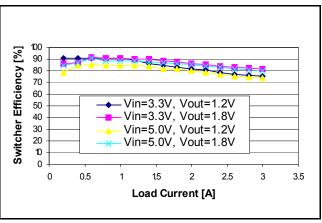

Figure 7. Switcher Efficiency vs. Load Current

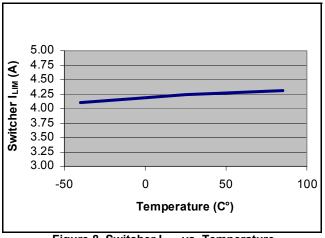

Figure 8. Switcher I<sub>LIM</sub> vs. Temperature

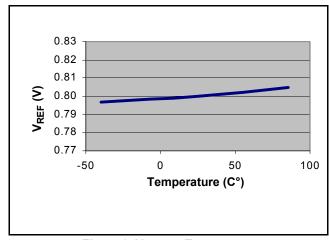

Figure 9. V<sub>REF</sub> vs. Temperature

Figure 10. Timer (ms) vs. RT

### **FUNCTIONAL DESCRIPTION**

### INTRODUCTION

The 34702 power supply integrated circuit provides the means to efficiently supply the Freescale Power QUICC and other families of Freescale microprocessors. It incorporates a high performance synchronous buck regulator, supplying the microprocessor's core, and a low dropout (LDO) linear regulator providing the microprocessor I/O and bus voltages.

This device incorporates many advanced features; e.g., precisely maintained up/down power sequencing, ensuring the proper operation and protection of the CPU and power system. At the same time, it provides high flexibility of configuration, allowing the maximum optimization of the power supply system.

### **FUNCTIONAL PIN DESCRIPTION**

### **OSCILLATOR FREQUENCY PIN (FREQ)**

This switcher frequency selection pin can be adjusted by connecting external resistor RF to the FREQ pin. The default switching frequency (FREQ pin left open or tied to VDDI) is set to 300kHz.

### **INVERTING INPUT PIN (INV)**

Buck Controller Error Amplifier inverting input.

### **OUTPUT VOLTAGE PIN (VOUT)**

Output voltage of the buck converter. Input pin of the switching regulator power sequence control circuit.

### **INPUT VOLTAGE 2 PINS (VIN2)**

Buck regulator power input. Drain of the high side power MOSFET.

### **SWITCH PINS (SW)**

Buck regulator switching node. This pin is connected to the inductor.

### **GROUND PINS (GND)**

Analog ground of the IC, thermal heatsinking.

### **POWER GROUND PINS (PGND)**

Buck regulator power ground.

### **BOOST DRAIN PIN (VBD)**

Drain of the internal boost regulator power MOSFET.

### **BOOST VOLTAGE PIN (VBST)**

Internal boost regulator output voltage. The internal boost regulator provides a 20mA output current to supply the drive circuits for the integrated power MOSFETs and the external N-channel power MOSFET of the linear regulator. The voltage at the VBST pin is 7.75V nominal.

### **BOOTSTRAP PIN (BOOT)**

Bootstrap capacitor input.

### **SERIAL DATA PIN (SDA)**

I<sup>2</sup>C bus pin. Serial data.

### SERIAL CLOCK PIN (SCL)

I<sup>2</sup>C bus pin. Serial clock.

### **LINEAR COMPENSATION PIN (LCMP)**

Linear regulator compensation pin.

### LINEAR FEEDBACK PIN (LFB)

Linear regulator feedback pin.

### **LINEAR REGULATOR PIN (LDO)**

Input pin of the linear regulator power sequence control circuit.

### **CURRENT SENSE PIN (CS)**

Current sense pin of the LDO. Over-current protection of the linear regulator external power MOSFET. The voltage drop over the LDO current sense resistor RS is sensed between the CS and LDO pins. The LDO current limit can be adjusted by selecting the proper value of the current sensing resistor RS.

### **LINEAR DRIVE PIN (LDRV)**

LDO gate drive of the external pass N-channel MOSFET.

### **INPUT VOLTAGE 1 PIN (VIN1)**

The input supply pin for the integrated circuit. The internal circuits of the IC are supplied through this pin.

ARCHIVE INFORMATIO

### **POWER SUPPLY PIN (VDDI)**

Internal supply voltage. A ceramic low ESR 1uF 6V X5R or X7R capacitor is recommended.

### **ADDRESS PIN (ADDR)**

The ADDR pin is used to set the address of the device when used in an I<sup>2</sup>C communication. This pin can either be tied to VDDI or grounded through a  $10k\Omega$  resistor. Refer to I<sup>2</sup>C Bus Operation on page 26 for more information on this pin.

### **ENABLE 1 AND 2 PINS (EN1 AND EN2)**

These two pins permit positive logic control of the Enable function and selection of the Power Sequencing Mode concurrently. <u>Table 5</u> depicts the EN1 and EN2 function and Power Sequencing Mode selection.

Both EN1 and EN2 pins have internal pull-down resistors and both can withstand a short circuit to the supply voltage, 6.0V.

Table 5. Operating Mode Selection

| EN1 | EN2 | Operating Mode            |  |

|-----|-----|---------------------------|--|

| 0   | 0   | Regulators Disabled       |  |

| 0   | 1   | Standard Power Sequencing |  |

| 1   | 0   | Inverted Power Sequencing |  |

| 1   | 1   | No Power Sequencing,      |  |

|     |     | Regulators Enabled        |  |

### **RESET TIMER PIN (RT)**

The Reset Timer power-up delay (RT) pin is used to set the delay between the time when the LDO and switcher outputs are active and stable and the  $\overline{\text{RST}}$  output is released. An external resistor and capacitor are used to program the timer. The power-up delay can be obtained by using the following formula:

$$t_D = 10ms + R_tC_t$$

Where  $R_t$  is the Reset Timer programming resistor and  $C_t$  is the Reset Timer programming capacitor, both connected in parallel from RT to ground.

Note Observe the maximum  $C_t$  value and expect reduced accuracy if  $R_t$  is less than  $10k\Omega.$

### RESET OUTPUT PIN (RST)

The reset control circuit monitors both the switching regulator and the LDO feedback voltages. It is an open drain output and has to be pulled up to some supply voltage (e.g., the output of the LDO) by an external resistor.

The reset control circuit supervises both output voltages—the linear regulator output VLDO and the switching regulator output VOUT. When either of these two regulators is out of regulation (high or low), the  $\overline{RST}$  pin is pulled low. There is a  $20\mu s$  delay filter preventing erroneous resets. During power-up sequencing,  $\overline{RST}$  is held low until the Reset Timer times out.

### **CLOCK SELECTION PIN (CLKSEL)**

This pin sets the CLKSYN pin as either an oscillator output or a synchronization input pin. The CLKSEL pin is also used for the I<sup>2</sup>C address selection.

### **CLOCK SYNCHRONIZATION PIN (CLKSYN)**

Oscillator output/synchronization input pin.

### FUNCTIONAL INTERNAL BLOCK DESCRIPTION

### INTRODUCTION

The 34702 incorporates a high-performance synchronous buck regulator, supplying the microprocessor's core, and a low dropout (LDO) linear regulator providing the microprocessor I/O and bus voltages. This device

incorporates many advanced features; e.g., precisely maintained up/down power sequencing, ensuring the proper operation and protection of the CPU and power system.

Figure 11. 34702 Functional Internal Block Diagram

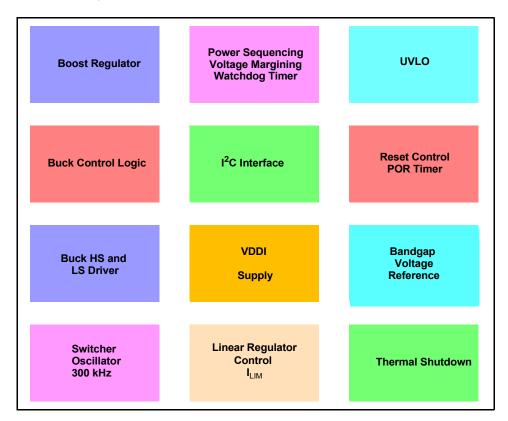

### **BOOST REGULATOR**

A boost regulator provides a high voltage necessary to properly drive the buck regulator power MOSFETs, especially during the low input voltage condition. The LDO regulator external N-channel MOSFET gate is also powered from the boost regulator. In order to properly enhance the high side MOSFETs when only a +3.3V supply rail powers the integrated circuit, the boost regulator provides an output voltage of 7.75V nominal value.

The 34702 boost regulator uses a simple hysteretic current control technique, which allows fast power-up and does not require any compensation. When the boost regulator main power switch (low side) is turned on, the current in the inductor starts to ramp up. After the inductor current reaches the upper current limit (nominally set at 1.0A), the low side switch is turned off and the current charges the output capacitor through the internal rectifier.

When the inductor current falls below the valley current limit value (nominally 600mA), the low side switch is turned on again, starting the next switching cycle. After the boost regulator output capacitor reaches approximately 6.0 volts, the peak and valley current limit levels are proportionally scaled down to approximately one fifth of their original values. When the boost regulator reaches its regulation limit (7.75V typical), the low side switch is turned off until the output voltage falls below the regulation limit again.

The higher current limit values in the beginning of the boost regulator start-up sequence allow fast power-up of the whole IC, while the normal operation with reduced current limit greatly reduces the switching noise and therefore improves the overall EMC performance. See <a href="Figure 12">Figure 12</a> for the boost regulator output voltage and inductor current waveforms (picture not to scale).

Figure 12. Boost Regulator Start-up (Not To Scale)

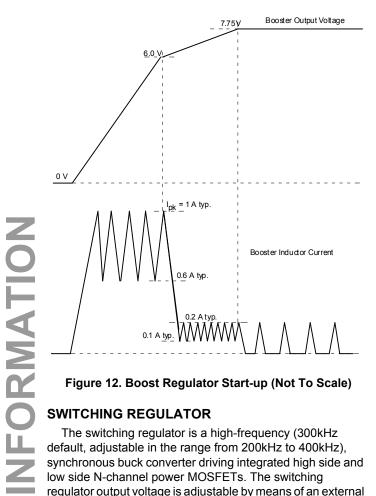

### **SWITCHING REGULATOR**

The switching regulator is a high-frequency (300kHz default, adjustable in the range from 200kHz to 400kHz), synchronous buck converter driving integrated high side and low side N-channel power MOSFETs. The switching regulator output voltage is adjustable by means of an external resistor divider to provide the required output voltage within ±2.0% accuracy, and is intended to directly power the core of the microprocessor. The buck controller uses a PWM voltage mode control topology with feed-forward to achieve excellent line and load regulation.

The 34702 integrated boost regulator provides a 7.75V rail which is used to properly bias the switcher's MOSFET. In addition, the boost structure has a very low start-up voltage (Typically 1.6V), hence ensuring very low input voltage functionality. A typical bootstrap technique is used to provide voltage necessary to properly enhance the high side MOSFET gate. When the regulator is supplied only from low input voltage (e.g., single +3.3V supply rail), the bootstrap capacitor is charged from the internal boost regulator output VBST through an external diode. This arrangement allows the 34702 to operate from very low input voltage and also comply with the power sequencing requirements of the supplied microcontroller.

Figure 13. Switching Regulator Current Limit (Not To Scale)

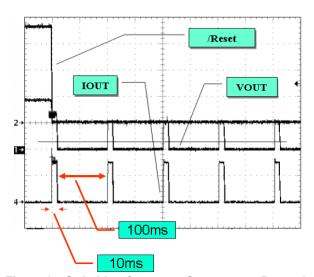

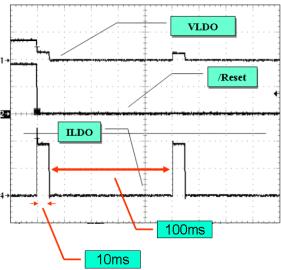

To avoid destruction of the supplied circuits, the switching regulator has a current limit with retry capability. When an over-current condition occurs and the switch current reaches the peak current limit value, the main (high side) switch is turned off until the inductor current decays to the valley value, which is one half of the peak current limit. If an over-current condition exists for 10ms, the buck regulator control circuit shuts the switcher OFF and the switcher retry timer starts to time out. When the timer expires after 100ms, the switcher engages the start-up sequence and runs for 10ms, repeatedly checking for the over-current condition. Figure 13 describes the switching regulator over-current condition and current limit. During the current limited operation (e.g., in case of short circuit on the switching regulator output), the switching regulator operation is not synchronized to the oscillator frequency. Figure 14 (respectively Figure 15) depicts the current limit with a retry capability feature of the switcher (respectively LDO).

Figure 14. Switching Converter Over-current Protection

Figure 15. LDO Converter Over-current Protection

The output voltage VOUT can be adjusted by means of an external resistor divider connected to the feedback control pin INV. The switching regulator output voltage can be adjusted in the range of 0.8V to VIN - buck dropout voltage. Power-up, power-down, and fault management are coordinated with the linear regulator.

### **SWITCHER OSCILLATOR**

A 300kHz (default) oscillator sets the switching frequency of the buck regulator. The frequency of the oscillator can be adjusted between 200kHz and 400kHz by an optional external resistor RF connected from the FREQ pin of the integrated circuit to ground. See <a href="Figure 6">Figure 6</a> on page 14 for frequency resistor selection.

The CLKSYN pin can be configured as either an oscillator output when the CLKSEL pin is left open or as a synchronization input when the CLKSEL pin is grounded. The oscillator output signal is a square wave logic signal with 50% duty cycle, 180 degrees out-of-phase with the internal clock signal. This allows opposite phase synchronization of two 34702 devices.

When the CLKSYN pin is used as a synchronization input (CLKSEL pin grounded), the external resistor RF chosen from the chart in Figure 6 should be used to synchronize the internal slope compensation ramp to the external clock. Operation is only recommended between 200kHz and 400kHz. The supplied synchronization signal does not need to be 50% duty cycle. Minimum pulse width is 1.0µs.

### LOW DROPOUT LINEAR REGULATOR (LDO)

The adjustable low dropout linear regulator (LDO) is capable of supplying a 1.0A output current. It has a current limit with retry capability. When the voltage measured across the current sense resistor reaches the 50mV threshold, the control circuit limits the current for 10ms. If the over-current condition still exists, the linear regulator is turned off and the retry timer starts to time out. When the timer expires after

100ms, the LDO tries to power up again for 10ms, repeatedly checking for the over-current condition. The current limit of the LDO can be set by using the following formula:

$$I_{LIM} = 50 \text{mV/RS}$$

Where RS is the LDO current sense resistor, connected between the CS pin and the LDO pin output (see <u>Figure 33</u> on page <u>34</u>), and 50mV is the typical value of the LDO current sense comparator threshold voltage.

When no current sense resistor is used, it is still possible to detect the over-current condition by tying the current sense pin CS to the VBST voltage. In this case, the over-current condition is sensed by saturation of the linear regulator driver buffer.

The output voltage of the LDO can be adjusted by means of an external resistor divider connected to the feedback control pin LFB. The linear regulator output voltage can be adjusted in the range of 0.8V to VIN - LDO dropout voltage. Power-up, power-down, and fault management are coordinated with the switching regulator.

# POWER SEQUENCING VOLTAGE MARGINING WATCHDOG TIMER

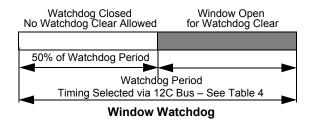

A watchdog function is available via I<sup>2</sup>C bus communication. It is possible to select either window watchdog or timeout watchdog operation, as illustrated in Figure 16.

Watchdog timeout starts when the watchdog function is activated via I<sup>2</sup>C bus sending a watchdog programming command byte, thus determining watchdog operation (window or timeout) and period duration (refer to <u>Table 8</u>, page <u>27</u>). If the watchdog is cleared by receiving a new watchdog programming command through the I<sup>2</sup>C bus, the watchdog timer is reset and the <u>new</u> timeout period begins. If the watchdog time expires, the <u>RST</u> will become active (LOW) for a time determined by the RC components of the RT timer plus 10ms. After a watchdog timeout, the function is no longer active.

ARCHIVE INFORMATION

Window Open for Watchdog Clear

Figure 16. Watchdog Operation

34702

**ARCHIVE INFORMATION**

When the window watchdog function is selected, the timer cannot be cleared during the closed window time, which is 50% of the total watchdog period. When the watchdog is cleared, the timer is reset and starts a new timeout period. If

the watchdog is not cleared during the open window time, the  $\overline{\text{RST}}$  will become active (LOW) for a time determined by the RC components of the RT timer plus 10ms.

### **FUNCTIONAL DEVICE OPERATION**

### **OPERATIONAL MODES**

### THERMAL SHUTDOWN

To increase the overall safety of the system designed with the 34702, an internal thermal shutdown function has been incorporated into the switching regulator circuit. The 34702 senses the temperature of the buck regulator main switching MOSFET (high side MOSFET M1; see Figure 2 on page 2), the low side (synchronous MOSFET M2), and control circuit. If the temperature of any of the monitored components exceeds the limit of safe operation (thermal shutdown), the switching regulator and the LDO shut down. After the temperature falls below the value given by the thermal shutdown hysteresis window, the switcher tries again to operate.

The VOUT pull-down MOSFET M3 has an independent thermal shutdown control. If the M3 temperature exceeds the thermal shutdown limit, the M3 is turned off without affecting the switcher operation.

The LDO pull-down MOSFET M4 has an independent thermal shutdown control. If the M4 temperature exceeds the thermal shutdown limit, the M4 will be turned off without affecting the LDO operation.

### **SOFT START**

A switching regulator soft start feature is incorporated in the 34702. The soft start is active each time the IC is enabled, VIN is reapplied, or after a fault retry. Other transient events do not activate the soft start.

### **VOLTAGE MARGINING**

The 34702 includes a voltage margining feature accessed through the  $I^2C$  bus. Voltage margining allows for independent adjustment of the Switcher VOUT voltage and the linear output VLDO. Each can be adjusted up and down in 1.0% steps to a range of  $\pm 7.0\%$ . This feature allows for worst case system validation; i.e., determining the design margin. Margining details are described in the section entitled  $I^2C$  Bus Operation, beginning on page  $\underline{26}$  of this datasheet.

### POWER SEQUENCING MODES

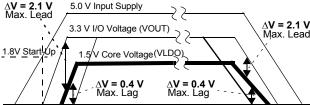

The power sequencing of the two outputs of this power supply IC is in compliance with the Freescale Power QUICC and other 32-bit microprocessor requirements. When the input voltage is applied, the switcher and linear regulator outputs follow the supply rail voltage during power-up and power-down in the limits given by the microcontroller power sequencing specification, illustrated in <a href="Figures 17">Figures 17</a> through <a href="19">19</a>. There are two possible power sequencing modes, Standard and Inverted, as explained in more detail below. The third mode of operation is Power Sequencing Disabled.

Figure 17. Standard Power-up/Down Sequence in +3.3V Supply System

IVE INFORMATION

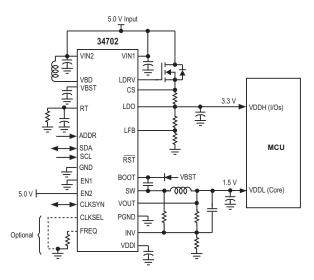

Figure 18. Standard Power-up/Down Sequence in +5.0V Supply System

### STANDARD POWER SEQUENCING

When the power supply IC operates in the Standard Power Sequencing Mode, the switcher output provides the core voltage for the microprocessor. This situation and operating conditions are illustrated in <a href="Figures 17">Figures 17</a> and <a href="18">18</a>. <a href="Table 5">Table 5</a>, page <a href="17">17</a>, shows the Power Sequencing Mode selection.

### INVERTED POWER SEQUENCING

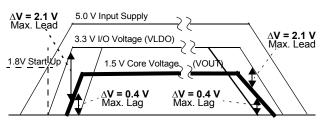

When the power supply IC is operating in the Inverted Power Sequencing Mode, the linear regulator (LDO) output provides the core voltage for the microprocessor, as illustrated in <a href="Figure 19">Figure 19</a>. <a href="Table 5">Table 5</a> shows the Power Sequencing Mode selection.

Figure 19. Inverted Power-up/Down Sequence in +5.0V Supply System

### **ASSUMED REQUIREMENTS**

- I/O supply voltage not to exceed core voltage by more than 2.0V.

- Core supply voltage not to exceed I/O voltage by more than 0.4V.

### **Methods of Control**

The 34702 has several methods of monitoring and controlling the regulator output voltages, as described in the paragraphs below. Power sequencing control is also achieved through the intrinsic operation of the regulators. The EN1 and EN2 pins can be used to select the proper Power Sequencing Mode required by the powered system or to disable the power sequencing (refer to Table 5).

### **Intrinsic Operation**

For both the LDO and switcher, whenever the output voltage is below the regulation point, the LDO external Pass MOSFET is on, or the buck high side MOSFET is on at a duty cycle controlled by the switcher. Because these devices are MOSFETs, current can flow in either direction, balancing the voltages via the common supply pin. The ability to maintain the MOSFETs on is dependent on the available gate voltage, and thus the size of the boost regulator storage capacitor.

### **Standard Power Sequencing Control**

Comparators monitor voltage differences between the LDO (LDO pin) and the switcher (VOUT pin) outputs as follows:

- LDO > VOUT + 1.9V, turn off LDO. The LDO can be forced off. This occurs whenever the LDO output voltage exceeds the switcher output voltage by more than 1.9V.

- 2. LDO > VOUT + 2.0V, shunt LDO to ground. If turning off the LDO is insufficient and the LDO output voltage exceeds the switcher output voltage by more than 2.0V, a 1.5Ω shunt MOSFET is turned on that discharges the LDO load capacitor to ground. The shunt MOSFET is used for switcher output shorts to ground and for power down in case of VIN1 ≠ VIN2 with the switcher output falling faster than the LDO.

- 3. LDO < VOUT + 1.9V cancel (2).

- LDO < VOUT + 1.8V, cancel (1) above, re-enable LDO. Normal operation resumes when the LDO output voltage is less than 1.8V above the switcher output voltage.

- LDO < VOUT 0.1V, turn off switcher. The switcher can be forced off. This occurs whenever the LDO is less than VOUT - 0.1V.

- LDO < VOUT 0.3V, turn on Sync (LS) MOSFET and 1.5Ω VOUT sink MOSFET. The buck high side MOSFET is forced off and the Sync MOSFET is forced on. This occurs when the switcher output voltage exceeds the LDO output by more than 300mV.

- 7. LDO > VOUT 0.3V, cancel (6).

- LDO > VOUT 0.1V, cancel (5). Normal operation resumes when LDO < VOUT - 0.1V.</li>

### **Inverted Power Sequencing Control**

Comparators monitor voltage differences between the switcher (VOUT pin) and LDO (LDO pin) outputs as follows:

- VOUT > LDO + 1.8V, turn off VOUT. The switcher VOUT can be forced off. This occurs whenever the VOUT output voltage exceeds the LDO output voltage by more than 1.8V.

- 2. VOUT > LDO + 2.0V, shunt VOUT to ground. If turning off the switcher VOUT is insufficient and the VOUT output voltage exceeds the LDO output voltage by more than 2.0V, a 1.5Ω shunt MOSFET and the switcher synchronous MOSFET are turned on to discharge the VOUT load capacitor to ground. The shunt MOSFET and synchronous MOSFET are used for LDO output shorts to ground and for power-down in case of VIN1 ≠ VIN2 with LDO output falling faster than the VOUT.

- VOUT < LDO + 1.8V, cancel (1) and (2) above, reenable VOUT. Normal operation resumes when the

- VOUT output voltage is less than 1.8V above the LDO output voltage.

- 4. VOUT < LDO + 2.0V, cancel (2)

- VOUT < LDO 0.2V, turn off LDO. The LDO can be forced off. This occurs whenever the VOUT is less than VLDO - 0.2V.

- VOUT < LDO 0.3V, turn on the 1.5Ω LDO sink

MOSFET. This occurs when the LDO output voltage

exceeds the VOUT output by more than 300mV.</li>

- 7. VOUT < LDO 0.2V, cancel (6).

- 8. VOUT < LDO 0.1V, cancel (5). Normal operation resumes when VOUT > LDO 0.1V.

### STANDARD OPERATING MODE

### Single 3.3V Supply, VIN = VIN1 = VIN2 = 3.3V

The 3.3V supplies the microprocessor I/O voltage, the switcher supplies core voltage (e.g., 1.5V nominal), and the LDO operates independently (see Figure 17, page 22). Power sequencing depends only on the normal switcher intrinsic operation to control the buck high side MOSFET.

### Power-up

When VIN is rising, initially VOUT is below the regulation point and the buck high side MOSFET is on. In order not to exceed the 2.1V differential requirement between the I/O (VIN) and the core (VOUT), the switcher must start up at 2.1V or less and be able to maintain the 2.1V or less differential. The maximum slew rate for VIN is 1.0V/ms.

CHIVE INFORMATION

### Power-down

When VIN is falling, VOUT falls below the regulation point; therefore, the buck high side MOSFET is on. In the case where VOUT is falling faster than VIN, the buck high side MOSFET attempts to maintain VOUT. In the case where VIN is falling faster than VOUT, the buck high side MOSFET is also on, and the VOUT load capacitor is discharged through the buck high side MOSFET to VIN. Thus, provided VIN does not fall too fast, the core voltage (VOUT) does not exceed the I/O voltage (VIN) by more than a maximum of 0.4V.

### Shorted Load

- VOUT shorted to ground. This causes the I/O voltage to exceed the core voltage by more than 2.1V. No load protection.

- VIN shorted to ground. Until the switcher load capacitance is discharged, the core voltage exceeds the I/O voltage by more than 0.4V. By the intrinsic operation of the switcher, the load capacitor is discharged rapidly through the buck high side MOSFET to VIN.

- VOUT shorted to supply. No load protection. 34702 is protected by current limit and thermal shutdown.

# Single 5.0V Supply, VIN1 = VIN2, or Dual Supply VIN1 $\neq$ VIN2

The LDO supplies the microprocessor I/O voltage. The switcher supplies the core (e.g., 1.5V nominal) (see Figure 18, page 23).

### Power-up

This condition depends upon the regulator current limit, load current and capacitance, and the relative rise times of the VIN1 and VIN2 supplies. There are two cases:

- LDO rises faster than VOUT. The LDO uses control methods (1) and (2) described in the section Methods of Control on page 23.

- VOUT rises faster than LDO. The switcher uses control methods (5) and (6) described in the section Methods of Control on page 23.

### Power-down

INFORMATIO

This condition depends upon the regulator load current and capacitance, and the relative fall times of the VIN1 and VIN2 supplies. There are two cases:

- VOUT falls faster than LDO. The LDO uses control methods (1) and (2) described in the section Methods of Control on page 23.

- In the case VIN1 = VIN2, the intrinsic operation turns on both the buck high side MOSFET and the LDO external Pass MOSFET, and discharges the LDO load capacitor into the VIN supply.

- 2. LDO falls faster than VOUT. The switcher uses control methods (5) and (6) described in the section Methods of Control on page 23.

### Shorted Load

- VOUT shorted to ground. The LDO uses method (1) and (2) described in the section Methods of Control on page 23.

- LDO shorted to ground. The switcher uses control

methods (5) and (6) described in the section Methods

of Control on page 23.

- 3. VIN1 shorted to ground. The device is not working.

- VIN2 shorted to ground with VIN1 and VIN2 different.

This is equivalent to the switcher output shorted to ground.

- 5. VOUT shorted to supply. No load protection. 34702 is protected by current limit and thermal shutdown.

- LDO shorted to supply. No load protection. 34702 is protected by current limit and thermal shutdown.

### **INVERTED OPERATING MODE**

### Single 3.3V Supply, VIN = VIN1 = VIN2 = 3.3V

The 3.3V supplies the microprocessor I/O voltage, the LDO supplies core voltage (e.g., 1.5V nominal), and the switcher VOUT operates independently. Power sequencing

depends only on the normal LDO intrinsic operation to control the Pass MOSFET.

### Power-up

When VIN is rising, initially LDO is below the regulation point and the Pass MOSFET is on. In order not to exceed the 2.1V differential requirement between the I/O (VIN) and the core (LDO), the LDO must start up at 2.1V or less and be able to maintain the 2.1V or less differential. The maximum slew rate for VIN is 1.0V/ms.

### Power-down

When VIN is falling, LDO falls below the regulation point; therefore, the Pass MOSFET is on. In the case where LDO is falling faster than VIN, the Pass MOSFET attempts to maintain LDO. In the case where VIN is falling faster than LDO, the Pass MOSFET is also on, and the LDO load capacitor is discharged through the Pass MOSFET to VIN. Thus, provided VIN does not fall too fast, the core voltage (LDO) does not exceed the I/O voltage (VIN) by more than maximum of 0.4V.

### Shorted Load

- LDO shorted to ground. This will cause the I/O voltage to exceed the core voltage by more than 2.1V. No load protection.

- 2. VIN shorted to ground. Until the LDO load capacitance is discharged, the core voltage exceeds the I/O voltage by more than 0.4V. By the intrinsic operation of the LDO, the load capacitor is discharged rapidly through the Pass MOSFET to VIN.

- 3. LDO shorted to supply. No load protection.

# Single 5.0V Supply, VIN1 = VIN2, or Dual Supply VIN1 $\neq$ VIN2

The switcher VOUT supplies the microprocessor I/O voltage. The LDO supplies the core (e.g., 1.5V nominal) (see Figure 19, page 23).

### Power-up

This condition depends upon the regulator current limit, load current and capacitance, and the relative rise times of the VIN1 and VIN2 supplies. There are two cases:

- VOUT rises faster than LDO. The switcher VOUT uses control methods (1) and (2) described in the section Methods of Control on page 23.

- 2. *LDO rises faster than VOUT*. The LDO uses control methods (5) and (6) described in the section Methods of Control on page 23.

### Power-down

This condition depends upon the regulator load current and capacitance and the relative fall times of the VIN1 and VIN2 supplies. There are two cases:

34702