Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 8-Channel Ultra-Low Phase Noise Continuous Waveform Transmitter with Beamformer

#### **Features**

- 8-Channel Ultrasound Continuous Waveform (CW) Transmitter with Integrated Beamformer

- CW Output ±1V to ±6Vp-p with Low R<sub>ON</sub>

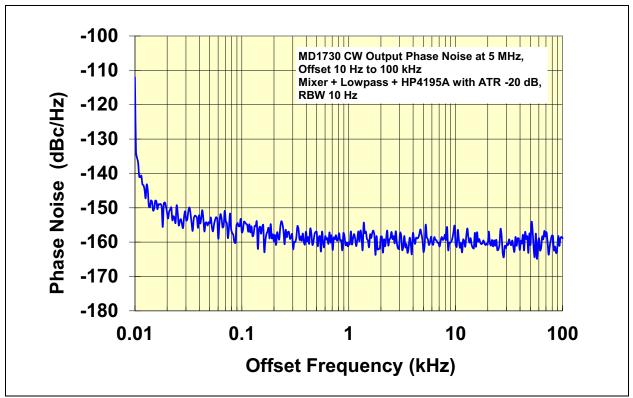

- -160 dbc/Hz Ultra-Low Phase Noise at 1 kHz Offset and 5 MHz

- 8-Bit Programmable Per-Channel Beamforming Phase Delay

- 8-Bit Programmable Dividers for CW Frequency with Input Clock Frequency up to 250 Mhz

- Input Clock Compatible with LVDS/SSTL or Single-Ended LVCMOS

- · LVCMOS 2.5V Logic for the Control I/O pins

- · Fast SPI Interface Supports up to 200 MHz

- SPI Interface Supports Daisy Chaining and Broadcasting Mode

### **Applications**

- Medical Ultrasound Imaging System for Cardiovascular Application

- · Ultrasound Fetal Heart Monitoring Device

- · Ultrasound Flow Meter

- · Programmable Array Pattern Generator

#### **General Description**

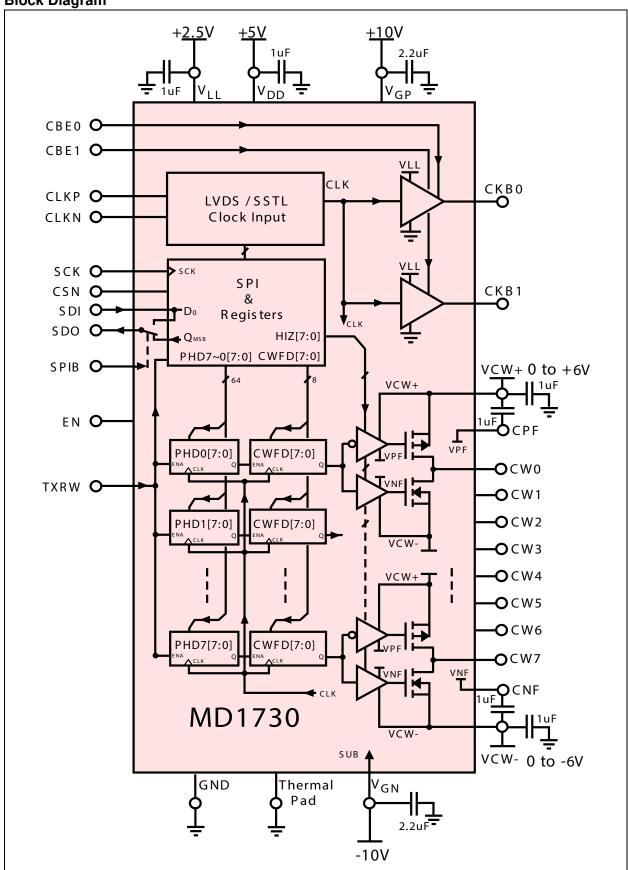

The MD1730 is an 8-channel ultra-low phase noise CW transmitter with integrated beamformer. It is designed for medical ultrasound imaging systems requiring high-performance CW Doppler mode. The MD1730 has a dedicated signal path designed to minimize phase noise to the output. In addition, it has a high-speed SPI interface that enables CW beamforming features. The outputs of the MD1730 can swing up to ±6V and each output has a separate programmable phase delay. Additionally, programming the internal frequency divider register, the MD1730 can output different CW frequencies from a single clock source. For instance, when the input clock frequency is 160 MHz and the frequency divider is set to 16, an output CW frequency of 5 MHz can be obtained with a phase delay step size of 6.25 ns, which translates to an angular resolution of 11.25 degrees.

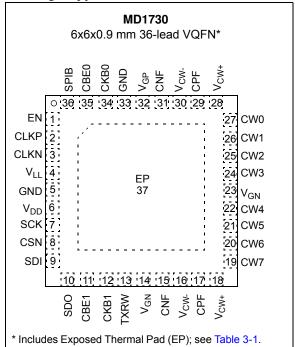

#### **Package Type**

## **Block Diagram**

# **MD1730**

**NOTES:**

#### 1.0 **ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings †

| 0.5V to +3.0V   |

|-----------------|

| 0.5V to +6.0V   |

| 0.5V to +13.5V  |

| +0.5V to -13.5V |

| 0.5V to +12V    |

| +0.5V to -12V   |

| -0.5V to +3.0V  |

| 12V to +12V     |

| 0°C to +85°C    |

| 0°C to +85°C    |

| +125°C          |

| 25°C/W          |

| 6.4°C/W         |

| 13.5°C/W        |

| ±1.0 kV         |

|                 |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

INPUT/OUTPUT PIN DC CHARACTERISTICS **TABLE 1-1:**

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW}$  = -6.0V,  $V_{DD}$  = +5V,  $T_A$  = 25°C. **Parameters** Sym. Min. Typ. Max. **Units Conditions Operating Supply** Logic Supply Voltage  $V_{LL}$ 2.35 2.50 2.65 ٧  $(V_{GP}+|V_{CW-}|) \ge 10V$  $(V_{GN}+|V_{CW+}|) \ge 10V$ 4.75 5.0 5.25 ٧ VDD Supply Voltage  $V_{DD}$  $T_A = 0$  to +85°C, Note 2 ٧  $V_{\mathsf{GP}}$ 12 Positive Supply Voltage 8.0 10 Negative Supply Voltage  $V_{GN}$ -12 -10 -8.0 ٧ CW Output Positive Supply 1.0 6.0 V  $V_{CW+}$ ٧ CW Output Negative Supply -6.0 -1.0  $V_{CW-}$ VII Quiescent Current 0.02 0.1 mΑ EN = 0,  $f_{CLK} = f_{SCK} = 0$  $I_{LLQ}$ All logic input no transit V<sub>DD</sub> Quiescent Current 0.15 0.2 mΑ  $I_{DDQ}$ V<sub>GP</sub> Quiescent Current  $I_{GPQ}$ 1.0 2.0 μΑ 45 V<sub>GN</sub> Quiescent Current 33 μΑ  $I_{GNQ}$ μΑ V<sub>CW+</sub> Quiescent Current 26 45  $I_{CW+Q}$ V<sub>CW</sub>- Quiescent Current 6 10 μΑ  $I_{CW-Q}$ V<sub>LL</sub> Enabled Current 6.0 9.0 EN = 1,  $f_{SCK} = 120 \text{ MHz}$ I<sub>LLEN</sub> mΑ TXRW = 0, SDI = 0, **V<sub>DD</sub>** Enabled Current 0.2 0.3 mΑ I<sub>DDEN</sub> SDO no load. V<sub>GP</sub> Enabled Current 2.0 3.0 mΑ  $I_{GPEN}$ V<sub>GN</sub> Enabled Current 2.0 3.0 mΑ I<sub>GNEN</sub> V<sub>CW+</sub> Enabled Current 2.0 3.0 mΑ I<sub>CW+EN</sub> 3.0

2.0

mΑ

Note 1: Characterized only; not 100% tested in production.

I<sub>CW-EN</sub>

2: Design Guidance Only (DGO).

V<sub>CW-</sub> Enabled Current

TABLE 1-1: INPUT/OUTPUT PIN DC CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| $V_{CW-} = -6.0V, V_{DD} = +5V, T_A = 25^{\circ}C.$ |                   |                     |      |                     |       |                                    |  |  |

|-----------------------------------------------------|-------------------|---------------------|------|---------------------|-------|------------------------------------|--|--|

| Parameters                                          | Sym.              | Min.                | Тур. | Max.                | Units | Conditions                         |  |  |

| V <sub>LL</sub> Current at CW 5MHz                  | I <sub>LL5</sub>  | _                   | 2.5  | 3.0                 | mA    | EN = 1, f <sub>CLK</sub> = 80 MHz, |  |  |

| V <sub>DD</sub> Current at CW 5MHz                  | I <sub>DD5</sub>  | _                   | 1.0  | 2.0                 | mA    | TXRW = 1, CW 5 MHz,                |  |  |

| V <sub>GP</sub> Current at CW 5MHz                  | I <sub>GP5</sub>  | _                   | 6.0  | 10                  | mA    | no load 8-channel                  |  |  |

| V <sub>GN</sub> Current at CW 5MHz                  | I <sub>GN5</sub>  | _                   | 12   | 18                  | mA    |                                    |  |  |

| V <sub>CW+</sub> Current at CW 5MHz                 | I <sub>CW+5</sub> | _                   | 26   | 35                  | mA    |                                    |  |  |

| V <sub>CW-</sub> Current at CW 5MHz                 | I <sub>CW-5</sub> | _                   | 21   | 30                  | mA    |                                    |  |  |

| SPI & Logic                                         |                   |                     |      |                     |       |                                    |  |  |

| Input Logic High Voltage                            | $V_{IH}$          | 0.8 V <sub>LL</sub> | _    | $V_{LL}$            | V     | 2.5V LVCMOS                        |  |  |

| Input Logic Low Voltage                             | V <sub>IL</sub>   | 0                   | _    | 0.2 V <sub>LL</sub> | V     |                                    |  |  |

| Input Logic High Current                            | I <sub>IH</sub>   | _                   | _    | 1.0                 | μA    |                                    |  |  |

| Input Logic Low Current                             | I <sub>IL</sub>   |                     | _    | _                   | μA    |                                    |  |  |

| SPI and Logic Input Capacitance                     | C <sub>IN</sub>   | _                   | 4.5  | _                   | pF    | Note 1                             |  |  |

| Output Logic High Current                           | I <sub>OH</sub>   |                     | _    | _                   | mA    | 2.5V LVCMOS                        |  |  |

| Output Logic Low Current                            | I <sub>OL</sub>   |                     | _    | _                   | mA    |                                    |  |  |

| SDO Output Logic High Voltage                       | V <sub>OH</sub>   |                     | _    | _                   | V     | with 5 pF load                     |  |  |

| SDO Output Logic Low Voltage                        | V <sub>OL</sub>   | _                   | _    | 0.35                | V     |                                    |  |  |

**Note 1:** Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

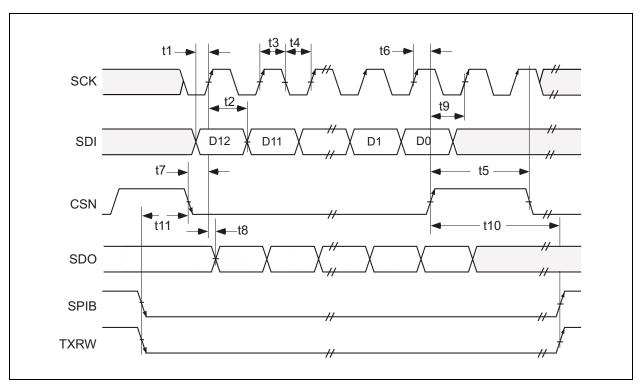

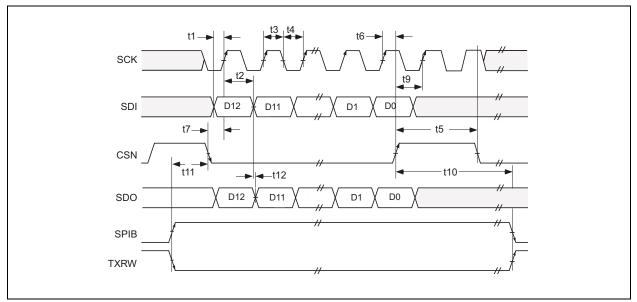

#### TABLE 1-2: SPI AND LOGIC AC ELECTRICAL SPECIFICATIONS

Electrical Specifications: Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| Parameters                            | Sym.            | Min.    | Тур.    | Max. | Units | Conditions                                               |

|---------------------------------------|-----------------|---------|---------|------|-------|----------------------------------------------------------|

| Output Rise Time                      | t <sub>r</sub>  | _       | 0.65    | _    | ns    | 1.5 pF load, Note 1                                      |

| Output Fall Time                      | t <sub>f</sub>  |         | 0.65    | _    |       |                                                          |

| Output Rise Propagation Delay         | t <sub>dr</sub> | _       | 2.8     | _    | ns    | CLK rise 50% to output                                   |

| Output Fall Propagation Delay         | t <sub>df</sub> | _       | 3.0     | _    |       | 50%, after latency.  Note 1                              |

| Delay Time Matching                   | t <sub>dm</sub> | _       | ±0.5    | ±1.0 | ns    | Channel to channel,<br>Note 1, f <sub>CLK</sub> = 80 MHz |

| SDI Valid to SCK, Setup Time          | t <sub>1</sub>  | 0.6     | 1.0     | _    | ns    | Note 1                                                   |

| SCK To SDI Data Hold Time             | t <sub>2</sub>  | 2.0     | _       | _    | ns    |                                                          |

| SCK High Time % of 1/f <sub>CLK</sub> | t <sub>3</sub>  | 45      | _       | 55   | %     | Note 2                                                   |

| SCK Low Time % of 1/f <sub>CLK</sub>  | t <sub>4</sub>  | 45      | _       | 55   | %     | 7                                                        |

| CSN Hi-Time                           | t <sub>5</sub>  | 2-cycle | _       | _    | SCK   | Note 2                                                   |

| SCK Rise to CSN Rise                  | t <sub>6</sub>  | _       | 2.0     | _    | ns    | Note 1                                                   |

| CSN Low to SCK Rise                   | t <sub>7</sub>  | _       | 0.8     | _    | ns    |                                                          |

| SDO Valid from SCK Rise               | t <sub>8</sub>  | _       | 3.1     | 4.0  | ns    | SPIB = 0, 1.5 pF Load,<br>Note 1                         |

| CSN Rise to SCK Rise                  | t <sub>9</sub>  | _       | 2.0     | _    | ns    | Note 1                                                   |

| CSN Rise to TXRW or SPIB Rise         | t <sub>10</sub> | 9-cycle |         |      | SCK   | Note 2                                                   |

| TXRW or SPIB Fall to CSN Fall         | t <sub>11</sub> |         | 1-cycle |      |       |                                                          |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

TABLE 1-2: SPI AND LOGIC AC ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-} = -6.0V$ ,  $V_{DD} = +5V$ ,  $T_A = 25$ °C. **Conditions Parameters** Sym. Min. Typ. Max. **Units** SPIB = 1, 1.5 pF Load, SDO to SDI Valid Delay 2.3 3.0 t<sub>12</sub> ns Note 1 TXRW Rise to CLKP Rise Note 1 2.5 ns t<sub>13</sub> Latency to CW Wave Rise t<sub>14</sub> 2-cycle CLK After TXRW = 1, PHD=0, Note 2 Latency CSN Rise to TXRW Fall CLK Note 2 2-cycle t<sub>15</sub> SCK Clock Frequency 200 MHz Note 1  $f_{SCK}$ **EN Off Time** 20 30 ns Note 2 t<sub>EN-Off</sub> **EN On Time** 300 2.0 µF on CPF/CNF, 150 t<sub>EN-On</sub> μs Note 2

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

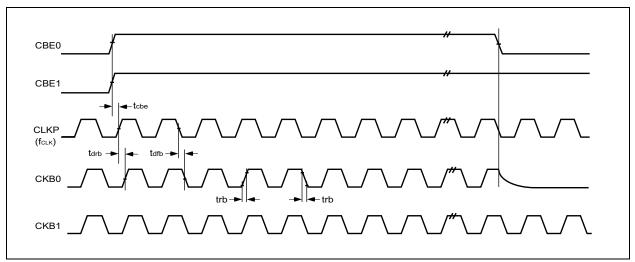

TABLE 1-3: CLOCK BUFFER OUTPUTS AC/DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| V <sub>CW-</sub> 0.00, V <sub>DD</sub> - 130, 1 <sub>A</sub> - 23 G. |                    |      |          |      |       |                                   |  |  |  |

|----------------------------------------------------------------------|--------------------|------|----------|------|-------|-----------------------------------|--|--|--|

| Parameters                                                           | Sym.               | Min. | Тур.     | Max. | Units | Conditions                        |  |  |  |

| Clock Output Frequency<br>Range                                      | f <sub>CKB</sub>   | 40   | 160      | 250  | MHz   | Note 1                            |  |  |  |

| Clock Output Duty Cycle                                              | D%                 | 45   |          | 55   | %     | Note 2                            |  |  |  |

| CKB0,1 Rise Time                                                     | t <sub>rb</sub>    | _    | 0.6      | 1.0  | ns    | f <sub>CLK</sub> = 80 Mhz, 1.5 pF |  |  |  |

| CKB0,1 Fall Time                                                     | t <sub>fb</sub>    | _    | 0.5      | 1.0  |       | load, Note 1                      |  |  |  |

| Output Rise Propagation Delay                                        | t <sub>drb</sub>   | _    | 2.0      | 3.0  | ns    | CLK rise to CKB, 50%, Note 1      |  |  |  |

| Output Fall Propagation Delay                                        | t <sub>dfb</sub>   | _    | 2.0      | 3.0  |       |                                   |  |  |  |

| CBE Enable Time                                                      | t <sub>cbe</sub>   | _    | 2.1      | 3.0  |       | CBE to CLK rise, 50%, Note 1      |  |  |  |

| CKB0,1 Output logic high                                             | V <sub>OHCKB</sub> | _    | $V_{LL}$ | _    | V     | Note 2                            |  |  |  |

| CKB0,1 Output Logic low                                              | V <sub>OLCKB</sub> | _    | GND      | _    | V     | Note 2                            |  |  |  |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

#### TABLE 1-4: CW OUTPUTS DC/AC ELECTRICAL CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| Parameters                       | Sym.               | Min. | Тур. | Max. | Units | Conditions                                     |

|----------------------------------|--------------------|------|------|------|-------|------------------------------------------------|

| CW Output Peak to Peak Voltage   | V <sub>CWOUT</sub> | -6.0 | -    | +6.0 | V     |                                                |

| CW Output Rise Propagation Delay | t <sub>drCW</sub>  | _    | 4.0  | 6.0  | ns    | TxCLK 50% to CWx                               |

| CW Output Fall Propagation Delay | t <sub>dfCW</sub>  | _    | 4.0  | 6.0  |       | 10%, after latency, Note 1                     |

| CW Output Maximum Current        | $I_{\text{CW}\pm}$ | ±250 | ±300 | _    | mA    | $V_{CW\pm}$ = ±5.0V, 0.1 $\Omega$ load, Note 1 |

Note 1: Characterized only; not 100% tested in production.

2: Design Guidance Only (DGO).

#### TABLE 1-4: CW OUTPUTS DC/AC ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL}$  = +2.5V,  $V_{GP}$  = +10V,  $V_{GN}$  = -10V,  $V_{CW+}$  = +6.0V,  $V_{CW-}$  = -6.0V,  $V_{DD}$  = +5V,  $V_{A}$  = 25°C.

| CVV- CVV- CVV-                                 |                     |      |      |      |            |                                            |

|------------------------------------------------|---------------------|------|------|------|------------|--------------------------------------------|

| Parameters                                     | Sym.                | Min. | Тур. | Max. | Units      | Conditions                                 |

| Static Output Resistance PFET                  | R <sub>ONCW</sub>   | _    | 7.5  | 12   | Ω          | RON at $V_{CW\pm} = \pm 5.0V$ ,            |

| Static Output Resistance NFET                  |                     | _    | 6.5  | 11   |            | I <sub>CW±</sub> = ±100 mA load,<br>Note 1 |

| Change in R <sub>DS(ON)</sub> with Temperature | ΔR <sub>ONCW</sub>  | _    | _    | 1.0  | %/C        | $V_{CW\pm} = \pm 5.0V$ , <b>Note 2</b>     |

| CW Phase Resolution                            | RE <sub>Phase</sub> | _    | 1    | _    | CLK        | Note 2                                     |

| CW Phase Noise                                 | N <sub>Phase</sub>  |      | -160 |      | dBC/<br>Hz | CW 5 MHz,<br>1 kHz Offset, Note 1          |

- **Note 1:** Characterized only; not 100% tested in production.

- 2: Design Guidance Only (DGO).

#### TABLE 1-5: LVDS / SSTL CLOCK INPUTS AC / DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $V_{LL} = +2.5V$ ,  $V_{GP} = +10V$ ,  $V_{GN} = -10V$ ,  $V_{CW+} = +6.0V$ ,  $V_{CW-} = -6.0V$ ,  $V_{DD} = +5V$ ,  $T_A = 25$ °C. **Parameters** Sym. Min. Max. Units **Conditions** Тур. CLKP/CLKN Clock Frequency 40 160 250 MHz Note 1  $f_{CLK}$ 1.0 Note 2 Clock Input Slew Rate V/ns t<sub>CSR</sub> Control/Data Input Slew Rate 1.0 V/ns  $t_{DSR}$ Single Ended Clock Input ٧ SSTL Reference Voltage 1.13 1.25 1.38 Note 1  $V_{REFS}$ V Note 1 DC Input Logic High  $V_{IH(DC)}$ V<sub>REFS</sub> +0.15  $V_{LL}$  +0.3 DC Input Logic Low V<sub>REFS</sub> -0.15 ٧ Note 1 V<sub>IL(DC)</sub> -0.3 ٧ AC Input Logic High  $V_{REF} = 0.5V_{LL}$ , Slew  $V_{IH(AC)}$ V<sub>REFS</sub> +0.31 rate 1.0 V/ns, Note 1 AC Input Logic Low V<sub>REFS</sub> -0.31  $V_{IL(AC)}$ **Differential Clock Input** CLK and CLK, Note 1 **AC Differential Cross Point**  $V_{X(AC)}$  $0.5V_{LL}$  -0.2  $0.5V_{11} + 0.2$ DC Input Max Swing Voltage 0.3 V<sub>LL</sub> +0.6 ٧ Note 1 V<sub>SWING(DC)</sub> AC Differential Input Voltage 0.62 ٧ Note 1  $V_{11} + 0.6$ V<sub>SWING(AC)</sub> DC Input Signal Voltage -0.3 V<sub>LL</sub> +0.3 V Note 1  $V_{IN(DC)}$

1.0

Note 1: Characterized only; not 100% tested in production.

**SLEW**

2: Design Guidance Only (DGO).

CLKP/CLKN Slew Rate

Note 2

V/ns

**NOTES:**

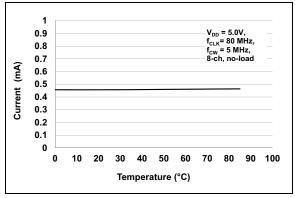

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

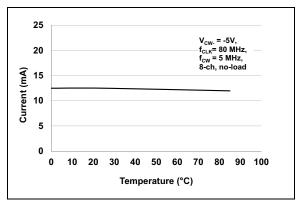

FIGURE 2-1: I<sub>DD</sub> vs. Temperature.

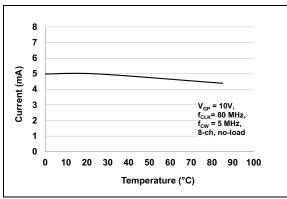

FIGURE 2-2: I<sub>VGP</sub> vs. Temperature.

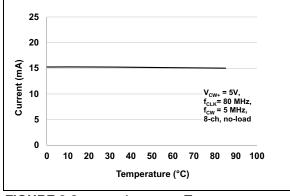

**FIGURE 2-3:**  $I_{VCW+}$  vs. Temperature.

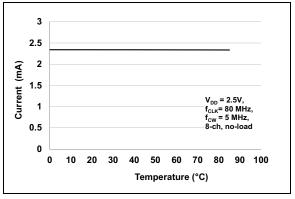

FIGURE 2-4: I<sub>VLL</sub> vs. Temperature.

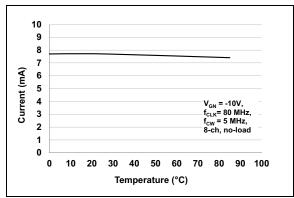

FIGURE 2-5: I<sub>VGN</sub> vs. Temperature.

FIGURE 2-6: I<sub>VCW-</sub> vs. Temperature.

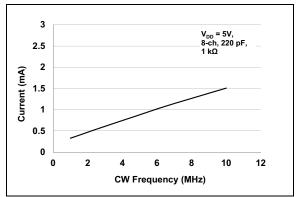

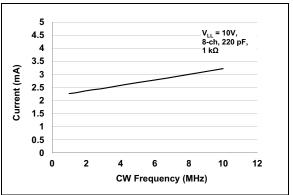

**FIGURE 2-7:** I<sub>VDD</sub> vs. CW Output Frequency.

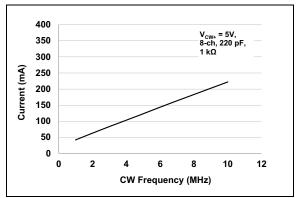

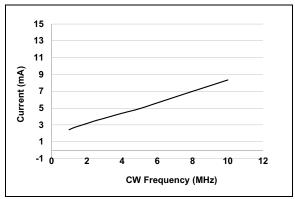

FIGURE 2-8: I<sub>VCW+</sub> vs. CW Output Frequency.

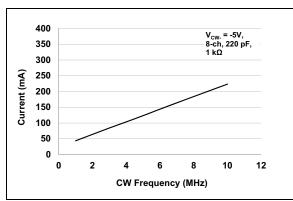

**FIGURE 2-9:** I<sub>VCW-</sub> vs. CW Output Frequency.

**FIGURE 2-10:** I<sub>VLL</sub> vs. CW Output Frequency.

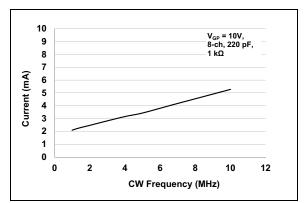

**FIGURE 2-11:** I<sub>VGN</sub> vs. CW Output Frequency.

**FIGURE 2-12:**  $I_{VGP}$  vs. CW Output Frequency.

FIGURE 2-13: Typical CW Output Phase Noise Curves.

# 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| 6x6 VQFN                             | Symbol           | Pin Function                                                                                                                                                                                                                             |

|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                    | EN               | Device Enable Input. When EN = 0, the SPI and the internal regulator are disabled. The device is enabled when EN = 1. Note that the EN pin has no control over the clock buffers, as the clock buffers have their dedicated enable pins. |

| 2                                    | CLKP             | Positive Input of the Internal System Clock and is compatible with LVDS/SSTL. For LVCMOS 2.5V input refer to Figure 4-8.                                                                                                                 |

| 3                                    | CLKN             | Negative Input of the Internal System Clock and is compatible with LVDS/SSTL. For LVCMOS 2.5V input refer to Figure 4-8.                                                                                                                 |

| 4                                    | $V_{LL}$         | +2.5V Positive Voltage Power Supply, it requires a 1.0 μF decoupling capacitor to GND                                                                                                                                                    |

| 5, 33                                | GND              | Ground, 0V                                                                                                                                                                                                                               |

| 6                                    | $V_{DD}$         | +5V Positive Voltage Power Supply, it requires a 1.0 μF decoupling capacitor to GND                                                                                                                                                      |

| 7                                    | SCK              | Serial Peripheral Interface (SPI) clock input                                                                                                                                                                                            |

| 8                                    | CSN              | Serial Peripheral Interface (SPI) chip-select. CSN is an active-low signal.                                                                                                                                                              |

| 9                                    | SDI              | Serial Peripheral Interface (SPI) data input                                                                                                                                                                                             |

| 10                                   | SDO              | Serial Peripheral Interface (SPI) data output                                                                                                                                                                                            |

| 11, 35                               | CBE0-1           | The clock buffer enable pin. When CBEn = 0, the corresponding clock buffer is disabled. The clock buffer is enabled otherwise.                                                                                                           |

| 12, 34                               | CKB0-1           | 2.5V Single-ended Clock Buffer output pins                                                                                                                                                                                               |

| 13                                   | TXRW             | CW Transmission Control pin. When TXRW = 0, the SPI is enabled for read/write. When TXRW = 1, the SPI is disabled and the CW transmission is started.                                                                                    |

| 14, 23                               | $V_{GN}$         | -10V Negative Voltage Power Supply, it requires a 2.2 $\mu$ F capacitor to GND. The V <sub>GN</sub> supply is also the substrate and should be the most negative supply to the chip.                                                     |

| 15, 31                               | CNF              | Negative Floating Supply Bypass Capacitor pin. Connects 1 $\mu$ F/10V capacitor between this pin and the $V_{\text{CW-}}$ pin.                                                                                                           |

| 16, 30                               | V <sub>CW-</sub> | -1V to -6V Negative Voltage Power Supply for the CW output, it requires a 1.0 μF decoupling capacitor per pin to GND                                                                                                                     |

| 17, 29                               | CPF              | Positive Floating Supply Bypass Capacitor pin. Connects 1 $\mu$ F/10V capacitor between this pin and the $V_{CW+}$ pin.                                                                                                                  |

| 18, 28                               | V <sub>CW+</sub> | +1V to +6V Positive Voltage Power Supply for the CW output. It requires a 1.0 μF decoupling capacitor per pin to GND.                                                                                                                    |

| 19, 20, 21,<br>22, 24, 25,<br>26, 27 | CW0-7            | Channel 0-7 CW Waveform Output                                                                                                                                                                                                           |

| 32                                   | V <sub>GP</sub>  | +10V Positive Voltage Power Supply, it requires a 2.2 µF decoupling capacitor to GND                                                                                                                                                     |

| 36                                   | SPIB             | SPI Broadcasting Mode pin. When SPIB = 1, the broadcast mode is enabled.                                                                                                                                                                 |

| 37                                   | EP               | Exposed Thermal Pad (EP); must be connected to GND                                                                                                                                                                                       |

# **MD1730**

**NOTES:**

#### 4.0 DEVICE DESCRIPTION

#### 4.1 Operation Description

The MD1730 is an 8-channel ultra-low phase noise monolithic CW transmitter. It consists of an SPI interface to program internal phase delay registers and frequency dividers to facilitate CW beamforming. It supports differential LVDS/SSTL and single-ended 2.5V LVCMOS clock inputs. The MD1730's output path is designed to provide ultra-low phase noise and can swing up to ±6V. The following sections provide a detailed overview of MD1730's feature set and operation.

## 4.2 Using The Built-in Clock Buffers

The MD1730 has two built-in single ended clock output buffers. The MD1730 can accept LVDS, SSTL25 and LVCMOS 2.5V clock at its input and provide a single-ended output buffered clock. The clock buffers are independent of the chip's main EN pin and each output clock buffer can be enabled or disabled separately using the CBE0 or CBE1 pin. The maximum clock frequency of the buffers is 250 MHz. The output timing diagram for the clock buffers is shown in Figure 4-5. As shown in the diagram CKB0 and CKB1, clock outputs are only dependent on CBE0 and CBE1 respectively. This feature makes it convenient to drive the TX pulser retiming clock input, such as the HV7321. Using the built in clock buffers will save the cost of additional buffers, reduce PCB area, simplify the system clock distribution design and improve power savings as well.

#### 4.3 SPI Registers Description

#### REGISTER 4-1: SPI CONTROL REGISTER DESCRIPTION

| Data Bits               | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W/R                     | The W/R is the read write control bit. When W/R = 1, the SPI writes the data provided at the addressed register. When W/R = 0, the SPI reads the data stored from the appropriate register. The read operation is disabled when SPIB = $1$ .                                                                                                                                            |

| CWFD<7:0>               | The CWFD<7:0> register stores the divisor value for setting the CW output frequency. The CW output frequency is set by using the equation ( $f_{CW} = f_{CLK}/(2*CWFD)$ ) except CWFD = 0. For CWFD = 0 the CW output frequency is $f_{CW} = f_{CLK}/2*512$ . The CW output frequency ranges from ( $f_{CLK}/512$ ) $\leq f_{CW} \leq (f_{CLK}/2)$ . The register's initial value is 0. |

| PHD <sub>CH</sub> <7:0> | $PHD_{CH}$ <7:0> sets the phase delay for each individual channel. The equation for the output delay time is $PHD$ <7:0>/ $f_{CLK}$ + $2/f_{CLK}$ once TXRW goes high. The register initial value is 0. Refer to Figure 4-4 for further details.                                                                                                                                        |

| HIZ <sub>CH</sub>       | $HIZ_{CH}$ bit enables the channel output when the corresponding bit is 0. The channel is disabled and its' output becomes high Z when the corresponding bit is 1. The default register value is 0.                                                                                                                                                                                     |

Note: CH denotes channel number 0 to 7.

REGISTER 4-2: SPI REGISTER ADDRESS AND CONTROL BITS

| W/R                 | SP  | I Registe | r ADD<3 | :0> |      |      | Writ      | e or Read | l Data <7 | :0>      |      |      |

|---------------------|-----|-----------|---------|-----|------|------|-----------|-----------|-----------|----------|------|------|

| D12                 | D11 | D10       | D9      | D8  | D7   | D6   | D5        | D4        | D3        | D2       | D1   | D0   |

|                     | 0   | 0         | 0       | 0   |      | (    | Channel ( | ) phase c | lelay PH  | ID0<7:0> | •    |      |

| 1 = Write           | 0   | 0         | 0       | 1   |      | (    | Channel 1 | l phase c | lelay PH  | ID1<7:0> | į    |      |

| 0 = Read            | 0   | 0         | 1       | 0   |      | (    | Channel 2 | 2 phase c | lelay PH  | ID2<7:0> | i    |      |

| MSB first.          | 0   | 0         | 1       | 1   |      | (    | Channel 3 | 3 phase c | lelay PH  | ID3<7:0> |      |      |

| (See                | 0   | 1         | 0       | 0   |      | (    | Channel 4 | phase o   | lelay PH  | ID4<7:0> |      |      |

| Section 4.3         | 0   | 1         | 0       | 1   |      | (    | Channel 5 | 5 phase c | lelay PH  | ID5<7:0> | •    |      |

| and<br>Section 4.4) | 0   | 1         | 1       | 0   |      | (    | Channel 6 | phase o   | lelay PH  | ID6<7:0> | •    |      |

| ,                   | 0   | 1         | 1       | 1   |      | (    | Channel 7 | 7 phase c | lelay PH  | ID7<7:0> | i    |      |

|                     | 1   | 0         | 0       | 0   | HIZ7 | HIZ6 | HIZ5      | HIZ4      | HIZ3      | HIZ2     | HIZ1 | HIZ0 |

|                     | 1   | 0         | 0       | 1   |      | CW   | frequenc  | y divisor | number    | CWFD<    | 7:0> | ·    |

**Note:** Power-On or EN = 0 sets all the registers to 0.

TABLE 4-1: PHD<7:0> PHASE DELAY TIME REGISTER DESCRIPTION

| PHD<7:0> | Delay Time to Start Transmitting      |

|----------|---------------------------------------|

| 0000000  | 0/f <sub>CLK</sub> (Power-on default) |

| 0000001  | 1/f <sub>CLK</sub>                    |

| 0000010  | 2/f <sub>CLK</sub>                    |

|          |                                       |

| 11111110 | 254/f <sub>CLK</sub>                  |

| 11111111 | 255/f <sub>CLK</sub>                  |

TABLE 4-2: CWFD<7:0> CW FREQUENCY DIVIDER REGISTER DESCRIPTION

| CWFD[7:0] | Transmit CW Frequency f <sub>CW</sub>    |

|-----------|------------------------------------------|

| 0000000   | f <sub>CLK</sub> /512 (Power-on default) |

| 0000001   | f <sub>CLK</sub> /2                      |

| 0000010   | f <sub>CLK</sub> /4                      |

| 00000011  | f <sub>CLK</sub> /6                      |

| •••••     |                                          |

| 11111110  | f <sub>CLK</sub> /508                    |

| 1111111   | f <sub>CLK</sub> /510                    |

**Note:** The selected CW frequency is same for all the CW0~7 outputs:  $f_{CW} = f_{CLK}/2*CWFD$ . The CW frequency applies to all channels.

### 4.4 Serial Peripheral Interface (SPI)

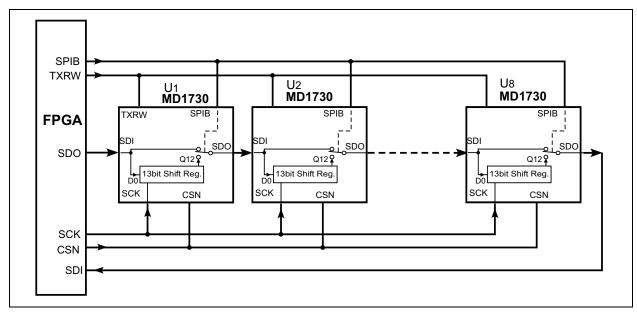

The MD1730's SPI is used to program the phase delay and frequency divider registers. The SPI supports writing at speed up to 200 MHz and the MSB is shifted in first. SPI interface supports two operating modes: daisy chain mode and broadcasting mode.

When SPIB = 0, the MD1730 is in daisy chain mode. In this mode, it supports both read and write operations.

When SPIB = 1 the chip enters the "Broadcasting" mode. In this mode, the SDI data shifts into the shift register as well as to the SDO output. In this mode, the user can write the same register of different daisy chained chips with the same value in a single write

transaction. However, when SPIB = 1 the read operation is disabled. To verify the written data for each chip, the user can revert SPIB = 0 and perform a normal read operation.

#### 4.4.1 SPI WRITE OPERATION EXAMPLES

The following is a 1-byte writing example for the register at ADD = 0011b with the data D<7:0> = 01010101 when SPIB = TXRW = 0.

- The Write operation starts with setting CSN to low.

- 2. The SCK clock is used to shift in the following SDI data:

D12 = 1, W/R bit set equal to high for write operation.

ADD<11:8> = 0011b, address for channel-3's phase delay register.

D<7:0> = 01010101b, data to be written into channel-3's phase delay register.

The SDI data is shifted in at the rising edge of SCK.

3. Once the complete data has been shifted in, the CSN should be taken high to finish the writing operation. The SDI data is latched into channel-3's phase delay register on the rising edge of the CSN signal. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be written into the appropriate register.

In the case of eight chips daisy chained together as shown in Figure 4-3, there should be  $13 \times 8 = 104$  cycles of SCK before the CSN is taken high.

The MD1730 can also be used in the Broadcasting mode to write several daisy chained chips with the same data. The Broadcasting mode can be used to reduce the time required to write the SPI if several MD1730 chips need the same data. The following is a 1-byte writing example for the register at the address location ADD = 0011b with data D<7:0> =01010101b while the MD1730 is set to broadcasting mode.

- The write operation starts with setting CSN to low with TXRW = 0 and SPIB = 1.

- The SCK clock is used to shift in the following SDI data to the first MD1730 chip:

D12 = 1, W/R bit set equal to high for write operation.

ADD<11:8> = 0011b, address for the channel-3's phase delay register.

D<7:0> = 01010101, data to be written into the channel-3's phase delay register.

The SDI data is shifted in at the rising edge of SCK.

In Broadcasting mode, the same set of data shifted into the first chip's SDI is sent to all the MD1730 chips along the daisy chain. As shown is Figure 4-3 when SPIB = 1 an internal switch connects the SDI and SDO directly.

3. Once the complete data has been shifted in, the CSN should be taken high to finish the writing operation. The SDI data is latched into each chip's channel-3 phase delay register on the rising edge of the CSN signal. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be written into the appropriate register.

#### 4.4.2 SPI READ OPERATION EXAMPLES

The following is a 2-byte reading example from the register at ADD = 0011b (Channel-3's phase delay register) when SPIB = TXRW = 0.

- The read operation starts with setting CSN to low

- The SCK clock is used to shift in the following SDI data:

D12 = 0, W/R bit set equal to high for read operation.

ADD<11:8> = 0011b, address for channel-3's phase delay register.

D<7:0> = x, for a Read operation the data field is don't' care.

The SDI data is shifted in at the rising edge of SCK.

- Once the complete data has been shifted into the SPI the CSN is taken high. While CSN is high the MD1730 fetches the data located at ADD<11:9> = 0011b and places it in its internal shift register.

- 4. Once the complete data has been shifted in, the CSN should be taken high to finish the reading operation. While CSN is high the MD1730 fetches the data located at ADD<11:9> = 0011b and places it in its internal shift register. CSN has to be kept high for a minimum of 2-SCK cycles for the data to be fetched and placed into the internal shift register.

- The CSN is taken low and during the next 13 SCK clock cycles, the fetched data in the internal shift register is clocked out on the rising edge of SCK from the SDO of the MD1730.

FIGURE 4-1: SPI Register Read/Write Timing with SPIB = 0, TXRW = 0.

FIGURE 4-2: SPI Register Broadcasting Write Timing with SPIB = 1, TXRW = 0.

**Note:** When in SPIB = 1 mode, the SPI register READ operations are not available.

FIGURE 4-3: Multiple MD1730 Devices SPI Daisy Chain Connections.

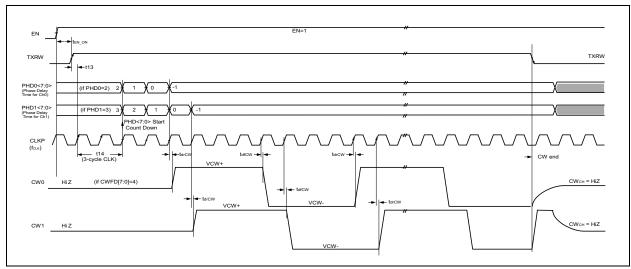

#### 4.5 CW0~7 Output Timing

The CW output waveform transmission timing is crucial to an ultrasound imaging system. Any small timing variations on the output can degrade the phase noise performance. The MD1730's internal circuitry is designed to ensure ultra-low phase noise. Figure 4-4 shows an example of the output waveform timing diagram. The chip is enabled by taking the EN pin high. Then using the SPI, channel-0's and channel-1's phase delay registers (PHD0<7:0> and PHD1<7:0>) are programmed with delays of 2 and 3 respectively. The rest of the channels are set to a high impedance state by programming the HIZ<7:0> register with data 11111100b. Furthermore, the frequency divider register (CWFD<7:0>) is set to 4. After completing the SPI operation the transmission starts by asserting

TXRW high. The phase delay counter starts counting down after a two CLK cycle latency. This is illustrated in Figure 4-4 for channel 0 and channel 1. In channel 0's case, the phase delay starts counting down from 2 to 0 after the latency and once the delay reaches 0 on the next rising edge of CLK, the positive output appears on the pin CW0. Based on the value of the CWFD<7:0> register, after 4-CLK cycles the CW0 output toggles to the negative supply rail. Subsequently, after 4-CLK cycles at the negative rail, the output switches back again to the positive supply rail, completing one full CW output wave cycle. This process continues until the TXRW pin deasserts low, which shuts the transmission off and forces the channel into a high impedance state. This same procedure applies to channel 1, which is also depicted in Figure 4-4.

FIGURE 4-4: CW0~7 Output Timing Diagram.

FIGURE 4-5: Clock Buffers CKB0/1 Output Timing Diagram.

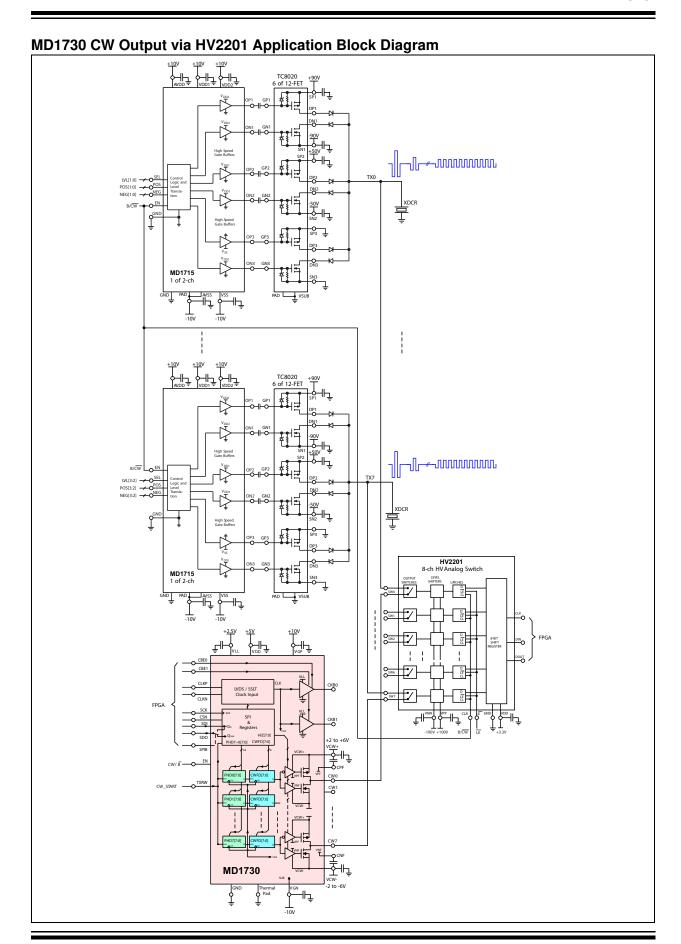

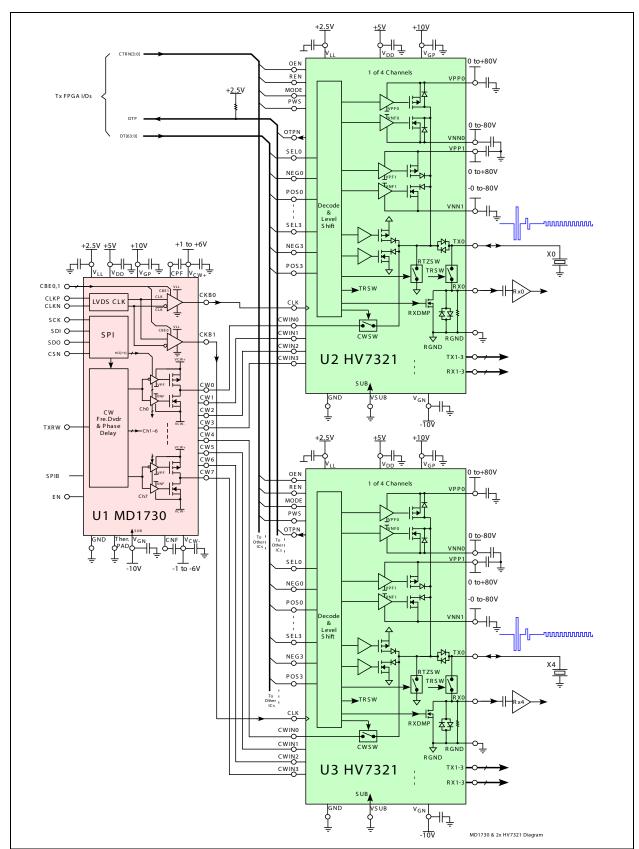

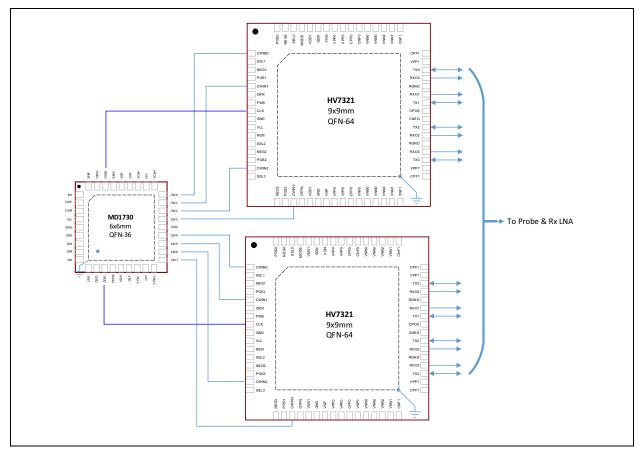

## 4.6 MD1730 Working with Two HV7321

The diagrams shown in Figure 4-6 and Figure 4-7 illustrate the MD1730 driving two HV7321s.

When the HV7321 is operated in the specific mode, CW MODE = 1, along with the MD1730, the following steps should be taken to ensure the combination settings work correctly:

- Apply all power supply rails to both chips and set HV7321's OEN = REN = PWS = 1 along with MD1730's EN = 1 to enable both chips. Set all other control logic pins to zero.

- 7. Adjust the VCW+ and VCW- power supplies to the required peak-to-peak voltage levels for CW output transmission. Please note that a higher peak-to-peak transmission voltage will result in the MD1730 dissipating more power. The power dissipation on the MD1730 is proportional to the square of the peak-to-peak voltage.

- 8. Assert HV7321's MODE pin high.

- Program the MD1730 with the desired CW frequency divider and delay settings for CW transmission.

- 10. To place a channel in receive mode, set the corresponding pins SEL, NEG, POS = 011b on the HV7321. To place a channel to CW Transmit mode, set the corresponding pins SEL, NEG, POS to any other combination other than 011b on HV7321. This will put that channel of the HV7321 high voltage Tx output in High Z mode, but turn the channel's CWSW on.

In the case user wants a channel not in High Z or CW Transmit mode, then similarly, to set the channel of HV7321 to High Z and also set the MD1730's corresponding bit in the HIZ register to 1.

Once the system is ready to perform CW

Doppler measurement, assert TXRW high to

start the CW transmission on the selected

channels.

FIGURE 4-6: MD1730 Works with Two HV7321 4-Channel ±80V 2.6A 5-Level Ultrasound Pulsers.

FIGURE 4-7: MD1730 Working with Two HV7321 Pulsers Pinout and Package.

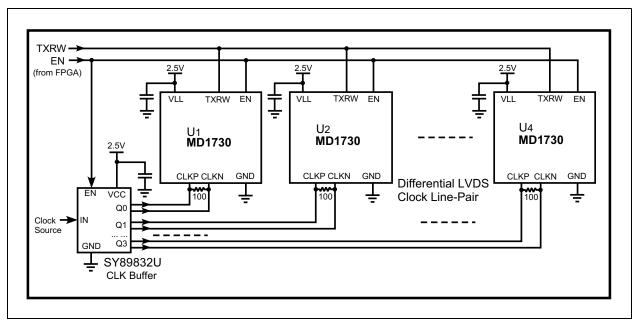

#### 4.7 CW Transmission Clock

The input clock of the MD1730, used for CW transmission, can be connected either differentially or single-ended. Figure 4-8 shows the LVDS differential implementation for the transmission clock. Here the CLKP and the CLKN pins are directly driven by a LVDS clock buffer. It is highly recommended that a multiple-output LVDS clock buffer IC is used, such as the SY89832U, and that a  $100\Omega$  termination resistor is placed very close to the CLKP and CLKN pins. For successful transmission of the LVDS signal over differential traces, the following guidelines should be followed while laying out the PCB board:

- To ensure minimal reflections and to maintain the receiver's common-mode noise rejection, keep the differential traces as short as possible between the clock buffer IC and the CLKP/CLKN pins of the MD1730.

- To reduce skew, the electrical lengths between differential LVDS traces should be identical. The arrival of one differential signal before the other will create a phase difference between the signal pairs, which would create clock skew and impair the system performance.

- · Minimize the number of vias or other

- discontinuities in the signal path. To avoid discontinuities, arcs or 45-degree traces are recommended instead of 90-degree turns.

- Any parasitic loading, such as capacitance, must be present in equal amounts on each differential line.

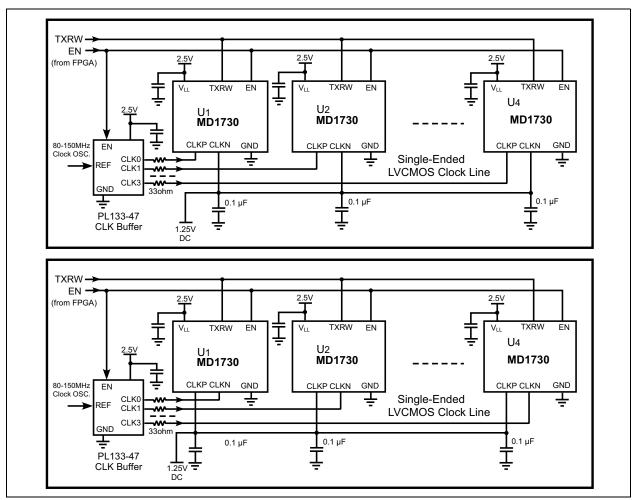

Figure 4-9 illustrates the two cases for the MD1730 used in a single-ended configuration. In these cases, one of the clock input pins, CLKP or CLKN, is connected to the  $V_{LL}/2$  voltage level and bypassed to ground with a 0.1 uF bypass capacitor. Each bypass capacitor must be placed very close to the MD1730. The other clock input pin connects to the main clock line. The PCB traces on the clock line must be designed for a  $50\Omega$  impedance with respect to the PCB ground place. Also, the clock pin must be terminated with a small  $50\Omega$  SMT resistor.

Generally, the LVCMOS input configuration provides better CW phase noise performance due to its higher amplitude swing as compared to the LVDS configuration. However, if the user needs a very high frequency clock transmission, such as 160 MHz-240 MHz range for a higher phase delay resolution, then LVDS should be used because it provides a better PCB clock trace distribution.

FIGURE 4-8: LVDS Differential Transmission Clock.

FIGURE 4-9: LVCMOS Single-Ended Transmission Clock.

# **MD1730**

**NOTES:**

#### 5.0 PACKAGING INFORMATION

### 5.1 Package Marking Information

36-Lead VQFN (6x6x0.9 mm)

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

© 2016 Microchip Technology Inc.