# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Standard performance MIFARE and NTAG frontend

Rev. 3.9 — 27 April 2016 112139 Product data sheet COMPANY PUBLIC

### 1. Introduction

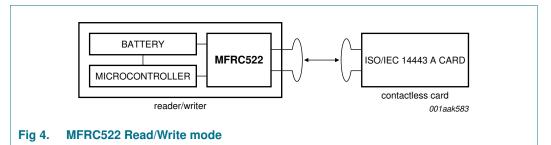

This document describes the functionality and electrical specifications of the contactless reader/writer MFRC522.

**Remark:** The MFRC522 supports all variants of the MIFARE Mini, MIFARE 1K, MIFARE 4K, MIFARE Ultralight, MIFARE DESFire EV1 and MIFARE Plus RF identification protocols. To aid readability throughout this data sheet, the MIFARE Mini, MIFARE 1K, MIFARE 4K, MIFARE Ultralight, MIFARE DESFire EV1 and MIFARE Plus products and protocols have the generic name MIFARE.

### 1.1 Differences between version 1.0 and 2.0

The MFRC522 is available in two versions:

- MFRC52201HN1, hereafter referred to version 1.0 and

- MFRC52202HN1, hereafter referred to version 2.0.

The MFRC522 version 2.0 is fully compatible to version 1.0 and offers in addition the following features and improvements:

- Increased stability of the reader IC in rough conditions

- An additional timer prescaler, see Section 8.5.

- · A corrected CRC handling when RX Multiple is set to 1

This data sheet version covers both versions of the MFRC522 and describes the differences between the versions if applicable.

### 2. General description

The MFRC522 is a highly integrated reader/writer IC for contactless communication at 13.56 MHz. The MFRC522 reader supports ISO/IEC 14443 A/MIFARE and NTAG.

The MFRC522's internal transmitter is able to drive a reader/writer antenna designed to communicate with ISO/IEC 14443 A/MIFARE cards and transponders without additional active circuitry. The receiver module provides a robust and efficient implementation for demodulating and decoding signals from ISO/IEC 14443 A/MIFARE compatible cards and transponders. The digital module manages the complete ISO/IEC 14443 A framing and error detection (parity and CRC) functionality.

The MFRC522 supports MF1xxS20, MF1xxS70 and MF1xxS50 products. The MFRC522 supports contactless communication and uses MIFARE higher transfer speeds up to 848 kBd in both directions.

#### Standard performance MIFARE and NTAG frontend

The following host interfaces are provided:

- Serial Peripheral Interface (SPI)

- Serial UART (similar to RS232 with voltage levels dependant on pin voltage supply)

- I<sup>2</sup>C-bus interface

### 3. Features and benefits

- Highly integrated analog circuitry to demodulate and decode responses

- Buffered output drivers for connecting an antenna with the minimum number of external components

- Supports ISO/IEC 14443 A/MIFARE and NTAG

- Typical operating distance in Read/Write mode up to 50 mm depending on the antenna size and tuning

- Supports MF1xxS20, MF1xxS70 and MF1xxS50 encryption in Read/Write mode

- Supports ISO/IEC 14443 A higher transfer speed communication up to 848 kBd

- Supports MFIN/MFOUT

- Additional internal power supply to the smart card IC connected via MFIN/MFOUT

- Supported host interfaces

- SPI up to 10 Mbit/s

- I<sup>2</sup>C-bus interface up to 400 kBd in Fast mode, up to 3400 kBd in High-speed mode

- RS232 Serial UART up to 1228.8 kBd, with voltage levels dependant on pin voltage supply

- FIFO buffer handles 64 byte send and receive

- Flexible interrupt modes

- Hard reset with low power function

- Power-down by software mode

- Programmable timer

- Internal oscillator for connection to 27.12 MHz quartz crystal

- 2.5 V to 3.3 V power supply

- CRC coprocessor

- Programmable I/O pins

- Internal self-test

## 4. Quick reference data

| Table 1.              | Quick reference data   |                                                         |        |     |     |     |      |  |  |

|-----------------------|------------------------|---------------------------------------------------------|--------|-----|-----|-----|------|--|--|

| Symbol                | Parameter              | Conditions                                              |        | Min | Тур | Max | Unit |  |  |

| V <sub>DDA</sub>      | analog supply voltage  | $V_{DD(PVDD)} \le V_{DDA} = V_{DDD} = V_{DD(TVDD)};$    | [1][2] | 2.5 | 3.3 | 3.6 | V    |  |  |

| V <sub>DDD</sub>      | digital supply voltage | $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$ |        | 2.5 | 3.3 | 3.6 | V    |  |  |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage    |                                                         |        | 2.5 | 3.3 | 3.6 | V    |  |  |

| V <sub>DD(PVDD)</sub> | PVDD supply voltage    |                                                         | [3]    | 1.6 | 1.8 | 3.6 | V    |  |  |

| V <sub>DD(SVDD)</sub> | SVDD supply voltage    | $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$ |        | 1.6 | -   | 3.6 | V    |  |  |

MFRC522

112139

#### Standard performance MIFARE and NTAG frontend

| Table 1. Quick reference data continued |                                                                                                  |                                                                  |            |     |     |     |      |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------|-----|-----|-----|------|

| Symbol                                  | Parameter                                                                                        | Conditions                                                       |            | Min | Тур | Max | Unit |

| I <sub>pd</sub>                         | power-down current                                                                               | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)} = 3 V$          |            |     |     |     |      |

|                                         |                                                                                                  | hard power-down; pin NRSTPD set LOW                              | <u>[4]</u> | -   | -   | 5   | μA   |

|                                         |                                                                                                  | soft power-down; RF level detector on                            | <u>[4]</u> | -   | -   | 10  | μA   |

| I <sub>DDD</sub>                        | digital supply current                                                                           | pin DVDD; V <sub>DDD</sub> = 3 V                                 |            | -   | 6.5 | 9   | mA   |

| I <sub>DDA</sub> analog supply current  | analog supply current                                                                            | pin AVDD; $V_{DDA} = 3 V$ , CommandReg register's RcvOff bit = 0 |            | -   | 7   | 10  | mA   |

|                                         | pin AVDD; receiver switched off; V <sub>DDA</sub> = 3 V,<br>CommandReg register's RcvOff bit = 1 |                                                                  | -          | 3   | 5   | mA  |      |

| I <sub>DD(PVDD)</sub>                   | PVDD supply current                                                                              | pin PVDD                                                         | <u>[5]</u> | -   | -   | 40  | mA   |

| I <sub>DD(TVDD)</sub>                   | TVDD supply current                                                                              | pin TVDD; continuous wave                                        |            | -   | 60  | 100 | mA   |

| T <sub>amb</sub>                        | ambient temperature                                                                              | HVQFN32                                                          |            | -25 | -   | +85 | °C   |

#### Table 1. Quick reference data ...continued

[1] Supply voltages below 3 V reduce the performance in, for example, the achievable operating distance.

- [2]  $~V_{\text{DDA}},\,V_{\text{DDD}}$  and  $V_{\text{DD}(\text{TVDD})}$  must always be the same voltage.

- $\label{eq:VDD} [3] \quad V_{DD(PVDD)} \text{ must always be the same or lower voltage than } V_{DDD}.$

- [4] I<sub>pd</sub> is the total current for all supplies.

- [5]  $I_{DD(PVDD)}$  depends on the overall load at the digital pins.

- [6]  $I_{DD(TVDD)}$  depends on  $V_{DD(TVDD)}$  and the external circuit connected to pins TX1 and TX2.

- [7] During typical circuit operation, the overall current is below 100 mA.

- [8] Typical value using a complementary driver configuration and an antenna matched to 40 Ω between pins TX1 and TX2 at 13.56 MHz.

### 5. Ordering information

#### Table 2.Ordering information

| Type number                        | Package |                                                                                                               |          |  |  |  |

|------------------------------------|---------|---------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                                    | Name    | Description                                                                                                   | Version  |  |  |  |

| MFRC52201HN1/TRAYB <sup>[1]</sup>  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminal; body $5 \times 5 \times 0.85$ mm | SOT617-1 |  |  |  |

| MFRC52201HN1/TRAYBM <sup>[2]</sup> | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminal; body $5 \times 5 \times 0.85$ mm | SOT617-1 |  |  |  |

| MFRC52202HN1/TRAYB[1]              | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminal; body $5 \times 5 \times 0.85$ mm | SOT617-1 |  |  |  |

| MFRC52202HN1/TRAYBM <sup>[2]</sup> | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminal; body $5 \times 5 \times 0.85$ mm | SOT617-1 |  |  |  |

[1] Delivered in one tray.

[2] Delivered in five trays.

**COMPANY PUBLIC**

### 6. Block diagram

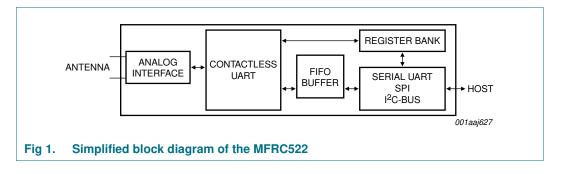

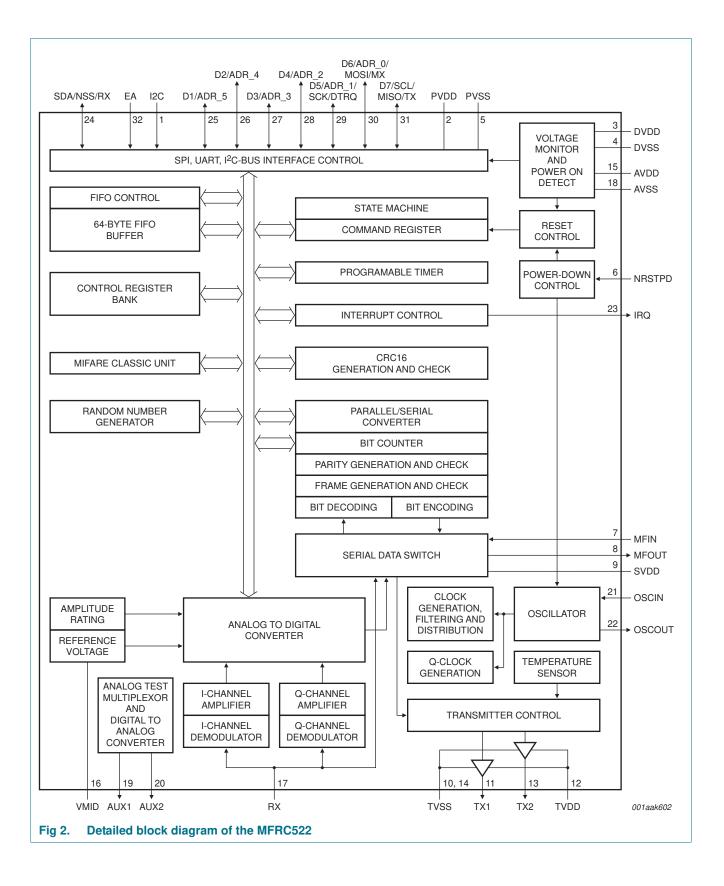

The analog interface handles the modulation and demodulation of the analog signals.

The contactless UART manages the protocol requirements for the communication protocols in cooperation with the host. The FIFO buffer ensures fast and convenient data transfer to and from the host and the contactless UART and vice versa.

Various host interfaces are implemented to meet different customer requirements.

#### Standard performance MIFARE and NTAG frontend

#### Standard performance MIFARE and NTAG frontend

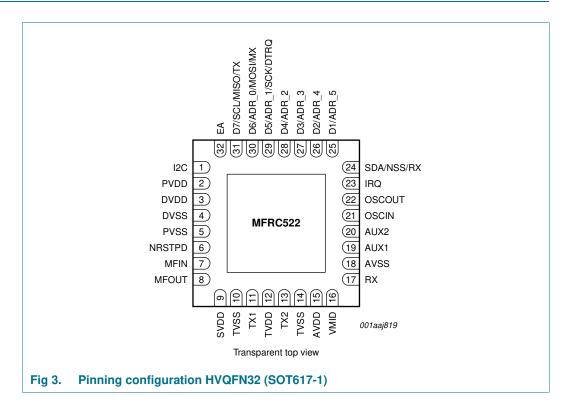

## 7. Pinning information

### 7.1 Pin description

### Table 3. Pin description

| Pin | Symbol | Type <mark>[1]</mark> | Description                                                                                                                                                   |

|-----|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | I2C    |                       | I <sup>2</sup> C-bus enable input <sup>[2]</sup>                                                                                                              |

| 2   | PVDD   | Р                     | pin power supply                                                                                                                                              |

| 3   | DVDD   | Р                     | digital power supply                                                                                                                                          |

| 4   | DVSS   | G                     | digital ground <sup>[3]</sup>                                                                                                                                 |

| 5   | PVSS   | G                     | pin power supply ground                                                                                                                                       |

| 6   | NRSTPD | I                     | reset and power-down input:                                                                                                                                   |

|     |        |                       | power-down: enabled when LOW; internal current sinks are switched off, the oscillator is inhibited and the input pins are disconnected from the outside world |

|     |        |                       | reset: enabled by a positive edge                                                                                                                             |

| 7   | MFIN   | I                     | MIFARE signal input                                                                                                                                           |

| 8   | MFOUT  | 0                     | MIFARE signal output                                                                                                                                          |

| 9   | SVDD   | Р                     | MFIN and MFOUT pin power supply                                                                                                                               |

| 10  | TVSS   | G                     | transmitter output stage 1 ground                                                                                                                             |

| 11  | TX1    | 0                     | transmitter 1 modulated 13.56 MHz energy carrier output                                                                                                       |

| 12  | TVDD   | Р                     | transmitter power supply: supplies the output stage of transmitters 1 and 2                                                                                   |

| 13  | TX2    | 0                     | transmitter 2 modulated 13.56 MHz energy carrier output                                                                                                       |

| 14  | TVSS   | G                     | transmitter output stage 2 ground                                                                                                                             |

| 15  | AVDD   | Р                     | analog power supply                                                                                                                                           |

#### Standard performance MIFARE and NTAG frontend

| Pin | Symbol | Type <sup>[1]</sup> | Description                                                                                                             |

|-----|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| 16  | VMID   | P                   | internal reference voltage                                                                                              |

| 17  | RX     | 1                   | RF signal input                                                                                                         |

| 18  | AVSS   | G                   | analog ground                                                                                                           |

| 19  | AUX1   | 0                   | auxiliary outputs for test purposes                                                                                     |

| 20  | AUX2   | 0                   | auxiliary outputs for test purposes                                                                                     |

| 21  | OSCIN  | I                   | crystal oscillator inverting amplifier input; also the input for an externally generated clock ( $f_{clk}$ = 27.12 MHz) |

| 22  | OSCOUT | 0                   | crystal oscillator inverting amplifier output                                                                           |

| 23  | IRQ    | 0                   | interrupt request output: indicates an interrupt event                                                                  |

| 24  | SDA    | I/O                 | I <sup>2</sup> C-bus serial data line input/output <sup>[2]</sup>                                                       |

|     | NSS    | I                   | SPI signal input <sup>[2]</sup>                                                                                         |

|     | RX     | I                   | UART address input[2]                                                                                                   |

| 25  | D1     | I/O                 | test port <sup>[2]</sup>                                                                                                |

|     | ADR_5  | I/O                 | I <sup>2</sup> C-bus address 5 input <sup>[2]</sup>                                                                     |

| 26  | D2     | I/O                 | test port                                                                                                               |

|     | ADR_4  | I                   | I <sup>2</sup> C-bus address 4 input <sup>[2]</sup>                                                                     |

| 27  | D3     | I/O                 | test port                                                                                                               |

|     | ADR_3  | I                   | I <sup>2</sup> C-bus address 3 input <sup>[2]</sup>                                                                     |

| 28  | D4     | I/O                 | test port                                                                                                               |

|     | ADR_2  | I                   | I <sup>2</sup> C-bus address 2 input <sup>[2]</sup>                                                                     |

| 29  | D5     | I/O                 | test port                                                                                                               |

|     | ADR_1  | I                   | I <sup>2</sup> C-bus address 1 input <sup>[2]</sup>                                                                     |

|     | SCK    | I                   | SPI serial clock input <sup>[2]</sup>                                                                                   |

|     | DTRQ   | 0                   | UART request to send output to microcontroller <sup>[2]</sup>                                                           |

| 30  | D6     | I/O                 | test port                                                                                                               |

|     | ADR_0  | I                   | I <sup>2</sup> C-bus address 0 input <sup>[2]</sup>                                                                     |

|     | MOSI   | I/O                 | SPI master out, slave in <sup>[2]</sup>                                                                                 |

|     | MX     | 0                   | UART output to microcontroller <sup>[2]</sup>                                                                           |

| 31  | D7     | I/O                 | test port                                                                                                               |

|     | SCL    | I/O                 | I <sup>2</sup> C-bus clock input/output <sup>[2]</sup>                                                                  |

|     | MISO   | I/O                 | SPI master in, slave out <sup>[2]</sup>                                                                                 |

|     | ТΧ     | 0                   | UART data output to microcontroller <sup>[2]</sup>                                                                      |

| 32  | EA     | I                   | external address input for coding I <sup>2</sup> C-bus address <sup>[2]</sup>                                           |

[2] The pin functionality of these pins is explained in <u>Section 8.1 "Digital interfaces"</u>.

[3] Connection of heatsink pad on package bottom side is not necessary. Optional connection to pin DVSS is possible.

#### Standard performance MIFARE and NTAG frontend

### 8. Functional description

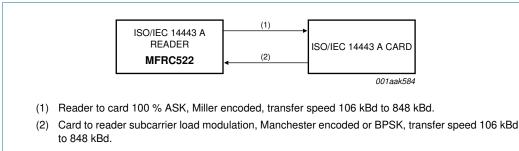

The MFRC522 transmission module supports the Read/Write mode for ISO/IEC 14443 A/MIFARE using various transfer speeds and modulation protocols.

The physical level communication is shown in Figure 5.

Fig 5. ISO/IEC 14443 A/MIFARE Read/Write mode communication diagram

The physical parameters are described in Table 4.

#### Table 4. Communication overview for ISO/IEC 14443 A/MIFARE reader/writer

| Communication                                               | Signal type             | Transfer speed              | Transfer speed              |                             |                             |  |  |  |

|-------------------------------------------------------------|-------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|

| direction                                                   |                         | 106 kBd                     | 212 kBd                     | 424 kBd                     | 848 kBd                     |  |  |  |

| Reader to card (send<br>data from the<br>MFRC522 to a card) | reader side modulation  | 100 % ASK                   | 100 % ASK                   | 100 % ASK                   | 100 % ASK                   |  |  |  |

|                                                             | bit encoding            | modified Miller<br>encoding | modified Miller<br>encoding | modified Miller<br>encoding | modified Miller<br>encoding |  |  |  |

|                                                             | bit length              | 128 (13.56 μs)              | 64 (13.56 μs)               | 32 (13.56 μs)               | 16 (13.56 μs)               |  |  |  |

| Card to reader<br>(MFRC522 receives                         | card side<br>modulation | subcarrier load modulation  | subcarrier load modulation  | subcarrier load modulation  | subcarrier load modulation  |  |  |  |

| data from a card)                                           | subcarrier<br>frequency | 13.56 MHz / 16              |  |  |  |

|                                                             | bit encoding            | Manchester<br>encoding      | BPSK                        | BPSK                        | BPSK                        |  |  |  |

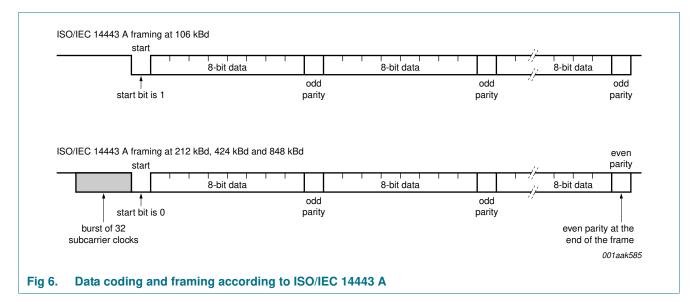

The MFRC522's contactless UART and dedicated external host must manage the complete ISO/IEC 14443 A/MIFARE protocol. <u>Figure 6</u> shows the data coding and framing according to ISO/IEC 14443 A/MIFARE.

### **NXP Semiconductors**

## MFRC522

#### Standard performance MIFARE and NTAG frontend

The internal CRC coprocessor calculates the CRC value based on ISO/IEC 14443 A part 3 and handles parity generation internally according to the transfer speed. Automatic parity generation can be switched off using the MfRxReg register's ParityDisable bit.

### 8.1 Digital interfaces

#### 8.1.1 Automatic microcontroller interface detection

The MFRC522 supports direct interfacing of hosts using SPI, I<sup>2</sup>C-bus or serial UART interfaces. The MFRC522 resets its interface and checks the current host interface type automatically after performing a power-on or hard reset. The MFRC522 identifies the host interface by sensing the logic levels on the control pins after the reset phase. This is done using a combination of fixed pin connections. <u>Table 5</u> shows the different connection configurations.

| Pin | Interface type |              |                            |  |  |  |  |

|-----|----------------|--------------|----------------------------|--|--|--|--|

|     | UART (input)   | SPI (output) | I <sup>2</sup> C-bus (I/O) |  |  |  |  |

| SDA | RX             | NSS          | SDA                        |  |  |  |  |

| I2C | 0              | 0            | 1                          |  |  |  |  |

| EA  | 0              | 1            | EA                         |  |  |  |  |

| D7  | ТХ             | MISO         | SCL                        |  |  |  |  |

| D6  | MX             | MOSI         | ADR_0                      |  |  |  |  |

| D5  | DTRQ           | SCK          | ADR_1                      |  |  |  |  |

| D4  | -              | -            | ADR_2                      |  |  |  |  |

| D3  | -              | -            | ADR_3                      |  |  |  |  |

| D2  | -              | -            | ADR_4                      |  |  |  |  |

| D1  | -              | -            | ADR_5                      |  |  |  |  |

#### Table 5. Connection protocol for detecting different interface types

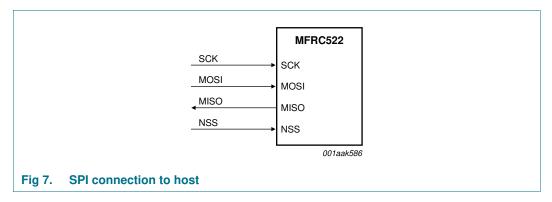

#### 8.1.2 Serial Peripheral Interface

A serial peripheral interface (SPI compatible) is supported to enable high-speed communication to the host. The interface can handle data speeds up to 10 Mbit/s. When communicating with a host, the MFRC522 acts as a slave, receiving data from the external host for register settings, sending and receiving data relevant for RF interface communication.

An interface compatible with SPI enables high-speed serial communication between the MFRC522 and a microcontroller. The implemented interface is in accordance with the SPI standard.

The timing specification is given in <u>Section 14.1 on page 78</u>.

The MFRC522 acts as a slave during SPI communication. The SPI clock signal SCK must be generated by the master. Data communication from the master to the slave uses the MOSI line. The MISO line is used to send data from the MFRC522 to the master.

Data bytes on both MOSI and MISO lines are sent with the MSB first. Data on both MOSI and MISO lines must be stable on the rising edge of the clock and can be changed on the falling edge. Data is provided by the MFRC522 on the falling clock edge and is stable during the rising clock edge.

#### 8.1.2.1 SPI read data

Reading data using SPI requires the byte order shown in <u>Table 6</u> to be used. It is possible to read out up to n-data bytes.

The first byte sent defines both the mode and the address.

| Line | Byte 0    | Byte 1    | Byte 2    | То | Byte n     | Byte n + 1 |

|------|-----------|-----------|-----------|----|------------|------------|

| MOSI | address 0 | address 1 | address 2 |    | address n  | 00         |

| MISO | X[1]      | data 0    | data 1    |    | data n – 1 | data n     |

[1] X = Do not care.

Remark: The MSB must be sent first.

#### 8.1.2.2 SPI write data

To write data to the MFRC522 using SPI requires the byte order shown in <u>Table 7</u>. It is possible to write up to n data bytes by only sending one address byte.

The first send byte defines both the mode and the address byte.

| Table 7. MOSI and MISO | byte o | order |

|------------------------|--------|-------|

|------------------------|--------|-------|

| Line | Byte 0    | Byte 1 | Byte 2 | То | Byte n     | Byte n + 1 |

|------|-----------|--------|--------|----|------------|------------|

| MOSI | address 0 | data 0 | data 1 |    | data n – 1 | data n     |

| MISO | X[1]      | X[1]   | X[1]   |    | X[1]       | X[1]       |

[1] X = Do not care.

Remark: The MSB must be sent first.

#### 8.1.2.3 SPI address byte

The address byte must meet the following format.

The MSB of the first byte defines the mode used. To read data from the MFRC522 the MSB is set to logic 1. To write data to the MFRC522 the MSB must be set to logic 0. Bits 6 to 1 define the address and the LSB is set to logic 0.

#### Table 8. Address byte 0 register; address MOSI

| 7 (MSB)   | 6       | 5 | 4 | 3 | 2 | 1 | 0 (LSB) |

|-----------|---------|---|---|---|---|---|---------|

| 1 = read  | address |   |   |   |   |   | 0       |

| 0 = write |         |   |   |   |   |   |         |

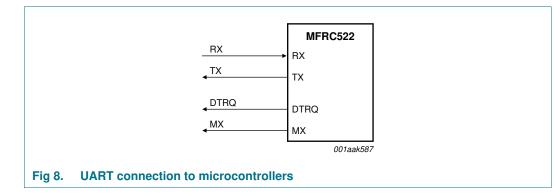

#### 8.1.3 UART interface

#### 8.1.3.1 Connection to a host

**Remark:** Signals DTRQ and MX can be disabled by clearing TestPinEnReg register's RS232LineEn bit.

#### 8.1.3.2 Selectable UART transfer speeds

The internal UART interface is compatible with an RS232 serial interface.

The default transfer speed is 9.6 kBd. To change the transfer speed, the host controller must write a value for the new transfer speed to the SerialSpeedReg register. Bits BR\_T0[2:0] and BR\_T1[4:0] define the factors for setting the transfer speed in the SerialSpeedReg register.

The BR\_T0[2:0] and BR\_T1[4:0] settings are described in <u>Table 9</u>. Examples of different transfer speeds and the relevant register settings are given in <u>Table 10</u>.

| Table 5. Dh_to and Dh_th Settings |         |          |          |          |          |          |          |          |  |

|-----------------------------------|---------|----------|----------|----------|----------|----------|----------|----------|--|

| BR_Tn                             | Bit 0   | Bit 1    | Bit 2    | Bit 3    | Bit 4    | Bit 5    | Bit 6    | Bit 7    |  |

| BR_T0 factor                      | 1       | 1        | 2        | 4        | 8        | 16       | 32       | 64       |  |

| BR_T1 range                       | 1 to 32 | 33 to 64 |  |

#### Table 9. BR\_T0 and BR\_T1 settings

#### Table 10. Selectable UART transfer speeds

| Transfer speed (kBd) | SerialSpeed | IReg value  | Transfer speed accuracy |  |  |

|----------------------|-------------|-------------|-------------------------|--|--|

|                      | Decimal     | Hexadecimal | (%) <mark>[1]</mark>    |  |  |

| 7.2                  | 250         | FAh         | -0.25                   |  |  |

| 9.6                  | 235         | EBh         | 0.32                    |  |  |

| 14.4                 | 218         | DAh         | -0.25                   |  |  |

| 19.2                 | 203         | CBh         | 0.32                    |  |  |

| 38.4                 | 171         | ABh         | 0.32                    |  |  |

| 57.6                 | 154         | 9Ah         | -0.25                   |  |  |

| 115.2                | 122         | 7Ah         | -0.25                   |  |  |

| 128                  | 116         | 74h         | -0.06                   |  |  |

| 230.4                | 90          | 5Ah         | -0.25                   |  |  |

| 460.8                | 58          | 3Ah         | -0.25                   |  |  |

| 921.6                | 28          | 1Ch         | 1.45                    |  |  |

| 1228.8               | 21          | 15h         | 0.32                    |  |  |

[1] The resulting transfer speed error is less than 1.5 % for all described transfer speeds.

The selectable transfer speeds shown in <u>Table 10</u> are calculated according to the following equations:

If BR\_T0[2:0] = 0:

$$transfer \ speed = \frac{27.12 \times 10^6}{(BR_T T 0 + 1)} \tag{1}$$

If BR\_T0[2:0] > 0:

$$transfer speed = \left(\frac{27.12 \times 10^6}{(BR_T T I + 33)}\right)$$

(2)

Remark: Transfer speeds above 1228.8 kBd are not supported.

#### 8.1.3.3 UART framing

#### Table 11. UART framing

| Bit   | Length | Value |

|-------|--------|-------|

| Start | 1-bit  | 0     |

| Data  | 8 bits | data  |

| Stop  | 1-bit  | 1     |

**Remark:** The LSB for data and address bytes must be sent first. No parity bit is used during transmission.

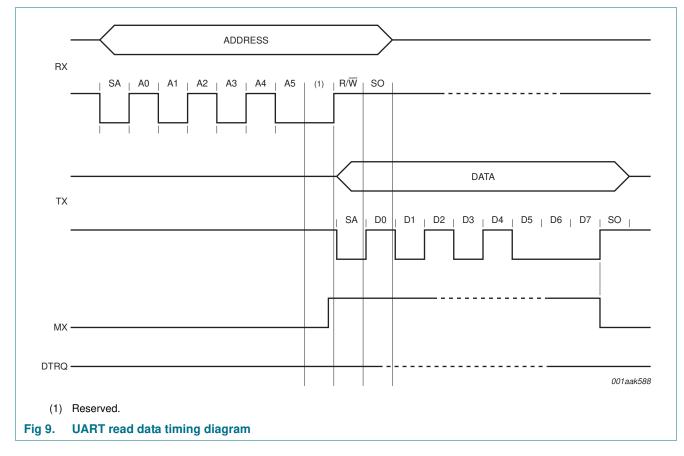

**Read data:** To read data using the UART interface, the flow shown in <u>Table 12</u> must be used. The first byte sent defines both the mode and the address.

#### Table 12. Read data byte order

| P | Pin         | Byte 0  | Byte 1 |

|---|-------------|---------|--------|

| F | RX (pin 24) | address | -      |

| Т | ΓX (pin 31) | -       | data 0 |

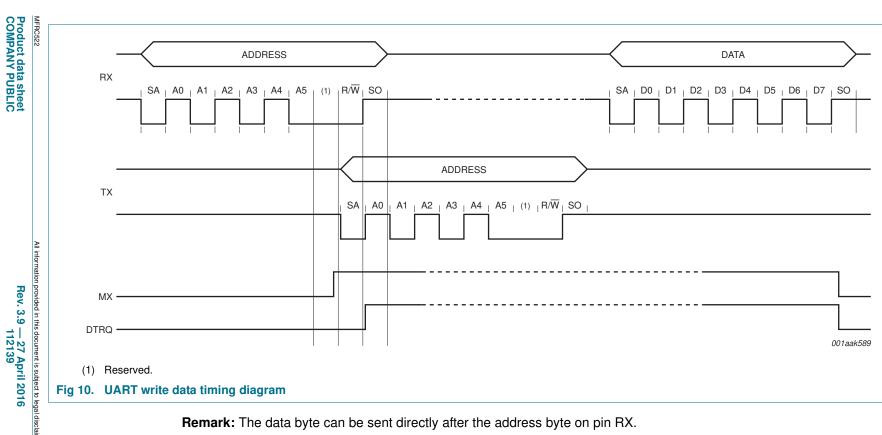

Write data: To write data to the MFRC522 using the UART interface, the structure shown in Table 13 must be used.

The first byte sent defines both the mode and the address.

All information provided in this document is subject to legal disclaimers.

#### Standard performance MIFARE and NTAG frontend

#### Table 13.Write data byte order

| Pin         | Byte 0    | Byte 1    |

|-------------|-----------|-----------|

| RX (pin 24) | address 0 | data 0    |

| TX (pin 31) | -         | address 0 |

NXP Semiconductors

Standard performance MIFARE and NTAG frontend MFRC522

Remark: The data byte can be sent directly after the address byte on pin RX.

Address byte: The address byte has to meet the following format:

The MSB of the first byte sets the mode used. To read data from the MFRC522, the MSB is set to logic 1. To write data to the MFRC522 the MSB is set to logic 0. Bit 6 is reserved for future use, and bits 5 to 0 define the address; see Table 14.

© NXP Semiconductors N.V. 2016. All rights reserved

#### Table 14. Address byte 0 register; address MOSI

| 7 (MSB)               | 6        | 5       | 4 | 3 | 2 | 1 | 0 (LSB) |

|-----------------------|----------|---------|---|---|---|---|---------|

| 1 = read<br>0 = write | reserved | address |   |   |   |   |         |

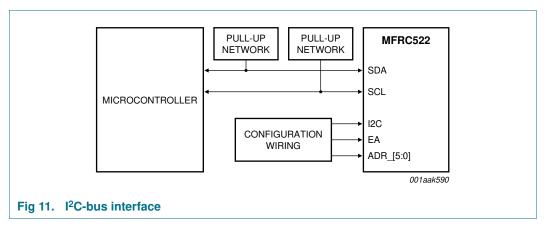

#### 8.1.4 I<sup>2</sup>C-bus interface

An  $l^2$ C-bus (Inter-IC) interface is supported to enable a low-cost, low pin count serial bus interface to the host. The  $l^2$ C-bus interface is implemented according to NXP Semiconductors'  $l^2$ C-bus interface specification, rev. 2.1, January 2000. The interface can only act in Slave mode. Therefore the MFRC522 does not implement clock generation or access arbitration.

The MFRC522 can act either as a slave receiver or slave transmitter in Standard mode, Fast mode and High-speed mode.

SDA is a bidirectional line connected to a positive supply voltage using a current source or a pull-up resistor. Both SDA and SCL lines are set HIGH when data is not transmitted. The MFRC522 has a 3-state output stage to perform the wired-AND function. Data on the I<sup>2</sup>C-bus can be transferred at data rates of up to 100 kBd in Standard mode, up to 400 kBd in Fast mode or up to 3.4 Mbit/s in High-speed mode.

If the I<sup>2</sup>C-bus interface is selected, spike suppression is activated on lines SCL and SDA as defined in the I<sup>2</sup>C-bus interface specification.

See <u>Table 155 on page 79</u> for timing requirements.

**COMPANY PUBLIC**

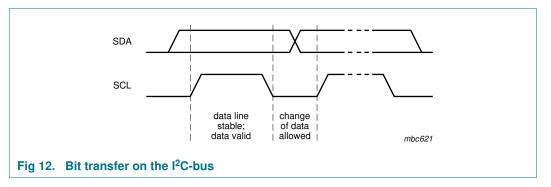

#### 8.1.4.1 Data validity

Data on the SDA line must be stable during the HIGH clock period. The HIGH or LOW state of the data line must only change when the clock signal on SCL is LOW.

#### 8.1.4.2 START and STOP conditions

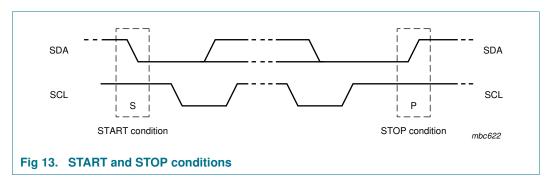

To manage the data transfer on the  $I^2C$ -bus, unique START (S) and STOP (P) conditions are defined.

- A START condition is defined with a HIGH-to-LOW transition on the SDA line while SCL is HIGH.

- A STOP condition is defined with a LOW-to-HIGH transition on the SDA line while SCL is HIGH.

The I<sup>2</sup>C-bus master always generates the START and STOP conditions. The bus is busy after the START condition. The bus is free again a certain time after the STOP condition.

The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. The START (S) and repeated START (Sr) conditions are functionally identical. Therefore, S is used as a generic term to represent both the START (S) and repeated START (Sr) conditions.

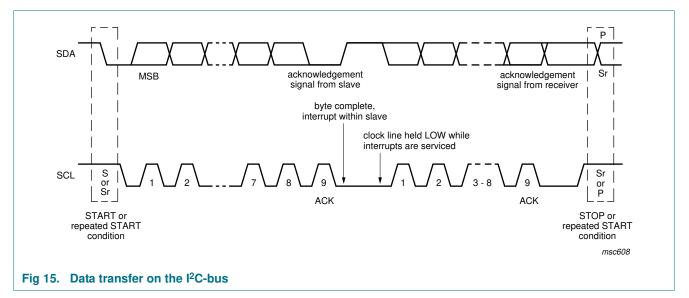

#### 8.1.4.3 Byte format

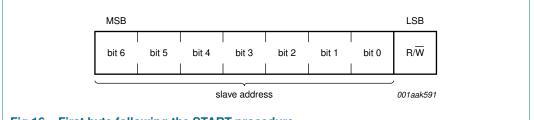

Each byte must be followed by an acknowledge bit. Data is transferred with the MSB first; see Figure 16. The number of transmitted bytes during one data transfer is unrestricted but must meet the read/write cycle format.

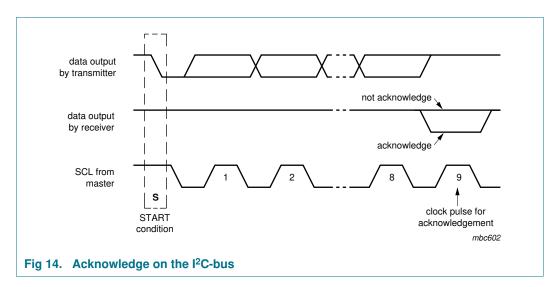

#### 8.1.4.4 Acknowledge

An acknowledge must be sent at the end of one data byte. The acknowledge-related clock pulse is generated by the master. The transmitter of data, either master or slave, releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver pulls down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

The master can then generate either a STOP (P) condition to stop the transfer or a repeated START (Sr) condition to start a new transfer.

A master-receiver indicates the end of data to the slave-transmitter by not generating an acknowledge on the last byte that was clocked out by the slave. The slave-transmitter releases the data line to allow the master to generate a STOP (P) or repeated START (Sr) condition.

#### 8.1.4.5 7-Bit addressing

During the I<sup>2</sup>C-bus address procedure, the first byte after the START condition is used to determine which slave will be selected by the master.

Several address numbers are reserved. During device configuration, the designer must ensure that collisions with these reserved addresses cannot occur. Check the  $l^2C$ -bus specification for a complete list of reserved addresses.

The I<sup>2</sup>C-bus address specification is dependent on the definition of pin EA. Immediately after releasing pin NRSTPD or after a power-on reset, the device defines the I<sup>2</sup>C-bus address according to pin EA.

If pin EA is set LOW, the upper 4 bits of the device bus address are reserved by NXP Semiconductors and set to 0101b for all MFRC522 devices. The remaining 3 bits (ADR\_0, ADR\_1, ADR\_2) of the slave address can be freely configured by the customer to prevent collisions with other I<sup>2</sup>C-bus devices.

If pin EA is set HIGH, ADR\_0 to ADR\_5 can be completely specified at the external pins according to Table 5 on page 9. ADR\_6 is always set to logic 0.

In both modes, the external address coding is latched immediately after releasing the reset condition. Further changes at the used pins are not taken into consideration. Depending on the external wiring, the I<sup>2</sup>C-bus address pins can be used for test signal outputs.

Fig 16. First byte following the START procedure

#### 8.1.4.6 Register write access

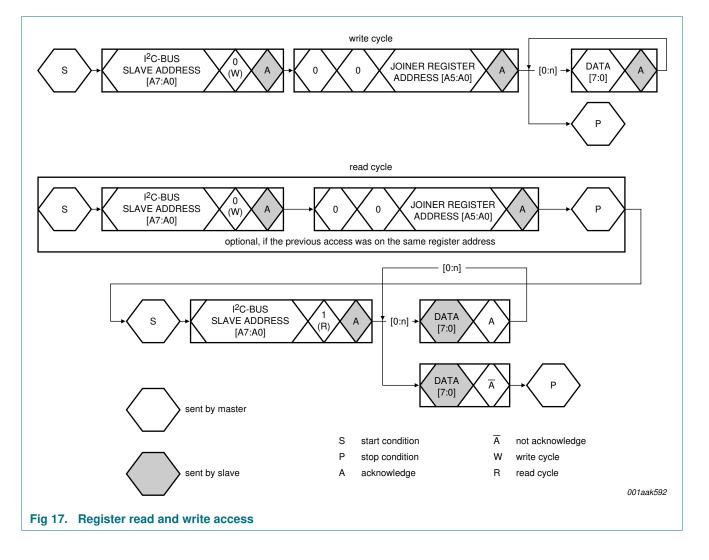

To write data from the host controller using the I<sup>2</sup>C-bus to a specific register in the MFRC522 the following frame format must be used.

- The first byte of a frame indicates the device address according to the I<sup>2</sup>C-bus rules.

- The second byte indicates the register address followed by up to n-data bytes.

In one frame all data bytes are written to the same register address. This enables fast FIFO buffer access. The Read/Write  $(R/\overline{W})$  bit is set to logic 0.

#### 8.1.4.7 Register read access

To read out data from a specific register address in the MFRC522, the host controller must use the following procedure:

- Firstly, a write access to the specific register address must be performed as indicated in the frame that follows

- The first byte of a frame indicates the device address according to the I<sup>2</sup>C-bus rules

- · The second byte indicates the register address. No data bytes are added

- The Read/Write bit is 0

After the write access, read access can start. The host sends the device address of the MFRC522. In response, the MFRC522 sends the content of the read access register. In one frame all data bytes can be read from the same register address. This enables fast FIFO buffer access or register polling.

The Read/Write (R/W) bit is set to logic 1.

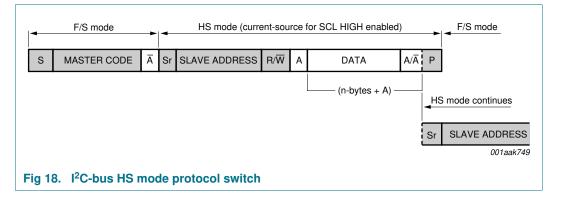

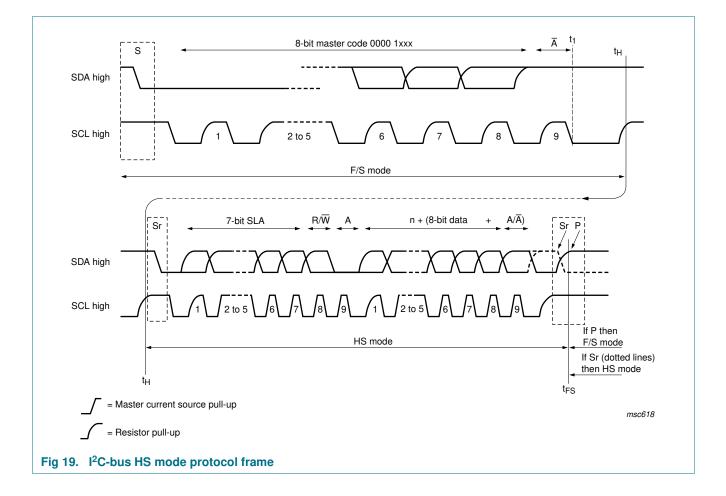

#### 8.1.4.8 High-speed mode

In High-speed mode (HS mode), the device can transfer information at data rates of up to 3.4 Mbit/s, while remaining fully downward-compatible with Fast or Standard mode (F/S mode) for bidirectional communication in a mixed-speed bus system.

#### 8.1.4.9 High-speed transfer

To achieve data rates of up to 3.4 Mbit/s the following improvements have been made to  $I^{2}C$ -bus operation.

- The inputs of the device in HS mode incorporate spike suppression, a Schmitt trigger on the SDA and SCL inputs and different timing constants when compared to F/S mode

- The output buffers of the device in HS mode incorporate slope control of the falling edges of the SDA and SCL signals with different fall times compared to F/S mode

#### 8.1.4.10 Serial data transfer format in HS mode

The HS mode serial data transfer format meets the Standard mode I<sup>2</sup>C-bus specification. HS mode can only start after all of the following conditions (all of which are in F/S mode):

- 1. START condition (S)

- 2. 8-bit master code (00001XXXb)

- 3. Not-acknowledge bit  $(\overline{A})$

When HS mode starts, the active master sends a repeated START condition (Sr) followed by a 7-bit slave address with a R/W bit address and receives an acknowledge bit (A) from the selected MFRC522.

Data transfer continues in HS mode after the next repeated START (Sr), only switching back to F/S mode after a STOP condition (P). To reduce the overhead of the master code, a master links a number of HS mode transfers, separated by repeated START conditions (Sr).

#### Standard performance MIFARE and NTAG frontend

#### 8.1.4.11 Switching between F/S mode and HS mode

After reset and initialization, the MFRC522 is in Fast mode (which is in effect F/S mode as Fast mode is downward-compatible with Standard mode). The connected MFRC522 recognizes the "S 00001XXX A" sequence and switches its internal circuitry from the Fast mode setting to the HS mode setting.

The following actions are taken:

- 1. Adapt the SDA and SCL input filters according to the spike suppression requirement in HS mode.

- 2. Adapt the slope control of the SDA output stages.

It is possible for system configurations that do not have other I<sup>2</sup>C-bus devices involved in the communication to switch to HS mode permanently. This is implemented by setting Status2Reg register's I<sup>2</sup>CForceHS bit to logic 1. In permanent HS mode, the master code is not required to be sent. This is not defined in the specification and must only be used when no other devices are connected on the bus. In addition, spikes on the I<sup>2</sup>C-bus lines must be avoided because of the reduced spike suppression.

#### 8.1.4.12 MFRC522 at lower speed modes

MFRC522 is fully downward-compatible and can be connected to an F/S mode I<sup>2</sup>C-bus system. The device stays in F/S mode and communicates at F/S mode speeds because a master code is not transmitted in this configuration.

**COMPANY PUBLIC**

### 8.2 Analog interface and contactless UART

#### 8.2.1 General

The integrated contactless UART supports the external host online with framing and error checking of the protocol requirements up to 848 kBd. An external circuit can be connected to the communication interface pins MFIN and MFOUT to modulate and demodulate the data.

The contactless UART handles the protocol requirements for the communication protocols in cooperation with the host. Protocol handling generates bit and byte-oriented framing. In addition, it handles error detection such as parity and CRC, based on the various supported contactless communication protocols.

**Remark:** The size and tuning of the antenna and the power supply voltage have an important impact on the achievable operating distance.

#### 8.2.2 TX p-driver

The signal on pins TX1 and TX2 is the 13.56 MHz energy carrier modulated by an envelope signal. It can be used to drive an antenna directly using a few passive components for matching and filtering; see <u>Section 15 on page 81</u>. The signal on pins TX1 and TX2 can be configured using the TxControlReg register; see <u>Section 9.3.2.5 on page 50</u>.

The modulation index can be set by adjusting the impedance of the drivers. The impedance of the p-driver can be configured using registers CWGsPReg and ModGsPReg. The impedance of the n-driver can be configured using the GsNReg register. The modulation index also depends on the antenna design and tuning.

The TxModeReg and TxSelReg registers control the data rate and framing during transmission and the antenna driver setting to support the different requirements at the different modes and transfer speeds.

| Bit<br>Tx1RFEn | Bit<br>Force<br>100ASK | Bit<br>InvTx1RFOn | Bit<br>InvTx1RFOff | Envelope     | Pin<br>TX1 | GSPMos           | GSNMos           | Remarks                                  |                    |

|----------------|------------------------|-------------------|--------------------|--------------|------------|------------------|------------------|------------------------------------------|--------------------|

| 0              | X[1]                   | X[1]              | X[1]               | X[1]         | X[1]       | X <sup>[1]</sup> | X <sup>[1]</sup> | not specified if RF is switched off      |                    |

| 1              | 0 0                    | 0                 | 0                  | X <u>[1]</u> | 0          | RF               | pMod             | nMod                                     | 100 % ASK: pin TX1 |

|                |                        |                   |                    | 1            | RF         | pCW              | nCW              | pulled to logic 0,<br>independent of the |                    |

|                | 0                      | 1                 | X <sup>[1]</sup>   | 0            | RF         | pMod             | nMod             | InvTx1RFOff bit                          |                    |

|                |                        |                   |                    | 1            | RF         | pCW              | nCW              |                                          |                    |

|                | 1                      | 1                 | X <u>[1]</u>       | 0            | 0          | pMod             | nMod             |                                          |                    |

|                |                        |                   |                    | 1            | RF_n       | pCW              | nCW              |                                          |                    |

| Table 15. | <b>Register and bit</b> | settings controlling | the signal on pin TX1 |

|-----------|-------------------------|----------------------|-----------------------|

|-----------|-------------------------|----------------------|-----------------------|

[1] X = Do not care.

#### Standard performance MIFARE and NTAG frontend

| Bit<br>Tx1RFEn | Bit<br>Force<br>100ASK | Bit<br>Tx2CW | Bit<br>InvTx2RFOn | Bit<br>InvTx2RFOff | Envelope         | Pin<br>TX2       | GSPMos       | GSNMos       | Remarks                                   |    |     |     |                          |

|----------------|------------------------|--------------|-------------------|--------------------|------------------|------------------|--------------|--------------|-------------------------------------------|----|-----|-----|--------------------------|

| 0              | X <u>[1]</u>           | X <u>[1]</u> | X[1]              | X[1]               | X[1]             | X <sup>[1]</sup> | X <u>[1]</u> | X <u>[1]</u> | not specified if<br>RF is switched<br>off |    |     |     |                          |

| 1              | 0                      | 0            | 0                 | X[1]               | 0                | RF               | pMod         | nMod         | -                                         |    |     |     |                          |

|                |                        |              |                   |                    | 1                | RF               | pCW          | nCW          | -                                         |    |     |     |                          |

|                |                        |              | 1                 | X[1]               | 0                | RF_n             | pMod         | nMod         | -                                         |    |     |     |                          |

|                |                        |              |                   |                    | 1                | RF_n             | pCW          | nCW          |                                           |    |     |     |                          |

|                |                        | 1            | 0                 | X <sup>[1]</sup>   | X[1]             | RF               | pCW          | nCW          | conductance                               |    |     |     |                          |

|                |                        |              | 1                 | X <u>[1]</u>       | X <sup>[1]</sup> | RF_n             | pCW          | nCW          | always CW for the Tx2CW bit               |    |     |     |                          |

|                | 1                      | 0            | 0                 | X[1]               | 0                | 0                | pMod         | nMod         | 100 % ASK: pin                            |    |     |     |                          |

|                |                        |              |                   |                    |                  |                  |              |              | 1                                         | RF | pCW | nCW | TX2 pulled<br>to logic 0 |

|                |                        |              | 1                 | X[1]               | 0                | 0                | pMod         | nMod         | (independent of                           |    |     |     |                          |

|                |                        |              |                   |                    | 1                | RF_n             | pCW          | nCW the      | the                                       |    |     |     |                          |

|                |                        | 1            | 0                 | X[1]               | X[1]             | RF               | pCW          | nCW          | InvTx2RFOn/Inv<br>Tx2RFOff bits)          |    |     |     |                          |

|                |                        |              | 1                 | X[1]               | X[1]             | RF_n             | pCW          | nCW          |                                           |    |     |     |                          |

#### Table 16. Register and bit settings controlling the signal on pin TX2

[1] X = Do not care.

The following abbreviations have been used in <u>Table 15</u> and <u>Table 16</u>:

- RF: 13.56 MHz clock derived from 27.12 MHz quartz crystal oscillator divided by 2

- RF\_n: inverted 13.56 MHz clock

- GSPMos: conductance, configuration of the PMOS array

- GSNMos: conductance, configuration of the NMOS array

- pCW: PMOS conductance value for continuous wave defined by the CWGsPReg register

- pMod: PMOS conductance value for modulation defined by the ModGsPReg register

- nCW: NMOS conductance value for continuous wave defined by the GsNReg register's CWGsN[3:0] bits

- nMod: NMOS conductance value for modulation defined by the GsNReg register's ModGsN[3:0] bits

- X = do not care.

**Remark:** If only one driver is switched on, the values for CWGsPReg, ModGsPReg and GsNReg registers are used for both drivers.