# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

MIC2592B

#### **Dual-Slot PCI Express Hot-Plug Controller**

### **General Description**

The MIC2592B is a dual-slot power controller supporting the power distribution requirements for Peripheral Component Interconnect Express (PCI Express) Hot-Plug compliant systems. The MIC2592B provides complete power control support for two PCI Express slots, including the 3.3VAUX defined by the PCI Express standards. Support for 12V, 3.3V, and 3.3VAUX supplies is provided including programmable constant-current inrush limiting, voltage supervision, programmable current limit, and circuit breaker functions. These features provide comprehensive system protection and fault isolation. The MIC2592B also incorporates an SMBus interface via which complete status of each slot is provided.

All support documentation can be found on Micrel's web site at www.micrel.com.

#### Features

- Supports two independent PCI Express slots

- SMBus interface for slot power control and status

Voltage-tolerant I/O for compatibility with SMBus 2.0

- systems

- 12V, 3.3V, and 3.3VAUX supplies supported per PCI Express Specification v1.0a

- Intergrated power MOSFETs for 3.3VAUX rails

- Standby operation for Wake-on-LAN applications with low backfeed on Main +12V and +3.3V rails.

- Programmable inrush current limiting

- Active current regulation controls inrush current

- Electronic circuit breaker for each supply to each slot

- High accuracies for both circuit breaker trip points and nuisance trip prevention timers

- Dual level fault detection for quick fault response without nuisance tripping

- Thermal isolation between circuitry for Slot A and Slot B

- Two General Purpose Input pins suitable for interface to logic and switches.

#### **Ordering Information**

| Part Number      |                  | 12V and 3V           | 3.3VAUX       | Package     |

|------------------|------------------|----------------------|---------------|-------------|

| Standard         | Pb-Free          | Fast-Trip Thresholds | Current Limit |             |

| MIC2592B – 2BTQ  | MIC2592B – 2YTQ  | 100mV                | 0.375A        | 48 Pin TQFP |

| MIC2592B - 3BTQ* | MIC2592B - 3YTQ* | 150mV                | 0.375A        | 48 Pin TQFP |

| MIC2592B - 5BTQ* | MIC2592B – 5YTQ* | Disabled             | 0.375A        | 48 Pin TQFP |

\* Contact factory for availability

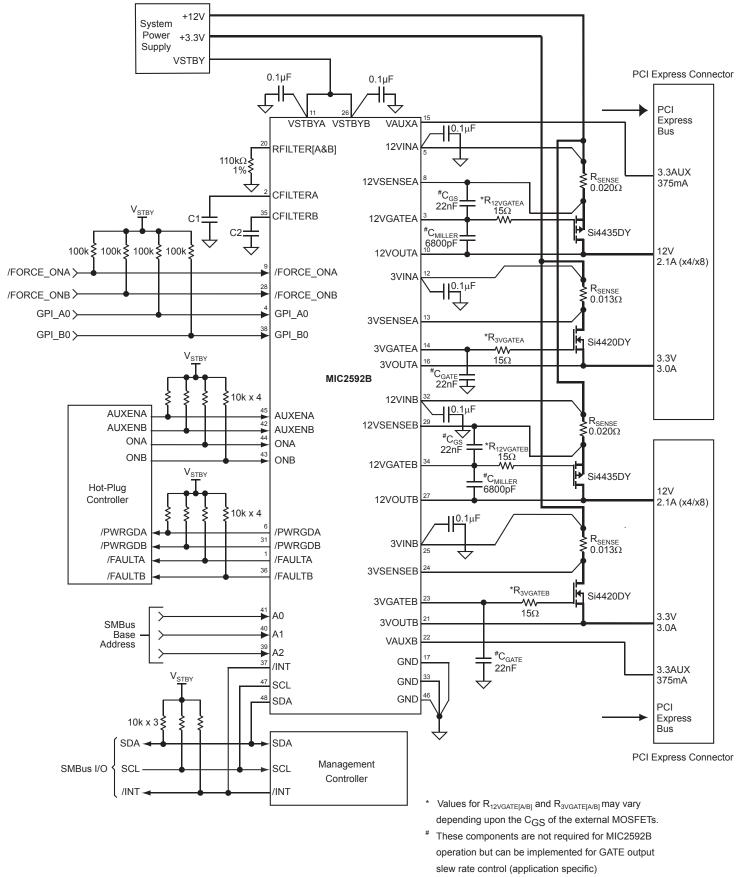

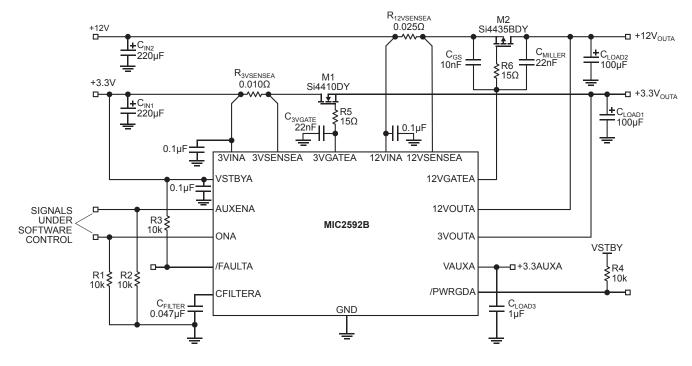

## **Typical Application**

¥ Bold lines indicate high current paths

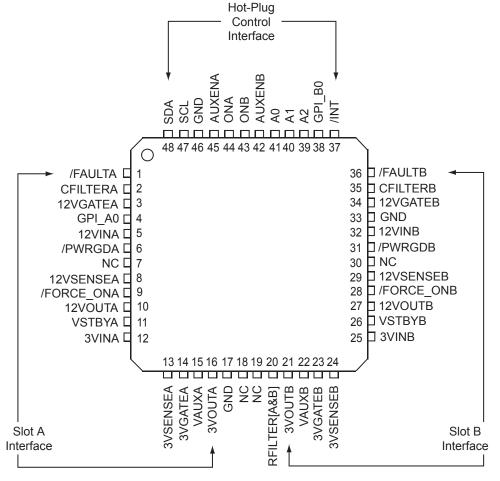

## **Pin Configuration**

48-Pin TQFP

## Pin Description

| Pin Number | Pin Name               | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>32    | 12VINA<br>12VINB       | 12V Supply Power and Sense Inputs [A/B]: Two pins are provided for Kelvin.<br>connection (one for each slot). Pin 5 is the (+) Kelvin-sense connection to<br>the supply side of the sense resistor for 12V Slot A. Pin 32 is the (+) Kelvin<br>sense connection to the supply side of the sense resistor for 12V Slot B.<br>These two pins must ultimately connect to each other as close as possible at<br>the MIC2592B controller in order to eliminate any IR drop between these<br>pins. An undervoltage lockout circuit (UVLO) prevents the switches from<br>turning on while this input is less than its lockout threshold.                                                                                                                                                                         |

| 12<br>25   | 3VINA<br>3VINB         | 3.3V Supply Power and Sense Inputs [A/B]: Two pins are provided for<br>connection (one for each slot). Pin 12 is the (+) Kelvin-sense connection to<br>the supply side of the sense resistor for 3V Slot A. Pin 25 is the (+) Kelvin<br>sense connection to the supply side of the sense resistor for 3V Slot B.<br>These two pins must ultimately connect to each other as close as possible at<br>the MIC2592B controller in order to eliminate any IR drop between these<br>pins. An undervoltage lockout circuit (UVLO) prevents the switches from<br>turning on while this input is less than its lockout threshold.                                                                                                                                                                                 |

| 16<br>21   | 3VOUTA<br>3VOUTB       | 3.3V Power-Good Sense Inputs: Connect to 3.3V[A/B] outputs. Used to monitor the 3.3V output voltages for Power-is-Good status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10<br>27   | 12VOUTA<br>12VOUTB     | 12V Power-Good Sense Inputs: Connect to 12V[A/B] outputs. Used to monitor the 12V output voltages for Power-is-Good status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8<br>29    | 12VSENSEA<br>12VSENSEB | 12V Circuit Breaker Sense Inputs: The current limit thresholds are set<br>by connecting sense resistors between these pins and 12VIN[A/B]. When<br>the current limit threshold of IR = 50mV is reached, the 12VGATE[A/B] pin<br>is modulated to maintain a constant voltage across the sense resistor and<br>therefore a constant current into the load. If the 50mV threshold is exceeded<br>for $t_{FLT}$ , the circuit breaker is tripped and the GATE pin for the affected 12V<br>supply's external MOSFET is immediately pulled high.                                                                                                                                                                                                                                                                |

| 13<br>24   | 3VSENSEA<br>3VSENSEB   | 3V Circuit Breaker Sense Inputs: The current limit thresholds are set by connecting sense resistors between these pins and 3VIN[A/B]. When the current limit threshold of IR = 50mV is reached, the 3VGATE[A/B] pin is modulated to maintain a constant voltage across the sense resistor and therefore a constant current into the load. If the 50mV threshold is exceeded for $t_{FLT}$ , the circuit breaker is tripped and the GATE pin for the affected 3V supply's external MOSFET is immediately pulled low.                                                                                                                                                                                                                                                                                       |

| 3<br>34    | 12VGATEA<br>12VGATEB   | 12V Gate Drive Outputs: Each pin connects to the gate of an external P-Channel MOSFET. During power-up, the $C_{GATE}$ and the $C_{GS}$ of the MOSFETs are connected to a 25µA current sink. This controls the value of dv/dt seen at the source of the MOSFETs.<br>During current limit events, the voltage at this pin is adjusted to maintain constant current through the switch for a period of $t_{FLT}$ . Whenever an overcurrent, thermal shutdown, or input undervoltage fault condition occurs, the GATE pin for the affected slot is immediately brought high. These pins are charged by an internal current source during power-down. Also, the 3V supply for the affected slot is shut-down.                                                                                                 |

| 14<br>23   | 3VGATEA<br>3VGATEB     | $\begin{array}{c} 3V \mbox{ Gate Drive Outputs: Each pin connects to the gate of an external} \\ N-Channel MOSFET. During power-up, the C_{GATE} and the C_{GS} of the MOSFETs are connected to a 25µA current source. This controls the value of dv/dt seen at the source of the MOSFETs, and hence the current flowing into the load capacitance. During current limit events, the voltage at this pin is adjusted to maintain constant current through the switch for a period of t_{FLT}. Whenever an overcurrent, thermal shutdown, or input undervoltage fault condition occurs, the GATE pin for the affected slot is immediately brought low. During powerdown, these pins are discharged by an internal current source. Also, the 12V supply for the affected slot is shut down. \\ \end{array}$ |

| D' N I     | P1 11                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Name                 | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11<br>26   | VSTBYA<br>VSTBYB         | 3.3V Standby Input Voltage: Required to support PCI Express VAUX output<br>Additionally, the SMBus logic and internal registers run off of VSTBY[A/B]<br>to ensure that the chip is accessible during standby modes. A UVLO circuit<br>prevents turn-on of this supply until VSTBY[A/B] rises above its UVLO<br>threshold. Both pins must be externally connected together at the MIC2592<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15<br>22   | VAUXA<br>VAUXB           | 3.3VAUX[A/B] Outputs to PCI Express Card Slots: These outputs connect the 3.3AUX pin of the PCI Express connectors to VSTBY[A/B] via internal 400mΩ MOSFETs. These outputs are current limited and protected agains short-circuit faults.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 44<br>43   | ONA<br>ONB               | Enable Inputs: Rising-edge triggered. Used to enable or disable the MAIN and MAINB (+3.3V and +12V) outputs. The outputs can be switched on by these controls only after the $V_{STBY}$ input supply is valid and stabe (i.e., $t_{PO}$ elapses - See the Electrical Characteristics Table). Taking ON[A/B] low after a fault resets the +12V and/or +3.3V fault latches for the affected slot. Tie these pins to GND if using SMI power control. Also, see pin description for /FAULTA and /FAULTB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 45<br>42   | AUXENA<br>AUXENB         | Enable Inputs: Rising-edge triggered. Used to enable or disable the VAUX[A/B] outputs. The outputs can be switched on by these controls only after the $V_{STBY}$ input supply is valid and stabe (i.e., $t_{POR}$ elapses - See the Electrical Characteristics Table). Taking AUXEN[A/B] low after a fault resets the respective slot's Aux Output Fault Latch. Tie these pins to GND if using SMI power control. Also, see pin description for /FAULTA and /FAULTB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2<br>35    | CFILTERA<br>CFILTERB     | Overcurrent Timers: Capacitors connected between these pins and GND set the duration of $t_{FLT}$ for each slot. The overcurrent filter delay ( $t_{FLT}$ ) is the amount of time for which a slot remains in current limit before its circuit breaker is tripped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6<br>31    | /PWRGDA<br>/PWRGDB       | /PWRGD[A/B] Outputs: Open-drain, active-low. Asserted when a slot has been commanded to turn on and has successfully begun delivering power its respective +12V, +3.3V, and VAUX outputs. Each pin requires an extern pull-up resistor to $V_{STBY}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1<br>36    | /FAULTA<br>/FAULTB       | <ul> <li>/FAULT[A/B] Outputs: Open-drain, active-low. Asserted whenever the circuit breaker trips due to a fault condition (overcurrent, input undervoltage overtemperature). Each pin requires an external pull-up resistor to V<sub>STBY</sub>. Bringing the slot's ON[A/B] pin low resets /FAULT[A/B] if /FAULT[A/B] was asserted in response to a fault condition on one of the slot's MAIN out puts (+12V or +3.3V).</li> <li>/FAULT[A/B] is reset by bringing the slot's AUXEN[A/B] pin low if /FAULT[A/B] was asserted in response to a fault condition on the slot's VAUX output. If a fault condition occurred on both the MAIN and VAUX outputs of the same slot, then both ON[A/B] and AUXEN[A/B] must be brought low to deassert the /FAULT[A/B] output.</li> </ul>                                                                                                                                                                                                                                                                                                  |

| 9<br>28    | /FORCE_ONA<br>/FORCE_ONB | Enable Inputs: Active-low, level-sensitive. Asserting a /FORCE_ON[A/B]<br>input will turn on all three of the respective slot's outputs (+12V, +3.3V, and<br>VAUX), while specifically defeating all protections on those supplies. This<br>explcitly includes all overcurrent and short circuit protections, and on-chip<br>thermal protection for the VAUX[A/B] supplies. Additionally included are the<br>UVLO protections for the +3.3V and +12V main supplies. The<br>/FORCE_ON[A/B] pins do <u>not</u> disable UVLO protection for the VAUX[A/B]<br>supplies. These input pins are intended for diagnostic purposes only.<br>Asserting /FORCE_ON[A/B] will cause the respective slot's /PWRGD[A/B]<br>and /FAULT[A/B] pins to enter their open-drain state. Note that the SMBus<br>register set will continue to reflect the actual state of each slot's supplies.<br>There is a pair of register bits, accessible via the SMBus, which can be set<br>to disable (unconditionally deassert) either or both of the /FORCE_ON[A/B]<br>pins See CNTRL[A/B] Register Bit D[2]. |

| 4<br>38    | GPI_A0<br>GPI_B0         | General Purpose Inputs: The states of these two inputs are available by reading the Common Status Register, Bits [4:5]. If not used, connect each pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Pin Description (continued) Pin Number Pin Name Pin

| Pin Number          | Pin Name       | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 39<br>40<br>41      | A2<br>A1<br>A0 | SMBus Address Select Pins: Connect to ground or leave open in order to program device SMBus base address. These inputs have internal pull-up resistors to VSTBY[A/B].                                                                                                                                                                                                                                                                            |  |

| 48                  | SDA            | SMBus Data: Bidirectional SMBus data line.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 47                  | SCL            | SMBus Clock: Input.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 37                  | /INT           | Interrupt Output: Open-drain, active-low. Asserted whenever a power fault is detected if the INTMSK bit (CS Register Bit D[3]) is a logical "0". This output is cleared by performing an "echo reset" to the appropriate fault bit(s) in the STAT[A/B] and/or CS registers. This pin requires an external pull-up resistor to V <sub>STBY</sub> .                                                                                                |  |

| 17<br>33<br>46      | GND            | 3 Pins, IC Ground Connections: Tie directly to the system's analog GND plane directly at the device.                                                                                                                                                                                                                                                                                                                                             |  |

| 20                  | RFILTER[A&B]   | Connecting this pin to GND through a 110k $\Omega$ , 1% resistor will provide a significant improvement in timeout duration accuracy for slow overcurrent faults on Slot A and Slot B. If left floating (NC), overcurrent timeout duration accuracy is determined by the specification for V <sub>FILTER</sub> and I <sub>FILTER</sub> . Please see the "Circuit Breaker Function" text in the "Functional Description" section for more detail. |  |

| 7<br>18<br>19<br>30 | NC             | Reserved: Make no external connections to these pins.                                                                                                                                                                                                                                                                                                                                                                                            |  |

### Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltages                                                          |

|--------------------------------------------------------------------------|

| 12VIN[A/B]14V                                                            |

| 3VIN[A/B], VSTBY[A/B]7V<br>Any Logic Pin7V –0.5V (min) to 3.6V (max)     |

| Output Current (/FAULT[A/B], /INT, SDA) 10mA                             |

| Power Dissipation Internally Limited                                     |

| Lead Temperature                                                         |

| (IR Reflow, Peak Temperature) 240°C +0°C/–5°C<br>Pb-Free Package (-xYTQ) |

| (IR Reflow, Peak Temperature) 260°C +0°C/–5°C                            |

| Storage Temperature–65°C to +150°C<br>ESD Rating <sup>(3)</sup>          |

## **Operating Ratings**<sup>(2)</sup>

| Supply Voltages                        |                |

|----------------------------------------|----------------|

| 12VIN[A/B]                             | 11.0V to 13.0V |

| 3VIN[A/B]                              | 3.0V to 3.6V   |

| VSTBY[A/B]                             | 3.0V to 3.6V   |

| Ambient Temperature (T <sub>A</sub> )  | 0°C to + 70°C  |

| Junction Temperature (T <sub>J</sub> ) | 125°C          |

| Package Thermal Resistance             |                |

| TQFP $(\theta_{JA})$                   | 56.5°C/W       |

Micrel

## **Electrical Characteristics**<sup>(4)</sup>

$12V_{IN[A/B]} = 12V$ ,  $3V_{IN[A/B]} = 3.3V$ ,  $V_{STBY[A/B]} = 3.3V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted. **Bold** indicates specification applies over the full operating temperature range from 0°C to +70°C.

| Symbol                                                                     | Parameter                                                                    | Condition                                                                                                   | Min                    | Тур                | Мах                | Units          |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--------------------|----------------|

| Power Control                                                              | and Logic Sections                                                           |                                                                                                             |                        |                    |                    |                |

| I <sub>CC12</sub><br>I <sub>CC3.3</sub><br>I <sub>CCSTBY</sub>             | Supply Current                                                               |                                                                                                             |                        | 2.5<br>0.5<br>2.5  | 5<br>1<br>5        | mA<br>mA<br>mA |

| V <sub>UVLO(12V)</sub><br>V <sub>UVLO(3V)</sub><br>V <sub>UVLO(STBY)</sub> | Undervoltage Lockout Thresholds<br>12VIN[A/B]<br>3VIN[A/B]<br>VSTBY[A/B]     | 12V <sub>IN[A/B]</sub> increasing<br>3V <sub>IN[A/B]</sub> increasing<br>V <sub>STBY[A/B]</sub> increasing  | 8<br>2.2<br>2.8        | 9<br>2.5<br>2.9    | 10<br>2.75<br>3.0  | V<br>V<br>V    |

| V <sub>HYSUV</sub>                                                         | Undervoltage Lockout Hysteresis<br>12V <sub>IN</sub> , 3V <sub>IN</sub>      |                                                                                                             |                        | 180                |                    | mV             |

| V <sub>HYSSTBY</sub>                                                       | Undervoltage Lockout Hysteresis<br>V <sub>STBY[A/B]</sub>                    |                                                                                                             |                        | 50                 |                    | mV             |

| V <sub>UVTH(12V)</sub><br>V <sub>UVTH(3V)</sub><br>V <sub>UVTH(VAUX)</sub> | Power-Good Undervoltage Thresholds<br>12VOUT[A/B]<br>3VOUT[A/B]<br>VAUX[A/B] | 12V <sub>OUT[A/B]</sub> decreasing<br>3V <sub>OUT[A/B]</sub> decreasing<br>V <sub>AUX[A/B]</sub> decreasing | 10.2<br>2.7<br>2.7     | 10.5<br>2.8<br>2.8 | 10.8<br>2.9<br>2.9 | V<br>V<br>V    |

| V <sub>HYSPG</sub>                                                         | Power-Good Detect Hysteresis                                                 |                                                                                                             |                        | 30                 | l –                | mV             |

| V <sub>GATE(12V)</sub>                                                     | 12VGATE Voltage                                                              |                                                                                                             | 0                      |                    | 1.5                | V              |

| IGATE(12VSINK)                                                             | 12VGATE Sink Current                                                         | Start Cycle                                                                                                 | 15                     | 25                 | 35                 | μA             |

| GATE(12VPULLUP)                                                            | 12VGATE Pull-up Current (Fault Off)                                          | Any fault condition<br>$(V_{DD} - V_{GATE}) = 2.5V$                                                         | -20                    |                    |                    | mA             |

| V <sub>GATE(3V)</sub>                                                      | 3VGATE Voltage                                                               |                                                                                                             | 12V <sub>IN</sub> –1.5 |                    | 12V <sub>IN</sub>  | V              |

| IGATE(3VCHARGE)                                                            | 3VGATE Charge Current                                                        | Start Cycle                                                                                                 | 15                     | 25                 | 35                 | μA             |

| GATE(3VSINK)                                                               | 3VGATE Sink Current (Fault Off)                                              | Any fault condition<br>V <sub>GATE</sub> = 2.5V                                                             | 40                     |                    |                    | mA             |

| CFILTER[A/B]                                                               | Overcurrent Delay Time, Pin 20 (RFIL                                         | TER[A&B]) Floating or NC                                                                                    |                        |                    |                    |                |

| V <sub>FILTER</sub> | CFILTER[A/B] Threshold Voltage                                                                                               |                                                                                                | 1.20 | 1.25 | 1.30 | V  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|----|

| I <sub>FILTER</sub> | $CFILTER[A/B] Charging Current$ $Delay(ms) = \frac{C_{FILTER}(\mu F) \times V_{FILTER}(V)}{I_{FILTER}(\mu A)} \times 10^{3}$ | $V_{12VIN} - V_{12VSENSE} > V_{THILIMIT}$<br>and/or<br>$V_{3VIN} - V_{3VSENSE} > V_{THILIMIT}$ | 1.80 | 2.5  | 5.0  | μA |

7

Notes:

1. Exceeding measurements given within the "Absolute Maximum Ratings" section may damage the device.

2. The device is not guaranteed to function outside of the measurements given in the "Operating Ratings" section.

3. Devices are ESD sensitive. Employ proper handling precautions. The human body model is  $1.5k\Omega$  in series with 100pF.

4. Specification for packaged product only.

| Symbol                       | Parameter                                                                                                                 | Condition                                                                                                                               | Min       | Тур                    | Max             | Units    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-----------------|----------|

| C <sub>FILTER</sub> Overcu   | urrent DelayTime, Pin 20 grounded thr                                                                                     | ough RFILTER[A&B] = 110 kΩ, 1%                                                                                                          |           |                        |                 | 1        |

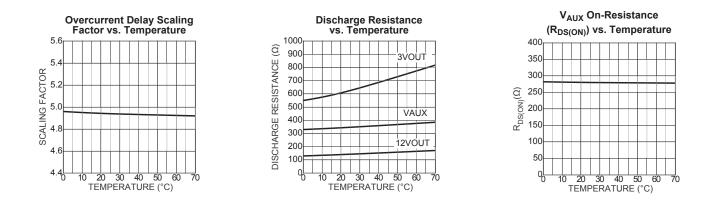

| SF                           | C <sub>FILTER</sub> Overcurrent Delay<br>Scaling Factor<br>Delay(ms)=C <sub>FILTER</sub> (μF)×R <sub>FILTER</sub> (kΩ)×SF | V <sub>12VIN</sub> – V <sub>12VSENSE</sub> > V <sub>THILIMIT</sub><br>and/or                                                            | 4.4       | 5                      | 5.6             |          |

| V <sub>THILIMIT</sub>        | Current Limit Threshold Voltages<br>12V[A/B] supplies<br>3.3V[A/B] supplies                                               | V <sub>12VIN</sub> – V <sub>12VSENSE</sub><br>V <sub>3VIN</sub> – V <sub>3VSENSE</sub>                                                  | 45<br>45  | 50<br>50               | <u>55</u><br>55 | mV<br>mV |

| V THFAST                     | 12VOUT[A/B] and 3VOUT[A/B]<br>Fast-Trip Threshold Voltages                                                                | V12VIN - V12VSENSE         MIC2592B-2BTQ           V3VIN - V3VSENSE         MIC2592B-3BTQ           MIC2592B-5BTQ         MIC2592B-5BTQ | 90<br>135 | 100<br>150<br>Disabled | 110<br>165      | mV<br>mV |

| 12VSENSE[A/B]                | 12VSENSE[A/B] Input current                                                                                               | р И<br> <br>                                                                                                                            |           | 0.35                   |                 | μA       |

| 3VSENSE[A/B]                 | 3VSENSE[A/B] Input current                                                                                                |                                                                                                                                         |           | 0.35                   |                 | μA       |

| V <sub>IL</sub>              | LOW-Level Input Voltage<br>ON[A/B], AUXEN[A/B], GPI_[A0/B0],<br>/FORCE_ON[A/B]                                            |                                                                                                                                         | -0.5      |                        | 0.8             | V        |

| V <sub>OL</sub>              | Output LOW Voltage<br>/FAULT[A/B], /PWRGD[A/B],<br>/INT, SDA                                                              | I <sub>OL</sub> = 3mA                                                                                                                   |           |                        | 0.4             | V        |

| V <sub>IH</sub>              | HIGH-Level Input Voltage<br>ON[A/B], AUXEN[A/B], GPI_[A0/B0],<br>/FORCE_ON[A/B], A[0-2], SCL, SDA                         |                                                                                                                                         | 2.1       |                        | 3.6             | V        |

| R <sub>PULLUP(A0 - A2)</sub> | Internal Pull-ups from A[0-2] to V <sub>STBY[A/B]</sub>                                                                   |                                                                                                                                         |           | 40                     |                 | kΩ       |

| LKG,OFF(12VIN[A/B])          | 12VIN[A/B] Input leakage current<br>12VIN[A/B] = OFF; 3VIN[A/B] = OFF                                                     | V <sub>STBY</sub> = VSTBY[A/B] = +3.3V,                                                                                                 |           | 1                      |                 | μA       |

| LKG,OFF(3VIN[A/B])           | 3VIN[A/B] Input leakage current<br>3VIN[A/B] = OFF; 12VIN[A/B] = OFF                                                      | V <sub>STBY</sub> = VSTBY[A/B] = +3.3V,                                                                                                 |           | 1                      |                 | μA       |

| l <sub>IL</sub>              | Input Leakage Current<br>SCL, ON[A/B], AUXEN[A/B],<br>/FORCE_ON[A/B]                                                      |                                                                                                                                         |           |                        | ±5              | μA       |

| l<br>LKG(OFF)                | Off-State Leakage Current<br>/FAULT[A/B], /PWRGD[A/B],<br>/INT, SDA, GPI_[A0/B0]                                          | GPI_[A0/B0]: I <sub>LKG</sub> for these two pins<br>measured with V <sub>AUX</sub> OFF                                                  |           |                        | ±5              | μA       |

| T <sub>OV</sub>              | Overtemperature Shutdown and Reset                                                                                        | T <sub>J</sub> increasing, each slot <sup>(6)</sup>                                                                                     |           | 140                    |                 | °C       |

|                              | Thresholds, with overcurrent on slot                                                                                      | T <sub>J</sub> decreasing, each slot <sup>(6)</sup>                                                                                     |           | 130                    |                 | °C       |

|                              | Overtemperature Shutdown and<br>Reset Thresholds, all other conditions<br>(all outputs will latch OFF)                    | T <sub>J</sub> increasing, both slots <sup>(6)</sup><br>T <sub>J</sub> decreasing, both slots <sup>(6)</sup>                            |           | 160<br>150             |                 | °C<br>℃  |

| R <sub>DS(AUX)</sub>         | Output MOSFET Resistance<br>VAUX[A/B] MOSFET                                                                              | I <sub>DS</sub> = 375mA, T <sub>J</sub> = 125°C                                                                                         |           |                        | 400             | mΩ       |

| V <sub>OFF(VAUX)</sub>       | Off-State Output Offset Voltage<br>V <sub>AUX[A/B]</sub>                                                                  | V <sub>AUX[A/B]</sub> = Off, T <sub>J</sub> = 125°C                                                                                     |           |                        | 50              | mV       |

Notes:

5. Specification for packaged product only.

6. Parameters guaranteed by design. Not 100% production tested.

| Symbol                                                                  | Parameter                                                              | Condition                                                                                                                  | Min                                           | Тур                | Max               | Units       |

|-------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|-------------------|-------------|

| I <sub>AUX(THRESH)</sub>                                                | Auxiliary Output Current Limit<br>Threshold (Figure 4)                 | Current which must be drawn from V <sub>AUX</sub> to register as a fault                                                   |                                               | 0.84               |                   | A           |

| I <sub>SC(TRAN)</sub>                                                   | Maximum Transient Short Circuit                                        | V <sub>AUX</sub> Enabled, then Grounded                                                                                    | $I_{MAX} = \frac{V_{STBY[A/B]}}{R_{DS(AUX)}}$ |                    | 3Y[A/B]<br>6(AUX) | A           |

| I <sub>LIM(AUX)</sub>                                                   | Regulated Current after Transient                                      | From end of $I_{SC(TRAN)}$ to $C_{FILTER}$ time-out                                                                        | 0.375                                         | 0.7                | 1.35              | Α           |

| R <sub>DIS(12V)</sub><br>R <sub>DIS(3V)</sub><br>R <sub>DIS(VAUX)</sub> | Output Discharge Resistance<br>12VOUT[A/B]<br>3VOUT[A/B]<br>3VAUX[A/B] | $12V_{OUT[A/B]} = 6.0V$<br>$3V_{OUT[A/B]} = 1.65V$<br>$3V_{AUX[A/B]} = 1.65V$                                              |                                               | 1600<br>150<br>430 |                   | Ω<br>Ω<br>Ω |

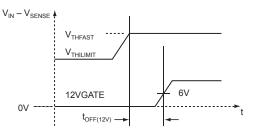

| t <sub>OFF(12V)</sub>                                                   | 12V Current Limit Response Time<br>(Figure 2)                          | MIC2592B-2BTQ<br>C <sub>GATE</sub> = 25pF<br>V <sub>IN</sub> –V <sub>SENSE</sub> = 140mV                                   |                                               | 1                  | 2.0               | μs          |

| t <sub>OFF(3V)</sub>                                                    | 3.3V Current Limit Response Time<br>(Figure 3)                         | $ \begin{array}{l} MIC2592B-2BTQ \\ C_{GATE} &= 25pF \\ V_{IN} - V_{SENSE} &= 140mV^{(8)} \end{array} $                    |                                               | 1                  | 2.0               | μs          |

| t <sub>SC(TRAN)</sub>                                                   | VAUX[A/B] Current Limit Response<br>Time (Figure 5)                    | $V_{AUX[A/B]} = 0V, V_{STBYA} = V_{STBYB} = +3.3V$                                                                         |                                               | 2.5                | 5                 | μs          |

| tprop(12VFAULT)                                                         | Delay from 12V[A/B] Overcurrent<br>Limit to /FAULT output              | $MIC2592B-2BTQ$ $C_{FILTER} = 0$ $V_{IN} - V_{SENSE} = 140 \text{mV}^{(8)}$                                                |                                               | 1                  |                   | μs          |

| tprop(3vfault)                                                          | Delay from 3V[A/B] Overcurrent<br>Limit to /FAULT[A/B] Output          | $MIC2592B-2BTQ$ $C_{FILTER} = 0$ $V_{IN} - V_{SENSE} = 140 \text{mV}^{(8)}$                                                |                                               | 1                  |                   | μs          |

| t <sub>PROP(VAUXFAULT)</sub>                                            | Delay from VAUX[A/B] Overcurrent                                       | MIC2592B-2BTQ<br>limit to /FAULT[A/B] output<br>C <sub>FILTER</sub> = 0<br>V <sub>AUX</sub> Output Grounded <sup>(8)</sup> |                                               | 1                  |                   | μs          |

| t <sub>W</sub>                                                          | ON[A/B], AUXEN[A/B] Pulse Width                                        | Note 8                                                                                                                     |                                               | 100                |                   | ns          |

| t <sub>POR</sub>                                                        | MIC2592B Power-On Reset Time<br>after VSTBY[A/B] becomes valid         | Note 8                                                                                                                     |                                               | 250                |                   | μs          |

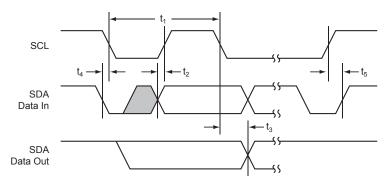

| SMBus Timing                                                            | l .                                                                    |                                                                                                                            |                                               |                    |                   |             |

| t <sub>1</sub>                                                          | SCL (clock) period                                                     | Figure 1                                                                                                                   | 2.5                                           |                    |                   | μs          |

| t <sub>2</sub>                                                          | Data In setup time to SCL HIGH                                         | Figure 1                                                                                                                   | 100                                           |                    |                   | ns          |

| t <sub>3</sub>                                                          | Data Out stable after SCL LOW                                          | Figure 1                                                                                                                   | 300                                           |                    |                   | ns          |

| t <sub>4</sub>                                                          | Data LOW setup time to SCL LOW                                         | Start condition, Figure 1                                                                                                  | 100                                           |                    |                   | ns          |

| t <sub>5</sub>                                                          | Data HIGH hold time after SCL HIGH                                     | Stop condition, Figure 1                                                                                                   | 100                                           |                    |                   | ns          |

Notes:

7. Specification for packaged product only.

8. Parameters guaranteed by design. Not 100% production tested.

## **Timing Diagrams**

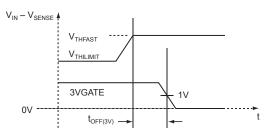

Figure 2. 12V Current Limit Response Timing

Figure 3. 3V Current Limit Response Timing

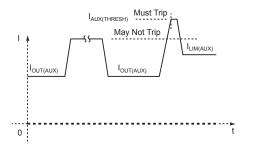

Figure 4. VAUX Current Limit Threshold

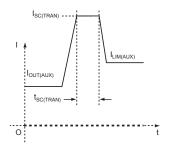

Figure 5. VAUX Current Limit Response Timing

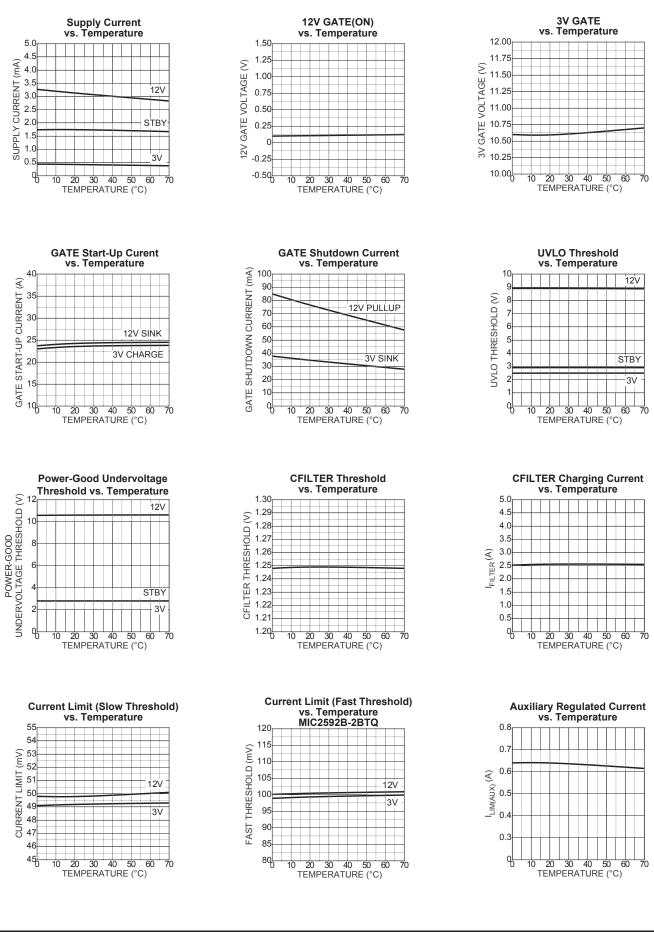

### **Typical Characteristics**

## **Typical Characteristics (cont.)**

**Test Circuit**

(Additional pins omitted for clarity - Slot A shown only)

#### **MIC2592B Test Circuit**

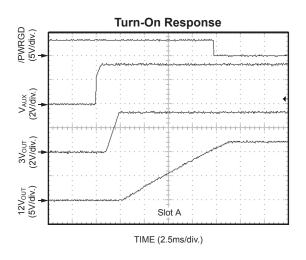

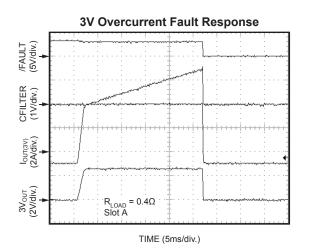

## **Functional Characteristics**

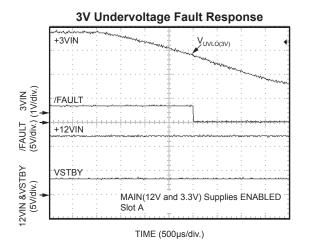

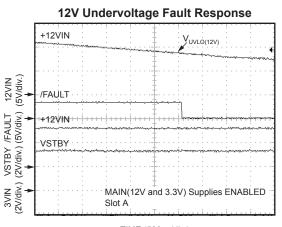

12V Overcurrent Fault Response

SV Ouput Discharge Response

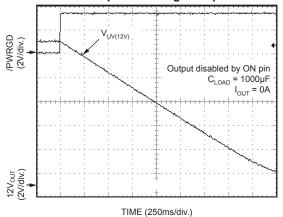

12V Ouput Discharge Response

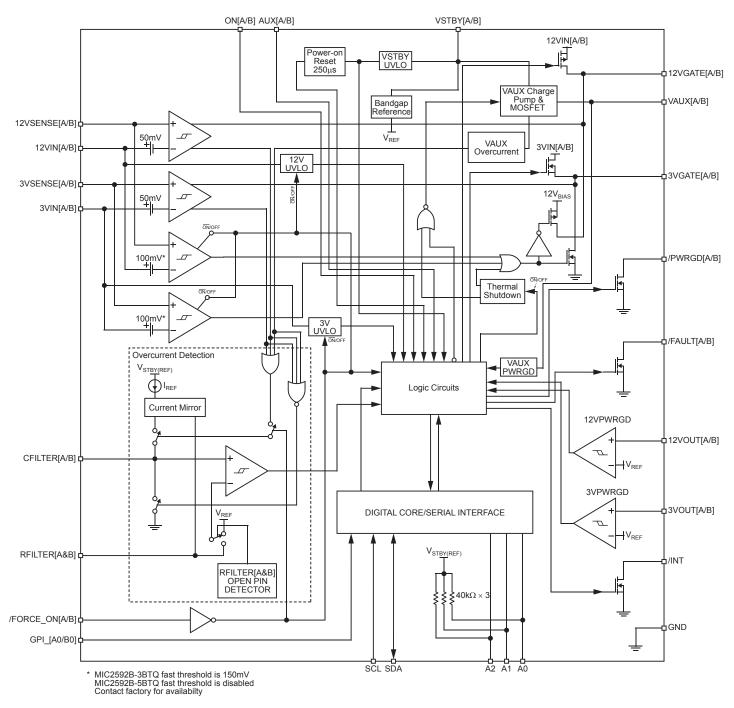

## **Functional Block Diagram**

MIC2592B Block Diagram

## **Functional Description**

#### **Hot Swap Insertion**

When circuit boards are inserted into systems carrying live supply voltages ("hot-plugged"), high inrush currents often result due to the charging of bulk capacitance that resides across the circuit board's supply pins. This transient inrush current can cause the system's supply voltages to temporarily go out of regulation, causing data loss or system lock-up. In more extreme cases, the transients occurring during a hotplug event may cause permanent damage to connectors or on-board components.

The MIC2592B addresses these issues by limiting the inrush currents to the load (PCI Express Board), and thereby controlling the rate at which the load's circuits turn-on. In addition to this inrush current control, the MIC2592B offers input and output voltage supervisory functions and current limiting to provide robust protection for both the system and circuit board.

#### System Interface

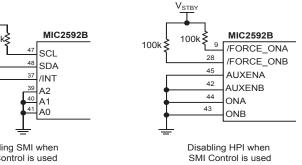

The MIC2592B employs two system interfaces: the hardware Hot-Plug Interface (HPI) and the System Management Interface (SMI). The HPI includes ON[A/B], AUXEN[A/B], as well as /FAULT[A/B]; the SMI consists of SDA, SCL, and /INT, whose signals conform to the levels and timing of the SMBus specification. The MIC2592B can be operated exclusively from the SMI, or can employ the HPI for power control while continuing to use the SMI for access to all but the power control registers.

In addition to the basic power control features of the MIC2592B accessible by the HPI, the SMI also gives the host access to the following information from the part:

- Fault conditions occurring on each supply.

- · GPI [A0/B0] pin status

When using the System Management Interface for power control, do not use the Hot-Plug Interface. Conversely, when using the Hot-Plug Interface for power control, do not execute power control commands over the System Management Interface bus (all other register accesses via the SMI bus remain permissible while in the HPI control mode). When utilizing the SMI exclusively, the HPI input pins (ON[A/B], AUXEN[A/B], and /FORCE\_ON[A/B]) should be configured as shown below in Figure 6 (Disabling HPI when SMI control is used). This configuration safeguards the power slots in the event that the SMBus communication link is disconnected for any reason.

/IN1

V<sub>STB1</sub> MIC2592B 100k§ 100k 9 100k SCL 28 SDA 45 /INT 42 A2 44 A1 ONA

> Disabling SMI when HPI Control is used

#### **Power Stability and Power-On Reset**

The MIC2592B utilizes VSTBY[A/B] as the main supply input source. VSTBY[A/B] is required for proper operation of the MIC2592B's SMBus and registers and must be applied at all times. To ensure that the MIC2592B controller operates properly, the V<sub>STBY</sub> input must be stable and remain above the undervoltage lockout (UVLO) threshold once applied. Sufficient input bulk capacitance should be used to prevent the supply from "drooping", causing VSTBY[A/B] to fall below the UVLO threshold. Also, decoupling capacitors should be placed at each of the MIC2592B inputs in order to filter high frequency noise transients.

V<sub>STBY</sub> must be the first supply input applied followed by the MAIN supply inputs of 12V<sub>IN</sub> and 3V<sub>IN</sub>. A Power-On Reset (POR) cycle is initiated after VSTBY[A/B] rises above its UVLO threshold and remains valid at that voltage for 250 µs. All internal registers are cleared after POR. If VSTBY[A/B] is recycled, the MIC2592B enters a new power-on-reset cycle. The SMBus is ready for access at the end of the POR cycle (250µs after VSTBY[A/B] is valid). During t<sub>POR</sub>, all outputs remain off. In most applications, the total POR interval will consist of the time required to charge the V<sub>STBY</sub> input (bypass) capacitance to the UVLO threshold plus the internal  $t_{POR}$ . The following equation is used to approximate the total POR interval:

$$t_{\text{POR\_TOTAL}(\mu S)} = \left\{ \left\lceil \frac{\left(C_{\text{STBY}(\mu F)} \times V_{\text{ULVO}(\text{STBY})}\right)}{I_{\text{CHARGE}(\text{STBY})}(A)} \right\rceil \times 10^{-6} \right\} + t_{\text{POR}}(\mu S)$$

where  $C_{STBY}$  is the  $V_{STBY}$  input bulk bypass capacitance and  $I_{\text{CHARGE}(\text{STBY})}$  is the current supplied by the  $V_{\text{STBY}}$  source to charge the capacitance.

#### **Power-Up Cycle**

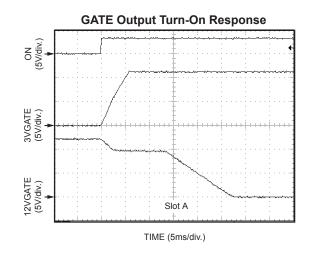

#### Enabling the GATE output

When a slot's MAIN supplies are off, the 12VGATE pin is held high with an internal pull-up. Similarly, the 3VGATE pin is internally held low. When the MAIN supplies of the MIC2592B are enabled by asserting ON[A/B], the 3VGATE[A/B] and 12VGATE[A/B] pins are each connected to a constant current supply. These supplies are each nominally 25µA. For a slot's 3VGATE pin, this is a current source; for the 12VGATE pin, this is a current sink.

Figure 6. Input Pin Configuration for Disabling HPI/SMI Control

#### Inrush Current and Load Dominated Start-up

The expected maximum inrush current can be calculated by using the following equation:

$$\mathsf{INRUSH} \cong \left| \mathsf{I}_{\mathsf{GATE}} \right| \times \frac{\mathsf{C}_{\mathsf{LOAD}}}{\mathsf{C}_{\mathsf{GATE}}} \cong 25 \mu \mathsf{A} \times \frac{\mathsf{C}_{\mathsf{LOAD}}}{\mathsf{C}_{\mathsf{GATE}}}$$

where  $|I_{GATE}|$  is the GATE pin current,  $I_{GATE(3VCHARGE)}$ or  $I_{GATE(12VSINK)}$ ,  $C_{LOAD}$  is the load capacitance, and  $C_{GATE}$  is the total GATE capacitance ( $C_{ISS}$  of the external MOSFET and any external capacitance connected from the GATE output pin to the GATE reference – GND or source).

For the 3.3V outputs and 12V outputs (if no external 12VGATE output capacitors are implemented), the following equation is used to determine the output slew rate.

$$dV_{OUT} / dt = \frac{I_{LIM(3V/12V)}}{C_{LOAD(3V/12V)}}$$

Consequently, the overcurrent timer delay must be programmed to exceed the time it will take to charge the output load to the input rail voltage level.

#### MAIN Outputs (Start-up Delay and Slew-Rate Control)

The 3.3V outputs act as source followers. In this mode of operation,  $V_{SOURCE} = [V_{GATE} - V_{TH(ON)}]$  until the associated output reaches 3.3V. The voltage on the gate of the MOSFET will then continue to rise until it reaches 12V, which ensures minimum  $R_{DS(ON)}$ . Note that a delay exists between the ON command to a slot and the appearance of voltage at the slot's 3.3V output. This delay is the time required to charge the 3VGATE output up to the threshold voltage of the external MOSFET (typically about 3V).

$$t_{3VDLY} = \frac{\left(C_{GATE} \times V_{GS(TH)}\right)}{I_{GATE(3VCHARGE)}}$$

The source (output) side of the external MOSFET will reach the drain voltage in a time given by:

$$t_{3V(SOURCE_DRAIN)} = t_{3VDLY} + \frac{\left(C_{LOAD} \times V_{DRAIN}\right)}{I_{LIM(3V)}}$$

For the 12V outputs, each MOSFET is configured as a Miller integrator (by virtue of  $C_{MILLER}$ , which is connected between the MOSFET's gate and drain). In this configuration, the feedback action from drain to gate of the MOSFET causes the voltage at the drain of the MOSFET to slew in a linear fashion at a rate which satisfies the following equation:

$$dv / dt(12V) = -\left(\frac{I_{GATE}}{C_{MILLER}}\right)$$

A delay exists between the ON command to a slot and the appearance of voltage at the slot's 12V output. For a slot's 12V output, that delay is given by the time required for the capacitor from the gate of the MOSFET to its source (typically five times the value of  $C_{\rm MILLER}$ ) to charge to the threshold voltage of the MOSFET (typically about 3V). In this instance, the delay before the output voltage starts ramping can be approximated by:

$$_{2VDLY} \cong \frac{\left(C_{GATE(TOTAL)} \times V_{GS(TH)}\right)}{\left|I_{GATE}\right|}$$

where  $C_{GATE(TOTAL)}$  is the sum of the  $C_{GS}$  of the external MOSFET, any external capacitance from the GATE output of the MIC2592B to the source of the MOSFET, and  $C_{MILLER}$  (external, if used).

Table 1 approximates the output slew-rate for various values of  $C_{GATE}$  when start-up is dominated by GATE capacitance (external  $C_{GATE}$  from GATE pin to ground plus  $C_{GS}$  of the external MOSFET for the 3.3V rail;  $C_{MILLER}$  for the 12V rail).

| I <sub>GATE</sub>   = 25µA               |              |  |  |

|------------------------------------------|--------------|--|--|

| C <sub>GATE</sub> or C <sub>MILLER</sub> | dv/dt (load) |  |  |

| 0.01µF*                                  | 2.5V/ms      |  |  |

| 0.022µF*                                 | 1.136V/ms    |  |  |

| 0.047µF                                  | 0.532 V/ms   |  |  |

| 0.1µF                                    | 0.250V/ms    |  |  |

Values in this range will be affected by the internal parasitic capacitances of the MOSFETs used, and should be verified experimentally.

#### Table 1. 3.3V and 12V Output Slew-Rate Selection for Gate Capacitance Dominated Start-up

#### Power-Down Cycle

t<sub>1</sub>

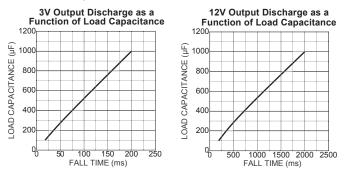

When one or more PCI slots are disabled via the MIC2592B output control pins, ON[A/B] or AUXEN[A/B], the output voltage for each supply will discharge as a function of the RC time constant produced by the controller's internal resistance (R<sub>DIS</sub>) connected to the output and the load capacitance (C<sub>LOAD</sub>). The typical value of R<sub>DIS</sub> for each supply is listed in the Electrical Characteristics Table. The charts below in Figure 7 display curves of the fall time (90% - 10%) as a function of the output load capacitance for both the 3V and 12V MAIN outputs.

## Figure 7. 3V and 12V Output Discharge vs. Load Capacitance

#### Standby Mode

Standby mode is entered when one or more of the MAIN supply inputs (12VIN and/or 3VIN) is below its respective UVLO threshold or OFF. The MIC2592B also supplies 3.3V auxiliary outputs (VAUX[A/B]), satisfying PCI Express specifications. These outputs are fed via the VSTBY[A/B] input pins and controlled by the AUXEN[A/B] input pins or via their respective bits in the Control Registers. These outputs are independent of the MAIN outputs (12VIN[A/B] and 3VIN[A/B]). Should the MAIN supply inputs move below their respective UVLO thresholds, VAUX[A/B] will still function as long as VSTBY[A/B] is present. Prior to standby mode, ONA and ONB (or the Control Registers' MAINA and MAINB bits) inputs should be deasserted or the MIC2592B will assert /FAULT[A/B] and /INT (if interrupts are enabled) output signals, if an undervoltage condition on the MAIN supply inputs is detected.

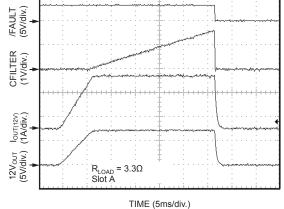

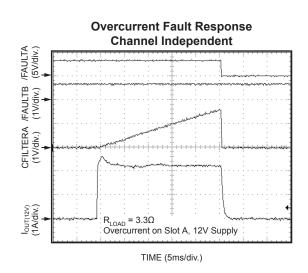

#### **Circuit Breaker Function**

The MIC2592B provides an electronic circuit breaker function that protects against excessive loads, such as short circuits, at each supply. When the current from one or more of a slot's MAIN outputs exceeds the current limit threshold ( $I_{LIM} = 50 \text{mV/R}_{SENSE}$ ) for a duration greater than  $t_{FLT}$ , the circuit breaker is tripped and both MAIN supplies (all outputs except VAUX[A/B]) are shut off. Should the load current cause a MAIN output's  $V_{SENSE}$  to exceed  $V_{THFAST}$ , the outputs are immediately shut off with no delay. Undervoltage conditions on the MAIN supply inputs also trip the circuit breaker, but only when the MAIN outputs are enabled (to signal a supply input brown-out condition).

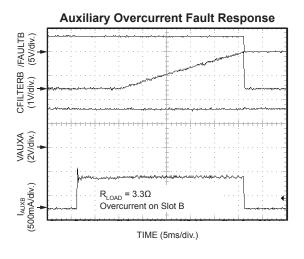

The VAUX[A/B] outputs have a different circuit-breaker function. The VAUX[A/B] circuit breakers do not incorporate a fast-trip detector, instead they regulate the output current into a fault to avoid exceeding their operating current limit. The circuit breaker will trip due to an overcurrent on VAUX[A/B] when the fault timer expires. This use of the  $t_{FLT}$  timer prevents the circuit breaker from tripping prematurely due to brief current transients.

Following a fault condition, the outputs can be turned on again via the ON inputs (if the fault occurred on one of the MAIN outputs), via the AUXEN inputs (if the fault occurred on the AUX outputs), or by cycling both ON and AUXEN (if faults occurred on both the MAIN and AUX outputs). A fault condition can alternatively be cleared under SMI control of the ENABLE bits in the CNTRL[A/B] registers (see Register Bits D[1:0]). When the circuit breaker trips, /FAULT[A/B] will be asserted if the outputs were enabled through the Hot-Plug Interface inputs. At the same time, /INT will be asserted (unless interrupts are masked). Note that /INT is deasserted by writing a Logic 1 back into the respective fault bit position(s) in the STAT[A/B] register or the Common Status Register.

The response time ( $t_{FLT}$ ) of the MIC2592B's primary overcurrent detector is set by external capacitors at the CFILTER[A/B] pins to GND. For Slot A, CFILTER[A] is located at Pin 2; for Slot B, CFILTER[B] is located at Pin 35. For a given response time, the value for C<sub>FILTER[A/B]</sub> is given by:

$$C_{FILTER[A/B]}(\mu F) = \frac{t_{FLT[A/B]}(ms) \times I_{FILTER}(\mu A)}{V_{FILTER}(V) \times 10^{3}}$$

where  $t_{FLT[A/B]}$  is the desired response time and quantities  $I_{FILTER}$  and  $V_{FILTER}$  are specified in the MIC2592B's "Electrical Characteristics" table.

For applications that require a more accurate response time for a given  $C_{FILTER[A/B]}$  tolerance, the MIC2592B employs a patent-pending technique that improves response time accuracy by more than a factor of two. A 110k $\Omega$ , 1% resistor connected from the MIC2592B's RFILTER[A&B] pin (Pin 20) to GND can be used. In this case, the value for  $C_{FILTER[A/B]}$  for a desired response time ( $t_{FIT}$ ) is given by:

$$C_{FILTER[A/B]}(\mu F) = \frac{t_{FLT}(ms)}{R_{FILTER[A\&B]}(k\Omega) \times SF}$$

where  $t_{FLT}$  is the desired response time,  $R_{FILTER[A\&B]}$  is 110k $\Omega$ , and "SF" is the CFILTER[A/B] response time "Scaling Factor" in the "Electrical Characteristics" table.

#### Thermal Shutdown

The internal VAUX[A/B] MOSFETs are protected against damage not only by current limiting, but by dual-mode overtemperature protection as well. Each slot controller on the MIC2592B is thermally isolated from the other. Should an overcurrent condition raise the junction temperature of one slot's controller and pass elements to 140°C, all of the outputs for that slot (including VAUX) will be shut off and the slot's /FAULT output will be asserted. The other slot's operating condition will remain unaffected. However, should the MIC2592B's die temperature exceed 160°C, both slots (all outputs, including VAUXA and VAUXB) will be shut off, whether or not a current limit condition exists. A 160°C overtemperature condition additionally sets the overtemperature bit (OT\_INT) in the Common Status Register.

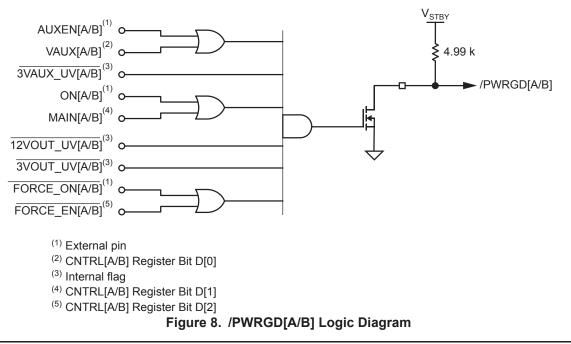

#### /PWRGD[A/B] Outputs

The MIC2592B has two /PWRGD outputs, one for each slot. These are open-drain, active-low outputs that require an external pull-up resistor to  $V_{STBY}$ . Each output is asserted when a slot has been enabled and has successfully begun delivering power to its respective +12V, +3.3V, and VAUX outputs. An equivalent logic diagram for /PWRGD[A/B] is shown in Figure 8.

#### /FORCE\_ON[A/B] Inputs

These level-sensitive, active-low inputs are provided to facilitate designing systems using the MIC2592B. Asserting /FORCE\_ON[A/B] will turn on all three of the respective slot's outputs (+12V, +3.3V, and VAUX), while specifically defeating all protections for those outputs. This explicitly includes all overcurrent and short circuit protections, and on-chip thermal protection for the VAUX supplies. Additionally, asserting a slot's /FORCE\_ON[A/B] input will disable all of its input and output UVLO protections, with the sole exception of that asserting either or both of the /FORCE\_ON[A/B] inputs will not disable the VSTBY[A/B] input UVLO.

Asserting /FORCE\_ON[A/B] will cause the respective slot's /PWRGD[A/B] and /FAULT[A/B] outputs to enter their opendrain state. Additionally, there are two SMBus accessible register bits (see CNTRL[A/B] Register Bit D[2]), which can be set to disable the corresponding slot's /FORCE\_ON[A/B] pins. This allows system software to prevent these hardware overrides from being inadvertently activated during normal use. If not used, each pin should be connected to V<sub>STBY</sub> using an external pull-up resistor. See Figure 6 for details.

#### **General Purpose Input (GPI) Pins**

Two pins on the MIC2592B are available for use as GPI pins. The logic state of each of these pins can be determined by polling Bits [4:5] of Common Status Register. Both of these inputs are compliant to 3.3V. If unused, connect each GPI\_[A0/B0] pin to GND.

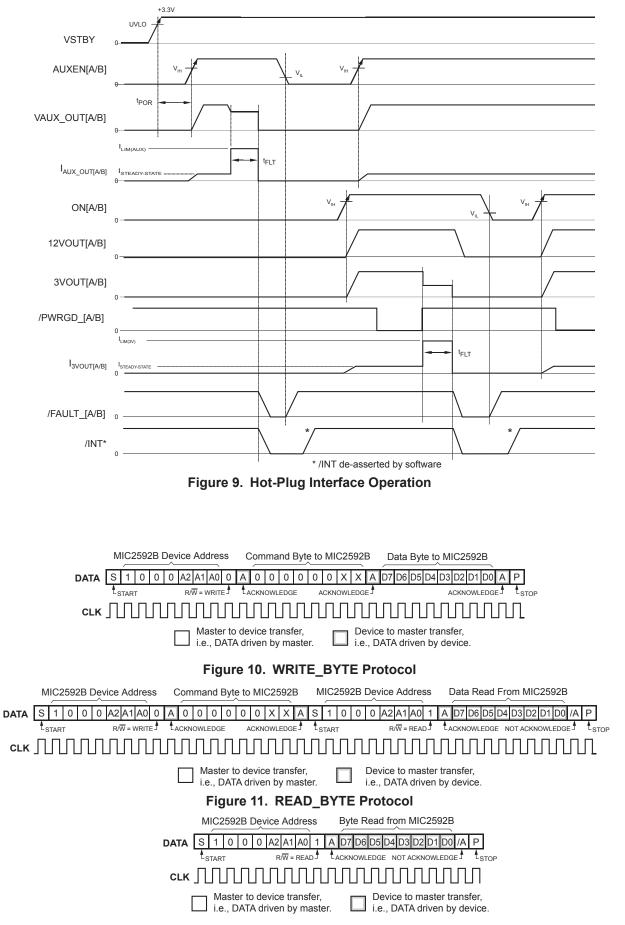

#### Hot-Plug Interface (HPI)

Once the input supplies are above their respective UVLO thresholds, the Hot-Plug Interface can be utilized for power control by enabling the control input pins (AUXEN[A/B] and ON[A/B]) for each slot. In order for the MIC2592B to switch on the VAUX supply for either slot, the AUXEN[A/B] control must be enabled after the power-on-reset delay, t<sub>POR</sub> (typi-

cally,  $250\mu$ s), has elapsed. The timing response diagram of Figure 9 illustrates a Hot-Plug Interface operation where an overcurrent fault is detected by the MIC2592B controller after initiating a power-up sequence. The MAIN (+12V & +3.3V) and VAUX[A/B] supply rails, /FAULT, /PWRGD and /INT output responses for both AUX and MAIN are shown in the figure.

#### System Management Interface (SMI)

The MIC2592B's System Management Interface uses the Read\_Byte and Write\_Byte subset of the SMBus protocols to communicate with its host via the System Management Interface bus. The /INT output signals the controlling processor that one or more events need attention, if an interrupt-driven architecture is used. Note that the MIC2592B does not participate in the SMBus Alert Response Address (ARA) portion of the SMBus protocol.

#### Fault Reporting and Interrupt Generation

#### SMI-only Control Applications

In applications where the MIC2592B is controlled only by the SMI, ON[A/B] and AUXEN[A/B] are connected to GND and the /FORCE\_ON[A/B] pins are connected to  $V_{STBY}$  as shown in Figure 6. In this case, the MIC2592B's /FAULT[A/B] outputs and STAT[A/B] Register Bit D[7] (FAULT[A/B]) are not activated as fault status is determined by polling STAT[A/B] Register Bits D[4], D[2], D[0] and CS (Common Status) Register Bits D[2:1]. Individual fault bits in STAT[A/B] and CS registers are asserted after power-on-reset when:

- Either or both CNTRL[A/B] Register Bits D[1:0] are asserted, AND

- 12VIN[A/B], 3VIN[A/B], or VSTBY[A/B] input voltage is lower than its respective ULVO threshold, OR

- The fast OC circuit breaker[A/B] has tripped, OR

- The slow OC circuit breaker[A/B] has tripped AND its filter timeout has expired, OR

- The slow OC circuit breaker[A/B] has tripped AND Slot[A/B] die temperature > 140°C, OR

- The MIC2592B's global die temperature > 160°C

To clear any one or all STAT[A/B] Register Bits D[4], D[2], D[0] and/or CS Register Bits D[2], D[1] once asserted, a software subroutine can perform an "echo reset" where a Logical "1" is written back to those register bit locations that have indicated a fault. This method of "echo reset" allows data to be retained in the STAT[A/B] and/or CS registers until such time as the system is prepared to operate on that data.

The MIC2592B can operate in interrupt mode or polled mode. For interrupt-mode operation, the open-drain, active-LOW /INT output signal is activated after power-on-reset if the INTMSK bit (CS Register Bit D[3]) has been reset to Logical "0". Once activated, the /INT output is asserted by any one of the fault conditions listed above and deasserted when one or all STAT[A/B] Register Bits D[4], D[2], D[0] and/or CS Register Bits D[2], D[1] are reset upon the execution of an SMBus "echo reset" WRITE\_BYTE cycle. For polled-mode operation, the INTMSK bit should be set to Logical "1," thereby inhibiting /INT output pin operation.

For those SMI-control applications where the /FORCE\_ON[A/B]

inputs are needed for diagnostic purposes, the /FORCE\_ON[A/B] inputs must be enabled; that is, CNTRL[A/B] RegisterBitD[2]should readLogical"0."Once/FORCE\_ON[A/B] inputs are asserted, all output voltages are present with all circuit protection features disabled, including overtemperature protection on VAUX[A/B] outputs. To inhibit /FORCE\_ON[A/B] operation, a Logical "1" shall be written to the CNTRL[A/B] Register Bit D[2] location(s).

#### HPI-only Control Applications

In applications where the MIC2592B is controlled only by the HPI, SMBus signals SCL, SDA, and /INT signals are connected to  $V_{STBY}$  as shown in Figure 6. In this configuration, the MIC2592B's /FAULT[A/B] outputs are activated after power-on-reset and become asserted when:

Either or both external ON[A/B] and AUXEN[A/B] input signals are asserted, AND

- 12VIN[A/B], 3VIN[A/B], or VSTBY[A/B] input voltage is lower than its respective ULVO threshold, OR

- The fast OC circuit breaker[A/B] has tripped, OR

- The slow OC circuit breaker[A/B] has tripped AND its filter timeout[A/B] has expired, OR

- The slow OC circuit breaker[A/B] has tripped AND Slot[A/B] die temperature > 140°C, OR

- The MIC2592B's global die temperature > 160°C

In order to clear /FAULT[A/B] outputs once asserted, either or both ON[A/B] and AUXEN[A/B] input signals must be deasserted. Please see /FAULT[A/B] pin description for additional information.

If the /FORCE\_ON[A/B] inputs are used for diagnostic purposes, both /FAULT[A/B] and /PWRGD[A/B] outputs are deasserted once /FORCE\_ON[A/B] inputs are asserted.

#### **Serial Port Operation**

The MIC2592B uses standard SMBus Write\_Byte and Read\_Byte operations for communication with its host. The SMBus Write\_Byte operation involves sending the device's target address, with the R/W bit (LSB) set to the low (write) state, followed by a command byte and a data byte. The SMBus Read\_Byte operation is similar, but is a composite write and read operation: the host first sends the device's target address followed by the command byte, as in a write operation. A new "Start" bit must then be sent to the MIC2592B, followed by a

repeat of the device address with the R/ $\overline{W}$  bit set to the high (read) state. The data to be read from the part may then be clocked out. There is one exception to this rule: If the location latched in the pointer register from the last <u>write</u> operation is known to be correct (i.e., points to the desired register within the MIC2592B), then the "Receive\_Byte" procedure may be used. To perform a Receive\_Byte operation, the host sends an address byte to select the target MIC2592B, with the R/ $\overline{W}$  bit set to the high (read) state, and then retrieves the data byte. Figures 10 through 12 show the formats for these data read and data write procedures.

The Command Register is eight bits (one byte) wide. This byte carries the address of the MIC2592B's register to be operated upon. The command byte values corresponding to the various MIC2592B register addresses are shown in Table 2. Command byte values other than 0000 0XXX<sub>b</sub> =  $00_h - 07_h$  are reserved and should not be used.

#### MIC2592B SMBus Address Configuration

The MIC2592B responds to its own unique SMBus address, which is assigned using A2, A1, and A0. These represent the 3 LSBs of its 7-bit address, as shown in Table 3. These address bits are assigned only during power up of the VSTBY[A/B] supply input. These address bits allow up to eight MIC2592B devices in a single system. These pins are either grounded or left unconnected to specify a logical 0 or logical 1, respectively. A pin designated as a logical 1 may also be pulled up to  $V_{STBY}$ .

| Inputs |    |    | MIC2592B Device Address |                 |

|--------|----|----|-------------------------|-----------------|

| A2     | A1 | A0 | Binary                  | Hex             |

| 0      | 0  | 0  | 1000 000X* <sub>b</sub> | 80 <sub>h</sub> |

| 0      | 0  | 1  | 1000 001X <sub>b</sub>  | 82 <sub>h</sub> |

| 0      | 1  | 0  | 1000 010X <sub>b</sub>  | 84 <sub>h</sub> |

| 0      | 1  | 1  | 1000 011X <sub>b</sub>  | 86 <sub>h</sub> |

| 1      | 0  | 0  | 1000 100X <sub>b</sub>  | 88 <sub>h</sub> |

| 1      | 0  | 1  | 1000 101X <sub>b</sub>  | 8A <sub>h</sub> |

| 1      | 1  | 0  | 1000 110X <sub>b</sub>  | 8C <sub>h</sub> |

| 1      | 1  | 1  | 1000 111X <sub>b</sub>  | 8E <sub>h</sub> |

\* Where X = "1" for READ and "0" for Write

```

Table 3. MIC2592B SMBus Addressing

```