# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## MIC5166

3A High-Speed Low VIN DDR Terminator

#### **General Description**

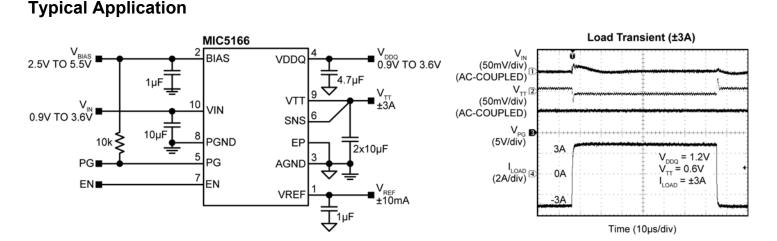

The MIC5166 is a 3A, high-speed, linear, low V<sub>IN</sub> double data rate (DDR), memory terminator power supply. The part is small and requires small output capacitors making it a tiny overall solution. This allows it to be conveniently placed close to the DDR memory, minimizing circuit board layout inductance which may cause excessive voltage ripple at the DDR memory.

The MIC5166 contains a precision voltage divider network in order to take in the  $V_{DDQ}$  voltage as a reference voltage and conveniently output the terminator voltage (V<sub>TT</sub>) at one half of the  $V_{DDQ}$  input voltage.

The MIC5166 is capable of sinking and sourcing up to 3A. It is stable with only two 10 $\mu$ F ceramic output capacitors. The part is available in a small 3mm × 3mm MLF<sup>®</sup> thermally-enhanced package.

The MIC5166 has a high-side NMOS output stage offering very-low output impedance, and very-high bandwidth. The NMOS output stage offers a unique ability to respond very quickly to sudden load changes such as is required for DDR memory termination power supply applications.

Data sheets and support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

#### Features

- Operating voltage range:

- V<sub>DDQ</sub> Supply: 0.9V to 3.6V

- Bias Supply: 2.5V to 5.5V

- High bandwidth very fast transient response

- Stable with two 10µF ceramic output capacitors

- Two 10µF output capacitors used in most applications

- High output voltage accuracy:

- 0.015% line regulation

- 1.5% load regulation

- Logic level enable input

- Power Good (PG)

- Thermally-enhanced 3mm × 3mm MLF®

- Junction temperature range –40°C to +125°C

## Applications

- Desktop computers

- Notebook computers

- Datacom systems

- Servers

- Video cards

Ramp Control is a trademark of Micrel, Inc

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Part Number | Output Voltage | Junction Temperature Range <sup>(1)</sup> | Package                                 | Lead Finish |

|-------------|----------------|-------------------------------------------|-----------------------------------------|-------------|

| MIC5166YML  | ½VDDQ          | –40°C to +125°C                           | 10-Pin 3mm $	imes$ 3mm MLF <sup>®</sup> | Pb-Free     |

Note:

1. MLF<sup>®</sup> is a GREEN RoHS-compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free..

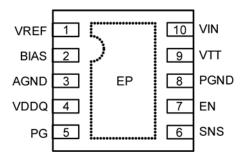

## **Pin Configuration**

10-Pin 3mm  $\times$  3mm MLF  $^{\tiny (\! R \!\!\!)}$  (ML)

## **Pin Description**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                         |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VREF     | Reference Voltage. This output provides an output of the internal reference voltage $V_{DDQ}/2$ . The $V_{REF}$ output is used to provide the reference voltage for the memory chip. Connect a 1.0µF capacitor to ground at this pin. This pin can sink and source 10mA.            |

| 2          | BIAS     | BIAS Supply Voltage. The BIAS supply is the power MOSFET gate drive supply voltage and the supply bus for the IC. The BIAS voltage must be greater than ( $V_{TT}$ + 2.2V). A 1.0µF ceramic capacitor from the BIAS pin to PGND must be placed next to the IC.                      |

| 3          | AGND     | Analog Ground. Internal signal ground for all low-power circuits.                                                                                                                                                                                                                   |

| 4          | VDDQ     | Input Supply. VDDQ is connected to an internal precision divider which provides the $V_{REF}$ . Connect a 4.7µF capacitor to ground at this pin.                                                                                                                                    |

| 5          | PG       | Power Good. This is an open drain output that indicates when the output voltage is within $\pm 10\%$ of the reference voltage. The PG flag is asserted typically with 65µs delay when the enable is set low or when the output goes outside $\pm 10\%$ the window threshold.        |

| 6          | SNS      | Feedback. Input to the error amplifier.                                                                                                                                                                                                                                             |

| 7          | EN       | Enable. Logic level control of the output. Logic HIGH enables the MIC5166 and a logic LOW shuts down the MIC5166. In the off state, supply current of the device is greatly reduced (typically $0.2\mu$ A). The EN pin should not be left open.                                     |

| 8          | PGND     | Power Ground. Internal ground connection to the source of the internal, low-side drive, N-channel MOSFET.                                                                                                                                                                           |

| 9          | VTT      | Power Output. This is the connection to the source of the internal high-side N-channel MOSFET and drain of the low-side N-channel MOSFET. This is a high-frequency, high-power connection, therefore two $10\mu$ F output capacitors must be placed as close to the IC as possible. |

| 10         | VIN      | High-Side N-Channel MOSFET Drain Connection. The V <sub>IN</sub> operating voltage range is from 0.9V to 3.6V. An input capacitor between the VIN pin and the PGND is required as close to the chip as possible.                                                                    |

| EP         | ePad     | Exposed Pad. Must be connected to a GND plane for best thermal performance.                                                                                                                                                                                                         |

## Absolute Maximum Ratings<sup>(1)</sup>

| $V_{\text{BIAS}}$ –0.3V to 6V                             |  |

|-----------------------------------------------------------|--|

| $V_{IN}$                                                  |  |

| $V_{DDQ}$ 0.3V to $V_{IN}$                                |  |

| V <sub>TT</sub> –0.3V to V <sub>IN</sub>                  |  |

| $V_{\text{EN}}$ –0.3V to $V_{\text{BIAS}}$                |  |

| $V_{\text{PG}}$ –0.3V to $V_{\text{BIAS}}$                |  |

| PGND to AGND0.3V to 0.3V                                  |  |

| Junction Temperature                                      |  |

| Storage Temperature Range65°C to +150°C                   |  |

| Lead Temperature (soldering, 10s)260°C                    |  |

| Continuous Power Dissipation ( $T_A = 25^{\circ}C$ )      |  |

| (De-rated 16.4mW/°C above 25°C)1.64W                      |  |

| Continuous Power Dissipation (T <sub>A</sub> = 85°C)656mW |  |

| ESD <sup>(2)</sup> 2kV(HBM)                               |  |

## Operating Ratings<sup>(3)</sup>

| Supply Voltage (V <sub>BIAS</sub> )               |                                        |

|---------------------------------------------------|----------------------------------------|

| Supply Voltage (VIN)                              | 0.9V to 3.6V <sup>(4)</sup>            |

| Supply Voltage (V <sub>DDQ</sub> )                | 0.9V to V <sub>IN</sub> <sup>(5)</sup> |

| Power Good Voltage (V <sub>PG</sub> )             | 0V to V <sub>BIAS</sub>                |

| Enable Input (V <sub>EN</sub> )                   | 0V to V <sub>BIAS</sub>                |

| Junction Temperature (T <sub>J</sub> )            | –40°C ≤ T <sub>J</sub> ≤ +125°C        |

| Package Thermal Resistance                        |                                        |

| 3mm x 3mm MLF <sup>®</sup> -10 (θ <sub>JC</sub> ) |                                        |

| 3mm x 3mm MLF <sup>®</sup> -10 ( $\theta_{JA}$ )  | 60.7°C/W                               |

## Electrical Characteristics<sup>(6)</sup>

$V_{\text{IN}} = 1.5V, V_{\text{BIAS}} = 3.3V, V_{\text{DDQ}} = 1.5V, T_{\text{A}} = 25^{\circ}\text{C}, \text{ unless noted}. \text{ Bold values indicate } -40^{\circ}\text{C} \le T_{\text{J}} \le +125^{\circ}\text{C}.$

| Parameter                                     | Condition                                                                          | Min.  | Тур.  | Max. | Units       |  |

|-----------------------------------------------|------------------------------------------------------------------------------------|-------|-------|------|-------------|--|

| Power Input Supply                            |                                                                                    | I     | 1     |      | 1           |  |

| Input Voltage Range (V <sub>IN</sub> )        |                                                                                    | 0.9   |       | 3.6  | V           |  |

| Undervoltage Lockout Trip Level               | V <sub>IN</sub> Rising                                                             | 0.625 | 0.8   | 0.9  | V           |  |

| UVLO Hysteresis                               |                                                                                    |       | 150   |      | mV          |  |

| Quiescent Supply Current (IIN)                | I <sub>OUT</sub> = 0A                                                              |       | 0.1   | 10   | μA          |  |

| Shutdown Current (I <sub>IN</sub> )           | V <sub>EN</sub> = 0V                                                               |       | 0.1   | 5    | μA          |  |

| Bias Supply                                   |                                                                                    |       |       |      |             |  |

| Bias Voltage Range (V <sub>BIAS</sub> )       |                                                                                    | 2.5   |       | 5.5  | V           |  |

| Undervoltage Lockout Trip Level               | V <sub>BIAS</sub> Rising                                                           | 1.9   | 2.23  | 2.33 | V           |  |

| UVLO Hysteresis                               |                                                                                    |       | 70    |      | mV          |  |

|                                               | I <sub>OUT</sub> = 1mA                                                             |       | 1.6   | 3    | <b>3</b> mA |  |

| Quiescent Supply Current (I <sub>BIAS</sub> ) | I <sub>OUT</sub> = 1A                                                              |       | 1.6   | 3    | IIIA        |  |

| Shutdown Current (I <sub>BIAS</sub> )         | V <sub>EN</sub> = 0V                                                               |       | 0.1   | 5    | μA          |  |

| V <sub>TT</sub> Output                        | •                                                                                  |       |       |      |             |  |

| V <sub>TT</sub> Accuracy                      | Variation from V <sub>REF</sub> , I <sub>OUT</sub> = -3A to 3A                     | -40   |       | 40   | mV          |  |

| Load Regulation                               | V <sub>SNS</sub> =0.75V, I <sub>OUT</sub> = 10mA to +3A                            |       | 1.5   | 2.1  | %           |  |

| Load Regulation                               | V <sub>SNS</sub> =0.75V, I <sub>OUT</sub> = -10mA to -3A                           | -1.8  | -1.4  |      |             |  |

| Line Regulation                               | $V_{IN}$ = 1.5V to 3.6V, $V_{BIAS}$ = 5.5V, $I_{OUT}$ = 100mA                      | -0.05 | 0.005 | 0.05 | %/V         |  |

| Line Regulation                               | V <sub>IN</sub> = 1.5V, V <sub>BIAS</sub> = 2.5V to 5.5V, I <sub>OUT</sub> = 100mA | -0.1  | 0.015 | 0.17 | %/V         |  |

3

## Electrical Characteristics<sup>(6)</sup> (Continued)

| V <sub>IN</sub> = 1.5V, V <sub>BIAS</sub> = 3.3V, V <sub>DDQ</sub> = 1.5V, 7 | $\Gamma_{\Lambda} = 25^{\circ}C_{\circ}$ unless noted. | <b>Bold</b> values indicate $-40^{\circ}C \le T_{\perp} \le +$ | ·125°C |

|------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------|

|                                                                              |                                                        |                                                                | 120 0. |

| Parameter                                              | Condition                                                   | Min. | Тур. | Max. | Units |  |

|--------------------------------------------------------|-------------------------------------------------------------|------|------|------|-------|--|

| V <sub>REF</sub> Output                                |                                                             |      |      | 1    |       |  |

| V <sub>REF</sub> Voltage Accuracy                      | Variation from ( $V_{DDQ}/2$ ), $I_{REF}$ = -10mA to 10mA   | _1   |      | 1    | %     |  |

| Bias Supply Dropout Voltage                            |                                                             |      |      |      |       |  |

| Dropout Voltage (V <sub>BIAS</sub> – V <sub>TT</sub> ) | I <sub>OUT</sub> = 100mA                                    |      | 1.15 |      | V     |  |

| Dropout Voltage (V <sub>BIAS</sub> – V <sub>TT</sub> ) | I <sub>OUT</sub> = 500mA                                    |      | 1.25 |      | V     |  |

| Dropout Voltage (V <sub>BIAS</sub> – V <sub>TT</sub> ) | I <sub>OUT</sub> = 3.0A                                     |      | 1.65 | 2.2  | V     |  |

| Enable Control                                         |                                                             |      |      |      |       |  |

| EN Logic High Level                                    | Logic High                                                  | 1.2  |      |      | V     |  |

| EN Logic Low Level                                     | Logic Low                                                   |      |      | 0.2  | V     |  |

| EN Current                                             | V <sub>EN</sub> = 0.2V                                      |      | 1.0  |      | μA    |  |

| EN Current                                             | V <sub>EN</sub> = 1.2V                                      |      | 6.0  |      |       |  |

| Start-Up Time                                          | From EN pin going high to $V_{TT}$ 90% of $V_{REF}$         |      | 55   |      | μs    |  |

| Short-Current Protection                               |                                                             |      |      |      |       |  |

| Sourcing Current Limit                                 | V <sub>IN</sub> = 2.7V, V <sub>TT</sub> = 0V                | 3.1  | 4.9  | 7.8  | А     |  |

| Sinking Current Limit                                  | $V_{IN} = 2.7V, V_{TT} = V_{IN}$                            | -3.1 | -4.9 | -7.8 | А     |  |

| Internal FETs                                          |                                                             |      |      |      |       |  |

| Top-MOSFET R <sub>DS(ON)</sub>                         | Source, I <sub>OUT</sub> = 3A (V <sub>TT</sub> to PGND)     |      | 130  | 190  | mΩ    |  |

| Bottom-MOSFET R <sub>DS(ON)</sub>                      | Sink, $I_{OUT}$ = -3A (V <sub>IN</sub> to V <sub>TT</sub> ) |      | 130  | 190  | mΩ    |  |

| Power Good (PG)                                        |                                                             |      |      |      |       |  |

| PG Window                                              | Threshold % of V <sub>TT</sub> from V <sub>REF</sub>        | ≥90  |      | ≤110 | %     |  |

| Hysteresis                                             |                                                             |      | 2    |      | %     |  |

| PG Output Low Voltage                                  | I <sub>PG</sub> = 4mA (sinking)                             |      | 430  |      | mV    |  |

| PG Leakage Current                                     | $V_{PG}$ = 5.5V, $V_{SNS}$ = $V_{REF}$                      |      |      | 1.0  | μA    |  |

| Thermal Protection                                     |                                                             | I    | 1    | 1    |       |  |

| Over-Temperature Shutdown                              | T <sub>J</sub> Rising                                       |      | 150  |      | °C    |  |

| Over-Temperature Shutdown<br>Hysteresis                |                                                             |      | 10   |      | °C    |  |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

3. The device is not guaranteed to function outside its operating rating.

$\label{eq:states} 4. \quad \ \ If \ V_{\text{BIAS}} \leq 3.6V, \ then \ V_{\text{IN(MAX)}} = V_{\text{BIAS}}.$

$5. \quad \ \ If \ V_{\text{BIAS}} \leq 4V, \ then \ V_{\text{DDQ(MAX)}} = 2 \times (V_{\text{BIAS}} - 2.2V). \ If \ V_{\text{BIAS}} > 4V, \ then \ V_{\text{DDQ(MAX)}} = 3.6V.$

6. Specification for packaged product only.

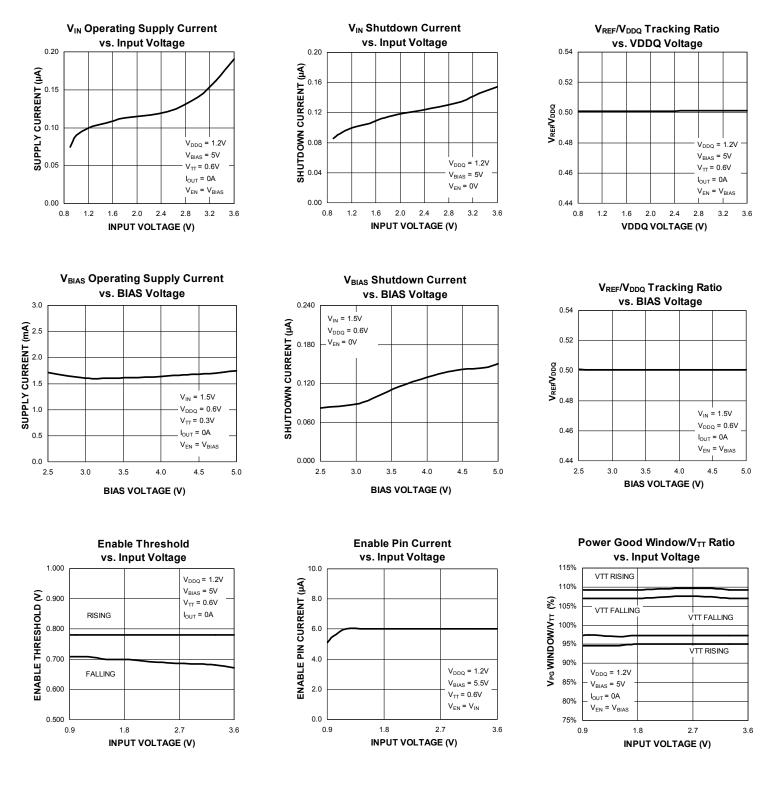

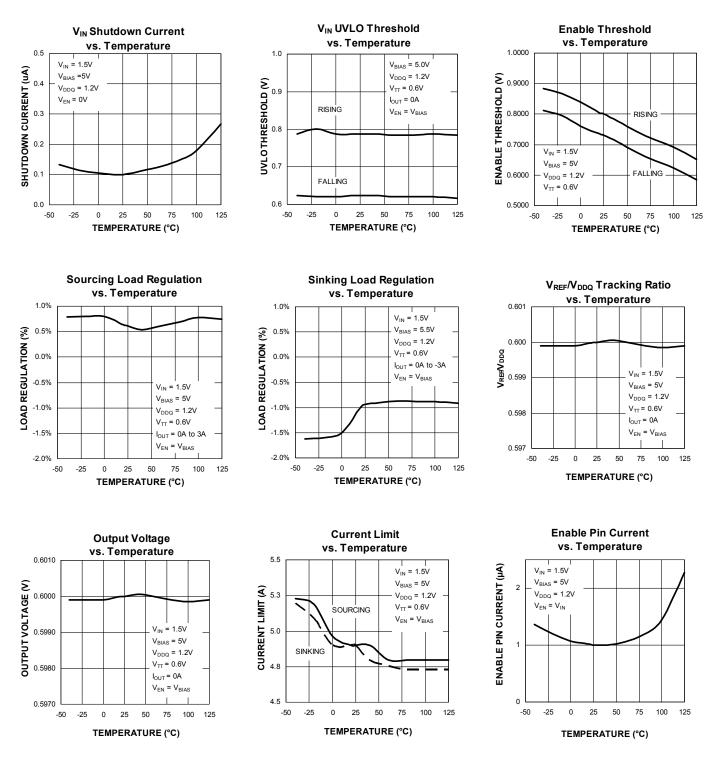

## **Typical Characteristics**

## **Typical Characteristics (Continued)**

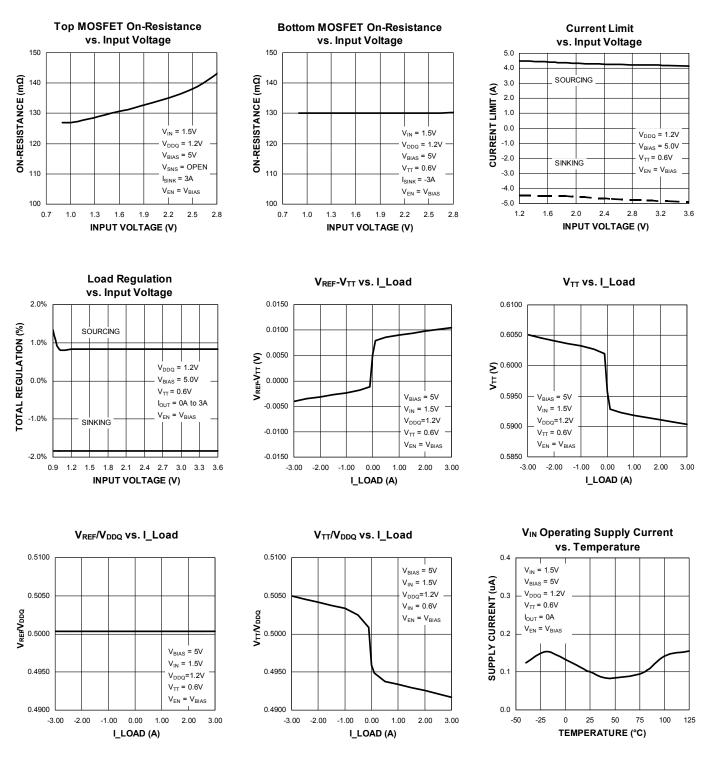

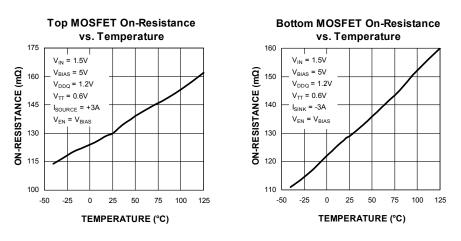

## **Typical Characteristics (Continued)**

## **Typical Characteristics (Continued)**

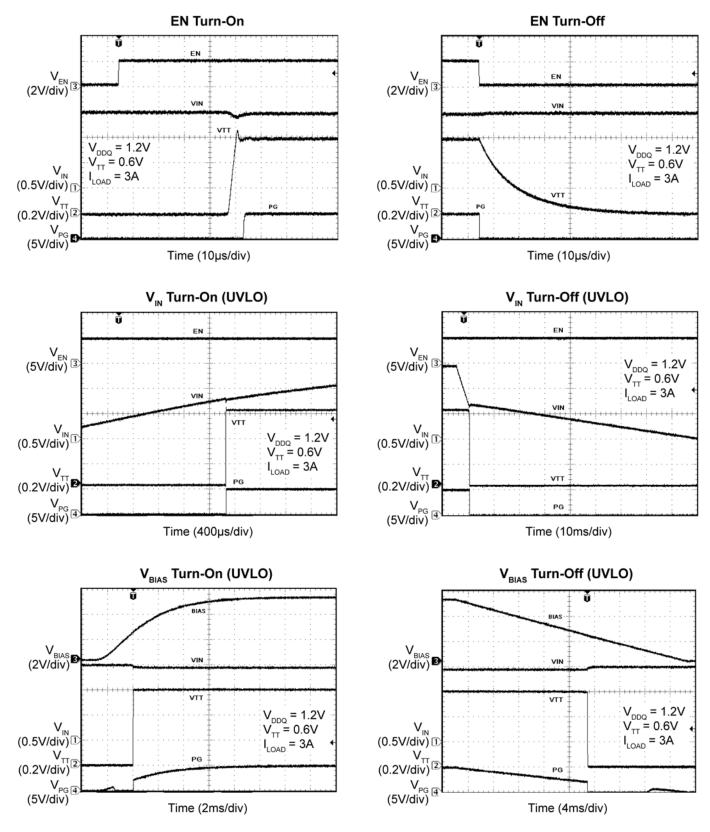

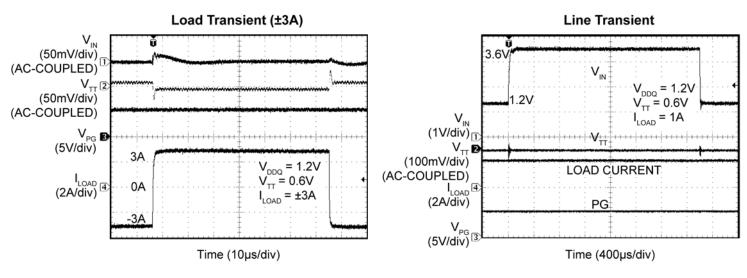

## **Functional Characteristics**

## **Functional Characteristics (Continued)**

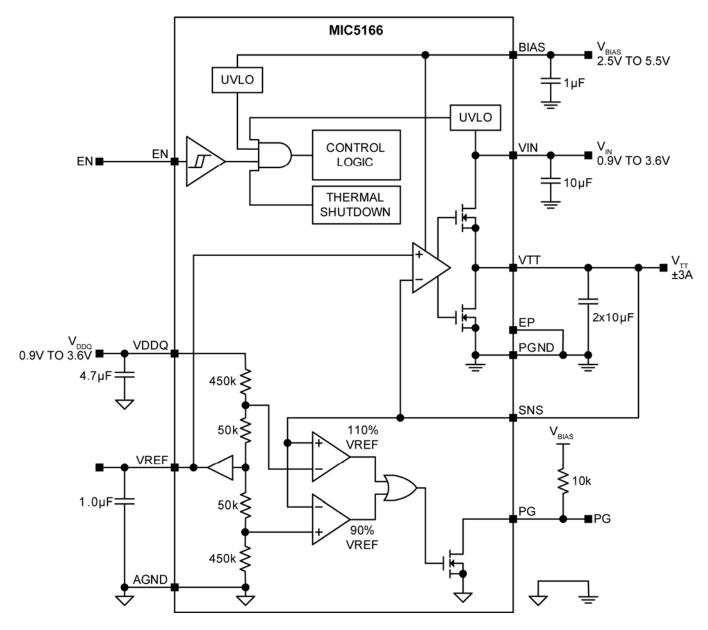

## **Functional Diagram**

Figure 1. MIC5166 Block Diagram

## **Application Information**

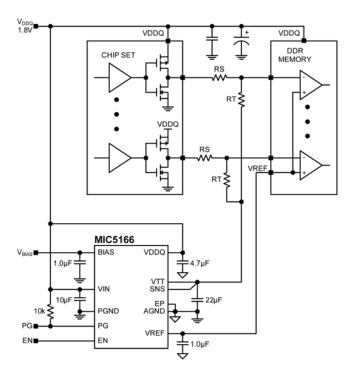

DDR memory requires two power supplies, one for the memory chip, referred to as  $V_{DDQ}$  and the other for a termination supply  $V_{TT}$ , which is one-half  $V_{DDQ}$ . With memory speeds in excess of 300MHz, the memory system bus must be treated as a transmission line. To maintain good signal integrity the memory bus must be terminated to minimize signal reflections. Figure 2 shows the simplified termination circuit. Each control, address and data lines have these termination resistors RS and RT connected to them.

Figure 2. DDR Memory Termination Circuit

Bus termination provides a means to increase signaling speed while maintaining good signal integrity. The termination network consists of a series resistor ( $R_s$ ) and a terminating resistor ( $R_T$ ). Values of  $R_s$  range between 10 $\Omega$  to 30 $\Omega$  with a typical of 22 $\Omega$ , while  $R_T$  ranges from 22 $\Omega$  to 28 $\Omega$  with a typical value of 25 $\Omega$ . V<sub>REF</sub> must maintain half V<sub>DDQ</sub> with a ±1% tolerance, while V<sub>TT</sub> will dynamically sink and source current to maintain a termination voltage of ±40mV from the V<sub>REF</sub> line under all conditions. This method of bus termination reduces common-mode noise, settling time, voltage swings, EMI/RFI and improves slew rates.

$V_{\text{DDQ}}$  powers all the memory ICs, memory drivers and receivers for all the memory bits in the DDR memory system. The MIC5166 regulates  $V_{\text{TT}}$  to  $V_{\text{DDQ/2}}$  during sourcing or sinking current.

The memory bits are not usually all at a logic high or logic low at the same time so the  $V_{TT}$  supply is usually not sinking or sourcing -3A or +3A current continuously.

#### $\mathbf{V}_{\mathsf{TT}}$

$V_{TT}$  is regulated to  $V_{REF}$ . Due to high-speed signaling, the load current seen by  $V_{TT}$  is constantly changing. To maintain adequate transient response, two  $10\mu$ F ceramic capacitors are required. The proper placement of ceramic capacitors is important to reduce both ESR and ESL such that high-current and high-speed transients do not exceed the dynamic voltage tolerance requirement of  $V_{TT}$ . The ceramic capacitors provide current during the fast edges of the bus transition. Using several smaller ceramic capacitors distributed near the termination resistors is important to reduce the effects of PCB trace inductance.

#### V<sub>DDQ</sub>

The  $V_{\text{DDQ}}$  input on the MIC5166 is used to create the internal reference voltage for  $V_{\text{TT}}$ . The reference voltage is generated from an internal resistor divider network of two 500k $\Omega$  resistors, generating a reference voltage  $V_{\text{REF}}$  that is  $V_{\text{DDQ/2}}$ . The  $V_{\text{DDQ}}$  input should be Kelvin connected as close as possible to the memory supply voltage.

Since the reference is simply  $V_{DDQ/2}$ , any perturbations on  $V_{DDQ}$  will also appear at half the amplitude on the reference. For this reason a 4.7µF ceramic capacitor is required on the  $V_{DDQ}$  supply. This will aid performance by improving the source impedance over a wide frequency range.

#### Sense

The sense (SNS) pin provides the path for the error amplifier to regulate  $V_{TT}$ . The SNS input must also be Kelvin connected to the  $V_{TT}$  bypass capacitors. If the SNS input is connected to close to the MIC5166, the IR drop of the PCB trace can cause the  $V_{TT}$  voltage at the memory chip to be too low. Placing the MIC5166 as close as possible to the DDR memory will improve the load regulation performance.

#### Enable

The MIC5166 features an active-high enable input (EN) that allows on-off control of the regulator. The current through the device reduces to near "zero" when the device is shutdown, with only <0.2 $\mu$ A of leakage current. The EN input may be directly tied to V<sub>BIAS</sub>. The active high enable pin uses CMOS technology and the enable pin cannot be left floating; a floating enable pin may cause an indeterminate state on the output.

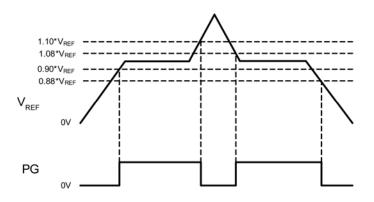

#### Power Good (PG)

The power-good (PG) output provides an under and over voltage fault flag for the  $V_{TT}$  output. The PG output remains high as long as  $V_{TT}$  is within ±10% range of  $V_{REF}$  and goes low if the output moves beyond this range.

Figure 3. Power Good Threshold

The PG has an open-drain output. A pull-up resistor must be connected to  $V_{\text{IBIAS}}$ ,  $V_{\text{IN}}$  or an external source. The external source voltage must not exceed the maximum rating of the pin. The PG pin can be connected to another regulator's enable pin for sequencing of the outputs.

#### **V<sub>BIAS</sub> Requirement**

A 1µF ceramic input capacitor is required on V<sub>BIAS</sub> pin. To achieve the ultra-fast transient response, the MIC5166 uses an all N-channel power output stage as shown in the Functional Diagram. The high-side N-channel MOSFET requires the V<sub>BIAS</sub> voltage to be 2.2V higher than the V<sub>TT</sub> to be able to fully enhance the high-side MOSFET.

#### V<sub>IN</sub> Requirement

$V_{\rm IN}$  is used to supply the rail voltage for the high-side Nchannel power output stage. It is normally connected to  $V_{\rm DDQ}$ , but it can be connected to a lower voltage to reduce power dissipation. In this case, the input voltage must be higher than the  $V_{\rm TT}$  voltage to ensure that the output stage is not operating in dropout.

## **Component Selection**

#### Input Capacitor

A  $10\mu F$  ceramic input capacitor is all that is required for most applications if it is close to a bulk capacitance.

The input capacitor must be placed on the same side of the board and next to the MIC5166 to minimize the dropout voltage and voltage ringing during transient and short circuit conditions. It is also recommended that each capacitor to be connected to the PGND directly, not through vias. X7R or X5R dielectric ceramic capacitors are recommended because of their temperature performance. X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much as 50% and 60% respectively over their operating temperature ranges. To use a ceramic chip capacitor with Y5V dielectric, the value must be much higher than an X7R ceramic.

#### **Output Capacitor**

As part of the frequency compensation, the MIC5166 requires two  $10\mu$ F ceramic output capacitors for best transient performance. To improve transient response, any other type of capacitor can be placed in parallel as long as the two  $10\mu$ F ceramic output capacitors are placed next to the MIC5166.

The output capacitor type and placement criteria are the same as the input capacitor. See the input capacitor section for a detailed description.

#### **Thermal Considerations**

The MIC5166 is packaged in the 3mm x 3mm  $\text{MLF}^{\text{®}}$ , a package that has excellent thermal performance. This maximizes heat transfer from the junction to the exposed pad (ePad) which connects to the ground plane. The size of the ground plane attached to the exposed pad determines the overall thermal resistance from the junction to the ambient air surrounding the printed circuit board.

#### **Thermal Design**

The most complicated design parameters to consider are thermal characteristics. Thermal design requires the following application-specific parameters:

- Maximum ambient temperature (T<sub>A</sub>)

- Output current (I<sub>OUT</sub>)

- Output voltage (V<sub>OUT</sub>)

- Input voltage (V<sub>IN</sub>)

- Ground current (I<sub>GND</sub>)

First, calculate the power dissipation of the regulator from these numbers and the device parameters from this datasheet.

$$P_{D} = (V_{IN} - V_{TT}) \times I_{OUT +} (V_{BIAS} \times I_{GND})$$

Eq. 1

where the ground current is approximated by using numbers from the "Electrical Characteristics" or "Typical Characteristics."

For example, given an expected maximum ambient temperature (T<sub>A</sub>) of 70°C with V<sub>IN</sub> = 1.2V, V<sub>BIAS</sub> = 3.3V, V<sub>TT</sub> = 0.9V, and I<sub>OUT</sub> = 3A, first calculate the expected P<sub>D</sub> using Equation 1:

Next, determine the junction temperature for the expected power dissipation above using the thermal resistance ( $\theta_{JA}$ ) of the 10-pin 3mm × 3mm MLF<sup>®</sup> (YML) adhering to the following criteria for the PCB design (1oz. copper and 100mm<sup>2</sup> copper area for the MIC5166):

$$T_{J} = (\theta_{JA} \times P_{D}) + T_{A} = (60.7^{\circ}C/W \times 0.90528W) + 70^{\circ}C$$

= 124.95°C Eq. 3

To determine the maximum power dissipation allowed that would not exceed the IC's maximum junction temperature ( $125^{\circ}C$ ) when operating at a maximum ambient temperature of  $70^{\circ}C$ :

#### **Thermal Measurements**

It is always wise to measure the IC's case temperature to make sure that it is within its operating limits. Although this might seem like a very elementary task, it is very easy to get erroneous results. The most common mistake is to use the standard thermocouple that comes with the thermal voltage meter. This thermocouple wire gauge is large, typically 22 gauge, and behaves like a heatsink, resulting in a lower case measurement. There are two suggested methods for measuring the IC case temperature: a thermocouple or an infrared thermometer. If a thermocouple is used, it must be constructed of 36 gauge wire or higher to minimize the wire heatsinking effect. In addition, the thermocouple tip must be covered in either thermal grease or thermal glue to make sure that the thermocouple junction is making good contact to the case of the IC. This thermocouple from Omega (5SC-TT-K-36-36) is adequate for most applications.

To avoid this messy thermocouple grease or glue, an infrared thermometer is recommended. Most infrared thermometers' spot size is too large for an accurate reading on small form factor ICs. However, an IR thermometer from Optris has a 1mm spot size, which makes it ideal for the 3mm x 3mm MLF<sup>®</sup> package.

#### Sequencing

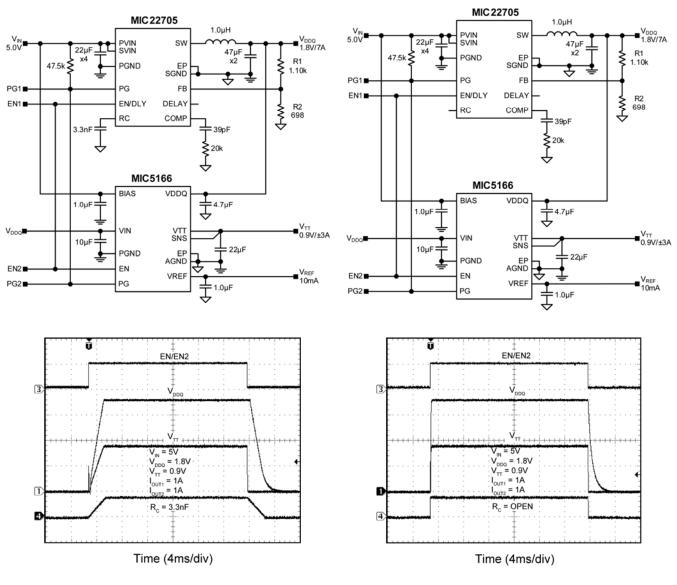

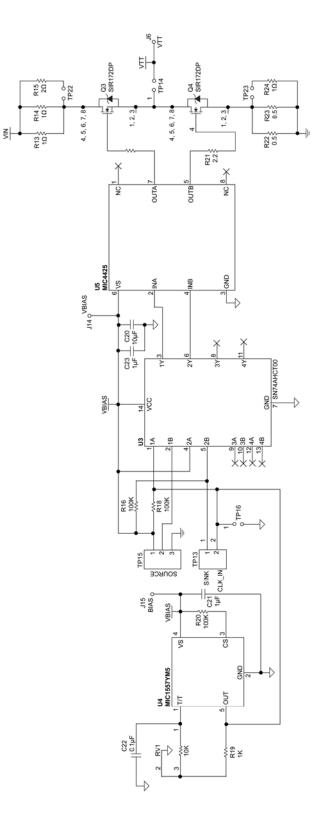

The following diagrams illustrate methods for connecting MIC5166's to achieve sequencing requirements:

Figure 6. Turn-On Sequence with Soft-Start (RC = 3.3nF)

## PCB Layout Guidelines

## Warning!!! To minimize EMI and output noise, follow these layout recommendations

PCB Layout is critical to achieve reliable, stable and efficient performance. A ground plane is required to control EMI and minimize the inductance in power, signal and return paths.

The following guidelines should be followed to insure proper operation of the MIC5166 converter.

#### IC

- The 10µF ceramic capacitor, which is connected to the VIN pin, must be located right at the IC. The VDDQ pin is very noise sensitive and placement of the capacitor is very critical. Use wide traces to connect to the VDDQ and AGND pins.

- The signal ground pin (AGND) must be connected directly to the ground planes. Do not route the AGND pin to the PGND Pad on the top layer.

- Place the IC close to the point-of-load (POL).

- Use wide traces to route the input and output power lines.

- Signal and power grounds should be kept separate and connected at only one location.

#### Input Capacitor

- A 10µF X5R or X7R dielectric ceramic capacitor is recommended on each of the VIN pins for bypassing.

- Place the input capacitors on the same side of the board and as close to the IC as possible.

- Keep both the VIN pin and PGND connections short.

- Place several vias to the ground plane close to the input capacitor ground terminal.

- Use either X7R or X5R dielectric input capacitors. Do not use Y5V or Z5U type capacitors.

- Do not replace the ceramic input capacitor with any other type of capacitor. Any type of capacitor can be placed in parallel with the input capacitor.

- If a Tantalum input capacitor is placed in parallel with the input capacitor, it must be recommended for switching regulator applications and the operating voltage must be derated by 50%.

- In "Hot-Plug" applications, a Tantalum or Electrolytic bypass capacitor must be used to limit the over-voltage spike seen on the input supply with power is suddenly applied.

#### Output Capacitor

- Use a wide trace to connect the output capacitor ground terminal to the input capacitor ground terminal.

- Phase margin will change as the output capacitor value and ESR changes. Contact the factory if the output capacitor is different from what is shown in the BOM.

- The feedback divider network must be place close to the IC with the bottom of R2 connected to AGND.

- The feedback trace should be separate from the power trace and connected as close as possible to the output capacitor. Sensing a long high current load trace can degrade the DC load regulation.

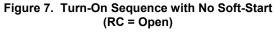

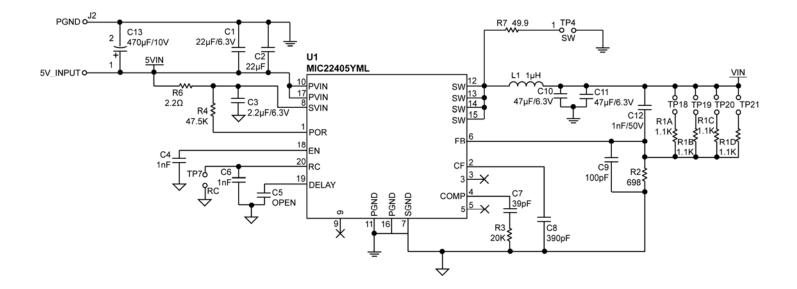

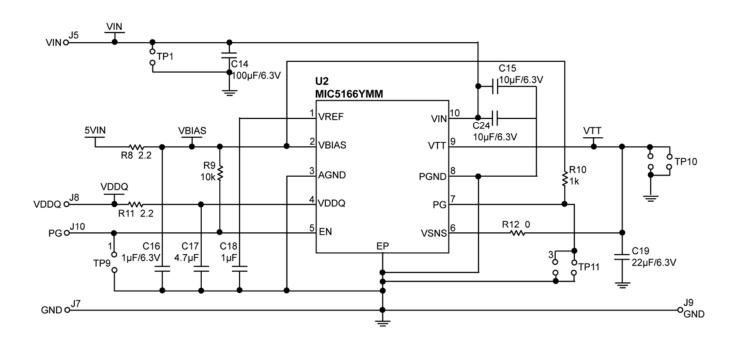

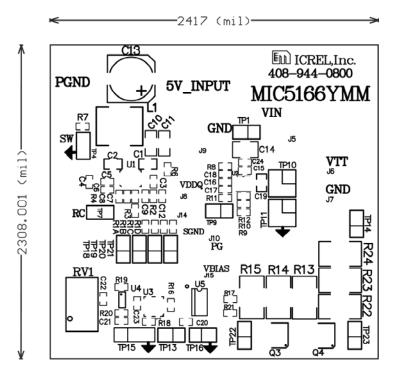

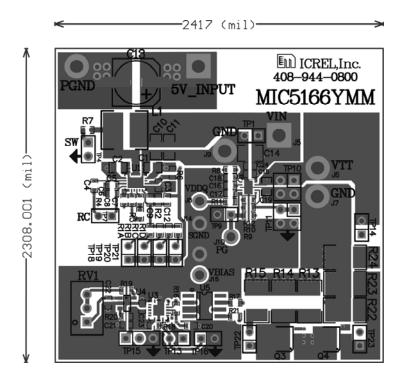

## **Evaluation Board Schematics**

## **Evaluation Board Schematics (Continued)**

## **Bill of Materials**

| ltem               | Part Number        | Manufacturer          | Description                               | Qty. |

|--------------------|--------------------|-----------------------|-------------------------------------------|------|

|                    | 08056D226MAT       | AVX <sup>(3)</sup>    |                                           |      |

| C1, C2, C19        | C2012X5R0J226K     | TDK <sup>(2)</sup>    | 22µF, 6.3V, ceramic capacitor, X5R, 0805  | 3    |

|                    | GRM21BR60J226ME39L | Murata <sup>(1)</sup> |                                           |      |

|                    | 08056D225KAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C3                 | C2012X5R0J225K     | TDK <sup>(2)</sup>    | 2.2µF, 6.3V, ceramic capacitor, X5R, 0805 | 1    |

|                    | GRM21BR60J225KA01L | Murata <sup>(1)</sup> |                                           |      |

|                    | 06035C102KAT       | AVX <sup>(3)</sup>    |                                           |      |

| C4, C6, C12        | C1608X7R1H102K     | TDK <sup>(2)</sup>    | 1nF, 50V, ceramic capacitor, X7R, 0603    | 3    |

|                    | GRM188R71H102KA01D | Murata <sup>(1)</sup> |                                           |      |

|                    | 06035A390JAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C7                 | C1608C0G1H390J     | TDK <sup>(2)</sup>    | 39pF, 50V, ceramic capacitor, NPO, 0603   | 1    |

|                    | GRM1885C1H390JA01D | Murata <sup>(1)</sup> |                                           |      |

|                    | 06035A391JAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C8                 | C1608C0G1H391J     | TDK <sup>(2)</sup>    | 390pF, 50V, ceramic capacitor, NPO, 0603  | 1    |

|                    | GRM188R71H391KA01D | Murata <sup>(1)</sup> |                                           |      |

|                    | 06035A101JAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C9                 | C1608C0G1H101J     | TDK <sup>(2)</sup>    | 100pF, 50V, ceramic capacitor, NPO, 0603  | 1    |

|                    | GRM1885C1H101JA01D | Murata <sup>(1)</sup> |                                           |      |

|                    | 12066D476MAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C10, C11           | C3216X5R0J476M     | TDK <sup>(2)</sup>    | 47µF, 6.3V, ceramic capacitor, X5R,1206   | 2    |

|                    | GRM31CR60J476ME19L | Murata <sup>(1)</sup> |                                           |      |

|                    | 12106D107MAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C14                | C3225X5R0J107M     | TDK <sup>(2)</sup>    | 100µF, 6.3V, ceramic capacitor, X5R, 1210 | 1    |

|                    | GRM32ER60J107ME20L | Murata <sup>(1)</sup> |                                           |      |

|                    | 06036D106MAT       | AVX <sup>(3)</sup>    |                                           |      |

| C15, C20, C24      | FP3-1R0-R          | TDK <sup>(2)</sup>    | 10µF, 6.3V, ceramic capacitor, X5R, 0603  | 3    |

|                    | GRM188R60J106ME47D | Murata <sup>(1)</sup> |                                           |      |

|                    | 06036D105KAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C16, C18, C21, C23 | C1608X5R0J105K     | TDK <sup>(2)</sup>    | 1µF, 6.3V, ceramic capacitor, X5R, 0603   | 4    |

|                    | GRM188R60J105KA01D | Murata <sup>(1)</sup> | 1                                         |      |

|                    | 06036D475KAT2A     | AVX <sup>(3)</sup>    |                                           |      |

| C17                | C1608X5R0J475M     | TDK <sup>(2)</sup>    | 4.7µF, 6.3V, ceramic capacitor, X5R, 0603 | 1    |

|                    | C1608X5R0J475M     | Murata <sup>(1)</sup> | • • • • • •                               |      |

## **Bill of Materials (Continued)**

| Item                     | Part Number        | Manufacturer               | Description                                       | Qty. |  |

|--------------------------|--------------------|----------------------------|---------------------------------------------------|------|--|

| C5                       |                    |                            | N.U. 0603 ceramic capacitor                       | 1    |  |

|                          | 06035C104KAT2A     | AVX <sup>(3)</sup>         |                                                   |      |  |

| C22                      | C1608X7R1H104K     | TDK <sup>(2)</sup>         | 0.1µF, 50V, ceramic capacitor, X7R, 0603          | 1    |  |

|                          | GRM188R71H104KA93D | Murata <sup>(1)</sup>      |                                                   |      |  |

| C13                      | EEU-FC1A471        | Panasonic <sup>(4)</sup>   | 470µF/10V, Elect., 20%, 8x11.5, Radial            | 1    |  |

| L1                       | FP3-1R0-R          | Cooper <sup>(5)</sup>      | 1µH,6.26A Inductor                                | 1    |  |

| Q3, Q4                   | NDS8425            | Fairchild <sup>(7)</sup>   | MOSFET, N-CH 20V 7.4A 8-SOIC                      | 2    |  |

| R1A                      | CRCW0603300RFKEA   | Vishay Dale <sup>(6)</sup> | 300Ω, resistor, 1%, 0603                          |      |  |

| R1B                      | CRCW06031101FKEA   | Vishay Dale <sup>(6)</sup> | 510Ω, resistor, 1%, 0603                          |      |  |

| R1C                      | CRCW0603806RFKEA   | Vishay Dale <sup>(6)</sup> | 806Ω, resistor, 1%, 0603                          | 1    |  |

| R1D                      | CRCW06031K10FKEA   | Vishay Dale <sup>(6)</sup> | 1.1K, resistor, 1%, 0603                          |      |  |

| R2                       | CRCW0603698RFKEA   | Vishay Dale <sup>(6)</sup> | 698Ω, resistor, 1%, 0603                          | 1    |  |

| R3                       | CRCW06032002FKEA   | Vishay Dale <sup>(6)</sup> | 20K, resistor, 1%, 0603                           | 1    |  |

| R4                       | CRCW06034752FKEA   | Vishay Dale <sup>(6)</sup> | 47.5K, resistor, 1%, 0603                         | 1    |  |

| R6, R8, R11,<br>R17, R21 | CRCW06032R20RFKEA  | Vishay Dale <sup>(6)</sup> | 2.2Ω, resistor, 1%, 0603                          | 5    |  |

| R7                       | CRCW060349R9RFKEA  | Vishay Dale <sup>(6)</sup> | 49.9Ω, resistor, 1%, 0603                         | 1    |  |

| R9                       | CRCW06031002FKEA   | Vishay Dale <sup>(6)</sup> | 10K, resistor, 1%, 0603                           | 1    |  |

| R10, R19                 | CRCW06031K00FKEA   | Vishay Dale <sup>(6)</sup> | 1K, resistor, 1%, 0603                            | 2    |  |

| R12                      | CRCW0603000RFKEA   | Vishay Dale <sup>(6)</sup> | 0Ω, resistor, 1%, 0603                            | 1    |  |

| R13, R14, R24            | CRCW25121R00FKEGHP | Vishay Dale <sup>(6)</sup> | 1Ω, resistor, 1.5W, 1%, 2512                      | 3    |  |

| R15                      | CRCW25122R00JNEG   | Vishay Dale <sup>(6)</sup> | 2Ω, resistor, 1.5W, 1%, 2512                      | 1    |  |

| R16, R18, R20            | CRCW06031003FKEA   | Vishay Dale <sup>(6)</sup> | 100K, resistor, 1%, 0603                          | 3    |  |

| R22, R23                 | LR2512-R50FW       | Vishay Dale <sup>(6)</sup> | 0.5Ω, resistor, 1.5W, 1%, 2512                    | 2    |  |

| RV1                      | PV36W103C01B00     | Murata <sup>(1)</sup>      | Pot, 10KΩ, 0.5W, 9.6x5xx10                        | 1    |  |

| U1                       | MIC22405YML        | Micrel <sup>(9)</sup>      | 4A, Synchronous Buck Regulator                    | 1    |  |

| U2                       | MIC5166YMM         | Micrel <sup>(9)</sup>      | 3A High-Speed Low V <sub>IN</sub> DDR Terminator  | 1    |  |

| U3                       | SN74AHCT00RGYR     | TI <sup>(8)</sup>          | Quad, 2IN Pos-NAND Gate, 14-pin, QFN              | 1    |  |

| U4                       | MIC1557YM5         | Micrel <sup>(9)</sup>      | 5MHz RC Timer Oscillator                          | 1    |  |

| U5                       | MIC4425            | Micrel <sup>(9)</sup>      | 3A Dual Inverting and Non-Inverting MOSFET Driver | 1    |  |

Notes:

1. Murata Tel: <u>www.murata.com</u>.

- 2. TDK: www.tdk.com.

- 3. AVX: <u>www.avx.com</u>.

- 4. Panasonic: <u>www.panasonic.com</u>.

- 5. Cooper: <u>www.cooper.com</u>

- 6. Vishay Dale: <u>www.vishay.com</u>.

- 7. Fairchild: <u>www.fairchildsemi.com</u>.

- 8. TI: <u>www.ti.com</u>

- 9. Micrel, Inc.: <u>www.micrel.com</u>.

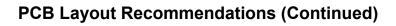

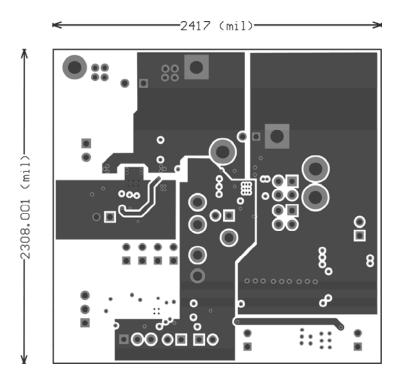

## **PCB Layout Recommendations**

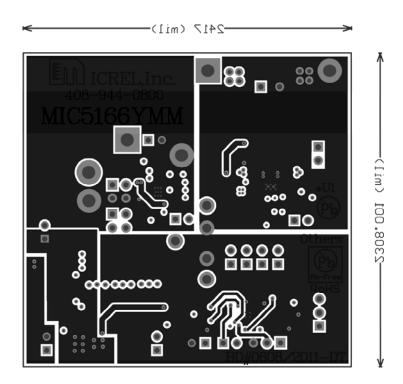

**Top Silk**

**Copper Layer 1**

Copper Layer 2

Copper Layer 3

## PCB Layout Recommendations (Continued)

Copper Layer 4

**Bottom Silk**

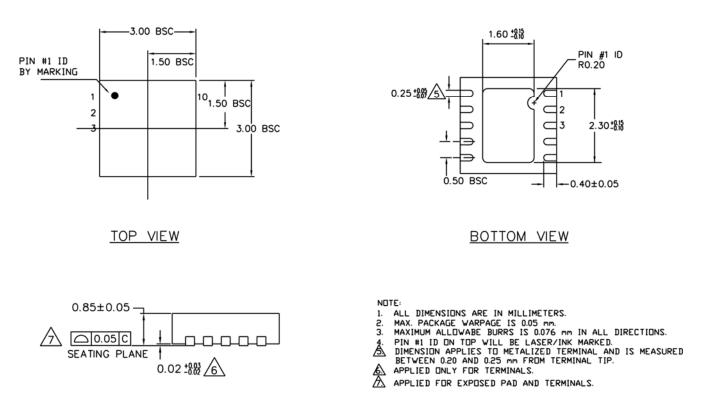

## **Package Information**

SIDE VIEW

10-Pin 3mm × 3mm MLF<sup>®</sup> (ML)

## **Recommended Landing Pattern**

LP # MLF33D-10LD-LP-1 All units are in mm Tolerance ± 0.05 if not noted

Red circle indicates Thermal Via. Size should be .300mm – .350mm in diameter and it should be connected to GND plane for maximum thermal performance.

10-Pin 3mm × 3mm MLF<sup>®</sup> Land Pattern

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2012 Micrel, Incorporated.