Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### MIC95410

# 6.6mΩ R<sub>DS(ON)</sub>, 7A, 5.5V V<sub>IN</sub> Load Switch in 1.2mm × 2.0mm QFN Package

### **General Description**

The MIC95410 is a high-side load switch for computing and ultra-dense embedded computing boards where high-current low-voltage rails from sub-1V to 5.5V have to be sectioned. The integrated  $6.6m\Omega$   $R_{\rm DS(ON)}$  N-channel MOSFET ensures low voltage drop and low power dissipation while delivering up to 7A of load current.

The MIC95410 is internally powered by a separated bias voltage from 2.7V to 9V. It includes a TTL-logic level to gate a voltage translator driving a charge pump, and an output discharge function when disabled. The OFF-state current from bias supply (VS) and the power switch OFF-state leakage current ( $I_{OFF}$ ) are both below 1 $\mu$ A.

The MIC95410 provides user-adjustable slew-rate-controlled turn-on to limit the inrush current to the input supply voltage.

The MIC95410 is available in a thermally efficient, space-saving 10-pin 1.2mm x 2.0mm QFN package with 0.5mm pin pitch and an operating junction temperature range from -40°C to +125°C.

Datasheets and support documentation are available on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

#### **Features**

- Ultra-low R<sub>DS(on)</sub>: 6.6mΩ typical

- True 7A current capability

- Power rail switching from sub-1V to 5.5V

- Bias voltage form 2.7V to 9V

- ≤1µA OFF-state bias supply current

- ≤1µA OFF-state power switch leakage current

- Adjustable slew rate for inrush current limiting by external capacitor

- · Load discharge

- TTL-compatible control input

- 10-pin 1.2mm × 2.0mm QFN package, 0.5mm pin pitch

- -40°C to +125°C junction temperature range

### **Applications**

- Embedded computing boards

- Servers

- Data storage equipment

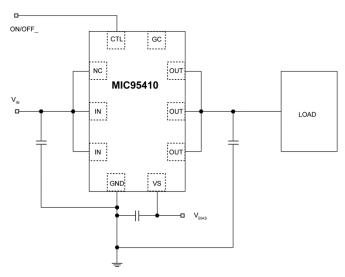

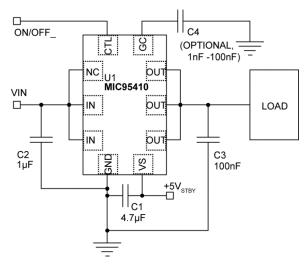

### **Typical Application**

MIC95410 Load Switch

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • <a href="http://www.micrel.com">http://www.micrel.com</a>

October 30, 2014 Revision 1.0

### **Ordering Information**

| Part Number <sup>(1)</sup> | Marking | Junction Temperature<br>Range | Package <sup>(1)</sup>   | Lead Finish |  |

|----------------------------|---------|-------------------------------|--------------------------|-------------|--|

| MIC95410YFL                | 9541    | -40°C to +125°C               | 10-Pin 1.2mm × 2.0mm QFN | Pb-Free     |  |

#### Note:

1. QFN is a GREEN, RoHS-compliant package. Lead finish is Matte Tin. Mold compound is Halogen Free.

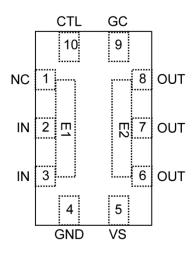

## **Pin Configuration**

10-Pin 1.2mm × 2.0mm QFN (FL) (Top View)

## **Pin Description**

| Pin Number  | Pin Name | Pin Function                                                                                                                              |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | NC       | Not internally connected. It is recommended to connect pin 1 to IN such that the width of the input trace can be maximized in the layout. |

| 2, 3, E1    | IN       | Power switch input (up to 5.5V).                                                                                                          |

| 4           | GND      | Driver ground and discharge return.                                                                                                       |

| 5           | VS       | Bias supply input (2.7V to 9V). Bypass with 4.7μF ceramic capacitor to GND.                                                               |

| 6, 7, 8, E2 | OUT      | Power switch output.                                                                                                                      |

| 9           | GC       | Gate connection of power FET. Add a ceramic capacitor from GC to ground GND for slew rate control.                                        |

| 10          | CTL      | Control input. TTL compatible. Logic high enables the power switch. A logic low disables the power switch and discharges OUT.             |

## Absolute Maximum Ratings<sup>(2)</sup>

| IN, OUT to GND                                        | 0.3V to +6V             |

|-------------------------------------------------------|-------------------------|

| IN to OUT                                             | 0.3V to +6V             |

| IN to GC                                              | +6V                     |

| VS to GND                                             | 0.6V to +10V            |

| CTL to GND                                            | 0.6V to V <sub>VS</sub> |

| Lead Temperature (soldering, 10s)                     | 260°C                   |

| Storage Temperature (Ts)<br>ESD Rating <sup>(4)</sup> | 65°C to +150°C          |

| ESD Rating <sup>(4)</sup>                             |                         |

| Human Body Model                                      | 1.5kV                   |

| Machine Model                                         | 150V                    |

## Operating Ratings<sup>(3)</sup>

| Input Voltage (V <sub>IN</sub> )           | +5.5\          |

|--------------------------------------------|----------------|

| Bias Voltage (V <sub>VS</sub> )            | +2.7V to +9\   |

| Gate Connection Voltage (V <sub>GC</sub> ) | 0V to +11\     |

| ON-state current (I <sub>IN</sub> )        | 7/             |

| Junction Temperature (T <sub>J</sub> )     | 40°C to +125°C |

| Junction Thermal Resistance <sup>(5)</sup> |                |

| 10-pin 1.2mm × 2mm QFN ( $\theta_{JA}$ ).  | 60°C/W         |

### Electrical Characteristics<sup>(6)</sup>

$V_{VS} = V_{IN} = V_{CTL} = 5V, \ C_{VS} = 4.7 \mu F, \ C_{IN} = 1 \mu F, \ C_{OUT} = 100 nF, \ R_{LOAD} = 50 \Omega \ unless \ otherwise \ specified \ (see Typical Application Schematic). Typical values at T_A = 25°C; Bold indicates values/limits over -40°C < T_J < +125°C.$

| Symbol           | Parameter                                                                                                                       | Condition                                                                                                                                                                                                                 | Min.            | Тур.       | Max.                                      | Units                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|-------------------------------------------|--------------------------|

|                  | Supply Current                                                                                                                  | $\begin{split} &V_{VS}=3.3V,\ V_{CTL}=0V\\ &V_{VS}=3.3V,\ V_{CTL}=3.3V,\ IN=\text{open},\ OUT=\text{open}\\ &V_{VS}=3.3V,\ V_{CTL}=3.3V,\ IN=\text{open},\ OUT=\text{open},\\ &T_A=T_{,I}=25^{\circ}\text{C} \end{split}$ |                 | 0.1<br>70  | <b>1</b><br><b>140</b><br>90              | μΑ<br>μΑ<br>μΑ           |

| I <sub>S</sub>   |                                                                                                                                 | $\begin{split} &V_{VS}=5V,\ V_{CTL}=0V\\ &V_{VS}=5V,\ V_{CTL}=5V,\ IN=open,\ OUT=open\\ &V_{VS}=5V,\ V_{CTL}=5V,\ IN=open,\ OUT=open,\\ &T_A=T_J=25^{\circ}C \end{split}$                                                 |                 | 0.1<br>150 | 1<br>300<br>200                           | μΑ<br>μΑ<br>μΑ           |

| V <sub>CTL</sub> | Control Input Voltage                                                                                                           | $2.7V \le V_{VS} \le 9V$ , logic-0<br>$2.7V \le V_{VS} \le 5V$ , logic-1<br>$5V < V_{VS} \le 9V$ , logic-1                                                                                                                | 0<br>2.0<br>2.4 |            | 0.8<br>V <sub>vs</sub><br>V <sub>vs</sub> | V<br>V<br>V              |

| I <sub>CTL</sub> | Control Input Current                                                                                                           | 2.7V ≤ V <sub>VS</sub> ≤ 9V                                                                                                                                                                                               |                 | 0.01       | 1                                         | μΑ                       |

| C <sub>CTL</sub> | Control Input Capacitance                                                                                                       |                                                                                                                                                                                                                           |                 | 5          |                                           | pF                       |

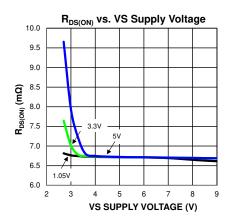

| R <sub>ON</sub>  | Switch ON-Resistance                                                                                                            | $V_{VS} = 2.7V$ , $V_{IN} = 1V$ , $I_{IN} = I_{OUT} = 4A$<br>$V_{VS} = 3.3V$ , $V_{IN} = 3.3V$ , $I_{IN} = I_{OUT} = 4A$<br>$V_{VS} = 5V$ , $V_{IN} = 5V$ , $I_{IN} = I_{OIIT} = 4A$                                      |                 | 6.6<br>6.6 | 9.9<br>9.9<br>9.9                         | $m\Omega$ $m\Omega$      |

| I <sub>OFF</sub> | Switch Input Leakage Current                                                                                                    | $V_{VS} = 5V, V_{IN} = 5.5V, V_{CTL} = 0V$                                                                                                                                                                                |                 | 0.02       | 1                                         | μΑ                       |

| I <sub>GC</sub>  | Gate Charge Current $ \begin{array}{c} V_{GC} = 4.0V, \; R_{LOAD} = \infty \\ V_{GC} = 0.5V, \; R_{LOAD} = \infty \end{array} $ |                                                                                                                                                                                                                           |                 | 27<br>630  |                                           | μ <b>Α</b><br>μ <b>Α</b> |

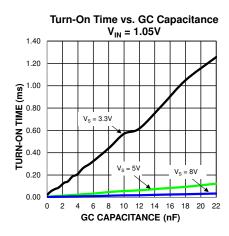

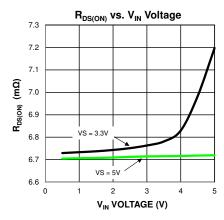

| T <sub>ON</sub>  | Turn-On Time <sup>(7)</sup>                                                                                                     | $C_{GC} = 10nF, V_{IN} = 5V$<br>$C_{GC} = 100nF, V_{IN} = 1V$                                                                                                                                                             |                 | 1.1<br>0.4 | 2.0<br>1.0                                | ms<br>ms                 |

## **Electrical Characteristics**(6) (Continued)

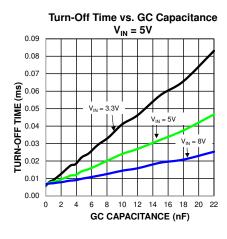

| T <sub>OFF</sub> | Turn-Off Time <sup>(8)</sup>                                      | $C_{GC} = 10nF, \ V_{IN} = 5V, \ C_3 = 0 \mu F$ $C_{GC} = 100nF, \ V_{IN} = 1V, \ C_3 = 0 \mu F$        | 30<br>150         | 60<br>300 | μs<br>μs       |

|------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|-----------|----------------|

| $R_D$            | Discharge Resistance                                              | $V_{OUT} = 5V, R_{LOAD} = \infty$ $V_{OUT} = 4V, R_{LOAD} = \infty$ $V_{OUT} = 2.5V, R_{LOAD} = \infty$ | 2.3<br>2.0<br>1.7 |           | kΩ<br>kΩ<br>kΩ |

| V <sub>D</sub>   | Discharge Diode Forward Drop (V <sub>OUT</sub> -V <sub>CG</sub> ) | $V_{CTL} = 0V$ , $I_{OUT} = -10\mu A$                                                                   | 0.5               | 0.75      | V              |

#### Notes:

- 2. Exceeding the absolute maximum ratings may damage the device.

- 3. The device is not guaranteed to function outside its operating ratings.

- 4. Devices are ESD sensitive. Handling precautions are recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 5. Junction-to-Ambient Thermal Resistance  $\theta_{JA}$  is measured using the Evaluation Board as described in section PCB Layout Recommendations.

- 6. Specification for packaged product only.

- 7. The turn-on time is defined as the time it takes from asserting CTL to  $V_{OUT}$  reaching 90% of  $V_{IN}$  (rising).

- 8. The turn-off time is defined as the time it takes from the falling edge of CTL to V<sub>OUT</sub> reaching 90% of V<sub>IN</sub> (falling).

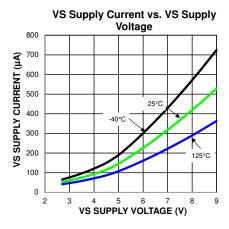

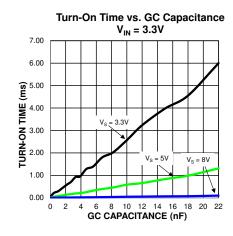

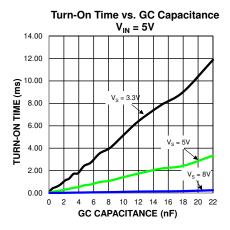

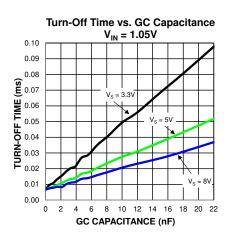

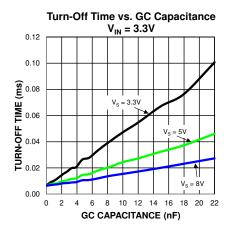

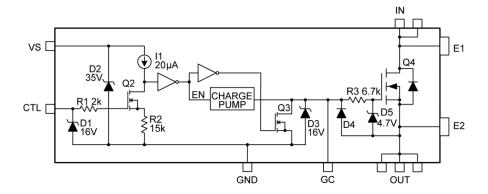

### **Typical Characteristics**

## **Typical Characteristics (Continued)**

### **Functional Characteristics**

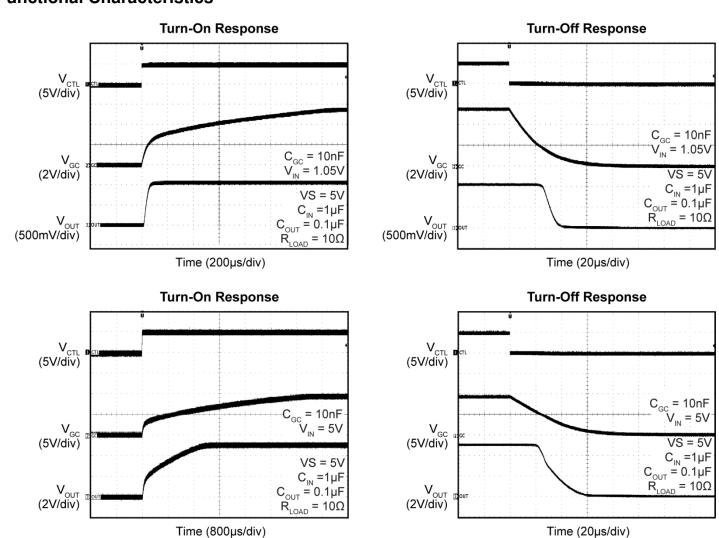

### **Functional Diagram**

### **Functional Description**

The MIC95410 is a non-inverting device. Applying a logic-high signal to control input (CTL) turns on an internal N-channel MOSFET switch (Q4). The gate control (GC) output can be used to reduce the turn-on speed of the MOSFET by connecting a capacitor from GC to ground.

#### Supply

Supply (VS) is rated for +2.7V to +9V. An external  $4.7\mu F$  capacitor (minimum) is recommended.

#### **ON/OFF Control**

Control (CTL) is a TTL-compatible input. CTL must be forced high or low by an external signal. A floating input may cause unpredictable operation.

A high input turns on Q2, which sinks the output of current source I1, and makes the input of the first inverter low. The inverter output becomes high, enabling the charge pump.

#### **Charge Pump**

The charge pump is enabled when CTL is logic high. The charge pump is powered from VS and consists of an oscillator and a 4x voltage multiplier . Output voltage is limited to 16V by an internal Zener diode. The charge pump output current raises the voltage on the GC pin and causes the internal MOSFET Q4 to be turned on. The gate-source voltage of Q4 is internally limited by R3 and D5.

The charge pump oscillator operates from approximately 70kHz to approximately 100kHz depending upon the supply voltage and temperature.

#### **Gate Control**

The charge pump output is connected directly to the GC output. The charge pump is active only when CTL is high. When CTL is low, Q3 is turned on by the second inverter and discharges the gate of Q4 to force it off.

If CTL is high, and the voltage applied to VS drops to zero, the gate output will be floating and unpredictable.

#### **ESD Protection**

D1 and D2 clamp positive and negative ESD voltages. R1 isolates the gate of Q2 from sudden changes on the CTL input. Zener D3 also clamps ESD voltages for the GC output. D4 protects the gate of Q4 from ESD on the GC pin.

### **Application Information**

#### Turn-On

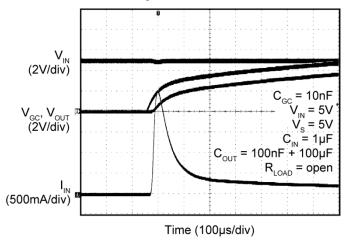

The MIC95410 is turned on by setting CTL  $\geq$ 2.0V. The CTL pin enables the MIC95410 which releases the pull-down on GC and starts the charge pump. When the charge pump is turned on, the OUT waveform will exhibit a two-stage rise-time. In the first stage, a higher drive current causes GC to rise rapidly, while in the second phase a lower drive current causes GC to rise more slowly. This is shown in Figure 1 below. With a purely capacitive load  $C_{\text{OUT}}$ , the current exhibits an initial peak ( $I_{\text{PEAK}}$ ) during the first stage and a limiting, flattening value  $I_{\text{CHARGE}}$  in the second stage.

Figure 1. OUT voltage and inrush current waveform during turn-on (IN current scale is 500mA/div)

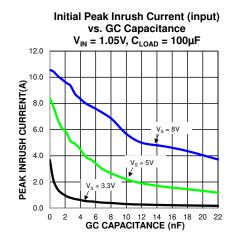

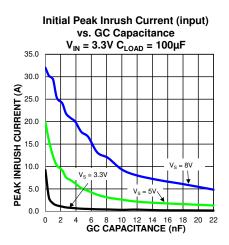

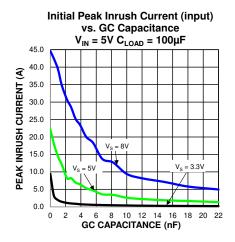

An analytical prediction of  $I_{PEAK}$  is complicated because it involves many factors. For an estimation of  $I_{PEAK}$ , and selection of the GC capacitor, the user can refer to the corresponding Typical Performance Characteristics plots (given for  $C_{OUT}=100\mu F$ ), and scale the values in proportion to the actual capacitive load. Note that these plots do not include any additional DC loads because large load capacitances are the most important factor to consider in initial peak inrush current estimation. DC contributions are either negligible at very low output voltage (e.g. resistive load) or typically activated when the OUT voltage has already approached its final value.

The input current during the second (flattening) stage can be estimated as shown in Equation 1:

$$I_{\mathit{CHARGE}} = \frac{I_{\mathit{STAGE2}} \times C_{\mathit{OUT}}}{C_{\mathit{GC}}}$$

Eq. 1

For example, if  $C_{GC}=10nF$ ,  $C_{OUT}=100\mu F$  (no additional DC load),  $I_{STAGE2}=27\mu A$  (see  $I_{GC}$  parameter in the Electrical Characteristics table) then we obtain  $I_{CHARGE}=0.27A$ . This calculation is in reasonable agreement with the measurement shown in Figure 1.

Note that for very low input voltages, the duration of the turn-on transition is likely to be dominated by the first stage, where the  $I_{GC}$  current is much stronger than in the second stage. In this case, an increase of the  $C_{GC}$  capacitance could be needed.

Also note that during turn-on the internal power switch can instantaneously dissipate a large amount of power due to the transition through the linear region. Depending upon the instantaneous values of load current and voltage, make sure the turn-on V-I trajectory stays within the Safe Operating Area plot shown in section Power Switch SOA.

#### Turn-Off

The turn-off of the MIC95410 is started by taking CTL to a logic low where the GC pin is pulled to GND with a resistive MOSFET switch of approximately  $2k\Omega$  (see MOSFET Q3 in the Functional Diagram). Pulling GC to GND will cause the power MOSFET to be turned off (see MOSFET Q4 in the Functional Diagram). Further, the diode D4 between the OUT pin and the GC pin turns on and discharges OUT with a controlled discharge path (D4-Q3).

#### **Power Dissipation Considerations**

The junction temperature  $(T_J)$  can be estimated from power dissipation, ambient temperature, and the junction-to-ambient thermal resistance  $(\theta_{JA})$ .

$$T_{J} = P_{DISS} \times \theta_{JA} + T_{A} \label{eq:TJ}$$

Eq. 2

For steady-state condition,  $P_{DISS}$  is calculated as  $I_{IN}^2 \times R_{ON(max)}$ .  $\theta_{JA}$  is found in the Operating Ratings section of the datasheet. This is the value of  $\theta_{JA}$  measured in still air on the evaluation kit board. Note that the actual  $\theta_{JA}$  in the final application is strongly dependent on the PCB layout, on the PCB thermal properties, as well as cooling techniques (e.g. forced convection vs. still air). Therefore, the  $\theta_{JA}$  value given for the evaluation kit board should be used with caution when trying to estimate  $T_J$  in the end user application.

#### **Power Switch SOA**

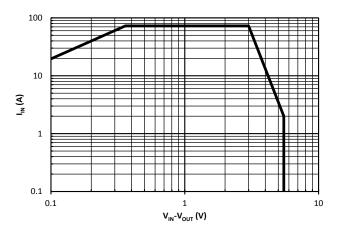

The safe operating area (SOA) curve shown in Figure 2 represents the boundary of maximum safe operating current and voltage for transient operation.

Figure 2. MIC95410 Power Switch Safe Operating Area

Ensure that the V-I trajectory stays within recommended SOA boundaries during the turn-on and turn-off transients. Also note that the SOA plot does not provide safe operating limits for continuous operation and it is only applicable for transient operation. For continuous (DC) operation, the allowable power dissipation limit is dictated by the ambient temperature  $\mathsf{T}_\mathsf{A}$  and the actual  $\theta_\mathsf{JA}$  of the device in the end user application as follows:

$$P_{DISS(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{J\!A}} \label{eq:pds}$$

Eq. 3

where  $T_{J(MAX)} = 125$ °C.

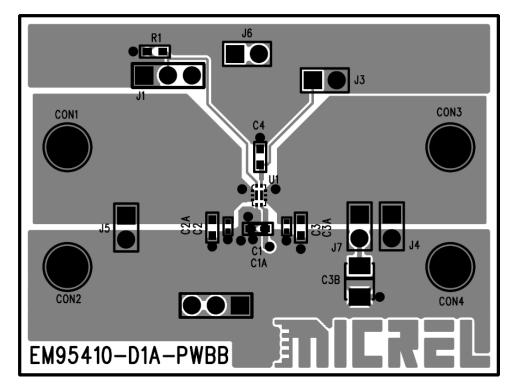

## **Typical Application Schematic**

### **Bill of Materials**

| Item | Part Number         | Manufacturer                 | Description                                                                                 | Qty.     |  |

|------|---------------------|------------------------------|---------------------------------------------------------------------------------------------|----------|--|

| C1   | C1005X5R1A475M050BC | TDK <sup>(9)</sup>           | 4.7μF, 10V, X5R, 20% size 0402 ceramic capacitor                                            | 1        |  |

| Ci   | GRM185R61A475ME11   | Murata <sup>(10)</sup>       | 4.7μF, 10V, X5R, 20% size 0603 ceramic capacitor                                            | <u> </u> |  |

| C2   | C1005X5R1A105M050BB | TDK                          | 1μF, 10V, X5R, 20% size 0402 ceramic capacitor                                              |          |  |

| 02   | GRM155R61A105ME01   | Murata                       |                                                                                             |          |  |

| C3   | C1005X5R1E104M050BC | TDK                          | 100nF, 25V, X5R, 20% size 0402 ceramic capacitor                                            |          |  |

| US   | GRM155R61E104MA87   | Murata                       | 10011F, 25 V, A5h, 20% Size 0402 ceramic capacitor                                          | ı        |  |

| C4   |                     |                              | 1nF to 100nF, 10%, size 0402 ceramic capacitor – optional (for inrush current control)      | 1        |  |

| U1   | MIC95410YFL         | Micrel, Inc. <sup>(11)</sup> | 6.6mΩ R <sub>DS(ON)</sub> , 7A, 5.5V <sub>IN</sub> Load Switch in 1.2mm × 2.0mm QFN Package | 1        |  |

#### Notes:

TDK: <u>www.global.tdk.com</u>

Murata: <u>www.murata.com</u>

11. Micrel, Inc.: www.micrel.com

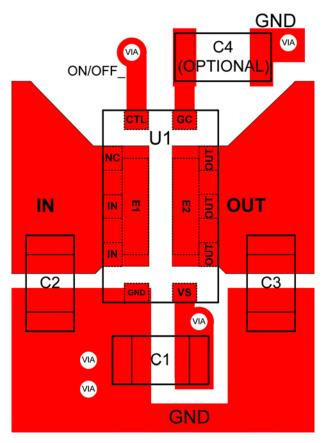

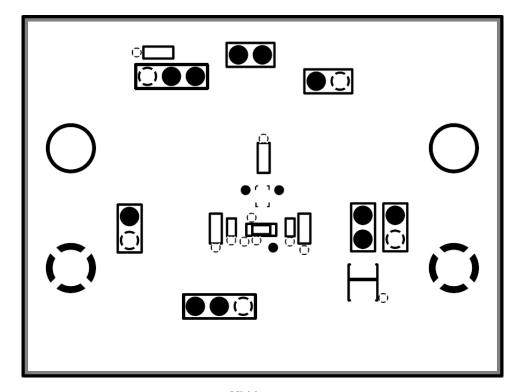

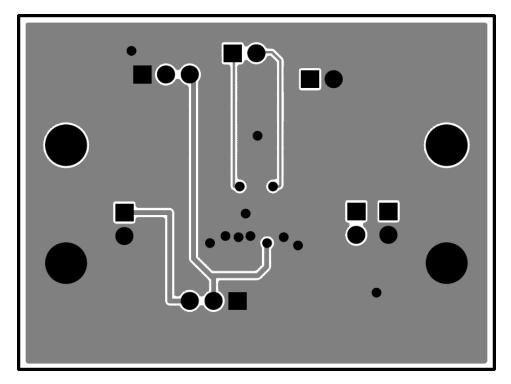

### **PCB Layout Recommendations**

The IN and OUT traces should be made as wide as possible because the main heat-sinking action will be performed by heat removal through the IN/E1 and OUT/E2 connections on the top layer. The traces should widen up as soon as space constraints allow it. In Figure 3 is a routing example of top layer connections.

Note that a two-layer routing is adequate for a very compact solution. In case multiple internal planes are

used, it is recommended to keep internal planes as solid as possible and to extend them under the MIC95410 and its vicinity (in special the IN and OUT top traces) in order to increase vertical, then lateral, heat transfer.

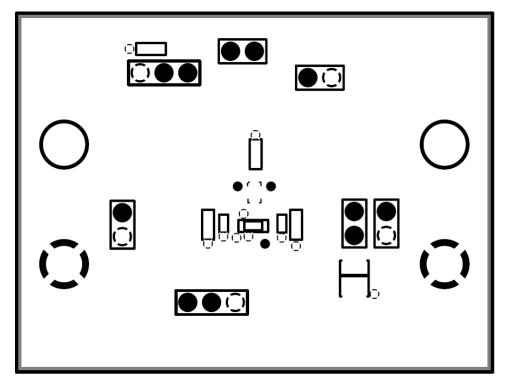

Another method is to copy the IN and OUT traces on the bottom layer and to stitch them through many thermal vias to the top layers IN and OUT connections, in particular in the immediate vicinity of the MIC95410 IC.

Figure 3. Top Layer Routing Example

## **PCB Layout Recommendations (Continued)**

**Top Layer**

Mid Layer 1

## **PCB Layout Recommendations (Continued)**

Mid Layer 2

**Bottom Layer (Top View)**

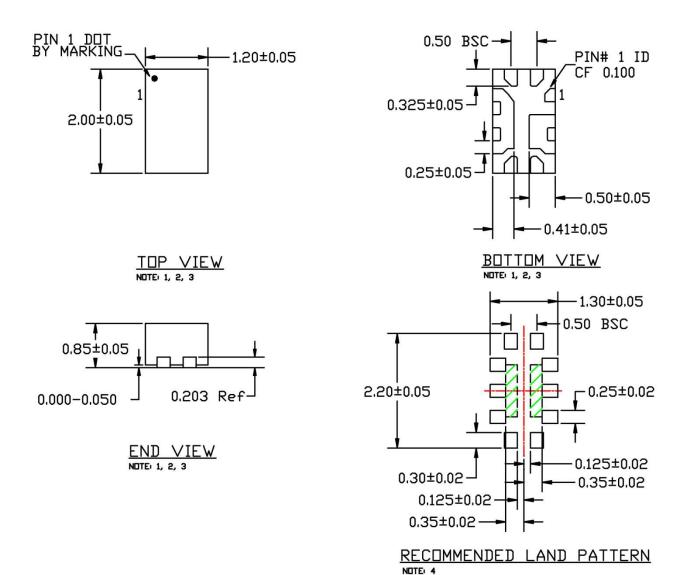

## Package Information<sup>(12)</sup>

### NOTE:

- 1. MAX PACKAGE WARPAGE IS 0.05mm.

- 2. MAX ALLOWABLE BURR IS 0.076mm IN ALL DIRECTIONS.

- 3. PIN #1 IS ON TOP WILL BE LASER MARKED.

- 4. GREEN SHADED AREAS INDICATE OPTIONAL SOLDER STENCIL OPENING FOR IMPROVED THERMAL PERFORMANCE.

### 10-Pin FQFN (FL)

#### Note:

12. Package information is correct as of the publication date. For updates and most current information, go to <a href="https://www.micrel.com">www.micrel.com</a>.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel, Inc. is a leading global manufacturer of IC solutions for the worldwide high performance linear and power, LAN, and timing & communications markets. The Company's products include advanced mixed-signal, analog & power semiconductors; high-performance communication, clock management, MEMs-based clock oscillators & crystal-less clock generators, Ethernet switches, and physical layer transceiver ICs. Company customers include leading manufacturers of enterprise, consumer, industrial, mobile, telecommunications, automotive, and computer products. Corporation headquarters and state-of-the-art wafer fabrication facilities are located in San Jose, CA, with regional sales and support offices and advanced technology design centers situated throughout the Americas, Europe, and Asia. Additionally, the Company maintains an extensive network of distributors and reps worldwide.

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this datasheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2014 Micrel, Incorporated.