# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **PN7150**

High performance full NFC Forum-compliant controller with integrated firmware and NCI interface

Rev. 3.3 — 4 July 2016

**Product data sheet**

## 1. Introduction

This document describes the functionality and electrical specification of the NFC Controller PN7150.

Additional documents describing the product functionality further are available for design-in support. Refer to the references listed in this document to get access to the full for full documentation provided by NXP.

#### 2. General description

Best plug'n play and high-performance full NFC solution PN7150 is a full NFC controller solution with integrated firmware and NCI interface designed for contactless communication at 13.56 MHz. It is compatible with NFC forum requirements.

PN7150 is designed based on learnings from previous NXP NFC device generation. It is the ideal solution for rapidly integrating NFC technology in any application, especially those running O/S environment like Linux and Android, reducing Bill of Material (BOM) size and cost, thanks to:

- Full NFC forum compliancy (see Ref. 1) with small form factor antenna

- Embedded NFC firmware providing all NFC protocols as pre-integrated feature

- Direct connection to the main host or microcontroller, by I<sup>2</sup>C-bus physical and NCI protocol

- · Ultra-low power consumption in polling loop mode

- Highly efficient integrated power management unit (PMU) allowing direct supply from a battery

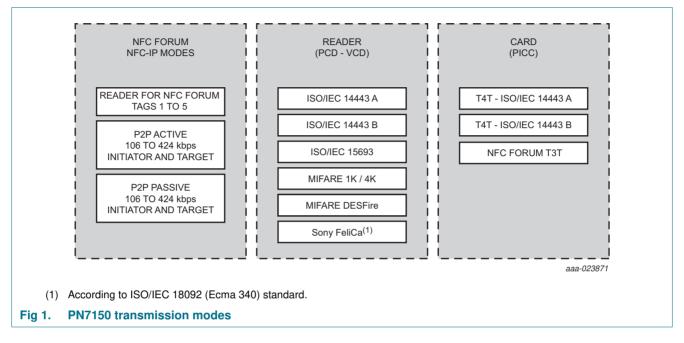

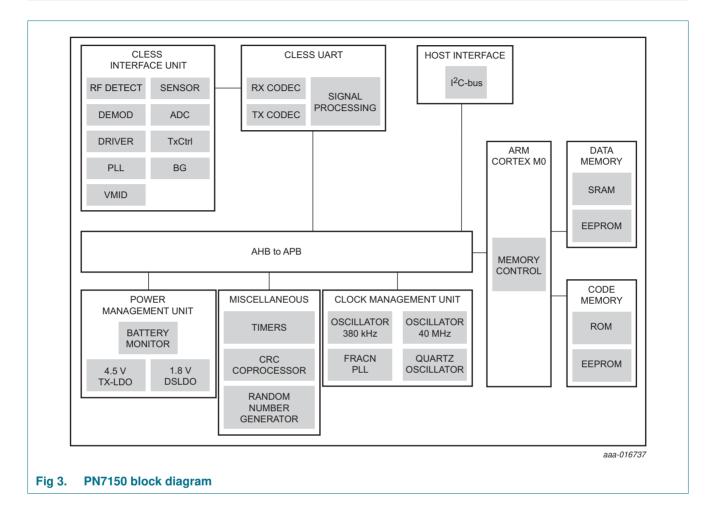

PN7150 embeds a new generation RF contactless front-end supporting various transmission modes according to NFCIP-1 and NFCIP-2, ISO/IEC14443, ISO/IEC 15693, MIFARE and FeliCa specifications. It embeds an ARM Cortex-M0 microcontroller core loaded with the integrated firmware supporting the NCI 1.0 host communication. It also allows to provide a higher output power by supplying the transmitter output stage from 3.0 V to 4.75 V.

The contactless front-end design brings a major performance step-up with on one hand a higher sensitivity and on the other hand the capability to work in active load modulation communication enabling the support of small antenna form factor.

Supported transmission modes are listed in Figure 1. For contactless card functionality, the PN7150 can act autonomously if previously configured by the host in such a manner.

PN7150 integrated firmware provides an easy integration and validation cycle as all the NFC real-time constraints, protocols and device discovery (polling loop) are being taken care internally. In few NCI commands, host SW can configure the PN7150 to notify for card or peer detection and start communicating with them.

#### 3. Features and benefits

- Includes NXP ISO/IEC14443-A, Innovatron ISO/IEC14443-B and NXP MIFARE crypto1 intellectual property licensing rights

- ARM Cortex-M0 microcontroller core

- Highly integrated demodulator and decoder

- Buffered output drivers to connect an antenna with minimum number of external components

- Integrated RF level detector

- Integrated Polling Loop for automatic device discovery

- RF protocols supported

- ◆ NFCIP-1, NFCIP-2 protocol (see <u>Ref. 8</u> and <u>Ref. 11</u>)

- ISO/IEC 14443A, ISO/IEC 14443B PICC, NFC Forum T4T modes via host interface (see <u>Ref. 3</u>)

- NFC Forum T3T via host interface

- ISO/IEC 14443A, ISO/IEC 14443B PCD designed according to NFC Forum digital protocol T4T platform and ISO-DEP (see <u>Ref. 1</u>)

- FeliCa PCD mode

- MIFARE PCD encryption mechanism (MIFARE 1K/4K)

- NFC Forum tag 1 to 5 (MIFARE Ultralight, Jewel, Open FeliCa tag, DESFire) (see <u>Ref. 1</u>)

- ISO/IEC 15693/ICODE VCD mode (see <u>Ref. 9</u>)

- Supported host interfaces

- NCI protocol interface according to NFC Forum standardization (see Ref. 2)

- ◆ I<sup>2</sup>C-bus High-speed mode (see Ref. 4)

- Integrated power management unit

- Direct connection to a battery (2.3 V to 5.5 V voltage supply range)

- Support different Hard Power-Down/Standby states activated by firmware

- Autonomous mode when host is shut down

- Automatic wake-up via RF field, internal timer and I<sup>2</sup>C-bus interface

- Integrated non-volatile memory to store data and executable code for customization

#### **Applications** 4.

- All devices requiring NFC functionality especially those running in an Android or Linux environment

- TVs, set-top boxes, Blu-ray decoders, audio devices

- Home automation, gateways, wireless routers

- Home appliances

- Wearables, remote controls, healthcare, fitness

- Printers, IP phones, gaming consoles, accessories

#### Quick reference data 5.

| Symbol                                                   |                                               | Min                                                                                      | Тур        | Max  | Unit |      |    |

|----------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|------------|------|------|------|----|

| V <sub>BAT</sub>                                         | Parameter           battery supply voltage    | Conditions<br>Card Emulation and Passive<br>Target; V <sub>SS</sub> = 0 V                | [1]<br>[2] | 2.3  | -    | 5.5  | V  |

|                                                          |                                               | Reader, Active Initiator and Active Target; $V_{SS} = 0 V$                               | [1]<br>[2] | 2.7  | -    | 5.5  | V  |

| V <sub>DD</sub>                                          | supply voltage                                | internal supply voltage                                                                  |            | 1.65 | 1.8  | 1.95 | V  |

| V <sub>DD(PAD)</sub> V <sub>DD(PAD)</sub> supply voltage | supply voltage for host interface             |                                                                                          |            |      |      |      |    |

|                                                          |                                               | 1.8 V host supply;<br>$V_{SS} = 0 V$                                                     | <u>[1]</u> | 1.65 | 1.8  | 1.95 | V  |

|                                                          |                                               | 3 V host supply; V <sub>SS</sub> = 0 V                                                   | [1]        | 3.0  | -    | 3.6  | V  |

| I <sub>BAT</sub>                                         | battery supply current                        | in Hard Power Down state;<br>V <sub>BAT</sub> = 3.6 V; T = 25 °C                         | [3]        | -    | 10   | 14   | μA |

|                                                          |                                               | in Standby state;<br>V <sub>BAT</sub> = 3.6 V; T = 25 °C                                 |            | -    | 20   | -    | μA |

|                                                          |                                               | in Monitor state;<br>V <sub>BAT</sub> = 2.75 V; T = 25 °C                                |            | -    | -    | 14   | μA |

|                                                          |                                               | in low-power polling loop;<br>V <sub>BAT</sub> = 3.6 V; T = 25 °C;<br>loop time = 500 ms | [4]        | -    | 150  | -    | μA |

|                                                          |                                               | PCD mode at typical 3 V                                                                  | [2]        | -    | -    | 190  | mA |

| I <sub>O(VDDPAD)</sub>                                   | output current on pin<br>V <sub>DD(PAD)</sub> | total current which can be<br>pulled on V <sub>DD(PAD)</sub> referenced<br>outputs       |            | -    | -    | 15   | mA |

| Table 1.         Quick reference datacontinued |                                 |                                                                      |     |     |     |      |  |

|------------------------------------------------|---------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|--|

| Symbol                                         | Parameter                       | Conditions                                                           | Min | Тур | Мах | Unit |  |

| I <sub>th(Ilim)</sub>                          | current limit threshold current |                                                                      | -   | 180 | -   | mA   |  |

| P <sub>tot</sub>                               | total power dissipation         | Reader; $I_{VDD(TX)} = 100 \text{ mA};$<br>$V_{BAT} = 5.5 \text{ V}$ | -   | -   | 420 | mW   |  |

| T <sub>amb</sub>                               | ambient temperature             | JEDEC PCB-0.5                                                        | -30 | -   | +85 | °C   |  |

[1]  $V_{SS}$  represents  $V_{SS(PAD)}$  and  $V_{SS(TX)}$ .

- [2] The antenna should be tuned not to exceed this current limit (the detuning effect when coupling with another device must be taken into account).

- [3] External clock on NFC\_CLK\_XTAL1 must be LOW.

- [4] See <u>Ref. 10</u> for computing the power consumption as it depends on several parameters.

#### 6. Ordering information

#### Table 2. Ordering information

| Type number                      | Package |                                                                                                                      |          |  |  |  |

|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                                  | Name    | Description                                                                                                          | Version  |  |  |  |

| PN7150B0HN/C110xx <sup>[1]</sup> | HVQFN40 | plastic thermal enhanced very thin quad<br>flat package; no leads; 40 terminals; body<br>$6 \times 6 \times 0.85$ mm | SOT618-1 |  |  |  |

[1] xx = firmware code variant.

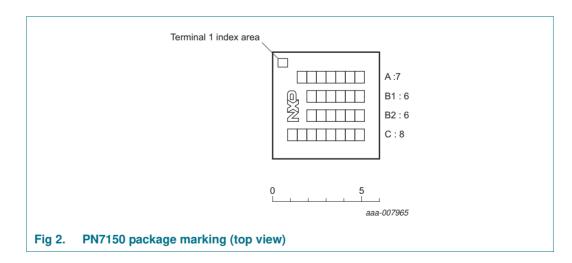

#### 7. Marking

#### Table 3.Marking codes

| Type number | Marking code                                                               |

|-------------|----------------------------------------------------------------------------|

|             | 7 characters used: basic type number:<br>PN7150x where x is the FW variant |

| Type number | Marking code                                                                            |

|-------------|-----------------------------------------------------------------------------------------|

| Line B1     | 6 characters used: diffusion batch sequence number                                      |

| Line B2     | 6 characters used: assembly ID number                                                   |

| Line C      | 7 characters used: manufacturing code including:                                        |

|             | diffusion center code:                                                                  |

|             | – Z: SSMC                                                                               |

|             | <ul> <li>S: Powerchip (PTCT)</li> </ul>                                                 |

|             | <ul> <li>assembly center code:</li> </ul>                                               |

|             | – S: APK                                                                                |

|             | <ul> <li>RoHS compliancy indicator:</li> </ul>                                          |

|             | <ul> <li>D: Dark Green; fully compliant RoHS<br/>and no halogen and antimony</li> </ul> |

|             | <ul> <li>manufacturing year and week, 3 digits:</li> </ul>                              |

|             | – Y: year                                                                               |

|             | – WW: week code                                                                         |

|             | <ul> <li>product life cycle status code:</li> </ul>                                     |

|             | <ul> <li>X: means not qualified product</li> </ul>                                      |

|             | <ul> <li>nothing means released product</li> </ul>                                      |

Table 3.

Marking codes ...continued

**Product data sheet**

#### 8. Block diagram

## 9. Pinning information

#### NFC\_CLK\_XTAL2 NFC\_CLK\_XTAL1 CLK\_REQ terminal 1 n.c. n.c n.c. n.c. n.c. ij ij index area 31 33 40 37 36 33 39 38 35 34 (30 I2CADR0 1 VDDD 2) (29 i.c. V<sub>DD</sub> (28 I2CADR1 3) VDDA (27 Vss V<sub>SS(PAD)</sub> 4) (26 I2CSDA 5 VBAT **PN7150** (25 V<sub>DD(PAD)</sub> 6 i.c. I2CSCL 7) (24 i.c. IRQ 8) (23 i.c. (22 V<sub>DD(TX IN)</sub> $V_{\text{SS}}$ 9) VSS **VEN** 10) (21 TX1 티민 (2) (4) 12 (9) **B** VBAT2 VBAT1 VDD(TX) RXN RXP Vss(TX) VDD(MID) <u>.</u>. TX2 n.c. Transparent top view aaa-016738 Fig 4. Pinning

#### 9.1 Pinning

#### Table 4.Pin description

| Symbol               | Pin | Type <sup>[1]</sup> | Refer                | Description                                                   |

|----------------------|-----|---------------------|----------------------|---------------------------------------------------------------|

| I2CADR0              | 1   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 0                                |

| i.c.                 | 2   | -                   | -                    | internally connected; must be connected to GND                |

| I2CADR1              | 3   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus address 1                                |

| V <sub>SS(PAD)</sub> | 4   | G                   | n/a                  | pad ground                                                    |

| I2CSDA               | 5   | I/O                 | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus data line                                |

| V <sub>DD(PAD)</sub> | 6   | Р                   | n/a                  | pad supply voltage                                            |

| I2CSCL               | 7   | I                   | V <sub>DD(PAD)</sub> | I <sup>2</sup> C-bus clock line                               |

| IRQ                  | 8   | 0                   | V <sub>DD(PAD)</sub> | interrupt request output                                      |

| V <sub>SS</sub>      | 9   | G                   | n/a                  | ground                                                        |

| VEN                  | 10  | I                   | V <sub>BAT</sub>     | reset pin. Set the device in Hard Power Down                  |

| i.c.                 | 11  | -                   | -                    | internally connected; leave open                              |

| V <sub>BAT2</sub>    | 12  | Р                   | n/a                  | battery supply voltage; must be connected to $V_{\text{BAT}}$ |

| V <sub>BAT1</sub>    | 13  | Р                   | n/a                  | battery supply voltage; must be connected to $V_{\text{BAT}}$ |

| V <sub>DD(TX)</sub>  | 14  | Ρ                   | n/a                  | transmitter supply voltage                                    |

| Table 4.         Pin descriptioncontinued           Oursehold         Description |     |                     |                      |                                                                                   |  |  |

|-----------------------------------------------------------------------------------|-----|---------------------|----------------------|-----------------------------------------------------------------------------------|--|--|

| Symbol                                                                            | Pin | Type <sup>[1]</sup> | Refer                | Description                                                                       |  |  |

| RXN                                                                               | 15  | I                   | V <sub>DD</sub>      | negative receiver input                                                           |  |  |

| RXP                                                                               | 16  | 1                   | V <sub>DD</sub>      | positive receiver input                                                           |  |  |

| V <sub>DD(MID)</sub>                                                              | 17  | Р                   | n/a                  | receiver reference input supply voltage                                           |  |  |

| TX2                                                                               | 18  | 0                   | $V_{DD(TX)}$         | antenna driver output                                                             |  |  |

| V <sub>SS(TX)</sub>                                                               | 19  | G                   | n/a                  | contactless transmitter ground                                                    |  |  |

| n.c.                                                                              | 20  | -                   | -                    | not connected                                                                     |  |  |

| TX1                                                                               | 21  | 0                   | $V_{DD(TX)}$         | antenna driver output                                                             |  |  |

| $V_{DD(TX_{IN})}$                                                                 | 22  | Ρ                   | n/a                  | transmitter input supply voltage; must be connected to $V_{\text{DD}(\text{TX})}$ |  |  |

| i.c.                                                                              | 23  | -                   | -                    | internally connected; leave open                                                  |  |  |

| i.c.                                                                              | 24  | -                   | -                    | internally connected; leave open                                                  |  |  |

| i.c.                                                                              | 25  | -                   | -                    | internally connected; leave open                                                  |  |  |

| V <sub>BAT</sub>                                                                  | 26  | Р                   | n/a                  | battery supply voltage                                                            |  |  |

| V <sub>SS</sub>                                                                   | 27  | G                   | n/a                  | ground                                                                            |  |  |

| V <sub>DDA</sub>                                                                  | 28  | Ρ                   | n/a                  | analog supply voltage; must be connected to $V_{\text{DD}}$                       |  |  |

| V <sub>DD</sub>                                                                   | 29  | Р                   | n/a                  | supply voltage                                                                    |  |  |

| V <sub>DDD</sub>                                                                  | 30  | Ρ                   | n/a                  | digital supply voltage; must be connected to $V_{\text{DD}}$                      |  |  |

| n.c.                                                                              | 31  | -                   | -                    | not connected                                                                     |  |  |

| n.c.                                                                              | 32  | -                   | -                    | not connected                                                                     |  |  |

| n.c.                                                                              | 33  | -                   | -                    | not connected                                                                     |  |  |

| n.c.                                                                              | 34  | -                   | -                    | not connected                                                                     |  |  |

| n.c.                                                                              | 35  | -                   | -                    | not connected                                                                     |  |  |

| NFC_CLK_XTAL1                                                                     | 36  | I                   | V <sub>DD</sub>      | oscillator input/PLL input                                                        |  |  |

| NFC_CLK_XTAL2                                                                     | 37  | 0                   | V <sub>DD</sub>      | oscillator output                                                                 |  |  |

| i.c.                                                                              | 38  | -                   | -                    | internally connected; leave open                                                  |  |  |

| i.c.                                                                              | 39  | -                   | -                    | internally connected; leave open                                                  |  |  |

| CLK_REQ                                                                           | 40  | 0                   | V <sub>DD(PAD)</sub> | clock request pin                                                                 |  |  |

|                                                                                   |     | 1                   | . ,                  |                                                                                   |  |  |

Table 4.

Pin description ...continued

[1] P = power supply; G = ground; I = input, O = output; I/O = input/output.

## **10. Functional description**

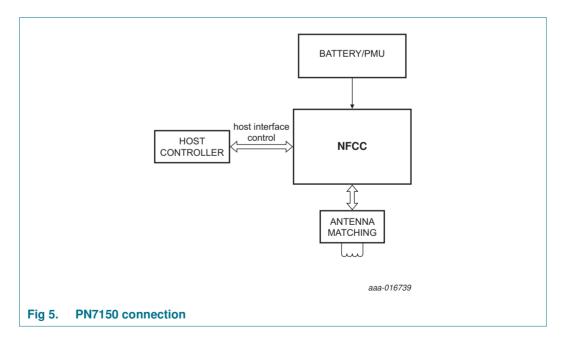

PN7150 can be connected on a host controller through  $l^2$ C-bus. The logical interface towards the host baseband is NCI-compliant <u>Ref. 2</u> with additional command set for NXP-specific product features. This IC is fully user controllable by the firmware interface described in <u>Ref. 5</u>.

Moreover, PN7150 provides flexible and integrated power management unit in order to preserve energy supporting Power Off mode.

In the following chapters you will find also more details about PN7150 with references to very useful application note such as:

• PN7150 User Manual (Ref. 5):

User Manual describes the software interfaces (API) based on the NFC forum NCI standard. It does give full description of all the NXP NCI extensions coming in addition to NCI standard (<u>Ref. 2</u>).

• PN7150 Hardware Design Guide (Ref. 6):

Hardware Design Guide provides an overview on the different hardware design options offered by the IC and provides guidelines on how to select the most appropriate ones for a given implementation. In particular, this document highlights the different chip power states and how to operate them in order to minimize the average NFC-related power consumption so to enhance the battery lifetime.

• PN7150 Antenna and Tuning Design Guide (<u>Ref. 7</u>):

Antenna and Tuning Design Guide provides some guidelines regarding the way to design an NFC antenna for the PN7150 chip.

It also explains how to determine the tuning/matching network to place between this antenna and the PN7150.

Standalone antenna performances evaluation and final RF system validation (PN7150 + tuning/matching network + NFC antenna within its final environment) are also covered by this document.

• PN7150 Low-Power Mode Configuration (<u>Ref. 10</u>):

Low-Power Mode Configuration documentation provides guidance on how PN7150 can be configured in order to reduce current consumption by using Low-power polling mode.

#### 10.1 System modes

#### 10.1.1 System power modes

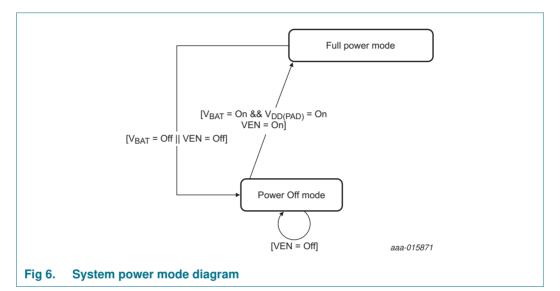

PN7150 is designed in order to enable the different power modes from the system.

2 power modes are specified: Full power mode and Power Off mode.

| Table 5. | S | ystem | power | modes | description |

|----------|---|-------|-------|-------|-------------|

|----------|---|-------|-------|-------|-------------|

| System power mode | Description                                                                                                                  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Full power mode   | the main supply $(V_{BAT})$ as well as the host interface supply $(V_{DD(PAD)})$ is available, all use cases can be executed |  |  |  |  |

| Power Off mode    | the system is kept Hard Power Down (HPD)                                                                                     |  |  |  |  |

<u>Table 6</u> summarizes the system power mode of the PN7150 depending on the status of the external supplies available in the system:

#### Table 6. System power modes configuration

| V <sub>BAT</sub> | VEN | Power mode      |

|------------------|-----|-----------------|

| Off              | Х   | Power Off mode  |

| On               | Off | Power Off mode  |

| On               | On  | Full power mode |

Depending on power modes, some application states are limited:

#### Table 7.System power modes description

| System power mode | Allowed communication modes              |

|-------------------|------------------------------------------|

| Power Off mode    | no communication mode available          |

| Full power mode   | Reader/Writer, Card Emulation, P2P modes |

#### 10.1.2 PN7150 power states

Next to system power modes defined by the status of the power supplies, the power states include the logical status of the system thus extend the power modes.

4 power states are specified: Monitor, Hard Power Down (HPD), Standby, Active.

| Power state name | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitor          | The PN7150 is supplied by $V_{BAT}$ which voltage is below its programmable critical level, VEN voltage > 1.1 V and the Monitor state is enabled. The system power mode is Power Off mode.                                                                                                                                                                                |

| Hard Power Down  | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when Monitor state is enabled and PN7150 is kept in Hard Power Down (VEN voltage is kept low by host or SW programming) to have the minimum power consumption. The system power mode is in Power Off.                                                                          |

| Standby          | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when the Monitor state is enabled, VEN voltage is high (by host or SW programming) and minimum part of PN7150 is kept supplied to enable configured wake-up sources which allow to switch to Active state; RF field, Host interface. The system power mode is Full power mode. |

| Active           | The PN7150 is supplied by $V_{BAT}$ which voltage is above its programmable critical level when Monitor state is enabled, VEN voltage is high (by host or SW programming) and the PN7150 internal blocks are supplied. 3 functional modes are defined: Idle, Target and Initiator. The system power mode is Full power mode.                                              |

At application level, the PN7150 will continuously switch between different states to optimize the current consumption (polling loop mode). Refer to <u>Table 1</u> for targeted current consumption in here described states.

The PN7150 is designed to allow the host controller to have full control over its functional states, thus of the power consumption of the PN7150 based NFC solution and possibility to restrict parts of the PN7150 functionality.

#### 10.1.2.1 Monitor state

In Monitor state, the PN7150 will exit it only if the battery voltage recovers over the critical level. Battery voltage monitor thresholds show hysteresis behavior as defined in Table 27.

#### 10.1.2.2 Hard Power Down (HPD) state

The Hard Power Down state is entered when  $V_{DD(PAD)}$  and  $V_{BAT}$  are high by setting VEN voltage < 0.4 V. As these signals are under host control, the PN7150 has no influence on entering or exiting this state.

#### 10.1.2.3 Standby state

Active state is PN7150's default state after boot sequence in order to allow a quick configuration of PN7150. It is recommended to change the default state to Standby state after first boot in order to save power. PN7150 can switch to Standby state autonomously (if configured by host).

In this state, PN7150 most blocks including CPU are no more supplied. Number of wake-up sources exist to put PN7150 into Active state:

- I<sup>2</sup>C-bus interface wake-up event

- Antenna RF level detector

- Internal timer event when using polling loop (380 kHz Low-power oscillator is enabled)

If wake-up event occurs, PN7150 will switch to Active state. Any further operation depends on software configuration and/or wake-up source.

#### 10.1.2.4 Active state

Within the Active state, the system is acting as an NFC device. The device can be in 3 different functional modes: Idle, Poller and Target.

#### Table 9. Functional modes in active state

| Functional modes | Description                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------|

| Idle             | the PN7150 is active and allows host interface communication. The RF interface is not activated. |

| Listener         | the PN7150 is active and is configured for listening to external device.                         |

| Poller           | the PN7150 is active and is configured in Poller mode. It polls external device                  |

**Poller mode:** In this mode, PN7150 is acting as Reader/Writer or NFC Initiator, searching for or communicating with passive tags or NFC target. Once RF communication has ended, PN7150 will switch to active battery mode (that is, switch off RF transmitter) to save energy. Poller mode shall be used with 2.7 V < V<sub>BAT</sub> < 5.5 V and VEN voltage > 1.1 V. Poller mode shall not be used with V<sub>BAT</sub> < 2.7 V. V<sub>DD(PAD)</sub> is within its operational range (see Table 1).

**Listener mode:** In this mode, PN7150 is acting as a card or as an NFC Target. Listener mode shall be used with 2.3 V <  $V_{BAT}$  < 5.5 V and VEN voltage > 1.1 V.

#### 10.1.2.5 Polling loop

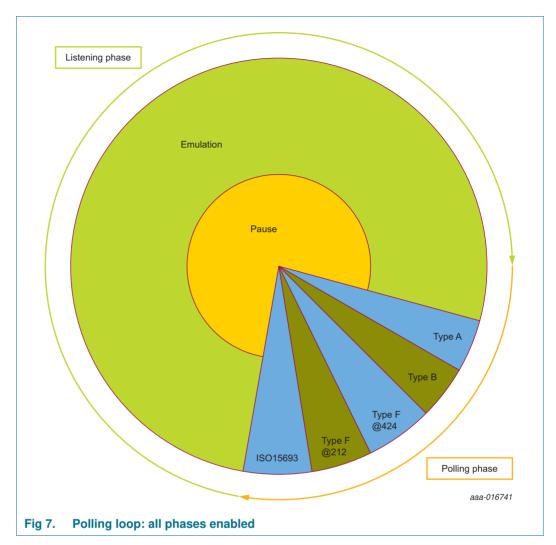

The polling loop will sequentially set PN7150 in different power states (Active or Standby). All RF technologies supported by PN7150 can be independently enabled within this polling loop.

There are 2 main phases in the polling loop:

- Listening phase. The PN7150 can be in Standby power state or Listener mode

- · Polling phase. The PN7150 is in Poller mode

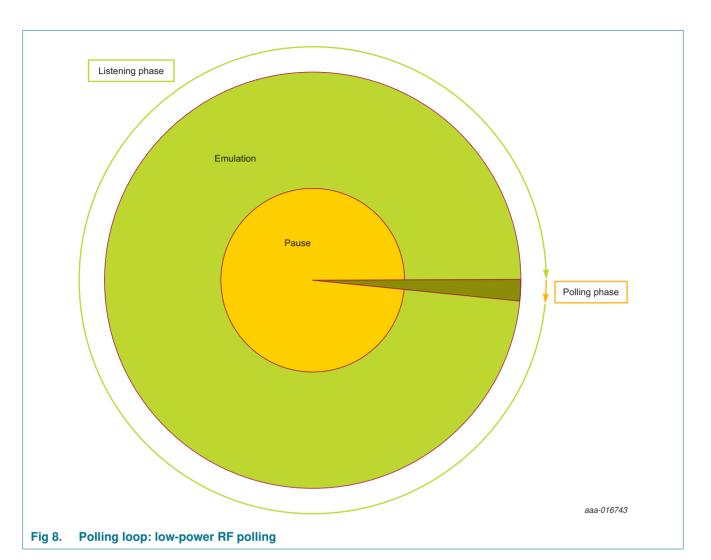

Listening phase uses Standby power state (when no RF field) and PN7150 goes to Listener mode when RF field is detected. When in Polling phase, PN7150 goes to Poller mode.

To further decrease the power consumption when running the polling loop, PN7150 features a low-power RF polling. When PN7150 is in Polling phase instead of sending regularly RF command, PN7150 senses with a short RF field duration if there is any NFC Target or card/tag present. If yes, then it goes back to standard polling loop. With 500 ms (configurable duration, see <u>Ref. 5</u>) listening phase duration, the average power consumption is around 150  $\mu$ A.

Detailed description of polling loop configuration options is given in Ref. 5.

#### **10.2 Microcontroller**

PN7150 is controlled via an embedded ARM Cortex-M0 microcontroller core.

PN7150 features integrated in firmware are referenced in Ref. 5.

#### 10.3 Host interface

PN7150 provides the support of an I<sup>2</sup>C-bus Slave Interface, up to 3.4 MBaud.

The host interface is waken-up on I<sup>2</sup>C-bus address.

To enable and ensure data flow control between PN7150 and host controller, additionally a dedicated interrupt line IRQ is provided which Active state is programmable. See <u>Ref. 5</u> for more information.

#### 10.3.1 I<sup>2</sup>C-bus interface

The I<sup>2</sup>C-bus interface implements a slave I<sup>2</sup>C-bus interface with integrated shift register, shift timing generation and slave address recognition.

I<sup>2</sup>C-bus Standard mode (100 kHz SCL), Fast mode (400 kHz SCL) and High-speed mode (3.4 MHz SCL) are supported.

The mains hardware characteristics of the I<sup>2</sup>C-bus module are:

- Support slave I<sup>2</sup>C-bus

- Standard, Fast and High-speed modes supported

- · Wake-up of PN7150 on its address only

- Serial clock synchronization can be used by PN7150 as a handshake mechanism to suspend and resume serial transfer (clock stretching)

The I<sup>2</sup>C-bus interface module meets the I<sup>2</sup>C-bus specification  $\underline{\text{Ref. 4}}$  except General call, 10-bit addressing and Fast mode Plus (Fm+).

#### 10.3.1.1 I<sup>2</sup>C-bus configuration

The l<sup>2</sup>C-bus interface shares four pins with l<sup>2</sup>C-bus interface also supported by PN7150. When l<sup>2</sup>C-bus is configured in EEPROM settings, functionality of interface pins changes to one described in Table 10.

#### Table 10. Functionality for I<sup>2</sup>C-bus interface

| Pin name              | Functionality                   |

|-----------------------|---------------------------------|

| I2CADR0               | I <sup>2</sup> C-bus address 0  |

| I2CADR1               | I <sup>2</sup> C-bus address 1  |

| I2CSCL <sup>[1]</sup> | I <sup>2</sup> C-bus clock line |

| I2CSDA <sup>[1]</sup> | I <sup>2</sup> C-bus data line  |

I2CSCL and I2CSDA are not fail-safe and V<sub>DD(pad)</sub> shall always be available when using the SCL and SDA lines connected to these pins.

PN7150 supports 7-bit addressing mode. Selection of the I<sup>2</sup>C-bus address is done by 2-pin configurations on top of a fixed binary header: 0, 1, 0, 1, 0, I2CADR1, I2CADR0, R/W.

#### Table 11. I<sup>2</sup>C-bus interface addressing

| I2CADR1 | I2CADR0 | l <sup>2</sup> C-bus address<br>(R/W = 0, write) | l <sup>2</sup> C-bus address<br>(R/W = 1, read) |

|---------|---------|--------------------------------------------------|-------------------------------------------------|

| 0       | 0       | 0x50                                             | 0x51                                            |

| 0       | 1       | 0x52                                             | 0x53                                            |

| 1       | 0       | 0x54                                             | 0x55                                            |

| 1       | 1       | 0x56                                             | 0x57                                            |

#### 10.4 PN7150 clock concept

There are 4 different clock sources in PN7150:

- 27.12 MHz clock coming either/or from:

- Internal oscillator for 27.12 MHz crystal connection

- Integrated PLL unit which includes a 1 GHz VCO, taking is reference clock on pin NFC CLK XTAL1

- 13.56 MHz RF clock recovered from RF field

- Low-power oscillator 40 MHz

- Low-power oscillator 380 kHz

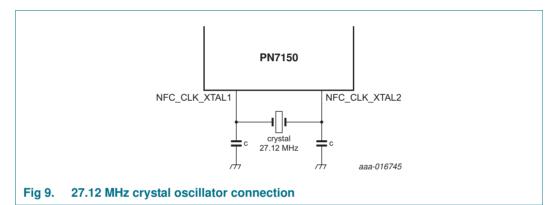

#### 10.4.1 27.12 MHz quartz oscillator

When enabled, the 27.12 MHz guartz oscillator applied to PN7150 is the time reference for the RF front end when PN7150 is behaving in Reader mode or NFCIP-1 initiator.

Therefore stability of the clock frequency is an important factor for reliable operation. It is recommended to adopt the circuit shown in Figure 9.

Table 12 describes the levels of accuracy and stability required on the crystal.

| Symbol            | Parameter                    | Conditions                                         |     | Min  | Тур   | Max  | Unit |

|-------------------|------------------------------|----------------------------------------------------|-----|------|-------|------|------|

| f <sub>xtal</sub> | crystal frequency            | ISO/IEC and FCC compliancy                         |     | -    | 27.12 | -    | MHz  |

| $\Delta f_{xtal}$ | crystal frequency accuracy   | full operating range                               | [1] | -100 | -     | +100 | ppm  |

|                   |                              | all V <sub>BAT</sub> range;<br>T = 20 °C           | [1] | -50  | -     | +50  | ppm  |

|                   |                              | all temperature range;<br>V <sub>BAT</sub> = 3.6 V | [1] | -50  | -     | +50  | ppm  |

| ESR               | equivalent series resistance |                                                    |     | -    | 50    | 100  | Ω    |

| CL                | load capacitance             |                                                    |     | -    | 10    | -    | pF   |

| P <sub>xtal</sub> | crystal power dissipation    |                                                    |     | -    | -     | 100  | μW   |

Table 12. Crystal requirements

[1] This requirement is according to FCC regulations requirements. To meet only ISO/IEC 14443 and ISO/IEC 18092, then ± 14 kHz apply.

#### 10.4.2 Integrated PLL to make use of external clock

When enabled, the PLL is designed to generate a low noise 27.12 MHz for an input clock 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz.

The 27.12 MHz of the PLL is used as the time reference for the RF front end when PN7150 is behaving in Reader mode or ISO/IEC 18092 Initiator as well as in Target when configured in Active Communication mode.

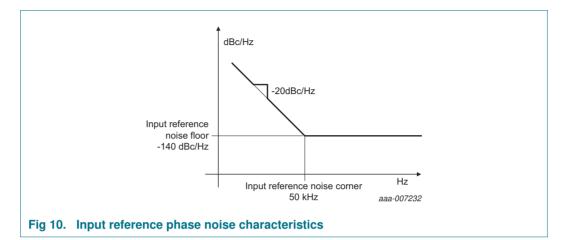

The input clock on NFC\_CLK\_XTAL1 shall comply with the following phase noise requirements for the following input frequency: 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz:

This phase noise is equivalent to an RMS jitter of 6.23 ps from 10 Hz to 1 MHz. For configuration of input frequency, refer to <u>Ref. 9</u>. There are 6 pre-programmed and validated frequencies for the PLL: 13 MHz, 19.2 MHz, 24 MHz, 26 MHz, 38.4 MHz and 52 MHz.

## Table 13. PLL input requirements Coupling: single-ended, AC coupling;

| Symbol                 | Parameter                             | Conditions                                                                               |     | Min  | Тур  | Max           | Unit      |

|------------------------|---------------------------------------|------------------------------------------------------------------------------------------|-----|------|------|---------------|-----------|

| f <sub>clk</sub>       | clock frequency                       | ISO/IEC and FCC                                                                          | -   | 13   | -    | MHz           |           |

|                        |                                       | compliancy                                                                               |     | -    | 19.2 | -             | MHz       |

|                        |                                       |                                                                                          | -   | 24   | -    | MHz           |           |

|                        |                                       |                                                                                          |     | -    | 26   | -             | MHz       |

|                        |                                       |                                                                                          |     | -    | 38.4 | -             | MHz       |

|                        |                                       |                                                                                          |     | -    | 52   | -             | MHz       |

| f <sub>i(ref)acc</sub> | reference input<br>frequency accuracy | full operating range;<br>frequencies typical values:<br>13 MHz, 26 MHz and<br>52 MHz     | [1] | -25  | -    | +25           | ppm       |

|                        |                                       | full operating range;<br>frequencies typical values:<br>19.2 MHz, 24 MHz and<br>38.4 MHz | [1] | -50  | -    | +50           | ppm       |

| φ <sub>n</sub>         | phase noise                           | input noise floor at 50 kHz                                                              |     | -140 | -    | -             | dB/<br>Hz |

| Sinusoid               | lal shape                             |                                                                                          |     |      | 1    |               |           |

| V <sub>i(p-p)</sub>    | peak-to-peak input<br>voltage         |                                                                                          |     | 0.2  | -    | 1.8           | V         |

| V <sub>i(clk)</sub>    | clock input voltage                   |                                                                                          |     | 0    | -    | 1.8           | V         |

| Square s               | hape                                  | 1                                                                                        |     | 1    | 1    | 1             | 1         |

| V <sub>i(clk)</sub>    | clock input voltage                   |                                                                                          |     | 0    | -    | $1.8\pm10~\%$ | V         |

[1] This requirement is according to FCC regulations requirements. To meet only ISO/IEC 14443 and ISO/IEC 18092, then  $\pm$  400 ppm limits apply.

For detailed description of clock request mechanisms, refer to Ref. 5 and Ref. 6.

#### 10.4.3 Low-power 40 MHz $\pm$ 2.5 % oscillator

Low-power OSC generates a 40 MHz internal clock. This frequency is divided by two to make the system clock.

#### 10.4.4 Low-power 380 kHz oscillator

A Low Frequency Oscillator (LFO) is implemented to drive a counter (WUC) waking-up PN7150 from Standby state. This allows implementation of low-power reader polling loop at application level. Moreover, this 380 kHz is used as the reference clock for write access to EEPROM memory.

#### 10.5 Power concept

#### 10.5.1 PMU functional description

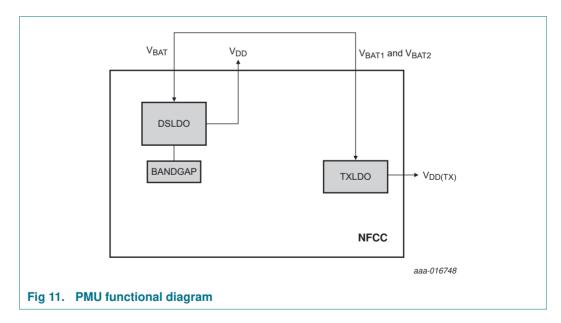

The Power Management Unit of PN7150 generates internal supplies required by PN7150 out of  $V_{BAT}$  input supply voltage:

- V<sub>DD</sub>: internal supply voltage

- V<sub>DD(TX)</sub>: output supply voltage for the RF transmitter

The Figure 11 describes the main blocks available in PMU:

#### 10.5.2 DSLDO: Dual Supply LDO

The input pin of the DSLDO is  $\ensuremath{\mathsf{V}_{\mathsf{BAT}}}$  .

The Low drop-out regulator provides V<sub>DD</sub> required in PN7150.

#### 10.5.3 TXLDO

Transmitter voltage can be generated by internal LDO ( $V_{DD(TX)}$ ) or come from an external supply source  $V_{DD(TX)}$ .

The regulator has been designed to work in 2 configurations:

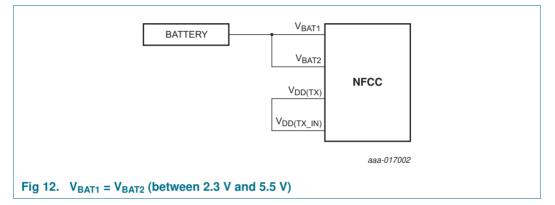

#### 10.5.3.1 Configuration 1: supply connection in case the battery is used to generate RF field

The Low drop Out Regulator has been designed to generate a 3.0 V, 3.3 V or 3.6 V supply voltage to a transmitter with a current load up to 180 mA.

The output is called  $V_{DD(TX)}$ . The input supply voltage of this regulator is a battery voltage connected to  $V_{BAT1}$  pin.

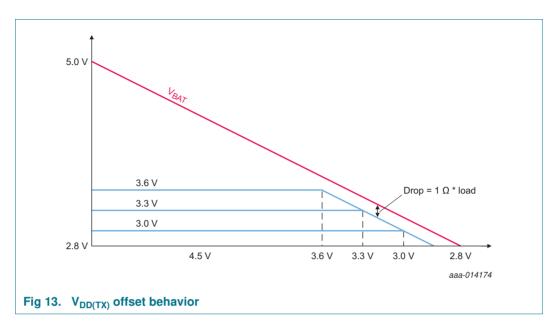

$V_{\text{DD}(\text{TX})}$  value shall be chosen according to the minimum targeted  $V_{\text{BAT}}$  value for which reader mode shall work.

If  $V_{BAT}$  is above 3.0 V plus the regulator voltage dropout, then  $V_{DD(TX)} = 3.0$  V shall be chosen:

$$\begin{split} V_{BAT} &\geq (3.0V + 1\Omega \times load) \Rightarrow V_{DD(TX)} = 3.0V \\ 3.0V &\geq V_{BAT} \geq 2.3V \Rightarrow V_{DD(TX)} = V_{BAT} - 1\Omega \times load \end{split}$$

If  $V_{BAT}$  is above 3.3 V plus the regulator voltage dropout, then  $V_{DD(TX)} = 3.3$  V shall be chosen:

$$V_{BAT} \ge (3.3V + 1\Omega \times load) \Rightarrow V_{DD(TX)} = 3.3V$$

$$3.3V \ge V_{BAT} \ge 2.3V \Longrightarrow V_{DD(TX)} = V_{BAT} - 1\Omega \times load$$

If  $V_{BAT}$  is above 3.6 V plus the regulator voltage dropout, then  $V_{DD(TX)} = 3.6$  V shall be chosen:

$$V_{BAT} \ge (3.6V + 1\Omega \times load) \Rightarrow V_{DD(TX)} = 3.6V$$

$$3.6V \ge V_{BAT} \ge 2.3V \Rightarrow V_{DD(TX)} = V_{BAT} - 1\Omega \times load$$

<u>Figure 13</u> shows  $V_{DD(TX)}$  offset disabled behavior for both cases of  $V_{DD(TX)}$  programmed for 3.0 V, 3.3 V or 3.6 V.

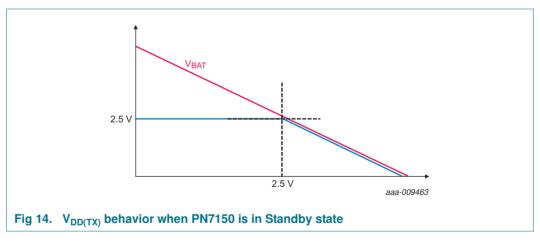

In Standby state, whenever  $V_{DD(TX)}$  is configured for 3.0 V, 3.3 V or 3.6 V,  $V_{DD(TX)}$  is regulated at 2.5 V.

Figure 14 shows the case where the PN7150 is in standby state.

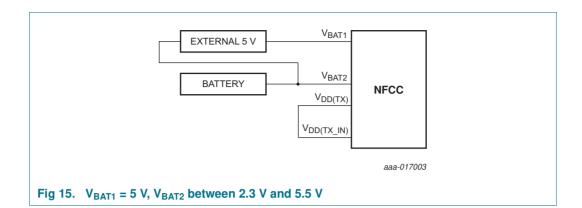

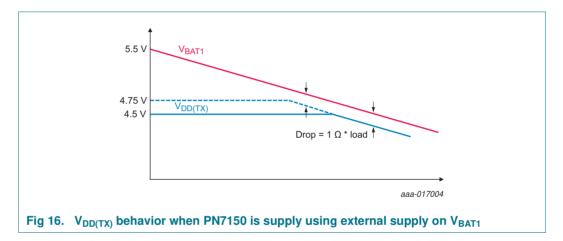

# 10.5.3.2 Configuration 2: supply connection in case a 5 V supply is used to generate RF field with the use of TXLDO

TXLDO has also the possibility to generate 4.75 V or 4.5 V supply in case the supply of this regulator is an external 5 V supply.

Figure 16 shows the behavior of  $V_{DD(TX)}$  depending on  $V_{BAT1}$  value.

#### 10.5.3.3 TXLDO limiter

The TXLDO includes a current limiter to avoid too high current within TX1, TX2 when in reader or initiator modes.

The current limiter block compares an image of the TXLDO output current to a reference. Once the reference is reached, the output current gets limited which is equivalent to a typical output current of 220 mA whatever  $V_{BAT}$  or  $V_{BAT1}$  value in the range of 2.3 V to 5.5 V.

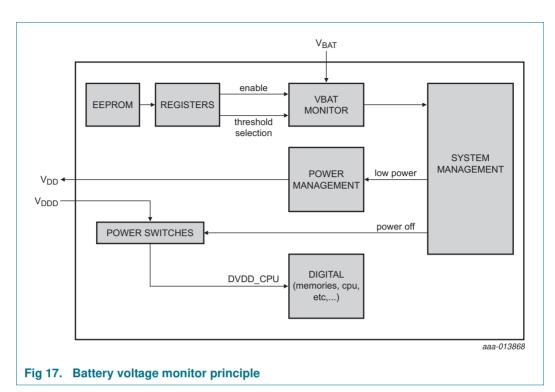

#### 10.5.4 Battery voltage monitor

The PN7150 features low-power V<sub>BAT</sub> voltage monitor which protects mobile device battery from being discharged below critical levels. When V<sub>BAT</sub> voltage goes below V<sub>BATcritical</sub> threshold, then the PN7150 goes in Monitor state. Refer to Figure 17 for principle schematic of the battery monitor.

The battery voltage monitor is enabled via an EEPROM setting.

At the first start-up,  $V_{BAT}$  voltage monitor functionality is OFF and then enabled if properly configured in EEPROM. The PN7150 monitors battery voltage continuously.

The value of the critical level can be configured to 2.3 V or 2.75 V by an EEPROM setting. This value has a typical hysteresis around 150 mV.

#### 10.6 Reset concept

#### 10.6.1 Resetting PN7150

To enter reset, there are 2 ways:

- Pulling VEN voltage low (Hard Power Down state)

- if V<sub>BAT</sub> monitor is enabled: lowering V<sub>BAT</sub> below the monitor threshold (Monitor state, if VEN voltage is kept above 1.1 V)

Reset means resetting the embedded FW execution and the registers values to their default values. Part of these default values is defined from EEPROM data loaded values, others are hardware defined. See <u>Ref. 5</u> to know which ones are accessible to tune PN7150 to the application environment.

To get out of reset:

• Pulling VEN voltage high with V<sub>BAT</sub> above V<sub>BAT</sub> monitor threshold if enabled

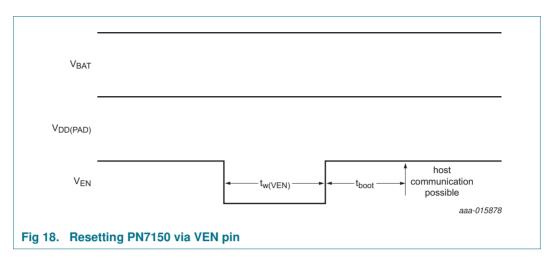

Figure 18 shows reset done via VEN pin.

See <u>Section 14.2.2</u> for the timings values.

#### 10.6.2 Power-up sequences

There are 2 different supplies for PN7150. PN7150 allows these supplies to be set up independently, therefore different power-up sequences have to be considered.

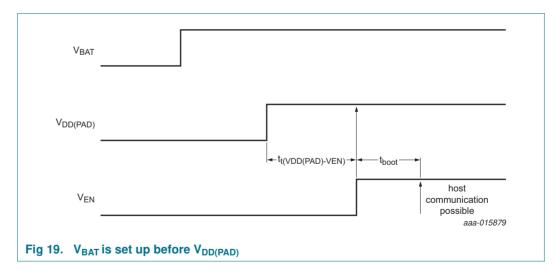

#### 10.6.2.1 V<sub>BAT</sub> is set up before V<sub>DD(PAD)</sub>

This is at least the case when  $V_{BAT}$  pin is directly connected to the battery and when PN7150  $V_{BAT}$  is always supplied as soon the system is supplied.

As VEN pin is referred to V<sub>BAT</sub> pin, VEN voltage shall go high after V<sub>BAT</sub> has been set.

See <u>Section 14.2.3</u> for the timings values.

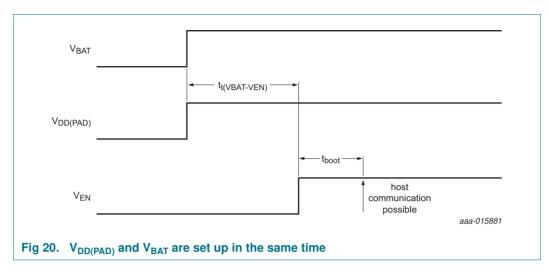

#### 10.6.2.2 $V_{DD(PAD)}$ and $V_{BAT}$ are set up in the same time

It is at least the case when  $V_{BAT}$  pin is connected to a PMU/regulator which also supply  $V_{\text{DD}(\text{PAD})}.$

See Section 14.2.3 for the timings values.

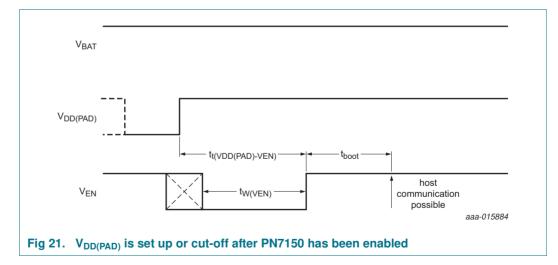

# 10.6.2.3 PN7150 has been enabled before $V_{DD(PAD)}$ is set up or before $V_{DD(PAD)}$ has been cut off

This can be the case when  $V_{BAT}$  pin is directly connected to the battery and when  $V_{DD(PAD)}$  is generated from a PMU. When the battery voltage is too low, then the PMU might no more be able to generate  $V_{DD(PAD)}$ . When the device gets charged again, then  $V_{DD(PAD)}$  is set up again.

As the pins to select the interface are biased from  $V_{DD(PAD)}$ , when  $V_{DD(PAD)}$  disappears the pins might not be correctly biased internally and the information might be lost. Therefore it is required to make the IC boot after  $V_{DD(PAD)}$  is set up again.

See Section 14.2.3 for the timings values.

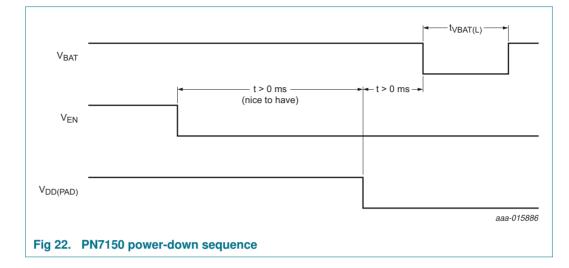

#### 10.6.3 Power-down sequence

#### 10.7 Contactless Interface Unit

PN7150 supports various communication modes at different transfer speeds and modulation schemes. The following chapters give more detailed overview of selected communication modes.

**Remark:** all indicated modulation index and modes in this chapter are system parameters. This means that beside the IC settings a suitable antenna tuning is required to achieve the optimum performance.

#### 10.7.1 Reader/Writer communication modes

Generally 5 Reader/Writer communication modes are supported:

- PCD Reader/Writer for ISO/IEC 14443A/MIFARE

- PCD Reader/Writer for Jewel/Topaz tags

- PCD Reader/Writer for FeliCa cards

- PCD Reader/Writer for ISO/IEC 14443B

- VCD Reader/Writer for ISO/IEC 15693/ICODE

#### 10.7.1.1 ISO/IEC 14443A/MIFARE and Jewel/Topaz PCD communication mode

The ISO/IEC 14443A/MIFARE PCD communication mode is the general reader to card communication scheme according to the ISO/IEC 14443A specification. This modulation scheme is as well used for communications with Jewel/Topaz cards.

Figure 23 describes the communication on a physical level, the communication table describes the physical parameters (the numbers take the antenna effect on modulation depth for higher data rates).