# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Freescale Semiconductor Data Sheet: Technical Data

# K53 Sub-Family Data Sheet

Supports the following: MK53DN512ZCLQ10, MK53DN512ZCMD10, MK53DX256ZCLQ10, MK53DX256ZCMD10

#### Features

- Operating Characteristics

- Voltage range: 1.71 to 3.6 V

- Flash write voltage range: 1.71 to 3.6 V

- Temperature range (ambient): -40 to 85°C

- Performance

- Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz

- Memories and memory interfaces

- Up to 512 KB program flash memory on non-FlexMemory devices

- Up to 256 KB program flash memory on FlexMemory devices

- Up to 256 KB FlexNVM on FlexMemory devices

- 4 KB FlexRAM on FlexMemory devices

- Up to 128 KB RAM

- Serial programming interface (EzPort)

- FlexBus external bus interface

- Clocks

- 3 to 32 MHz crystal oscillator

- 32 kHz crystal oscillator

- Multi-purpose clock generator

- System peripherals

- Multiple low-power modes to provide power optimization based on application requirements

- Memory protection unit with multi-master protection

- 16-channel DMA controller, supporting up to 63 request sources

- External watchdog monitor

- Software watchdog

- Low-leakage wakeup unit

# K53P144M100SF2

- Security and integrity modules

- Hardware CRC module to support fast cyclic redundancy checks

- Hardware random-number generator

- Hardware encryption supporting DES, 3DES, AES, MD5, SHA-1, and SHA-256 algorithms

- 128-bit unique identification (ID) number per chip

- Human-machine interface

- Segment LCD controller supporting up to 40 frontplanes and 8 backplanes, or 44 frontplanes and 4 backplanes, depending on the package size

- Low-power hardware touch sensor interface (TSI)

- General-purpose input/output

- Analog modules

- Two 16-bit SAR ADCs

- Programmable gain amplifier (PGA) (up to x64) integrated into each ADC

- Two 12-bit DACs

- Two operational amplifiers

- Two transimpedance amplifiers

- Three analog comparators (CMP) containing a 6-bit DAC and programmable reference input

- Voltage reference

- Timers

- Programmable delay block

- Eight-channel motor control/general purpose/PWM timer

- Two 2-channel quadrature decoder/general purpose timers

- IEEE 1588 timers

- Periodic interrupt timers

- 16-bit low-power timer

- Carrier modulator transmitter

- Real-time clock

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

- Communication interfaces

- Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- Three SPI modules

- Two I2C modules

- Six UART modules

- Secure Digital host controller (SDHC)

- I2S module

# **Table of Contents**

| 1 | Orde | ering parts | 5                                            |

|---|------|-------------|----------------------------------------------|

|   | 1.1  | Determini   | ng valid orderable parts5                    |

| 2 | Part | identificat | ion5                                         |

|   | 2.1  | Descriptio  | on5                                          |

|   | 2.2  | Format      | 5                                            |

|   | 2.3  | Fields      | 5                                            |

|   | 2.4  | Example.    |                                              |

| 3 | Terr | ninology a  | nd guidelines6                               |

|   | 3.1  | Definition  | : Operating requirement6                     |

|   | 3.2  | Definition  | : Operating behavior7                        |

|   | 3.3  | Definition  | : Attribute7                                 |

|   | 3.4  | Definition  | : Rating8                                    |

|   | 3.5  | Result of   | exceeding a rating8                          |

|   | 3.6  | Relations   | hip between ratings and operating            |

|   |      | requireme   | ents8                                        |

|   | 3.7  | Guideline   | s for ratings and operating requirements9    |

|   | 3.8  | Definition  | : Typical value9                             |

|   | 3.9  | Typical va  | alue conditions10                            |

| 4 | Rati | ngs         |                                              |

|   | 4.1  | Thermal h   | nandling ratings11                           |

|   | 4.2  | Moisture    | handling ratings11                           |

|   | 4.3  | ESD hand    | dling ratings11                              |

|   | 4.4  | Voltage a   | nd current operating ratings11               |

| 5 | Gen  | eral        |                                              |

|   | 5.1  | AC electri  | cal characteristics12                        |

|   | 5.2  | Nonswitcl   | ning electrical specifications12             |

|   |      | 5.2.1       | Voltage and current operating requirements13 |

|   |      | 5.2.2       | LVD and POR operating requirements14         |

|   |      | 5.2.3       | Voltage and current operating behaviors14    |

|   |      | 5.2.4       | Power mode transition operating behaviors16  |

|   |      | 5.2.5       | Power consumption operating behaviors17      |

|   |      | 5.2.6       | EMC radiated emissions operating behaviors20 |

|   |      | 5.2.7       | Designing with radiated emissions in mind21  |

|   |      | 5.2.8       | Capacitance attributes21                     |

|   | 5.3  | Switching   | specifications21                             |

|   |      | 5.3.1       | Device clock specifications21                |

|   |      | 5.3.2       | General switching specifications21           |

|   | 5.4  | Thermal s   | specifications22                             |

|   |      | 5.4.1       | Thermal operating requirements22             |

|   |      | 5.4.2     | Thermal attributes                              | 23   |

|---|------|-----------|-------------------------------------------------|------|

| 6 | Peri | pheral op | erating requirements and behaviors              | 24   |

|   | 6.1  | Core mo   | dules                                           | 24   |

|   |      | 6.1.1     | Debug trace timing specifications               | 24   |

|   |      | 6.1.2     | JTAG electricals                                | 25   |

|   | 6.2  | System    | modules                                         | 28   |

|   | 6.3  | Clock m   | odules                                          | 28   |

|   |      | 6.3.1     | MCG specifications                              | 28   |

|   |      | 6.3.2     | Oscillator electrical specifications            | 30   |

|   |      | 6.3.3     | 32 kHz Oscillator Electrical Characteristics    | 32   |

|   | 6.4  | Memorie   | es and memory interfaces                        | 33   |

|   |      | 6.4.1     | Flash electrical specifications                 | 33   |

|   |      | 6.4.2     | EzPort Switching Specifications                 | 37   |

|   |      | 6.4.3     | Flexbus Switching Specifications                | 38   |

|   | 6.5  | Security  | and integrity modules                           | 41   |

|   | 6.6  | Analog    |                                                 | 41   |

|   |      | 6.6.1     | ADC electrical specifications                   | 41   |

|   |      | 6.6.2     | CMP and 6-bit DAC electrical specifications     | 49   |

|   |      | 6.6.3     | 12-bit DAC electrical characteristics           | 51   |

|   |      | 6.6.4     | Op-amp electrical specifications                | 54   |

|   |      | 6.6.5     | Transimpedance amplifier electrical             |      |

|   |      |           | specifications — full range                     | 55   |

|   |      | 6.6.6     | Transimpedance amplifier electrical             |      |

|   |      |           | specifications — limited range                  | 56   |

|   |      | 6.6.7     | Voltage reference electrical specifications     | 57   |

|   | 6.7  | Timers    |                                                 | 58   |

|   | 6.8  | Commu     | nication interfaces                             | 58   |

|   |      | 6.8.1     | Ethernet switching specifications               | 58   |

|   |      | 6.8.2     | USB electrical specifications                   | 60   |

|   |      | 6.8.3     | USB DCD electrical specifications               | 60   |

|   |      | 6.8.4     | USB VREG electrical specifications              | 61   |

|   |      | 6.8.5     | DSPI switching specifications (limited voltage  |      |

|   |      |           | range)                                          | 61   |

|   |      | 6.8.6     | DSPI switching specifications (full voltage     |      |

|   |      |           | range)                                          | 63   |

|   |      | 6.8.7     | Inter-Integrated Circuit Interface (I2C) timing | . 65 |

|   |      | 6.8.8     | UART switching specifications                   | 66   |

|   |      | 6.8.9     | SDHC specifications                             | 66   |

|   |      | 6.8.10    | I2S switching specifications                    | 67   |

|   |      |           |                                                 |      |

|   | 6.9 Human-machine interfaces (HMI) |         |                                 |    |  |

|---|------------------------------------|---------|---------------------------------|----|--|

|   |                                    | 6.9.1   | TSI electrical specifications7  | 0' |  |

|   |                                    | 6.9.2   | LCD electrical characteristics7 | '1 |  |

| 7 | Dim                                | ensions | 7                               | 2  |  |

|   | 7.1 Obtaining package dimensions   |         |                                 | 2  |  |

| 8 | Pinc | put                                         | .72 |

|---|------|---------------------------------------------|-----|

|   | 8.1  | K53 Signal Multiplexing and Pin Assignments | .72 |

|   | 8.2  | K53 Pinouts                                 | .78 |

| 9 | Rev  | ision History                               | .80 |

# 1 Ordering parts

# 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to freescale.com and perform a part number search for the following device numbers: PK53 and MK53.

# 2 Part identification

### 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 2.2 Format

Part numbers for this device have the following format:

Q K## A M FFF R T PP CC N

# 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description          | Values                                                                                     |

|-------|----------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| K##   | Kinetis family       | • K53                                                                                      |

| A     | Key attribute        | <ul> <li>D = Cortex-M4 w/ DSP</li> <li>F = Cortex-M4 w/ DSP and FPU</li> </ul>             |

| М     | Flash memory type    | <ul> <li>N = Program flash only</li> <li>X = Program flash and FlexMemory</li> </ul>       |

Table continues on the next page ...

#### Terminology and guidelines

| Field | Description                 | Values                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> <li>256 = 256 KB</li> <li>512 = 512 KB</li> <li>1M0 = 1 MB</li> <li>2M0 = 2 MB</li> </ul>                                                                                                                                                                                                                                                                                  |

| R     | Silicon revision            | <ul> <li>Z = Initial</li> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LF = 48 LQFP (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>MP = 64 MAPBGA (5 mm x 5 mm)</li> <li>LK = 80 LQFP (12 mm x 12 mm)</li> <li>LL = 100 LQFP (14 mm x 14 mm)</li> <li>MC = 121 MAPBGA (8 mm x 8 mm)</li> <li>LQ = 144 LQFP (20 mm x 20 mm)</li> <li>MD = 144 MAPBGA (13 mm x 13 mm)</li> <li>MJ = 256 MAPBGA (17 mm x 17 mm)</li> </ul> |

| СС    | Maximum CPU frequency (MHz) | <ul> <li>5 = 50 MHz</li> <li>7 = 72 MHz</li> <li>10 = 100 MHz</li> <li>12 = 120 MHz</li> <li>15 = 150 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                          |

| N     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

# 2.4 Example

This is an example part number:

MK53DN512ZVMD10

# 3 Terminology and guidelines

# 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

# 3.1.1 Example

This is an example of an operating requirement:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

# 3.2 Definition: Operating behavior

An *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

### 3.2.1 Example

This is an example of an operating behavior:

| Symbol | Description                                  | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| •••    | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

# 3.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

### 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 3.4 Definition: Rating

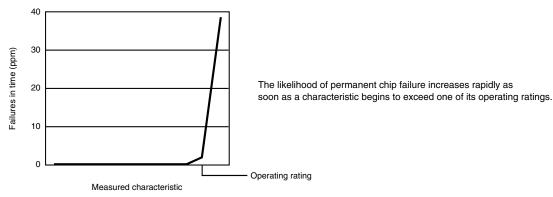

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- Handling ratings apply when the chip is not powered.

### 3.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

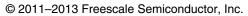

# 3.5 Result of exceeding a rating

Terminology and guidelines

# 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 3.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

# 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

### 3.8.2 Example 2

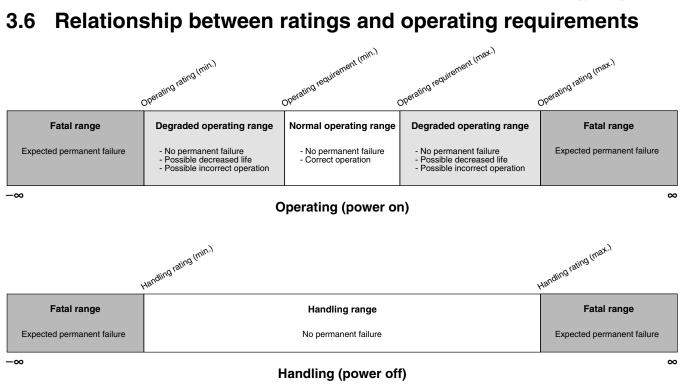

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 3.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | ٥°C  |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 4 Ratings

# 4.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

|                  | Solder temperature, leaded    | —    | 245  |      |       |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 4.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105°C      | -100  | +100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

# 4.4 Voltage and current operating ratings

General

| Symbol              | Description                                                    | Min.                  | Max.                  | Unit |

|---------------------|----------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>     | Digital supply voltage                                         | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>     | Digital supply current                                         | —                     | 185                   | mA   |

| V <sub>DIO</sub>    | Digital input voltage (except RESET, EXTAL, and XTAL)          | -0.3                  | 5.5                   | V    |

| V <sub>AIO</sub>    | Analog <sup>1</sup> , RESET, EXTAL, and XTAL input voltage     | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub>      | Maximum current single pin limit (applies to all digital pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub>    | Analog supply voltage                                          | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>USB_DP</sub> | USB_DP input voltage                                           | -0.3                  | 3.63                  | V    |

| V <sub>USB_DM</sub> | USB_DM input voltage                                           | -0.3                  | 3.63                  | V    |

| VREGIN              | USB regulator input                                            | -0.3                  | 6.0                   | V    |

| V <sub>BAT</sub>    | RTC battery supply voltage                                     | -0.3                  | 3.8                   | V    |

1. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

# 5 General

### 5.1 AC electrical characteristics

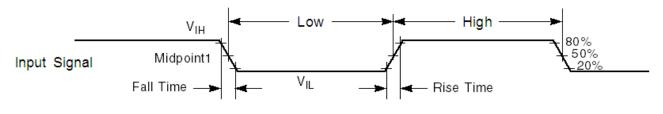

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

#### Figure 1. Input signal measurement reference

All digital I/O switching characteristics assume:

- 1. output pins

- have C<sub>L</sub>=30pF loads,

- are configured for fast slew rate (PORTx\_PCRn[SRE]=0), and

- are configured for high drive strength (PORTx\_PCRn[DSE]=1)

- 2. input pins

- have their passive filter disabled (PORTx\_PCRn[PFE]=0)

# 5.2 Nonswitching electrical specifications

### 5.2.1 Voltage and current operating requirements Table 1. Voltage and current operating requirements

| Symbol              | Description                                                                                                                                                                                        | Min.                  | Max.                 | Unit | Notes |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|-------|

| V <sub>DD</sub>     | Supply voltage                                                                                                                                                                                     | 1.71                  | 3.6                  | V    |       |

| V <sub>DDA</sub>    | Analog supply voltage                                                                                                                                                                              | 1.71                  | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$  | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                                                          | -0.1                  | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$  | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                                                                                          | -0.1                  | 0.1                  | V    |       |

| V <sub>BAT</sub>    | RTC battery supply voltage                                                                                                                                                                         | 1.71                  | 3.6                  | V    |       |

| V <sub>IH</sub>     | Input high voltage                                                                                                                                                                                 |                       |                      |      |       |

|                     | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                                                        | $0.7 \times V_{DD}$   | —                    | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                       | $0.75 \times V_{DD}$  | _                    | V    |       |

| V <sub>IL</sub>     | Input low voltage                                                                                                                                                                                  |                       |                      |      |       |

|                     | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                                                       | _                     | $0.35 \times V_{DD}$ | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                       | _                     | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>    | Input hysteresis                                                                                                                                                                                   | $0.06 \times V_{DD}$  | _                    | V    |       |

| I <sub>ICDIO</sub>  | Digital pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                                                | -5                    | _                    | mA   | 1     |

| I <sub>ICAIO</sub>  | Analog <sup>2</sup> , EXTAL, and XTAL pin DC injection current —<br>single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V (Negative current injection)                                           | -5                    |                      | mA   | 3     |

|                     | <ul> <li>V<sub>IN</sub> &gt; V<sub>DD</sub>+0.3V (Positive current injection)</li> </ul>                                                                                                           | —                     | +5                   |      |       |

| I <sub>ICcont</sub> | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins<br>• Negative current injection | -25                   |                      | mA   |       |

|                     | Positive current injection                                                                                                                                                                         |                       | _                    |      |       |

| V <sub>ODPU</sub>   | Open drain pullup voltage level                                                                                                                                                                    | V <sub>DD</sub>       | V <sub>DD</sub>      | V    | 4     |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                     | 1.2                   | —                    | V    |       |

| V <sub>RFVBAT</sub> | $V_{\text{BAT}}$ voltage required to retain the VBAT register file                                                                                                                                 | V <sub>POR_VBAT</sub> | _                    | V    |       |

- All 5 V tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through an ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> is less than V<sub>DIO\_MIN</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICDIO</sub>I.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function. Additionally, EXTAL and XTAL are analog pins.

- 3. All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>AIO\_MIN</sub> or greater than V<sub>AIO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is exposed to positive and negative injection currents.

- 4. Open drain outputs must be pulled to VDD.

# 5.2.2 LVD and POR operating requirements

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>   | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| $V_{LVDH}$         | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| $V_{LVW1H}$        | Level 1 falling (LVWV=00)                                   | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | Level 3 falling (LVWV=10)                                   | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range   | _    | ±80  | _    | mV   |       |

| $V_{LVDL}$         | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    |       |

|                    | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| $V_{LVW1L}$        | Level 1 falling (LVWV=00)                                   | 1.74 | 1.80 | 1.86 | V    |       |

| V <sub>LVW2L</sub> | Level 2 falling (LVWV=01)                                   | 1.84 | 1.90 | 1.96 | V    |       |

| V <sub>LVW3L</sub> | Level 3 falling (LVWV=10)                                   | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$        | Level 4 falling (LVWV=11)                                   | 2.04 | 2.10 | 2.16 | V    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range    | —    | ±60  | -    | mV   |       |

| $V_{BG}$           | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   |       |

1. Rising thresholds are falling threshold + hysteresis voltage

#### Table 3. VBAT power operating requirements

| Symbol                | Description                            | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------|------|------|------|------|-------|

| V <sub>POR_VBAT</sub> | Falling VBAT supply POR detect voltage | 0.8  | 1.1  | 1.5  | V    |       |

### 5.2.3 Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

| Symbol           | Description                                                                                        | Min.                  | Typ. <sup>1</sup> | Max. | Unit | Notes   |

|------------------|----------------------------------------------------------------------------------------------------|-----------------------|-------------------|------|------|---------|

| V <sub>OH</sub>  | Output high voltage — high drive strength                                                          |                       |                   |      |      |         |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -9mA                                | V <sub>DD</sub> – 0.5 | —                 | —    | V    |         |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -3\text{mA}$ | V <sub>DD</sub> – 0.5 | —                 | _    | V    |         |

|                  | Output high voltage — low drive strength                                                           |                       |                   |      |      |         |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -2mA                                | V <sub>DD</sub> – 0.5 | _                 | _    | V    |         |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -0.6mA                             | V <sub>DD</sub> – 0.5 | —                 | _    | V    |         |

| I <sub>OHT</sub> | Output high current total for all ports                                                            |                       | _                 | 100  | mA   |         |

| V <sub>OL</sub>  | Output low voltage — high drive strength                                                           |                       |                   |      |      | 2       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 9mA                                 | _                     | —                 | 0.5  | V    |         |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 3mA                                | _                     | —                 | 0.5  | V    |         |

|                  | Output low voltage — low drive strength                                                            |                       |                   |      |      | -       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 2mA                                 | _                     | —                 | 0.5  | V    |         |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 0.6mA                              | _                     | —                 | 0.5  | V    |         |

| I <sub>OLT</sub> | Output low current total for all ports                                                             |                       | _                 | 100  | mA   |         |

| I <sub>INA</sub> | Input leakage current, analog pins and digital pins configured as analog inputs                    |                       |                   |      |      | 3, 4    |

|                  | • $V_{SS} \le V_{IN} \le V_{DD}$                                                                   |                       |                   |      |      |         |

|                  | <ul> <li>All pins except EXTAL32, XTAL32,<br/>EXTAL, XTAL</li> </ul>                               | _                     | 0.002             | 0.5  | μA   |         |

|                  | • EXTAL (PTA18) and XTAL (PTA19)                                                                   | _                     | 0.004             | 1.5  | μA   |         |

|                  | • EXTAL32, XTAL32                                                                                  | _                     | 0.075             | 10   | μΑ   |         |

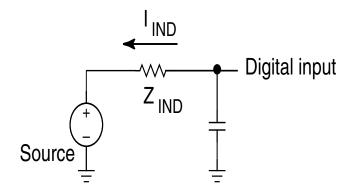

| I <sub>IND</sub> | Input leakage current, digital pins                                                                |                       |                   |      |      | 4, 5    |

|                  | • $V_{SS} \le V_{IN} \le V_{IL}$                                                                   |                       |                   |      |      |         |

|                  | All digital pins                                                                                   | _                     | 0.002             | 0.5  | μA   |         |

|                  | • V <sub>IN</sub> = V <sub>DD</sub>                                                                |                       |                   |      |      |         |

|                  | All digital pins except PTD7                                                                       | _                     | 0.002             | 0.5  | μA   |         |

|                  | • PTD7                                                                                             | _                     | 0.004             | 1    | μΑ   |         |

| I <sub>IND</sub> | Input leakage current, digital pins                                                                |                       |                   |      |      | 4, 5, 6 |

|                  | • V <sub>IL</sub> < V <sub>IN</sub> < V <sub>DD</sub>                                              |                       |                   |      |      |         |

|                  | • V <sub>DD</sub> = 3.6 V                                                                          | _                     | 18                | 26   | μA   |         |

|                  | • V <sub>DD</sub> = 3.0 V                                                                          |                       | 12                | 49   | μA   |         |

|                  | • V <sub>DD</sub> = 2.5 V                                                                          |                       | 8                 | 13   | μA   |         |

|                  | • V <sub>DD</sub> = 1.7 V                                                                          | _                     | 3                 | 6    | μA   |         |

Table continues on the next page...

#### General

| Symbol           | Description                                 | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|------------------|---------------------------------------------|------|-------------------|------|------|-------|

| I <sub>IND</sub> | Input leakage current, digital pins         |      |                   |      |      | 4, 5  |

|                  | • V <sub>DD</sub> < V <sub>IN</sub> < 5.5 V | —    | 1                 | 50   | μA   |       |

| Z <sub>IND</sub> | Input impedance examples, digital pins      |      |                   |      |      | 4, 7  |

|                  | • V <sub>DD</sub> = 3.6 V                   | _    | _                 | 48   | kΩ   |       |

|                  | • V <sub>DD</sub> = 3.0 V                   | _    | _                 | 55   | kΩ   |       |

|                  | • V <sub>DD</sub> = 2.5 V                   | _    | _                 | 57   | kΩ   |       |

|                  | • V <sub>DD</sub> = 1.7 V                   | _    | _                 | 85   | kΩ   |       |

| R <sub>PU</sub>  | Internal pullup resistors                   | 20   | 35                | 50   | kΩ   | 8     |

| R <sub>PD</sub>  | Internal pulldown resistors                 | 20   | 35                | 50   | kΩ   | 9     |

#### Table 4. Voltage and current operating behaviors (continued)

- 1. Typical values characterized at  $25^{\circ}$ C and VDD = 3.6 V unless otherwise noted.

- 2. Open drain outputs must be pulled to  $V_{\text{DD}}$ .

- 3. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 4. Digital pins have an associated GPIO port function and have 5V tolerant inputs, except EXTAL and XTAL.

- 5. Internal pull-up/pull-down resistors disabled.

- 6. Characterized, not tested in production.

- 7. Examples calculated using  $V_{IL}$  relation,  $V_{DD}$ , and max  $I_{IND}$ :  $Z_{IND}=V_{IL}/I_{IND}$ . This is the impedance needed to pull a high signal to a level below  $V_{IL}$  due to leakage when  $V_{IL} < V_{IN} < V_{DD}$ . These examples assume signal source low = 0 V.

- 8. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and Vinput = V<sub>SS</sub>

- 9. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 100 MHz

- Bus clock = 50 MHz

- FlexBus clock = 50 MHz

- Flash clock = 25 MHz

- MCG mode: FEI

| Symbol           | Description                                                                                                                                                        | Min. | Max.                                   | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.71 V to execution of the first instruction across the operating temperature range of the chip. |      |                                        | μs   | 1     |

|                  | • $V_{DD}$ slew rate $\geq 5.7$ kV/s                                                                                                                               | —    | 300                                    |      |       |

|                  | <ul> <li>V<sub>DD</sub> slew rate &lt; 5.7 kV/s</li> </ul>                                                                                                         | _    | 1.7 V / (V <sub>DD</sub><br>slew rate) |      |       |

|                  | • VLLS1 → RUN                                                                                                                                                      | _    | 134                                    | μs   |       |

|                  | VLLS2 → RUN                                                                                                                                                        | —    | 96                                     | μs   |       |

|                  | VLLS3 → RUN                                                                                                                                                        | _    | 96                                     | μs   |       |

|                  | • LLS → RUN                                                                                                                                                        | _    | 6.2                                    | μs   |       |

|                  | VLPS → RUN                                                                                                                                                         | _    | 5.9                                    | μs   |       |

|                  | • STOP → RUN                                                                                                                                                       |      | 5.9                                    | μs   |       |

### Table 5. Power mode transition operating behaviors

1. Normal boot (FTFL\_OPT[LPBOOT]=1)

## 5.2.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

| Symbol               | Description                                                                   | Min. | Тур. | Max.     | Unit | Notes |

|----------------------|-------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>     | Analog supply current                                                         | _    | —    | See note | mA   | 1     |

| I <sub>DD_RUN</sub>  | Run mode current — all peripheral clocks disabled, code executing from flash  |      |      |          |      | 2     |

|                      | • @ 1.8V                                                                      | —    | 45   | 70       | mA   |       |

|                      | • @ 3.0V                                                                      | —    | 47   | 72       | mA   |       |

| I <sub>DD_RUN</sub>  | Run mode current — all peripheral clocks enabled, code executing from flash   |      |      |          |      | 3, 4  |

|                      | • @ 1.8V                                                                      | _    | 61   | 85       | mA   |       |

|                      | • @ 3.0V                                                                      |      |      |          |      |       |

|                      | • @ 25°C                                                                      | _    | 63   | 71       | mA   |       |

|                      | • @ 125°C                                                                     | —    | 72   | 87       | mA   |       |

| I <sub>DD_WAIT</sub> | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled    | —    | 35   | -        | mA   | 2     |

| I <sub>DD_WAIT</sub> | Wait mode reduced frequency current at 3.0 V — all peripheral clocks disabled | —    | 15   | -        | mA   | 5     |

| I <sub>DD_VLPR</sub> | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled     | _    | N/A  | -        | mA   | 6     |

Table continues on the next page...

#### General

| Symbol                | Description                                                                | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VLPR</sub>  | Very-low-power run mode current at 3.0 V — all peripheral clocks enabled   | _    | N/A  | —    | mA   | 7     |

| I <sub>DD_VLPW</sub>  | Very-low-power wait mode current at 3.0 V — all peripheral clocks disabled | —    | N/A  | _    | mA   | 8     |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V                                                 |      |      |      |      |       |

|                       | • @40 to 25°C                                                              | _    | 0.59 | 1.4  | mA   |       |

|                       | • @ 70°C                                                                   | _    | 2.26 | 7.9  | mA   |       |

|                       | • @ 105°C                                                                  | —    | 5.94 | 19.2 | mA   |       |

| I <sub>DD_VLPS</sub>  | Very-low-power stop mode current at 3.0 V                                  |      |      |      |      |       |

|                       | • @ -40 to 25°C                                                            |      | 93   | 435  | μA   |       |

|                       | • @ 70°C                                                                   |      | 520  | 2000 | μA   |       |

|                       | • @ 105°C                                                                  | —    | 1350 | 4000 | μA   |       |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                     |      |      |      |      | 9     |

|                       | • @40 to 25°C                                                              | _    | 4.8  | 20   | μA   |       |

|                       | • @ 70°C                                                                   | _    | 28   | 68   | μA   |       |

|                       | • @ 105°C                                                                  | _    | 126  | 270  | μA   |       |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                              |      |      |      |      | 9     |

|                       | • @ -40 to 25°C                                                            | —    | 3.1  | 8.9  | μA   |       |

|                       | • @ 70°C                                                                   | _    | 17   | 35   | μA   |       |

|                       | • @ 105°C                                                                  | _    | 82   | 148  | μA   |       |

| I <sub>DD_VLLS2</sub> | Very low-leakage stop mode 2 current at 3.0 V                              |      |      |      |      |       |

|                       | • @40 to 25°C                                                              | _    | 2.2  | 5.4  | μA   |       |

|                       | • @ 70°C                                                                   | _    | 7.1  | 12.5 | μA   |       |

|                       | • @ 105°C                                                                  | —    | 41   | 125  | μΑ   |       |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                              |      |      |      |      |       |

|                       | • @ -40 to 25°C                                                            | _    | 2.1  | 7.6  | μA   |       |

|                       | • @ 70°C                                                                   | _    | 6.2  | 13.5 | μA   |       |

|                       | • @ 105°C                                                                  | —    | 30   | 46   | μΑ   |       |

| I <sub>DD_VBAT</sub>  | Average current with RTC and 32kHz disabled at 3.0 V                       |      |      |      |      |       |

|                       | • @ -40 to 25°C                                                            | _    | 0.33 | 0.39 | μA   |       |

|                       | • @ 70°C                                                                   | _    | 0.60 | 0.78 | μA   |       |

|                       | • @ 105°C                                                                  |      | 1.97 | 2.9  | μA   |       |

### Table 6. Power consumption operating behaviors (continued)

Table continues on the next page ...

| Symbol               | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|----------------------|---------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VBAT</sub> | Average current when CPU is not accessing RTC registers |      |      |      |      | 10    |

|                      | • @ 1.8V                                                |      |      |      |      |       |

|                      | • @ -40 to 25°C                                         |      | 0.71 | 0.81 | μA   |       |

|                      | • @ 70°C                                                |      | 1.01 | 1.3  | μΑ   |       |

|                      | • @ 105°C                                               | _    | 2.82 | 4.3  | μA   |       |

|                      | • @ 3.0V                                                |      |      |      | Prot |       |

|                      | <ul> <li>@ -40 to 25°C</li> </ul>                       | _    | 0.84 | 0.94 | μA   |       |

|                      | • @ 70°C                                                | _    | 1.17 | 1.5  | μA   |       |

|                      | • @ 105°C                                               | _    | 3.16 | 4.6  | μA   |       |

Table 6. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock . MCG configured for FEI mode. All peripheral clocks disabled.

- 3. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 4. Max values are measured with CPU executing DSP instructions.

- 5. 25MHz core and system clock, 25MHz bus clock, and 12.5MHz FlexBus and flash clock. MCG configured for FEI mode.

- 6. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 7. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 8. 2 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 9. Data reflects devices with 128 KB of RAM. For devices with 64 KB of RAM, power consumption is reduced by 2 µA.

- 10. Includes 32kHz oscillator current and RTC operation.

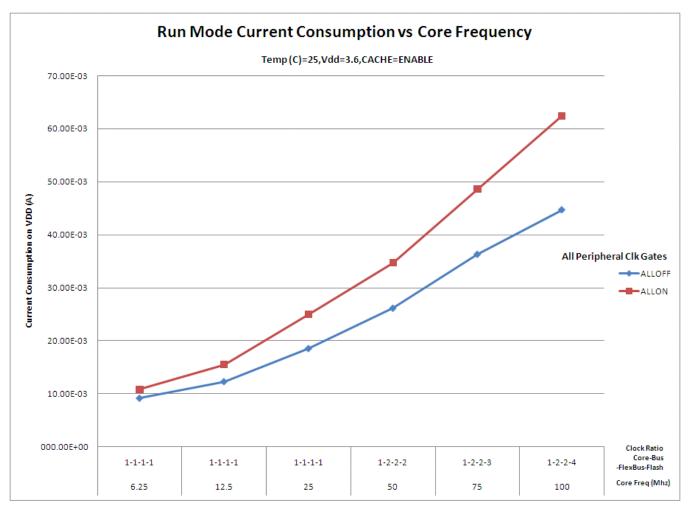

### 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater than 50 MHz frequencies.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFL

Figure 2. Run mode supply current vs. core frequency

### 5.2.6 EMC radiated emissions operating behaviors

#### Table 7. EMC radiated emissions operating behaviors as measured on 144LQFP and 144MAPBGA packages

| Symbol           | Description                        | Frequency<br>band (MHz) | 144LQFP | 144MAPBGA | Unit | Notes |

|------------------|------------------------------------|-------------------------|---------|-----------|------|-------|

| V <sub>RE1</sub> | Radiated emissions voltage, band 1 | 0.15–50                 | 23      | 12        | dBµV | 1,2   |

| V <sub>RE2</sub> | Radiated emissions voltage, band 2 | 50–150                  | 27      | 24        | dBµV |       |

| V <sub>RE3</sub> | Radiated emissions voltage, band 3 | 150–500                 | 28      | 27        | dBµV |       |

| V <sub>RE4</sub> | Radiated emissions voltage, band 4 | 500–1000                | 14      | 11        | dBµV |       |

| $V_{RE\_IEC}$    | IEC level                          | 0.15–1000               | К       | К         |      | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions – TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD} = 3.3 \text{ V}, T_A = 25 \text{ °C}, f_{OSC} = 12 \text{ MHz} \text{ (crystal)}, f_{SYS} = 96 \text{ MHz}, f_{BUS} = 48 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

#### 5.2.8 Capacitance attributes

#### Table 8. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

### 5.3 Switching specifications

### 5.3.1 Device clock specifications

#### Table 9. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit | Notes |  |

|----------------------|--------------------------------------------------------|------|------|------|-------|--|

|                      | Normal run mode                                        |      |      |      |       |  |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 100  | MHz  |       |  |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |       |  |

| f <sub>ENET</sub>    | System and core clock when ethernet in operation       |      |      | MHz  |       |  |

|                      | • 10 Mbps                                              | 5    | —    |      |       |  |

|                      | • 100 Mbps                                             | 50   | —    |      |       |  |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 50   | MHz  |       |  |

| FB_CLK               | FlexBus clock                                          | _    | 50   | MHz  |       |  |

| f <sub>FLASH</sub>   | Flash clock                                            | —    | 25   | MHz  |       |  |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | _    | 25   | MHz  |       |  |

#### General

### 5.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, CMT, IEEE 1588 timer, and I<sup>2</sup>C signals.

| Symbol | Description                                                                                                 | Min. | Max. | Unit                | Notes |

|--------|-------------------------------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                          | 1.5  | _    | Bus clock<br>cycles | 1, 2  |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter enabled) — Asynchronous path  | 100  | -    | ns                  | 3     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled) — Asynchronous path | 16   | -    | ns                  | 3     |

|        | External reset pulse width (digital glitch filter disabled)                                                 | 100  | _    | ns                  | 3     |

|        | Mode select (EZP_CS) hold time after reset deassertion                                                      | 2    | -    | Bus clock<br>cycles |       |

|        | Port rise and fall time (high drive strength)                                                               |      |      |                     | 4     |

|        | Slew disabled                                                                                               |      |      |                     |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                                                                                | _    | 12   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | _    | 6    | ns                  |       |

|        | Slew enabled                                                                                                |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | _    | 36   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | _    | 24   | ns                  |       |

|        | Port rise and fall time (low drive strength)                                                                |      |      |                     | 5     |

|        | Slew disabled                                                                                               |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | —    | 12   | ns                  |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                                                                                 | _    | 6    | ns                  |       |

|        | Slew enabled                                                                                                |      |      |                     |       |

|        | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                             | —    | 36   | ns                  |       |

|        | <ul> <li>2.7 ≤ V<sub>DD</sub> ≤ 3.6V</li> </ul>                                                             | _    | 24   | ns                  |       |

Table 10. General switching specifications

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

- 4. 75 pF load

- 5. 15 pF load

### 5.4 Thermal specifications

# 5.4.1 Thermal operating requirements

Table 11.

Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 85   | °C   |

### 5.4.2 Thermal attributes

| Board type           | Symbol            | Description                                                                                                          | 144 LQFP | 144<br>MAPBGA | Unit | Notes |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|----------|---------------|------|-------|

| Single-layer<br>(1s) | R <sub>θJA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 45       | 48            | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>eJA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection)                                             | 36       | 29            | °C/W | 1     |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 36       | 38            | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 30       | 25            | °C/W | 1     |

| _                    | R <sub>0JB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                       | 24       | 16            | °C/W | 2     |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                                                           | 9        | 9             | °C/W | 3     |

| _                    | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 2        | 2             | °C/W | 4     |

1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

#### Peripheral operating requirements and behaviors

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

### 6.1 Core modules

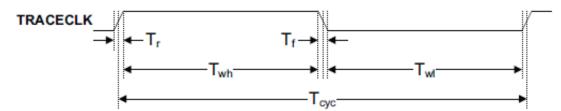

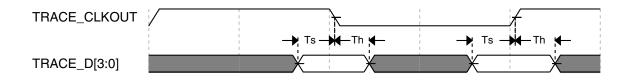

### 6.1.1 Debug trace timing specifications

#### Table 12. Debug trace operating behaviors

| Symbol           | Description              | Min.                | Max. | Unit |

|------------------|--------------------------|---------------------|------|------|

| T <sub>cyc</sub> | Clock period             | Frequency dependent |      | MHz  |

| $T_{wl}$         | Low pulse width          | 2                   | —    | ns   |

| T <sub>wh</sub>  | High pulse width         | 2                   | —    | ns   |

| T <sub>r</sub>   | Clock and data rise time | _                   | 3    | ns   |

| Τ <sub>f</sub>   | Clock and data fall time | _                   | 3    | ns   |

| Τs               | Data setup               | 3                   | —    | ns   |

| T <sub>h</sub>   | Data hold                | 2                   | —    | ns   |

Figure 3. TRACE\_CLKOUT specifications

### 6.1.2 JTAG electricals

| Table 13. | JTAG | limited | voltage | range | electricals |

|-----------|------|---------|---------|-------|-------------|

|-----------|------|---------|---------|-------|-------------|

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 25   |      |

|        | Serial Wire Debug                                  | 0    | 50   |      |

| J2     | TCLK cycle period                                  | 1/J1 |      | ns   |

| J3     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 20   | _    | ns   |

|        | Serial Wire Debug                                  | 10   | _    | ns   |

| J4     | TCLK rise and fall times                           |      | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | —    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 0    | —    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | —    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | —    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | —    | ns   |

| J11    | TCLK low to TDO data valid                         |      | 17   | ns   |

| J12    | TCLK low to TDO high-Z                             | —    | 17   | ns   |

| J13    | TRST assert time                                   | 100  |      | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8    |      | ns   |

#### Table 14. JTAG full voltage range electricals

| Symbol | Description                 | Min. | Max. | Unit |

|--------|-----------------------------|------|------|------|

|        | Operating voltage           | 1.71 | 3.6  | V    |

| J1     | TCLK frequency of operation |      |      | MHz  |

|        | Boundary Scan               | 0    | 10   |      |

|        | JTAG and CJTAG              | 0    | 20   |      |

|        | Serial Wire Debug           | 0    | 40   |      |

| J2     | TCLK cycle period           | 1/J1 |      | ns   |

Table continues on the next page...