Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ML67Q5260**

**DFT Based Fingerprint Authentication LSI**

## **GENERAL DESCRIPTION**

The ML67Q5260 is a single chip LSI that executes fingerprint authentication without external memory by using the embedded fingerprint authentication accelerator. This fingerprint authentication accelerator uses DFT(Discrete Fourier Transform) based algorithm licensed from Precise Biometrics, and supports AuthenTec's slide sensors and certain touch sensors from several sensor manufacturers. Besides the ML67Q5260 has the secure circuit to protect enrolled fingerprint data from unauthorized access. Thus this LSI helps customers quickly design new products that offer convenient security as far as high performance fingerprint authentication, low cost, small size and high level of security.

#### **FEATURES**

- Fingerprint authentication

- DFT (Discrete Fourier Transform) based algorithm licensed from Precise Biometrics

This DFT based algorithm achieves a lower FTE (False To Enrollment rate) and a higher authentication accuracy especially when a slide sensor is used, as compared to the minutiae algorithm.

- Easy-to-use

The fingerprint authentication is performed by the fingerprint authentication accelerator, which does not ask customers for so complicated control.

- No external memory

Customer's application program and up to 45 fingerprint data can be stored in the embedded Flash memory on the ML67Q5260. No external memory is required, when a slide sensor is used.

- High-speed authentication, besides low power consumption

The highly optimized fingerprint authentication accelerator achieves high-speed authentication using a low speed clock.

Authentication : < 0.8 seconds (1:1 authentication)

< 1.8 seconds (1:45 authentication)

Enrollment : < 2 seconds/finger

- Applicable fingerprint sensor

Slide sensor : AuthenTec AES1751 ( $128 \times 8$  pixels)

## • CPU

- 32-bit RISC CPU (ARM7TDMI-S)

- Little endian format

- Instruction system: A high-density 32-bit instruction and a 16-bit instruction of high-object efficiency, which is the subset of the 32-bit instruction, can be executed in mixed mode.

- General-purpose register: 32 bits x 31 registers

- Built-in barrel shifter (ALU and barrel shift operation can be executed by one instruction)

- Built-in debugging function (JTAG interface) The JTAG interface pin is shared with GPIO.

- Built-in Memories

- 16 Kbyte working RAM for CPU

- 128 Kbyte Flash ROM for application program and fingerprint template data, whose erase/rewrite times are maximum 10,000

- 8 Kbyte Mask ROM for update of program in the Built-in Flash ROM

- Interrupt control

- 1 FIQ resource External : 1 - 20 IRQ resources

External: 3, Internal: 17 7 priority levels for each source

- DMA controller (DMAC)

- 2 channels

- Enable to allocate multiple DMA transfer request sources for each channel.

- Channel priority: fixed mode/round robin mode

- DMA transfer mode: cycle steal mode/burst mode

- DMA request type: software requests/hardware requests

- Maximum transfer count: 65,536

- Data transfer size: 8 bits/16 bits/32 bits

- Transfer request source: CPU, SPI, Synchronous SIO, Smartcard IF

#### • GPIO

- 13 bits  $\times$  1 channel, 12 bits  $\times$  1 channel

- Enable to setting input mode or output mode for each bit

- Enable to setting as interruption source for each bit

- Interruption mode: level/edge and positive logic/negative logic

#### • Timer

- 16-bit auto reload timer × 4 channel

- Watch dog timer (WDT)

- 16-bit timer

- 8.389 seconds max. (when CPU operating frequency is 32 MHz)

- Enables generation of interrupt or reset by setting

## • SIO (UART)

- Full-duplex asynchronous mode

- Built-in baud rate generator

#### • SPI

- 2 channels of full-duplex serial peripheral interfaces

- Operating mode: master mode/slave mode

- Data transfer size: 8 bits (byte) / 16 bits (word)

- Built-in 16-byte/16-word FIFO on the transmission side and the reception side

- Supports DMA transfer (master/slave mode)

- Synchronous SIO (SSIO)

- clock synchronous serial port × 1 channel

- Data transfer size : 8 bits (byte)

- Selectable clock polarity

- Selectable LSB first or MSB first

- Operation mode: master mode/slave mode

- Supports DMAC transfer (in master mode only)

- Smart Card interface (Smartcard IF)

- ISO UART × 1 channel

- Built-in 16-byte FIFO

- Built-in parity error counter in receive mode and transmit mode at automatic retransmission

- Supports asynchronous protocol of T = 0 and T = 1 according to ISO7816 and EMV

- Built-in error detection code generation and error detection functions by hardware

- Supports DMA transfer

- USB2.0 full-speed device

- Compliant with Universal Serial Bus (USB) 2.0

- Full speed (12 Mbps)  $\times$  1 port.

- End points: 5 or 6

- Supports all data transfer types (control transfer, bulk transfer, interrupt transfer, isochronous transfer).

- Built-in SOP generation and CRC5/16 generation functions

- Access size to data transfer FIFOs: 8 bits/16 bits/32 bits

- Random number generator (RANDOM)

- Generates 8-bit random numbers

- Clock

- Input clock: 12 MHz (oscillator connected)

- System clock (CPU operating clock): 32 MHz

System clock is generated by PLL using 12MHz clock.

- Output clock: 6/12 MHz for fingerprint sensor

- Power management

- Power saving mode

- •Individual module clock stop mode:

Clock operation/stop can be set for each functional block.

•HALT mode:

Only CPU clock is stopped.

•STOP mode:

All clocks are stopped, and start /stop of internal PLL and oscillator circuit are selectable.

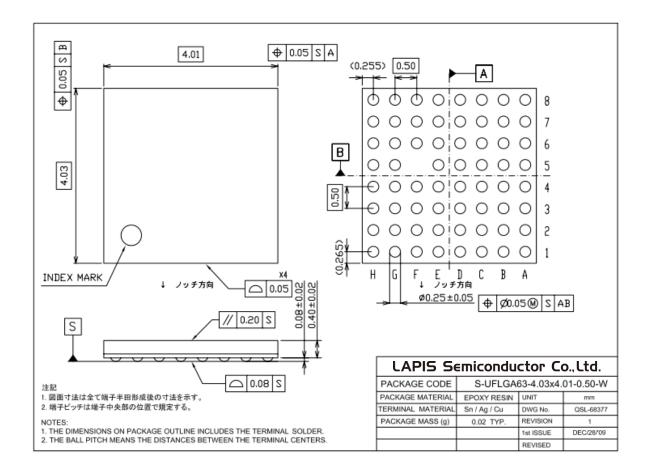

Package

- 63-pin WCSP Package (S-UFLGA63-4.03x4.01-0.50-W)

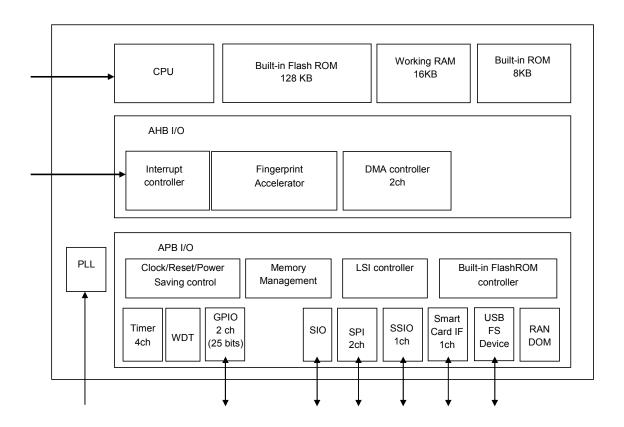

# **BLOCK DIAGRAM**

Figure 1 Block Diagram

# **PIN LAYOUT**

| TESTF            | PB01<br>(SIMVCTL0) | PB03<br>(SIMVCMD) | PB04<br>(SIMDATA)  | PB06<br>(SIMCLK)   | NTRST              | VDDCORE            | BSEL1              | 8 |

|------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---|

| PA08<br>(SSIOTX) | PB00<br>(SIMDET)   | VDDIO             | VDDCORE            | PR0                | TDO                | TCK                | VDDIO              | 7 |

| PA09<br>(SSIORX) | PA10<br>(SSIOCLK)  | GNDIO             | GNDCORE            | GNDCORE            | TDI                | RTCK               | GNDIO              | 6 |

| AFSEL            | PUCTL              |                   | PB02<br>(SIMVCTL1) | PB05<br>(SIMRST)   | TMS                | PA12<br>(SIORX)    | GNDCORE            | 5 |

| PB11<br>(CLKOUT) | GNDCORE            | DP                | PB08<br>(EXINT0)   | XI                 | PA07<br>(SPI1SCK)  | PA11<br>(SIOTX)    | VDDCORE            | 4 |

| VDDCORE          | DM                 | PB09<br>(EXINT1)  | RESETN             | хо                 | PA00<br>(SPI0MOSI) | PA04<br>(SPI1MOSI) | PA02<br>(SPI0SSN)  | 3 |

| VDDUSB           | PB10<br>(VBUS)     | VDDPLL            | VDDIO              | PA05<br>(SPI1MISO) | PA03<br>(SPI0SCK)  | VDDIO              | PA01<br>(SPI0MISO) | 2 |

| GNDUSB           | PB07<br>(FIQ)      | GNDPLL            | PA06<br>(SPI1SSN)  | TESTE              | GNDIO              | VDDCORE            | GNDCORE            | 1 |

| Н                | G                  | F                 | E                  | D                  | С                  | В                  | А                  | - |

S-UFLGA61-4.03x4.01-0.50-W (Bottom View)

# PIN LIST

|         |          |     |          | Description              |                 |   |                                       |           |                |             |                   |               |          |

|---------|----------|-----|----------|--------------------------|-----------------|---|---------------------------------------|-----------|----------------|-------------|-------------------|---------------|----------|

|         |          |     |          | Primary function         |                 |   | Secondary function                    |           |                | iŧ          | ±                 | on            | a        |

| Pin No. | Pin name | 0/I | Polarity | Description              | O/I Description |   | Schmitt                               | PU/PD(*1) | Drive capacity | 5V Tolerant | Initial direction | Initial value |          |

| D4      | ΧI       | ı   | -        | Oscillation Pin          | -               | - | -                                     | -         | -              | -           | -                 | ı             | -        |

| D3      | XO       | 0   | -        | Oscillation Pin          | -               | - | -                                     | -         | -              | -           | -                 | 0             | -        |

| E3      | RESETN   | I   | Ν        | System Reset             | -               | - | -                                     | S         | PU             | -           | -                 | ı             | -        |

| D7      | PR0      | I   | Р        | Built-in ROM Port0 (*2)  | -               | - | -                                     | -         | PU             | -           | -                 | I             | -        |

| В6      | RTCK     | 0   | -        | JTAG Return Clock        | -               | - | -                                     | -         | -              | 4mA         | -                 | О             | L        |

| В7      | TCK      | I   | -        | JTAG Test Clock          | -               | - | -                                     | -         | PU             | _           | -                 | ı             | -        |

| C5      | TMS      | I   | Р        | JTAG Test Mode State     | -               | - | -                                     | _         | PU             | -           | -                 | I             | _        |

| C6      | TDI      | ı   | -        | JTAG Test Data In        | -               | - | -                                     | -         | PU             | -           | -                 | ı             | -        |

| C7      | TDO      | 0   | -        | JTAG Test Data Out       | _               | - | -                                     | -         | -              | 4mA         | -                 | 0             | Н        |

| C8      | NTRST    | ı   | N        | JTAG Test Reset          | -               | - | -                                     | -         | PU             | -           | -                 | ı             | -        |

| B5      | PA12     | I/O | -        | General Purpose Port A12 | ı               | - | SIO Receive Data                      | _         | -              | 4mA         | -                 | ı             | -        |

| B4      | PA11     | I/O | -        | General Purpose Port A11 | 0               | - | SIO Transmit Data                     | _         | _              | 4mA         | _                 | ı             | -        |

| G6      | PA10     | I/O | -        | General Purpose Port A10 | I/O             | - | SSIO Communication Clock              | _         | -              | 4mA         | _                 | Ť             | -        |

| H6      | PA09     | I/O | _        | General Purpose Port A9  | ı               | _ | SSIO Receive Data                     | _         | _              | 4mA         | _                 | ī             | -        |

| H7      | PA08     | I/O | _        | General Purpose Port A8  | 0               | - | SSIO Transmit Data                    | _         | _              | 4mA         | _                 | ī             | -        |

| C4      | PA07     | I/O | _        | General Purpose Port A7  | I/O             | _ | SPI Clock for CH1                     | _         | _              | 4mA         | _                 | i             | _        |

| E1      | PA06     | I/O | _        | General Purpose Port A6  | 1               | N | SPI Slave Select for CH1              | _         | -              | 4mA         | _                 | i             | _        |

|         | 17100    | "0  |          | ·                        | <u>'</u>        |   | SPI Data for CH1                      |           |                | 1111// \    |                   | •             | $\vdash$ |

| D2      | PA05     | I/O | -        | General Purpose Port A5  | I/O             | - | (Master Receive / Slave Transmit)     | -         | -              | 4mA         | -                 | I             | -        |

|         |          |     |          |                          |                 |   | SPI Data for CH1                      |           |                |             |                   |               |          |

| В3      | PA04     | I/O | -        | General Purpose Port A4  | I/O             | - | (Master Transmit / Slave Receive)     | -         | -              | 4mA         | -                 | I             | -        |

| C2      | PA03     | I/O | _        | General Purpose Port A3  | I/O             | _ | SPI Clock for CH0                     | _         | _              | 4mA         | _                 | ı             | -        |

| A3      | PA02     | I/O | _        | General Purpose Port A2  | ı               | Ν | SPI Slave Select for CH0              | _         | _              | 4mA         | _                 | ī             | -        |

|         |          |     |          | ·                        |                 |   | SPI Data for CH0                      |           |                | 1111/       |                   |               |          |

| A2      | PA01     | I/O | -        | General Purpose Port A1  | I/O             | - | (Master Receive / Slave Transmit)     | -         | -              | 4mA         | -                 | I             | -        |

|         |          |     |          |                          |                 |   | SPI Data for CH0                      |           |                |             |                   |               |          |

| C3      | PA00     | I/O | -        | General Purpose Port A0  | I/O             | - | (Master Transmit / Slave Receive )    | -         | -              | 4mA         | -                 | ı             | -        |

| H4      | PB11     | I/O | -        | General Purpose Port B11 | 0               | - | Clock Output (for sensor)             | -         | -              | 4mA         | -                 | ı             | -        |

| G2      | PB10     | I/O | -        | General Purpose Port B10 | ı               | - | External Interrupt Input ( for USB    | s         | _              | 4mA         | Т                 | 1             | _        |

|         | DDOO     |     |          | •                        |                 |   | VBUS)                                 | _         |                |             |                   |               | H        |

| F3      | PB09     | 1/0 | -        | General Purpose Port B09 | <br>            | - | External Interrupt Input (for IRQ 28) | S         | -              | 4mA         | -                 | <u> </u>      | -        |

| E4      | PB08     | I/O | -        | General Purpose Port B08 | l               | - |                                       |           | -              | 4mA         | -                 | 1             | -        |

| G1      | PB07     | I/O | -        | General Purpose Port B07 |                 | - | External Interrupt Input ( for FIQ)   | S         | -              | 4mA         | -                 | 1             | _        |

| D8      | PB06     | I/O | -        | General Purpose Port B06 | 0               | - | Smartcard IF Clock                    | -         | -              | 4mA         | -                 | ı             | -        |

| D5      | PB05     | I/O | -        | General Purpose Port B05 | 0               | N | Smartcard IF Reset                    | -         | -              | 4mA         | -                 | ı             | -        |

| E8      | PB04     | I/O | -        | General Purpose Port B04 | I/O             | - | Smartcard IF Serial Data              | -         | -              | 4mA         | -                 | ı             | -        |

| F8      | PB03     | I/O | -        | General Purpose Port B03 | 0               | - | Smartcard IF Power Control            | -         | -              | 4mA         | -                 | ı             | _        |

| E5      | PB02     | I/O | -        | General Purpose Port B02 | 0               | - | Smartcard IF Voltage Control 1        | -         | -              | 4mA         | -                 | ı             | -        |

| G8      | PB01     | I/O | -        | General Purpose Port B01 | 0               | - | Smartcard IF Voltage Control 0        | -         | -              | 4mA         | -                 | ı             | -        |

| G7      | PB00     | I/O | -        | General Purpose Port B00 | 0               | - | Smartcard IF Card Detection           | -         | -              | 4mA         | _                 | ı             |          |

| G3      | DM       | Α   | -        | USB dev D-               | -               | - | -                                     | -         |                | -           | -                 | I             |          |

| F4      | DP       | Α   | -        | USB dev D+               | -               | - | -                                     | -         | -              | -           | -                 | I             |          |

| G5      | PUCTL    | 0   | Р        | USB dev Pull-up Control  | _               | - | -                                     | -         | -              | 4mA         |                   | 0             | L        |

| H8      | TESTF    | Α   | -        | FLASH Test Pin           | _               | - | -                                     | -         |                | -           | _                 | Α             |          |

| A8      | BSEL1    | ı   | Р        | Boot Device Select 1     |                 | - | -                                     | -         | PD             | -           | -                 | Ι             | - ]      |

| H5      | AFSEL    | I   | Р        | JTAG Select (ARM/FLASH)  |                 | - | -                                     | -         | PD             | -           | -                 | I             | _ ]      |

| D1      | TESTE    |     | Р        | Test Mode Select         | -               | - | -                                     | -         | PD             | -           | -                 | Ι             | -        |

|                                |         |                               | Description |                            |         |                    |                |             |                   |               |     |       |     |

|--------------------------------|---------|-------------------------------|-------------|----------------------------|---------|--------------------|----------------|-------------|-------------------|---------------|-----|-------|-----|

|                                | e e     |                               |             | Primary function           |         | Secondary function |                |             | ۲۱)               | acity         | ant | ction | Ine |

| Pin No.                        | Pin nan | Polarity Description Ol Value |             | Description                | Schmitt | PU/PD(*1)          | Drive capacity | 5V Tolerant | Initial direction | Initial value |     |       |     |

| B8,<br>E7,<br>H3,<br>A4,<br>B1 | VDDCORE | -                             | -           | 1.8V Power Supply for CORE | -       | -                  | -              | -           | -                 | -             | -   | -     | -   |

| E6,<br>D6,<br>A5,<br>G4,       | GNDCORE | -                             | -           | Ground for CORE            | -       | -                  | -              | -           | -                 | -             | -   | -     | -   |

| A7,<br>F7,<br>B2,<br>E2        | VDDIO   | -                             | -           | 3.3V Power Supply for IO   | -       | -                  | -              | -           | ı                 | 1             | -   | -     | -   |

| A6,<br>F6,<br>C1               | GNDIO   | -                             | -           | Ground for IO              | -       | -                  | -              | -           | -                 | -             | -   | -     | _   |

| F2                             | VDDPLL  | -                             | -           | 1.8V Power Supply for PLL  | -       | -                  | -              | -           | -                 | -             | -   | -     | -   |

| F1                             | GNDPLL  | -                             | -           | Ground for PLL             | -       | -                  | <del>-</del>   | -           | -                 | -             | -   | -     | -   |

| H2                             | VDDUSB  | -                             | -           | 3.3V Power Supply for USB  | -       | -                  | <del>-</del>   | -           | -                 | -             | -   | _     |     |

| H1                             | GNDUSB  | -                             | -           | Ground for PLL             | -       | -                  | -              | -           | -                 | -             | -   | -     | -   |

<sup>\*1:</sup> PU/PD column:

PU: Pulled up with a built-in resistor

PD: Pulled down with a built-in resistor

For details, see the User's manual for USB firmware update function.

## **Termination of Pins Not Used**

| Pin name             | Pin termination      |

|----------------------|----------------------|

| DM, DP, PUCTL        | Open                 |

| PA00-12 PB00-11      | Pulled down          |

| TDO, RTCK            | Open                 |

| TCK, TMS, TDI, NTRST | Pulled up            |

| TESTF                | Must be used as open |

<sup>\*2:</sup> This pin is used in the Built-in ROM for an update function of the Built-in FlashROM.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                 | Symbol               | Condition                                       | Rating                          | Unit |

|-------------------------------------------|----------------------|-------------------------------------------------|---------------------------------|------|

| Digital power supply voltage CORE (1.8 V) | V <sub>DD_CORE</sub> |                                                 | -0.3 to +2.5                    |      |

| PLL power supply voltage (1.8 V)          | $V_{DD\_PLL}$        |                                                 | -0.5 to 12.5                    |      |

| Digital power supply voltage I/O (3.3 V)  | $V_{DD\_IO}$         |                                                 | -0.3 to +4.6                    |      |

| USB power supply voltage I/O (3.3 V)      | $V_{DD\_USB}$        | _                                               | -0.3 to +4.0                    |      |

| Input voltage (normal buffer)             |                      | _                                               | -0.3 to V <sub>DD_IO</sub> +0.3 | V    |

| Input voltage (5 \/ telerant)             | $V_{l}$              | $V_{DD_{IO}} = 3.0 \text{ V to } 3.6 \text{ V}$ | -0.3 to +6.0                    |      |

| Input voltage (5 V tolerant)              |                      | $V_{DD\_IO} < 3.0 \ V$                          | -0.3 to V <sub>DD_IO</sub> +0.3 |      |

| Output voltage                            | Vo                   | _                                               | -0.3 to V <sub>DD_IO</sub> +0.3 |      |

| Input allowable current                   | l <sub>l</sub>       | _                                               | −10 to +10                      |      |

| "H" output allowable current              | I <sub>OH</sub>      | _                                               | +10                             | mA   |

| "L" output allowable current              | I <sub>OL</sub>      | _                                               | -10                             | ША   |

| Power dissipation                         | P <sub>D</sub>       | T <sub>a</sub> = 85°C                           | 455                             | mW   |

| Storage temperature                       | T <sub>STG</sub>     | _                                               | −50 to 150                      | °C   |

## **GUARANTEED OPERATING RANGES**

(GND = 0 V)

| Parameter                          |                | Symbol                | Condition | Min. | Тур. | Max.   | Unit  |

|------------------------------------|----------------|-----------------------|-----------|------|------|--------|-------|

| Digital power supply volta         | ge (CORE) (*1) | V <sub>DD_CORE</sub>  |           | 1.62 | 1.8  | 1.98   |       |

| PLL power supply voltage           | (*1)           | $V_{DD\_PLL}$         |           | 1.62 | 1.8  | 1.98   | \/    |

| Digital power supply voltage (I/O) |                | $V_{DD\_IO}$          | _         | 3.0  | 3.3  | 3.6    | V     |

| USB power supply voltage           |                | $V_{DD\_USB}$         |           | 3.0  | 3.3  | 3.6    |       |

| CPU operating frequency            |                | f <sub>BUSCLK</sub>   | _         | -    | 32   | -      | MHz   |

| Ambient temperature                |                | Ta                    |           | -40  | 25   | 85     |       |

| _ Flash read                       |                | T <sub>a_fread</sub>  |           | -40  | 25   | 85     | °C    |

|                                    | Flash write    | T <sub>a_fwrite</sub> |           | -40  | 25   | 85     |       |

| Flash write count                  |                | Cwr                   |           | _    | _    | 10,000 | cycle |

<sup>\* 1:</sup> Please supply from same power source to both  $V_{DD\_CORE}$  pins and  $V_{DD\_PLL}$  pin.

#### **ELECTRICAL CHARACTERISTICS**

## **DC** Characteristics

DC characteristics (Core/IO)

$(V_{DD CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$ Symbol Parameter Condition Min. Max. Unit Тур. "H" input voltage  $V_{DD\_IO} + 0.3$  $V_{IH}$ 2.0 "L" input voltage  $V_{IL}$ -0.38.0 Schmitt trigger 2.0  $V_{T+}$ input threshold voltage  $V_{T-}$ 0.6 (3.3 V)٧ Schmitt trigger  $V_{T+}$ 2.0 input threshold voltage  $V_{T-}$ 0.6 (5 V tolerant) "H" output voltage  $V_{OH}$  $I_{OH} = -4 \text{ mA}$ 2.4 "L" output voltage  $I_{OL} = 4 \text{ mA}$ 0.4  $V_{OL}$  $\overline{V}_{IH} = V_{DD\_IO}$ 10 High level input current (\*1) pull-down 30 140  $I_{\text{IH}}$  $V_{IH} = V_{DD IO}$ 10 — High level input current (\*2)  $V_{IH} = 5.5 V$ 30 μΑ  $V_{IL} = 0 V$ -10Low level input current (\*1) pull-up -140-30lπ Low level input current (\*2)  $V_{IL} = 0 V$ -10 $V_{OH} = V_{DD IO}$ 10  $I_{OZH}$ pull-down 30 140 3-state output leakage current μΑ  $V_{OL} = 0 V$ -10  $I_{OZL}$ -140 -30 pull-up 1500 I<sub>DDS\_CORE</sub> 80 Supply current (during STOP) (\*4) (\*3) 4 20 μΑ  $I_{DDS\_IO}$ 2 10

Supply current (during operation)

(\*5)

No load excluding the current flowing in pull-up/pull-down resistors Other ports:

I<sub>DDS\_PLL</sub>

I<sub>DDO\_CORE</sub>

$I_{DDO\ IO}$

I<sub>DDO\_PLL</sub>

$f_{BUSCLK}$  = 32.0 MHz

(\*3) (\*6)

50

5

70

10

3

mΑ

<sup>\*1:</sup> Pins other than 5 V tolerant pins

<sup>\*2: 5</sup> V tolerant pins

<sup>\*3:</sup> Input ports: VDD IO or 0 V

<sup>\*4:</sup> LSI supply current when going into LSI stop mode by stopping clock oscillation, PLL operation, and random number generator operation and setting USB power-down mode.

<sup>\*5:</sup> The current supplied to the LSI when fingerprint authentication is executed without USB operation under the conditions that the programs are stored in the built-in Flash ROM and no external memory are connected.

<sup>\*6:</sup> Clock pulse is driven to XI clock input pin.

DC characteristics (USB)

$(V_{DD\_CORE} = 1.62 \text{ to } 1.98V, V_{DD\_USB} = 3.0 \text{ to } 3.6V, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter                               | Symbol          | Condition                                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|-----------------|-------------------------------------------------------------|------|------|------|------|

| Differential input sensitivity          | V <sub>DI</sub> | Absolute value of the difference between the DP and DM pins | 0.2  | _    | _    | V    |

| Differential common mode range          | $V_{CM}$        | Includes VDI range                                          | 0.8  | _    | 2.5  | V    |

| Single end input threshold voltage      | $V_{SE}$        |                                                             | 8.0  | _    | 2.0  | V    |

| High level output voltage               | V <sub>OH</sub> | 15K W RL is connected to GND                                | 2.8  | _    | _    | V    |

| Low level output voltage                | $V_{OL}$        | 1.5K W RL to 3.6 V                                          | 1    | _    | 0.3  | V    |

| Hi-Z state input/output leakage current | I <sub>LO</sub> | 0 V < VIN < 3.3 V                                           | -10  | _    | 10   | μА   |

| Driver output resistance                | $Z_{DRV}$       | Steady state                                                | 28   | _    | 44   | Ω    |

# **AC Characteristics**

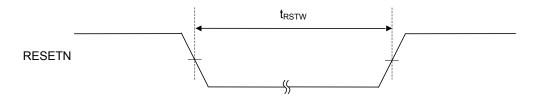

# Reset Timing

|                   |        | (V <sub>DD_CORE</sub> = | = 1.62 to 1.98 | $V, V_{DD_{10}} = 3.0$ | to 3.6 V, $T_a =$ | –40 to +85°C) |

|-------------------|--------|-------------------------|----------------|------------------------|-------------------|---------------|

| Parameter         | Symbol | Condition               | Min.           | Тур.                   | Max.              | Unit          |

| Reset pulse width | trstw  | _                       | 6.0            | _                      | _                 | ms            |

<sup>\*</sup>When power on, release the reset after the clock oscillation stabilization.

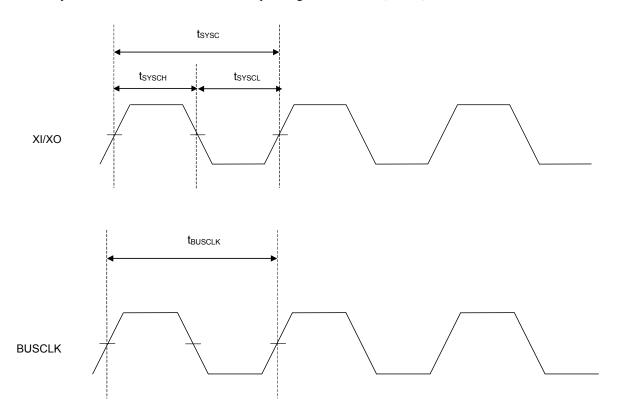

Main Clock Timing

| (V <sub>DD</sub> | CORE = | 1.62 to | 1.98 V. | V <sub>DD</sub> 10 | = 3.0 tc | 3.6 V.    | T <sub>2</sub> = | = -40 to | +85°C) |

|------------------|--------|---------|---------|--------------------|----------|-----------|------------------|----------|--------|

| ( • טט           | CORE   | 1.02 10 | 1.00 v, | טו טט יי           | 0.0 10   | , o.o v , | 'a               | 10 10    | 100 0, |

| Parameter                        | Symbol              | Condition | Min.                   | Typ.  | Max.                        | Unit |

|----------------------------------|---------------------|-----------|------------------------|-------|-----------------------------|------|

| Main clock (XI/XO) frequency     | f <sub>SYSC</sub>   | _         | 12 × 0.9975            | 12    | 12 × 1.0025                 | MHz  |

| Main clock (XI/XO) cycle         | tsysc               | _         | 83.33 ×<br>0.9975      | 83.33 | 83.33 ×<br>1.0025           | ns   |

| Main clock (XI/XO) H pulse width | t <sub>sysch</sub>  | _         | $0.45 \times t_{SYSC}$ | _     | 0.55 ×<br>t <sub>SYSC</sub> | ns   |

| Main clock (XI/XO) L pulse width | t <sub>SYSCL</sub>  | _         | $0.45 \times t_{SYSC}$ | _     | 0.55 ×<br>t <sub>SYSC</sub> | ns   |

| Bus clock frequency (*1)         | f <sub>BUSCLK</sub> | _         | _                      | 32    | _                           | MHz  |

| Bus clock cycle (*1)             | t <sub>BUSCLK</sub> | _         | _                      | 31.25 | _                           | ns   |

<sup>\* 1:</sup> Main system bus clock within the LSI and operating clocks of CPU, DMA, etc.

USB Access Timing (Full-Speed)

$(V_{DD\_CORE}$  = 1.62 to 1.98 V,  $V_{DD\_USB}$  = 3.0 to 3.6 V,  $T_a$  = -40 to +85°C)

|                                 |                    | ( DD_0011L                       |       | , ,,, | 000   | ,    | <u>u</u>    |

|---------------------------------|--------------------|----------------------------------|-------|-------|-------|------|-------------|

| Parameter                       | Symbol             | Condition                        | Min.  | Тур.  | Max.  | Unit | Applied pin |

| Rise time (*1)                  | T <sub>R</sub>     | CL = 50 pF                       | 4     | _     | 20    | ns   |             |

| Fall time (*1)                  | $T_F$              | CL = 50 pF                       | 4     | _     | 20    | ns   |             |

| Output signal crossover voltage | V <sub>CRS</sub>   | CL = 50 pF                       | 0.8   | _     | 2.5   | V    | DP, DM      |

| Data rate                       | T <sub>DRATE</sub> | Average bit rate (12Mbps ±0.25%) | 11.97 | _     | 12.03 | Mbps |             |

<sup>\*1</sup> TR and TF are transition time from 10% to 90% of  $V_{DD\_USB}$ .

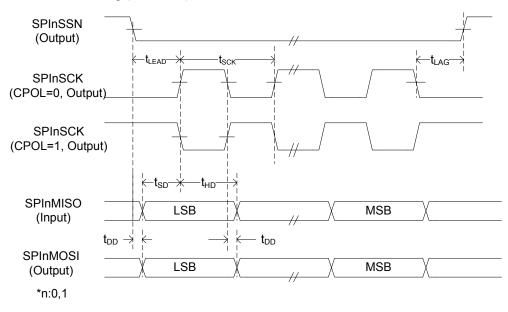

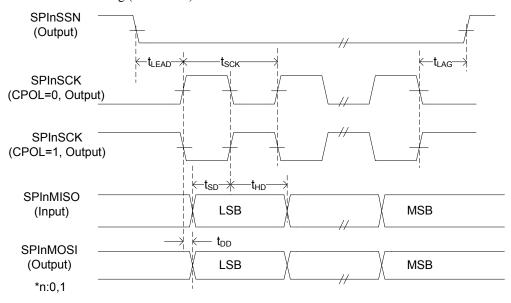

**SPI Access Timing**

- Characteristics of master mode timing

$(V_{DD\_CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD\_IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                 | Symbol            | Condition  | Min.                     | Тур. | Max.                     | Unit               |

|---------------------------|-------------------|------------|--------------------------|------|--------------------------|--------------------|

| Data delay time (output)  | t <sub>DD</sub>   |            | _                        | _    | 25                       | ns                 |

| Data setup time (input)   | t <sub>SD</sub>   |            | 25                       | _    | _                        | ns                 |

| Data hold time (input)    | t <sub>HD</sub>   | CL = 30 pF | 0 (*1)                   | _    | _                        | ns                 |

| SPInSSN-SPInSCK lead time | t <sub>LEAD</sub> |            | 0.5*t <sub>SCK</sub> -15 | _    | 0.5*t <sub>SCK</sub> +15 | ns <sup>(*2)</sup> |

| SPInSCK-SPInSSN lag time  | t <sub>LAG</sub>  |            | 0.5*t <sub>SCK</sub> -15 | _    | 0.5*t <sub>SCK</sub> +15 | ns <sup>(*2)</sup> |

<sup>\* 1:</sup> Although actual values may become negative depending on the external load, input the serial data so that the data hold time can be guaranteed.

SPI master mode timing (CPHA = 0)

SPI master mode timing (CPHA = 1)

<sup>\* 2:</sup> tSCK is the cycle time of the serial clock for SPI transferring which is obtained by dividing the frequency of the bus clock, whose cycle time is tBUSCLK.

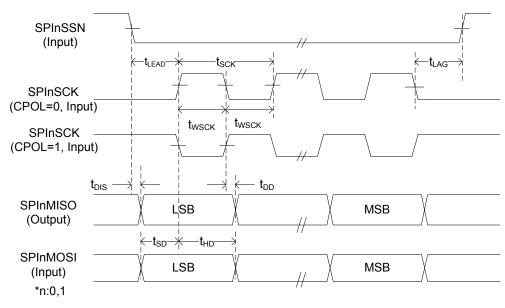

- Characteristics of slave mode timing

$(V_{DD\_CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD\_IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                  | Symbol            | Condition  | Min.                     | Тур. | Max. | Unit                |

|----------------------------|-------------------|------------|--------------------------|------|------|---------------------|

| Serial clock cycle time    | t <sub>SCK</sub>  |            | 2                        | _    | _    | t <sub>BUSCLK</sub> |

| Serial clock High/Low time | twsck             |            | 1                        | _    | _    | t <sub>BUSCLK</sub> |

| Data delay time (output)   | t <sub>DD</sub>   |            | _                        | _    | 25   | ns                  |

| Data setup time (input)    | t <sub>SD</sub>   | CL = 30 pF | 25                       | _    | _    | ns                  |

| Data hold time (input)     | t <sub>HD</sub>   |            | 25                       | _    | _    | ns                  |

| SPInSSN-SPInSCK lead time  | t <sub>LEAD</sub> |            | 25                       | _    | _    | ns                  |

| SPInSCK-SPInSSN lag time   | t <sub>LAG</sub>  |            | t <sub>BUSCLK</sub> + 15 | _    | _    | ns                  |

| Slave data invalid time    | t <sub>DIS</sub>  |            | _                        | _    | 25   | ns                  |

SPI slave mode timing (CPHA = 0)

SPI slave mode timing (CPHA = 1)

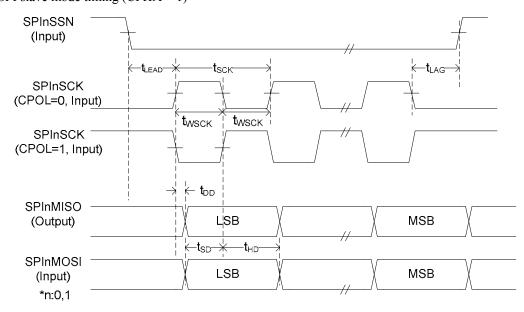

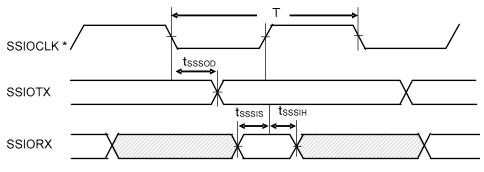

## Synchronous SIO Access Timing

Switching between master mode and slave mode can be set for this synchronous SIO by the software register setting. Serial clock polarity can be switched.

When clock polarity is set to positive, data is transmitted (shifted out) on the falling edge of the clock and is received (shifted in) on the rising edge of the clock. At completion of 8-bit data transmission/reception, the clock stops at a high level and the last data is retained for data output.

When clock polarity is set to negative, data is transmitted (shifted out) on the rising edge of the clock and is received (shifted in) on the falling edge of the clock. At completion of 8-bit data transmission/reception, the clock stops at a low level and the last data is retained for data output.

The following waveforms show the cases where the clock polarity is positive.

#### - Master mode

$(V_{DD\_CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD\_IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$ Symbol Condition Min. Typ. Max. Unit

| Parameter                | Symbol             | Condition  | Min. | Тур. | Max. | Unit |

|--------------------------|--------------------|------------|------|------|------|------|

| Output data delay time   | t <sub>MSSOD</sub> |            |      | _    | 20   |      |

| Input data setting time  | t <sub>MSSIS</sub> | CL = 30 pF | 30   | _    | _    | ns   |

| Input data retained time | t <sub>MSSIH</sub> |            | 10   | _    | _    |      |

#### Note:

11 clock outputs for transferring is selectable from 2 synchronous SIO clock sources and the frequency divide ratios.

\* Serial clock: Positive polarity

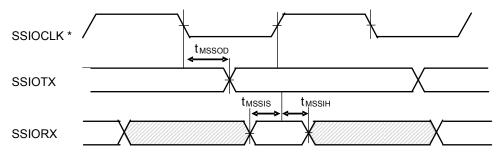

# - Slave mode

$(V_{DD CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                | Symbol             | Condition  | Min. | Тур. | Max. | Unit |  |

|--------------------------|--------------------|------------|------|------|------|------|--|

| Serial clock cycle       | Т                  |            | 62.5 | _    | _    |      |  |

| Output data delay time   | tsssod             | CL = 30 pF | _    | _    | 40   |      |  |

| Input data setting time  | t <sub>SSSIS</sub> | CL = 30 pr | 20   | _    | _    | ns   |  |

| Input data retained time | t <sub>SSSIH</sub> |            | 20   | _    | _    |      |  |

Serial clock: Positive polarity

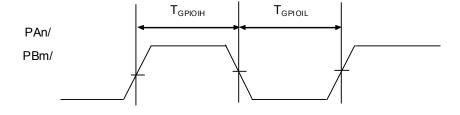

GPIO (PA, PB) Access Timing

$(V_{DD\_CORE}$  = 1.62 to 1.98 V,  $V_{DD\_IO}$  = 3.0 to 3.6 V,  $T_a$  = -40 to +85°C)

| Parameter                 | Symbol              | Condition | Min.                   | Тур. | Max. | Unit |

|---------------------------|---------------------|-----------|------------------------|------|------|------|

| PAn, PBm input H duration | T <sub>GPIOIH</sub> | _         | t <sub>BUSCLK</sub> ×2 | _    | _    | ns   |

| PAn, PBm input L duration | T <sub>GPIOIL</sub> | _         | t <sub>BUSCLK</sub> ×2 | _    | _    | ns   |

Note 1: n = 12 to 0, m=11 to 0

$\bigcirc$  PAn, PBm input timing (n = 12 to 0, m = 11 to 0)

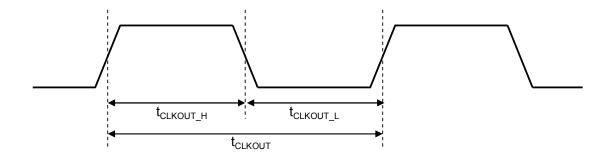

Clock Output (Secondary Function of PB11 Pin) Timing

$(V_{DD\_CORE} = 1.62 \text{ to } 1.98 \text{ V}, V_{DD\_IO} = 3.0 \text{ to } 3.6 \text{ V}, T_a = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                  | Symbol    | Condition | Min.                | Тур.                | Max.                | Unit               |

|----------------------------|-----------|-----------|---------------------|---------------------|---------------------|--------------------|

| Clock output High duration | tourour   |           | 45% ×               | 50% ×               | 55% ×               | ns <sup>(*1)</sup> |

| Clock output High duration | CLKOUT_H  | _         | tclkout             | t <sub>CLKOUT</sub> | tclkout             |                    |

| Clock output Low duration  |           |           | 45% ×               | 50% ×               | 55% ×               | no(*1)             |

| Clock output Low duration  | ICLKOUT_L | _         | t <sub>CLKOUT</sub> | t <sub>CLKOUT</sub> | t <sub>CLKOUT</sub> | ns <sup>( 1)</sup> |

<sup>\*</sup>t<sub>CLKOUT</sub> is the cycle time of the 6 MHz or 12 MHz clock generated by 2 clock sources and the frequency divide ratio.

Clock output (secondary function of PB11 pin) timing

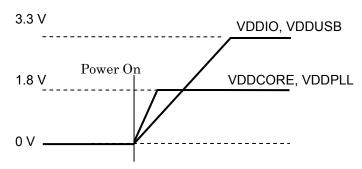

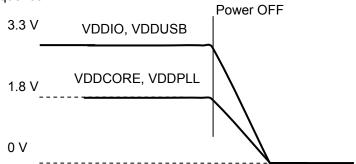

# POWER ON / OFF SEQUENCE

## **Power ON sequence**

- Core(VDDCORE, VDDPLL) and IO(VDDIO, VDDUSB) power should be on at the same time, or IO(VDDIO, VDDUSB) power should be on after Core(VDDCORE, VDDPLL) on.

# Power ON Sequence

## **Power OFF sequence**

- Core(VDDCORE, VDDPLL) and IO(VDDIO, VDDUSB power should be off at the same time, or Core(VDDCORE, VDDPLL) power should be off after IO(VDDIO, VDDUSB) off.

## PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# REVISION HISTORY

|                |              | Page     |         |                                                   |

|----------------|--------------|----------|---------|---------------------------------------------------|

| Document No.   | Date         | Previous | Current | Description                                       |

|                |              | Edition  | Edition |                                                   |

| PEDL67Q5260-01 | Aug.18, 2009 | _        | ı       | Preliminary edition 1                             |

| PEDL67Q5260-02 | Jul.15, 2010 | _        | ı       | Preliminary edition 2                             |

| FEDL67Q5260-01 | Sep.15, 2010 | 22       | 22      | Final edition 1                                   |

|                |              |          |         | - Corrected Power dissipation to 450mW            |

|                |              |          |         | - Changed IIL of Pull-Up pin to -14030uA          |

|                |              |          |         | - Changed IIH of Pull-Down pin to 30 - 140uA      |

| FEDL67Q5260-02 | Jul.1, 2011  | 1        | 1       | Applicable fingerprint sensor AES1711 is deleted. |

#### NOTICE

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2009 - 2011 LAPIS Semiconductor Co., Ltd.