Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# S12XS MCU and multifunctional ignition and injector driver system in package (SiP)

The MM912\_S812 is an engine control SMARTMOS IC combining an MCU (S12XS) and analog control die (MC33812) intended for motorcycle and other single cylinder small engine control applications. The MCU S12XS has 8.0 KB or 12 KB RAM, and flash memory size of 128 KB or 256 KB. The S12XS family retains many of the features of the S12XE family including error correction code (ECC) on flash memory, a separate data-flash module for code or data storage, a frequency modulated locked loop (IPLL) that improves the EMC performance and a fast ATD converter.

#### Features:

- Designed to operate over the range of ~4.7 V ≤ V<sub>PWR</sub> ≤ 36 V

- · Relay/injector/fuel pump driver current limit 4.0 A, typical

- · Lamp driver current limit 1.5 A, typical

- · All external outputs protected against short to battery and overcurrent

- VCC voltage pre-regulator provides +5.0 V power for the MCU

- MCU watchdog timer circuit with parallel refresh/time setting line

- ISO-9141 K-Line transceiver for communicating diagnostic messages

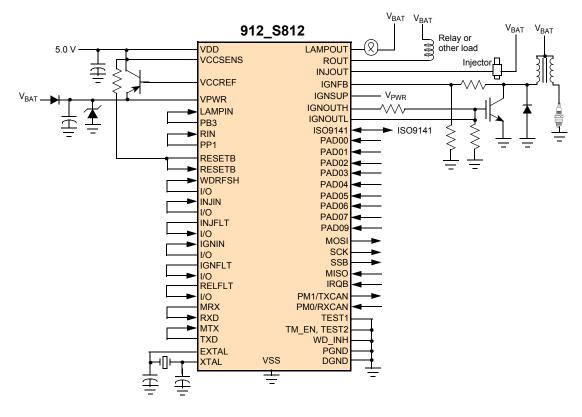

912\_S812

**SMALL ENGINE CONTROL SIP**

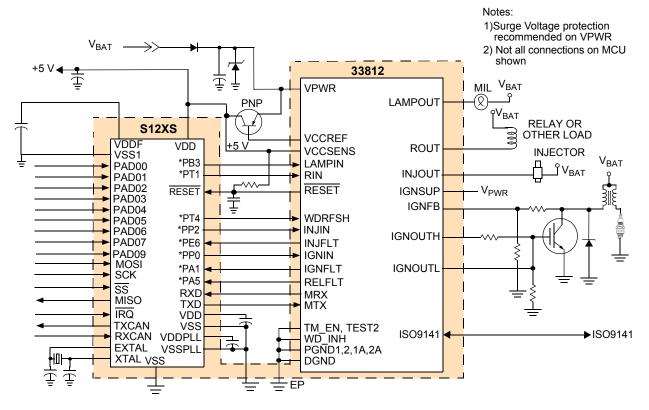

#### Notes

- 1. Surge Voltage protection recommended on VPWR

- 2. Not all connections on MCU shown

Figure 1. 912\_S812 simplified application diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© 2016 NXP B.V.

## 1 Orderable parts

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a> and perform a part number search for the following device numbers.

Table 1. Orderable part variations

| Part number <sup>(3)</sup> | MCU   | Temperature (T <sub>A</sub> ) | Flash memory | RAM   | Package            |  |

|----------------------------|-------|-------------------------------|--------------|-------|--------------------|--|

| MM912JS812AMAF             | S12XS | -40 to 125 °C                 | 128 k        | 8.0 k | 100 pin LQFP-EP    |  |

| MM912KS812AMAF             | 012/0 | -40 10 125 0                  | 256 k        | 12 k  | 100 piii EQi 1 -Ei |  |

#### Notes

3. To Order parts in Tape & Reel, add the R2 suffix to the part number.

Table 2. Calibration tools

| Part number             |                  | Package         |                                             |

|-------------------------|------------------|-----------------|---------------------------------------------|

| MC9S12XEP100 (MCU Only) | S12XEP           | Multiple        | Contact sales for availability and quantity |

| PV912NE812AMAF          | S12XEP + MC33812 | 100 pin LQFP-EP | Contact sales for availability and quantity |

<sup>\*</sup> I/O pins indicated are examples only and not necessarily recommendations

Figure 2. 912\_S812 detailed application diagram

## 2 Part identification

This section provides an explanation of the part numbers and their alpha numeric breakdown.

## 2.1 Description

Part numbers for the chips have fields that identify the specific part configuration. You can use the values of these fields to determine the specific part you have received.

## 2.2 Format and examples

Part numbers for a given device have the following format, followed by a device example:

<u>Table 3</u> - Part numbering - analog EMBEDDED MCU + POWER:

MM 9 cc f xxx r v PPP RR - MM912JS812AMAF

### 2.3 Fields

These tables list the possible values for each field in the part number (not all combinations are valid).

Table 3. Part numbering - analog EMBEDDED MCU + POWER

| FIELD | DESCRIPTION             | VALUES                                                              |

|-------|-------------------------|---------------------------------------------------------------------|

| MM    | Product Category        | MM- Qualified Device     SM- Custom Device     PM- Prototype Device |

| 9     | Memory Type             | • 9 = Flash, OTP                                                    |

| СС    | Micro Core              | • 12 = HC12                                                         |

| f     | Memory Size             | • J 128 k<br>• K 256 k                                              |

| xxx   | Analog Core/Target      | • 812 - MC33812                                                     |

| r     | Revision                | • (default A)                                                       |

| t     | Temperature Range       | • M = -40 °C to 125 °C                                              |

| V     | Variation               | (default blank)                                                     |

| PPP   | Package Designator      | AF - 100 lead LQFP with exposed pad                                 |

| RR    | Tape and Reel Indicator | •R2                                                                 |

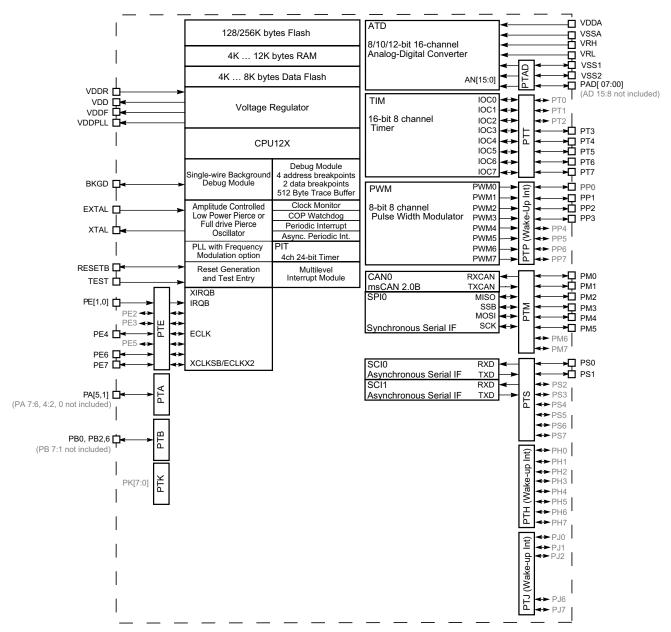

## 3 Internal block diagram

Figure 3. MC9S12XS family block diagram

Notes

4. Pull-up and pull-down current sources are  $\sim$ 50  $\mu$ A, unless otherwise noted

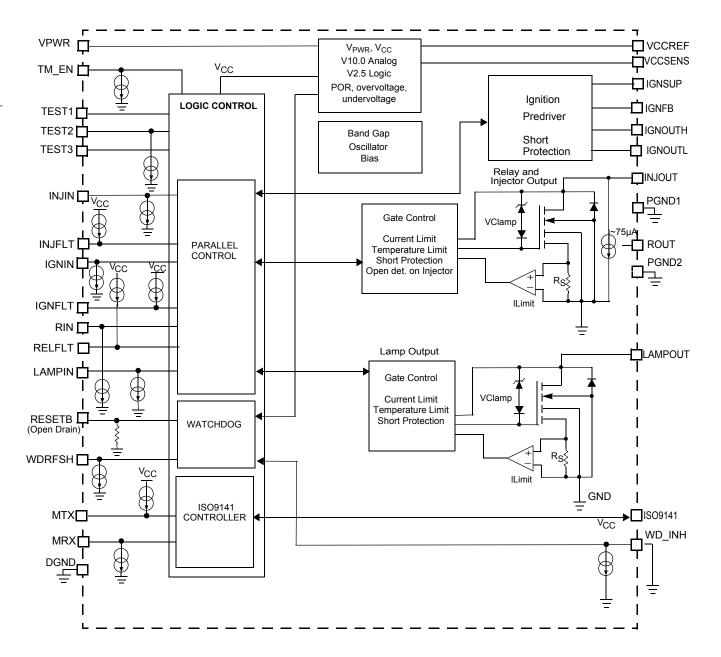

Figure 4. 33812 simplified internal block diagram

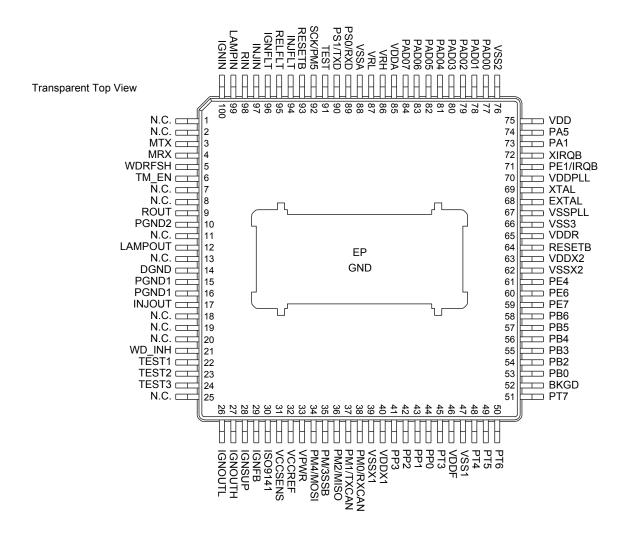

## 4 Pin connections

## 4.1 Pinout diagram

#### Notes

- 5. EP, PGND1, PGND2, and DGND, must all be connected to the ground plane.

- 6. Compared to the MC33812 in the 32 pin SOICW package, there are no pins missing.

- 7. Compared to the S12XS in the 80 pin QFP package, 22 pins are missing in the SiP. These pins are: PB1, PB7, PE5, PJ2, PE2, PE3, PA0, PA2, PA3, PA4, PA6, PA7, PAD08, PAD09, PS2, PS3, PJ7, PJ6, PP7, PP6, PP5, and PP4.

Figure 5. 33812\_S812 pin connections

6

## 4.2 Pin definitions

Table 4. 912\_S812 pin definitions

| Analog<br>or MCU | Pin | Pin name | Pin<br>function | Formal name                  | Description and recommendations                                                                                                                     |

|------------------|-----|----------|-----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| -                | 1   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| -                | 2   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 3   | MTX      | Input           | ISO9141 Data Input to<br>MCU | Input logic level ISO9141 data, from the MCU, to the ISO9141 IN/OUT pin Connect to MCU SCI TXD output (pin 90) if using ISO9141 circuit             |

| Analog           | 4   | MRX      | Output          | ISO9141 Data Output to MCU   | Output logic level ISO9141 data to the MCU from the ISO9141 IN/OUT pin Connect to MCU SCI RXD input (pin 89) if using ISO9141 circuit               |

| Analog           | 5   | WDRFSH   | Input           | Watchdog Refresh             | Logic Level input from MCU to refresh the watchdog circuit to prevent RESETB Connect to MCU I/O output (e.g. PT4 pin 48)                            |

| Analog           | 6   | TM_EN    | Input           | Test Mode Enable             | Used by NXP test engineering, Connect to Ground                                                                                                     |

| -                | 7   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| -                | 8   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 9   | ROUT     | Output          | Relay Driver Output          | Low side relay driver output driven by parallel input RIN Use ESD capacitor where the signal goes off the PC Board.                                 |

| Analog           | 10  | PGND2    | Ground          | Power Ground 2               | Ground for the RELAY driver output Connect to Ground                                                                                                |

| -                | 11  | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 12  | LAMPOUT  | Output          | Warning Lamp Output          | Low side driver output for MIL (warning lamp) driven by parallel input LAMPIN. Use an ESD capacitor where the signal goes off the PC Board          |

| -                | 13  | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 14  | DGND     | Ground          | Supply Ground                | Used as ground for all low power signals. Connect to Ground                                                                                         |

| -                | 7   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 16  | PGND1    | Ground          | Power Ground 1               | Ground for INJOUT injector driver output. Connect to Ground                                                                                         |

| Analog           | 17  | INJOUT   | Output          | Injector Driver Output       | Low side driver output for the Injector driven by parallel input INJIN. Use an ESD capacitor where the signal goes off the PC Board.                |

| -                | 7   | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| -                | 19  | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| -                | 20  | N.C.     | Unused          |                              | Unused pin, leave open                                                                                                                              |

| Analog           | 21  | WD_INH   | Input           | Watchdog Inhibit             | Normally tied to GND, If tied high through a pull-up, it inhibits RESETB from occurring when a watchdog timeout occurs. Normally connect to Ground. |

| Analog           | 22  | TEST1    | Input           | Test 1                       | MUST be tied to GND. Connect to Ground                                                                                                              |

| Analog           | 23  | TEST2    | Input           | Test 2                       | MUST be tied to GND. Connect to Ground                                                                                                              |

| Analog           | 24  | TEST3    | Input           | Test 3                       | MUST leave OPEN. Leave open                                                                                                                         |

| -                | 25  | N.C.     | Unused          |                              | Unused pin. Leave open                                                                                                                              |

| Analog           | 26  | IGNOUTL  | Output          | Ignition Output Low          | Low side output to drive the Gate/Base of the IGBT/Bipolar Darlington The network used on this pin is determined by the user requirements.          |

| Analog           | 27  | IGNOUTH  | Output          | Ignition Output High         | High side output to drive the Gate/Base of IGBT/Bipolar Darlington The network used on this pin is determined by the user requirements.             |

| Analog           | 28  | IGNSUP   | Input           | Ignition Output Supply       | Tie to +5.0 V for Darlington, tie to the V <sub>PWR</sub> supply for the IGBT output device                                                         |

| Analog           | 29  | IGNFB    | Input           | Feedback from Source         | Voltage feedback from the source of the Ignition driver transistor through a 10:1 voltage divider. Use a 10:1 voltage divider (36 k/4.02 k)         |

Table 4. 912\_S812 pin definitions

| Analog or MCU | Pin | Pin name                  | Pin<br>function  | Formal name                                           | Description and recommendations                                                                                                                                                                                                                                                                           |

|---------------|-----|---------------------------|------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog        | 30  | ISO9141                   | Input/<br>Output | ISO9141 K-Line<br>Bidirectional Serial Data<br>Signal | The ISO9141 pin is a $V_{PWR}$ level IN/OUT signal connected to a external ECU Tester, using ISO9141 Protocol.The Output is Open drain and the Input is a ratiometric $V_{PWR}$ level threshold comparator. Use an ESD capacitor where the signal goes off the PC Board.                                  |

| Analog        | 31  | VCCSENS                   | Input            | Voltage Sense from VCC                                | Feedback to the internal VCC regulator from a external pass transistor. Must have the minimum of a 2.2 $\mu\text{F}$ capacitor                                                                                                                                                                            |

| Analog        | 32  | VCCREF                    | Output           | VCC Reference Base drive                              | Base drive voltage for an external PNP pass transistor                                                                                                                                                                                                                                                    |

| Analog        | 33  | VPWR                      | Supply<br>Input  | Main Voltage Supply<br>Input                          | VPWR is the main voltage supply input for the device. It is connected to a +12 volt battery (It should have reverse battery protection and transient suppression.) It also needs a bypass capacitor to ground (100 nF or 0.1 $\mu\text{F})$                                                               |

| MCU           | 34  | PM4/MOSI                  | I/O              | PM4/<br>SPI MOSI                                      | Port M, I/O pin 4 is a general purpose input or output pin. It can be configured as the master output (during master mode) or slave input pin (during slave mode). MOSI for the serial peripheral interface (SPI).                                                                                        |

| мси           | 35  | PM3/SSB                   | I/O              | PM3/<br>SPI SSB                                       | Port M, I/O pin 3 is a general purpose input or output pin. It can be configured as the slave select output pin SSB of the serial peripheral interface (SPI) (during master mode) and chip select input (CSB) (during slave mode).                                                                        |

| мси           | 36  | PM2/MISO                  | I/O              | PM2/<br>SPI MISO                                      | Port M, I/O pin 2 is a general purpose input or output pin. It can be configured as the master input (during master mode) or slave output pin (during slave mode). MISO for the serial peripheral interface (SPI).                                                                                        |

| мси           | 37  | PM1/TXCAN                 | I/O              | PM1/<br>TXCAN                                         | Port M, I/O pin 1 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the scalable controller area network controller (CAN).                                                                                                                                      |

| мси           | 38  | PM0/RXCAN                 | I/O              | PM0/<br>RXCAN                                         | Port M, I/O pin 0 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the scalable controller area network controller (CAN).                                                                                                                                       |

| мси           | 39  | VSSX1                     | Ground           | VSSX1                                                 | External ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VSSX pins are connected together internally. Connect to Ground                                                                                                                                    |

| мси           | 40  | VDDX1                     | Supply<br>Input  | VDDX1                                                 | External power for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VDDX pins are connected together internally. Connect to VCC and use a 100 nF bypass capacitor to ground.                                                                                           |

| мси           | 41  | PP3                       | I/O              | PP3/KWP3/PWM3                                         | Port P, I/O pin 3 is a general purpose input or output pin. It can be configured as a keypad wake-up input. It can be configured as a pulse width modulator (PWM) output channel 3.                                                                                                                       |

| мси           | 42  | PP2<br>PT0 <sup>(8)</sup> | I/O              | PP2/KWP2/PWM2<br>PT0 <sup>(8)</sup>                   | Port P, I/O pin 3 is a general purpose input or output pin. It can be configured as a keypad wake-up input. It can be configured as a pulse width modulator (PWM) output channel $2.^{(8)}$                                                                                                               |

| MCU           | 43  | PP1<br>PT1 <sup>(8)</sup> | I/O              | PP1/KWP1/PWM1<br>PT1 <sup>(8)</sup>                   | Port P, I/O pin 3 is a general purpose input or output pin. It can be configured as a keypad wake-up input. It can be configured as a pulse width modulator (PWM) output channel $1.^{(8)}$                                                                                                               |

| мси           | 44  | PP0<br>PT2 <sup>(8)</sup> | I/O              | PP0/KWP0/PWM0<br>PT2 <sup>(8)</sup>                   | Port P, I/O pin 3 is a general purpose input or output pin. It can be configured as a keypad wake-up input. It can be configured as a pulse width modulator (PWM) output channel $0.^{(8)}$                                                                                                               |

| MCU           | 45  | PT3                       | I/O              | PT3/IOC3                                              | Port T, I/O pin 3 is a general purpose input or output pin. It can be configured as a timer (TIM) channel 3.                                                                                                                                                                                              |

| MCU           | 46  | VDDF                      | Supply           | VDDF 3.3 V supply output                              | Signals VDDF/VSS are the secondary outputs of VREG_3V3 that provide the power supply for the NVM logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic). In Shutdown mode an external supply driving VDDF/VSS can replace the voltage regulator. |

| MCU           | 47  | VSS1                      | Ground           | VSS1                                                  | See previous description for VDDF/VSS.                                                                                                                                                                                                                                                                    |

#### Notes

8. S12XEP signals noted for reuse of PC board for the calibration device.

Table 4. 912\_S812 pin definitions

| Analog or MCU | Pin | Pin name | Pin<br>function | Formal name                  | Description and recommendations                                                                                                                                                                                                                                                                                                              |  |

|---------------|-----|----------|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MCU           | 48  | PT4      | I/O             | PT4/IOC4/PWM4                | Port T, I/O pin 4 is a general purpose input or output pin. It can be configured as a timer (TIM) channel 4 or pulse width modulator (PWM) output 4.                                                                                                                                                                                         |  |

| MCU           | 49  | PT5      | I/O             | PT5/IOC5/PWM5/<br>API_EXTCLK | Port T, I/O pin 5 is a general purpose input or output pin. It can be configured as a timer (TIM) channel 5, pulse width modulator (PWM) output 5, or as the output of the API_EXTCLK.                                                                                                                                                       |  |

| MCU           | 50  | PT6      | I/O             | PT6/IOC6                     | Port T, I/O pin 6 is a general purpose input or output pin. It can be configur as a timer (TIM) channel 6.                                                                                                                                                                                                                                   |  |

| MCU           | 51  | PT7      | I/O             | PT7/IOC7                     | Port T, I/O pin 7 is a general purpose input or output pin. It can be configured as a timer (TIM) channel 7.                                                                                                                                                                                                                                 |  |

| MCU           | 52  | BKGD     | BDM             | BKGD/MODC                    | The BKGD/MODC pin is used as a pseudo open-drain pin for the background debug communication. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of RESETB. The BKGD pin has an internal pull-up device.                                                         |  |

| MCU           | 53  | PB0      | I/O             | PB0                          | Port B, I/O pin 0 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 54  | PB2      | I/O             | PB2                          | Port B, I/O pin 2 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 55  | PB3      | I/O             | PB3                          | Port B, I/O pin 3 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 56  | PB4      | I/O             | PB4                          | Port B, I/O pin 4 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 57  | PB5      | I/O             | PB5                          | Port B, I/O pin 5 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 58  | PB6      | I/O             | PB6                          | Port B, I/O pin 6 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 59  | PE7      | I/O             | PE7/ECLKX2                   | Port E, I/O pin 7 is a general purpose input or output pin. An internal pull-up is enabled during reset. It can be configured to output ECLKX2.                                                                                                                                                                                              |  |

| MCU           | 60  | PE6      | I/O             | PE6                          | Port E, I/O pin 6 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                  |  |

| MCU           | 61  | PE4      | I/O             | PE4/ECLK                     | Port E, I/O pin 4 is a general purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference. The ECLK output has a programmable prescaler.                                                                                                                                 |  |

| MCU           | 62  | VSSX2    | Ground          | VSSX2                        | External ground for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VSSX pins are connected together internally.Connect to Ground                                                                                                                                                                        |  |

| MCU           | 63  | VDDX2    | Supply<br>Input | VDDX2                        | External power for I/O drivers. Bypass requirements depend on how heavily the MCU pins are loaded. All VDDX pins are connected together internally. Connect to VCC and use a 100 nF bypass capacitor to Ground                                                                                                                               |  |

| MCU           | 64  | RESETB   | Input           | RESETB<br>External Reset Pin | The RESETB pin is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset. The RESETB pin has an internal pull-up device. Use external pull-up (10 k and 0.1 μF capacitor to Ground) connect to the 33812 RESETB pin 93. |  |

| MCU           | 65  | VDDR     | Supply<br>Input | VDDR                         | Power supply input to the internal voltage regulator. Connect to VCC and use bypass capacitor, 100 nF to Ground.                                                                                                                                                                                                                             |  |

| MCU           | 66  | VSS3     | Ground          | VSS3<br>Core Ground Pin      | The voltage supply of nominally 1.8 V is derived from the internal voltage regulator. The return current path is through the VSS3 pin. No static external loading of these pins is permitted. Connect to Ground                                                                                                                              |  |

| MCU           | 67  | VSSPLL   | Ground          | VSSPLL<br>PLL Ground Pin     | Provides operating voltage and ground for the phased-locked loop. This allows the supply voltage to the PLL to be bypassed independently. Internal power and ground are generated by the internal regulator. Connect to Ground                                                                                                               |  |

| MCU           | 68  | EXTAL    | Clock Input     | EXTAL<br>Oscillator Pin      | EXTAL is the external clock pin. On reset all the device clocks are derived from the internal reference clock. Connect to external crystal and 18 pf capacitor to Ground                                                                                                                                                                     |  |

| MCU           | 69  | XTAL     | Clock<br>Output | XTAL<br>Oscillator Pin       | XTAL is the crystal driver pin. On reset all the device clocks are derived from the internal reference clock. XTAL is the oscillator output. Connect to external crystal and 18 pf capacitor to Ground                                                                                                                                       |  |

Table 4. 912\_S812 pin definitions

| Analog<br>or MCU | Pin | Pin name | Pin<br>function | Formal name               | Description and recommendations                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-----|----------|-----------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU              | 70  | VDDPLL   | PLL Supply      | Output of 3.3 V regulator | Signals VDDPLL/VSSPLL are the secondary outputs of VREG_3V3 that provide the power supply for the PLL and oscillator. These signals are connected to device pins to allow external decoupling capacitors. (100 nF220 nF, X7R ceramic). In Shutdown mode, an external supply driving VDDPLL/VSSPLL can replace the voltage regulator.                                                                   |

| MCU              | 71  | IRQB     | I/O             | PE1/IRQB                  | Port E, I/O pin 1 is a general purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake-up the MCU from stop or wait mode.                                                                                                                                                                                         |

| MCU              | 72  | XIRQB    | I/O             | PE0/XIRQB                 | Port E, I/O pin 0 is a general purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake-up the MCU from stop or wait mode. The XIRQ interrupt is level sensitive and active low. As XIRQ is level sensitive while this pin is low, the MCU will not enter STOP mode. Connect to a 10K pull-up resistor to VCC. |

| MCU              | 73  | PA1      | I/O             | PA1                       | Port A, I/O pin 1 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                                                                            |

| MCU              | 74  | PA5      | I/O             | PA5                       | Port A, I/O pin 5 is a general purpose input or output pin.                                                                                                                                                                                                                                                                                                                                            |

| MCU              | 75  | VDD      | Supply          | Output of 3.3 V regulator | Signals VDD/VSS2 are the primary outputs of VREG_3V3 that provide the power supply for the core logic. These signals are connected to device pins to allow external decoupling capacitors (220 nF, X7R ceramic). In Shutdown mode, an external supply driving VDD/VSS2 can replace the voltage regulator.                                                                                              |

| MCU              | 76  | VSS2     | Ground          | Ground of 3.3 V regulator | See previous description on VDD.                                                                                                                                                                                                                                                                                                                                                                       |

| MCU              | 77  | PAD00    | A/D Input       | PAD00                     | PAD00 is the general purpose input or output pin and analog input AN0 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 78  | PAD01    | A/D Input       | PAD01                     | PAD01 is the general purpose input or output pin and analog input AN1 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 79  | PAD02    | PA/D Input      | PAD02                     | PAD02 is the general purpose input or output pin and analog input AN2 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 80  | PAD03    | A/D Input       | PAD03                     | PAD03 is the general purpose input or output pin and analog input AN3 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 81  | PAD04    | A/D Input       | PAD04                     | PAD04 is the general purpose input or output pin and analog input AN4 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 82  | PAD05    | A/D Input       | PAD05                     | PAD05 is the general purpose input or output pin and analog input AN5 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 83  | PAD06    | A/D Input       | PAD06                     | PAD06 is the general purpose input or output pin and analog input AN6 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 84  | PAD07    | A/D Input       | PAD07                     | PAD07 is the general purpose input or output pin and analog input AN7 of the analog-to-digital converter, A/D. Use voltage divider if necessary, and ESD protection capacitor. Use of low pass filter as necessary.                                                                                                                                                                                    |

| MCU              | 85  | VDDA     | Supply<br>Input | VDDA                      | This is the power supply input pin for the analog-to-digital converter and the voltage regulator. Connect to VCC and use a bypass capacitor, 100 nF to Ground.                                                                                                                                                                                                                                         |

| MCU              | 86  | VRH      | Supply<br>Input | VRH                       | VRH and VRL are the reference voltage input pins for the analog-to-digital converter.Connect to VCC and use a bypass capacitor, 100 nF to Ground.                                                                                                                                                                                                                                                      |

| MCU              | 87  | VRL      | Supply<br>Input | VRL                       | VRH and VRL are the reference voltage input pins for the analog-to-digital converter. Connect to Ground.                                                                                                                                                                                                                                                                                               |

| MCU              | 88  | VSSA     | Ground          | VSSA                      | This is the ground input pin for the analog-to-digital converter and the voltage regulator. Connect to Ground.                                                                                                                                                                                                                                                                                         |

Table 4. 912\_S812 pin definitions

| Analog or MCU | Pin | Pin name | Pin<br>function | Formal name             | Description and recommendations                                                                                                                                                                                                                     |

|---------------|-----|----------|-----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| мси           | 89  | PS0/RXD  | I/O             | PS0/<br>SCI RXD         | Port S, I/O pin 0 is a general purpose input or output pin. It can be configured as the receive pin RXD of serial communication interface (SCI). If used for ISO9141 connect to pin 4, MRX.                                                         |

| мси           | 90  | PS1/TXD  | I/O             | PS1/<br>SCI TXD         | Port S, I/O pin 1 is a general purpose input or output pin. It can be configured as the receive pin TXD of serial communication interface (SCI). If used for ISO9141 connect to pin 3, MTX.                                                         |

| MCU           | 91  | TEST     | Input           | Test                    | MUST leave OPEN. leave open                                                                                                                                                                                                                         |

| MCU           | 92  | PM5/SCK  | I/O             | PM5/<br>SPI SCK         | Port M, I/O pin 5 is a general purpose input or output pin. It can be configured as the serial clock input pin for the serial peripheral interface (SPI) when the SPI is in slave mode and as a serial clock output when the SPI is in master mode. |

| Analog        | 93  | RESETB   | Output          | RESETB Output to MCU    | Logic Level ResetB signal used to reset the MCU when the watchdog circuit times out, during undervoltage condition on VCC, and for initial power up and power down. Provides RESETB to MCU on pin 64.                                               |

| Analog        | 94  | INJFLT   | Output          | Injector Fault          | Logic Level output to MCU indicating any fault in the injector circuit.                                                                                                                                                                             |

| Analog        | 95  | RELFLT   | Output          | Relay Fault             | Logic Level output to MCU indicating any fault in the relay circuit.                                                                                                                                                                                |

| Analog        | 96  | IGNFLT   | Output          | Ignition Fault          | Logic Level output to MCU indicating any fault in the ignition circuit.                                                                                                                                                                             |

| Analog        | 97  | INJIN    | Input           | Injector Parallel Input | Logic Level Parallel Input from the MCU to control the injector driver output                                                                                                                                                                       |

| Analog        | 98  | RIN      | Input           | Relay Parallel Input    | Logic Level Parallel input to activate RELAY output, ROUT                                                                                                                                                                                           |

| Analog        | 99  | LAMPIN   | Input           | LAMP Parallel Input     | Logic Level Parallel input to activate the malfunction indicator lamp output, LAMP                                                                                                                                                                  |

| Analog        | 100 | IGNIN    | Input           | Ignition Parallel Input | Logic Level Parallel Input from MCU controlling the ignition coil current flow and spark.                                                                                                                                                           |

| -             | EP  | GND      | Ground          | Substrate Ground        | Should be tied to the Ground plane. Connect to Ground.                                                                                                                                                                                              |

## 5 Electrical characteristics

## 5.1 Maximum ratings

#### Table 5. 912\_S812 maximum ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                  | Rating                                                                                                       | Value                                  | Unit | Notes      |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------|------|------------|

| Electrical ratings                                                      |                                                                                                              |                                        |      |            |

| V <sub>ESD1</sub> V <sub>ESD2</sub> V <sub>ESD3</sub> V <sub>ESD4</sub> | ESD Voltage  • Human Body Model  • Machine Model  • Charge Device Model (Corner pins)  • Charge Device Model | ±2000<br>±200<br>±750<br>±500          | V    | (9)        |

| Thermal ratings                                                         |                                                                                                              |                                        | •    | •          |

| T <sub>A</sub><br>T <sub>J</sub><br>T <sub>C</sub>                      | Operating Temperature                                                                                        | -40 to 125<br>-40 to 150<br>-40 to 125 | °C   |            |

| T <sub>STG</sub>                                                        | Storage Temperature                                                                                          | -55 to 150                             | °C   |            |

| P <sub>D</sub>                                                          | Power Dissipation (T <sub>A</sub> = 25°C)                                                                    | 1.7                                    | W    | (12)       |

| T <sub>SOLDER</sub>                                                     | Peak Package Reflow Temperature During Solder Mounting                                                       | Note 11                                | °C   | (10), (11) |

| R <sub>θJA</sub><br>R <sub>θJL</sub><br>R <sub>θJC</sub>                | Thermal Resistance  • Junction-to-Ambient  • Junction- to-Lead  • Junction-to-Flag                           | 75<br>8.0<br>1.2                       | °C/W |            |

#### Notes

- 9. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), the Machine Model (MM) ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP}$  = 4.0 pF).

- 10. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 11. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.NXP.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 12. This parameter is guaranteed by design but is not production tested.

## 5.2 Analog MC33812 parametrics

The detailed MC33812 specifications can be found in the MC33812 data sheet. See MC33812.

## 5.3 Microcontroller S12XS parametrics

The detailed S12XS specifications can be found in the MC9S12XS128 reference manual. See MC9S12XS128.

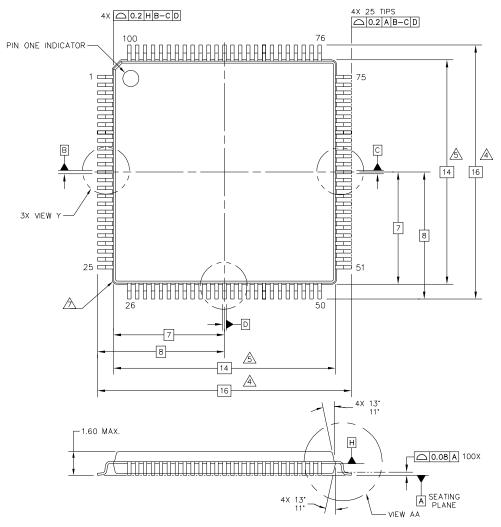

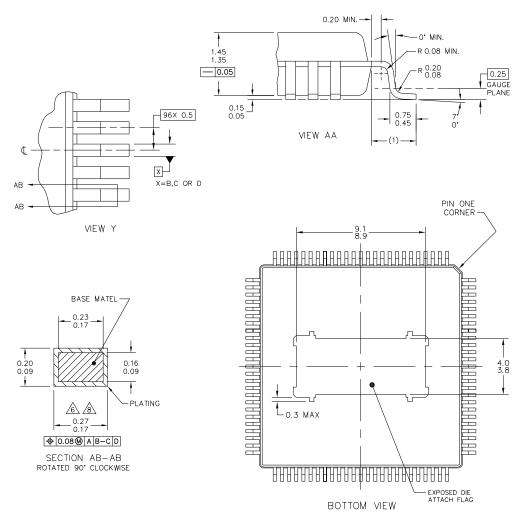

## 6 Packaging

## 6.1 Package mechanical dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to www.freescale.com and perform a keyword search for the drawing's document number.

| Package         | Suffix | Package outline drawing number |

|-----------------|--------|--------------------------------|

| 100-Pin LQFP-EP | AF     | 98ASA00371D                    |

RELEASED FOR EXTERNAL ASSEMBLY ONLY

THIS DESIGN ONLY MEETS EXTERNAL DESIGN AND ASSEMBLY RULES. MUST BE REVIEWED

AND UPDATED BEFORE BEING ASSEMBLED INTERNALLY.

| NXP SEMICONDUCTORS N.V.     ALL RIGHTS RESERVED | MECHANICAL OU | TLINE              | PRINT VERSION NOT | TO SCALE    |

|-------------------------------------------------|---------------|--------------------|-------------------|-------------|

| TITLE: LQFP PACKAGI                             | DOCUMEN       | NT NO: 98ASA00371D | REV: A            |             |

| 100 TERMINAL, 14X14X1.4                         | '             | STANDAF            | RD: NON-JEDEC     |             |

| EXPOSED PAG                                     |               | SOT1570            | <b>-</b> 1 (      | 08 JAN 2016 |

| © NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | MECHANICAL OUTLINE |                    | T TO SCALE  |

|--------------------------------------------------|---------------|--------------------|--------------------|-------------|

| TITLE: LQFP PACKAGI                              | Ε,            | DOCUME             | NT NO: 98ASA00371D | REV: A      |

| 100 TERMINAL, 14X14X1.4                          | 1, 0.5 PITCH  | STANDAF            | RD: NON-JEDEC      |             |

| EXPOSED PAG                                      | )             | SOT1570            | <del>-</del> 1     | 08 JAN 2016 |

#### NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. DIMENSIONS IN MILLIMETERS.

- 3. DATUMS B-C AND D TO BE DETERMINED AT DATUM PLANE H.

THESE DIMENSIONS TO BE DETERMINED AT SEATING PLANE, DATUM A.

THESE DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.25 PER SIDE. THESE DIMENSIONS DO INCLUDE MOLD MISMATCH. THESE DIMENSIONS ARE TO BE DETERMINED AT DATUM PLANE H..

$\stackrel{\textstyle \scriptstyle 6}{\sim}$  this dimension does not include dambar protrusion. Dambar protrusion shall not CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

EXACT SHAPE OF EACH CORNER IS OPTIONAL.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10MM AND 0.25MM FROM THE LEAD TIP.

| NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED | MECHANICAL OUTLINE |         | PRINT VERSION NOT  | TO SCALE |

|---------------------------------------------|--------------------|---------|--------------------|----------|

| TITLE: LQFP PACKAGE.                        |                    | DOCUME  | NT NO: 98ASA00371D | REV: A   |

| 100 TERMINAL, 14X14X1.4                     | ,                  | STANDAF | RD: NON-JEDEC      |          |

| EXPOSED PAI                                 |                    | S0T1570 | -1 08              | JAN 2016 |

# 7 Revision history

| Revision | Date   | Description of changes                                                                                                            |  |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | 2/2013 | Initial release                                                                                                                   |  |

| 2.0      | 2/2015 | Changed ordering part numbers from PM to MM     Updated document status to Advance Information     Update document form and style |  |

|          | 8/2016 | Updated to NXP document form and style                                                                                            |  |

#### How to Reach Us:

Home Page: NXP.com

Web Support:

http://www.nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no expressed or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation, consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by the customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address:

http://www.nxp.com/terms-of-use.html.

NXP, the NXP logo, Freescale, the Freescale logo and SMARTMOS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2016 NXP B.V.

Document Number: MM912\_S812

Rev. 2.0 8/2016