# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Document Number: MMA52xxLW Rev. 1, 03/2014

#### **VRoHS**

# Xtrinsic MMA52xxLW PSI5 Inertial Sensor

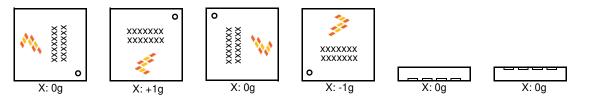

The MMA52xxLW family, a SafeAssure solution, includes the AKLV27 and PSI5 Version 1.3 compatible overdamped X-axis satellite accelerometers.

#### Features

- ±60g to ±480g Full-Scale Range

- Selectable 400 Hz, 3 Pole, or 4 pole Low-Pass Filter

- Single Pole High Pass Filter with Fast Startup and Output Rate Limiting

- PSI5 Version 1.3 Compatible

- PSI5-P10P-500/3L Compatible

- Programmable Time Slots with 0.5 μs Resolution

- Selectable Baud Rate: 125 kBaud or 190.5 kBaud

- Selectable Data Length: 8 or 10 bits

- Selectable Error Detection: Even Parity, or 3-bit CRC

- Optional Daisy Chain with External Low-Side Switch

- Two-Wire Programming Mode

- 16 μs Internal Sample Rate, with Interpolation to 1 μs

- Pb-Free 16-Pin QFN, 6 x 6 Package

- Qualified AECQ100, Revision G, Grade 1 (-40°C to +125°C) (<u>http://www.aecouncil.com/</u>)

#### **Typical Applications**

· Airbag Front and Side Crash Detection

|             | OR   | DERING INFO | RMATION |             |

|-------------|------|-------------|---------|-------------|

| Device      | Axis | Range       | Package | Shipping    |

| MMA5206LW   | Х    | 60g         | 2086-01 | Tubes       |

| MMA5212LW   | Х    | 120g        | 2086-01 | Tubes       |

| MMA5224LW   | Х    | 240g        | 2086-01 | Tubes       |

| MMA5248LW   | Х    | 480g        | 2086-01 | Tubes       |

| MMA5206LWR2 | Х    | 60g         | 2086-01 | Tape & Reel |

| MMA5212LWR2 | Х    | 120g        | 2086-01 | Tape & Reel |

| MMA5224LWR2 | Х    | 240g        | 2086-01 | Tape & Reel |

| MMA5248LWR2 | Х    | 480g        | 2086-01 | Tape & Reel |

MMA52xxLW

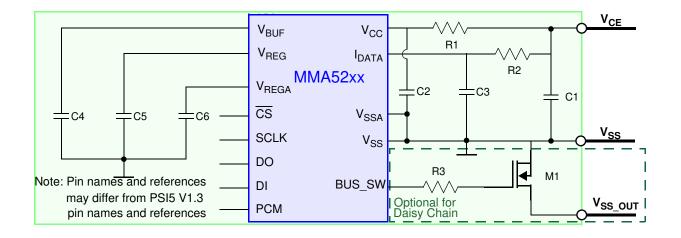

#### Figure 1. Application Diagram

**Table 1. External Component Recommendations**

| Ref Des    | Туре             | Description                   | Purpose                                                     |

|------------|------------------|-------------------------------|-------------------------------------------------------------|

| C1         | Ceramic          | 2.2 nF, 10%, 50V minimum, X7R | $\rm V_{\rm CC}$ Power Supply Decoupling and Signal Damping |

| C3         | Ceramic          | 470 pF, 10%, 50V minimum, X7R | I <sub>DATA</sub> Filtering and Signal Damping              |

| C2         | Ceramic          | 15 nF, 10%, 50V minimum, X7R  | V <sub>CC</sub> Power Supply Decoupling                     |

| C4, C5, C6 | Ceramic          | 1 µF, 10%, 10V minimum, X7R   | Voltage Regulator Output Capacitor(s)                       |

| R1         | General Purpose  | 82Ω, 5%, 200 PPM              | V <sub>CC</sub> Filtering and Signal Damping                |

| R2         | General Purpose  | 27Ω, 5%, 200 PPM              | I <sub>DATA</sub> Filtering and Signal Damping              |

| R3         | General Purpose  | 20 kΩ, 5%, 200 PPM            | Gate Resistor for External Low-Side Daisy Chain FET         |

| M1         | N-Channel MOSFET | _                             | Low-Side Daisy Chain Transistor                             |

EARTH GROUND

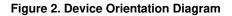

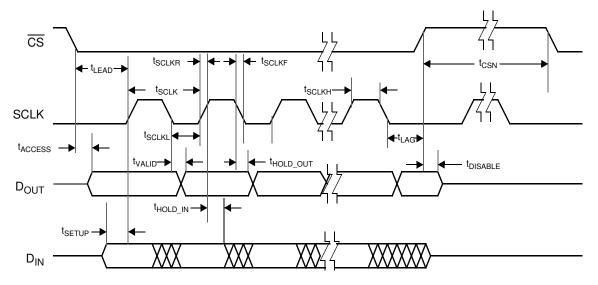

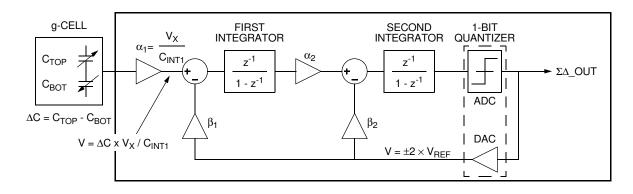

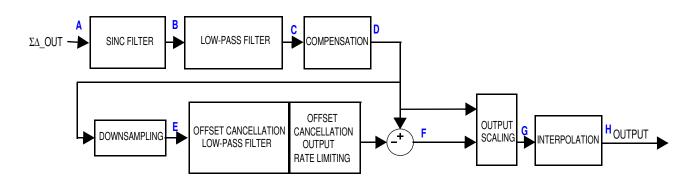

Figure 3. Internal Block Diagram

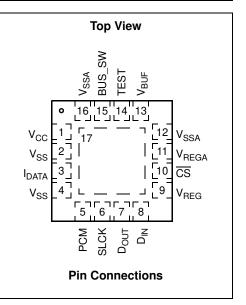

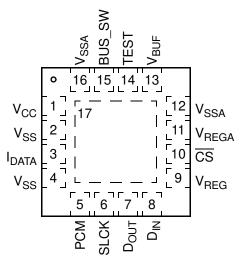

# 1 Pin Connections

#### Table 2. Pin Description

| Pin | Pin<br>Name       | Formal Name              | Definition                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CC</sub>   | Supply                   | This pin is connected to the PSI5 power and data line through a resistor and supplies power to the device. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1.                                                                                                                             |

| 2   | V <sub>SS</sub>   | Digital GND              | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                |

| 3   | I <sub>DATA</sub> | Response<br>Current      | This pin is connected to the PSI5 power and data line through a resistor and modulates the response current for PSI5 com-<br>munication. Reference Figure 1.                                                                                                                                                                       |

| 4   | V <sub>SS</sub>   | Digital GND              | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                |

| 5   | PCM               | PCM<br>Output            | This pin provides a 4 MHz PCM signal proportional to the acceleration data for test purposes. The output can be enabled via OTP. Reference Section 3.5.3.7. If unused, this pin must be left unconnected.                                                                                                                          |

| 6   | SCLK              | SPI Clock                | This input pin provides the serial clock to the SPI port for test purposes. An internal pulldown device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                                |

| 7   | D <sub>OUT</sub>  | SPI Data Out             | This pin functions as the serial data output from the SPI port for test purposes. This pin must be left unconnected in the appli-<br>cation.                                                                                                                                                                                       |

| 8   | D <sub>IN</sub>   | SPI Data In              | This pin functions as the serial data input to the SPI port for test purposes. An internal pulldown device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                             |

| 9   | V <sub>REG</sub>  | Digital<br>Supply        | This pin is connected to the power supply for the internal digital circuitry. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1.                                                                                                                                                          |

| 10  | CS                | Chip Select              | This input pin provides the chip select to the SPI port for test purposes. An internal pullup device is connected to this pin. This pin must be left unconnected in the application.                                                                                                                                               |

| 11  | V <sub>REGA</sub> | Analog<br>Supply         | This pin is connected to the power supply for the internal analog circuitry. An external capacitor must be connected between this pin and $V_{SSA}$ . Reference Figure 1.                                                                                                                                                          |

| 12  | VSSA              | Analog GND               | This pin is the power supply return node for the analog circuitry.                                                                                                                                                                                                                                                                 |

| 13  | V <sub>BUF</sub>  | Power<br>Supply          | This pin is connected to a buffer regulator for the internal circuitry. The buffer regulator supplies both the analog ( $V_{REGA}$ ) and digital ( $V_{REG}$ ) supplies to provide immunity from EMC and supply dropouts on $V_{CC}$ . An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1. |

| 14  | TEST              | Test Pin                 | This pin is must be grounded or left unconnected in the application.                                                                                                                                                                                                                                                               |

| 15  | BUS_SW            | Bus Switch<br>Gate Drive | This pin is the drive for a low-side daisy chain switch. When daisy chain mode is enabled, this pin is connected to the gate of an n-channel FET which connects $V_{SS}$ to $V_{SS\_OUT}$ . Reference Figure 1. If unused, this pin must be left unconnected.                                                                      |

| 16  | VSSA              | Analog GND               | This pin is the power supply return node for the analog circuitry.                                                                                                                                                                                                                                                                 |

| 17  | PAD               | Die Attach Pad           | This pin is the die attach flag, and is internally connected to VSS. Reference Section 7 for die attach pad connection details.                                                                                                                                                                                                    |

|     | Corner<br>Pads    | Corner Pads              | The corner pads are internally connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                      |

#### **Electrical Characteristics** 2

#### 2.1 **Maximum Ratings**

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it.

| #                   | Rating                                                                                                                                                                                                                                                   | Symbol                                                                       | Value                           | Unit             |                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------|------------------|--------------------------|

| 1<br>2<br>3         | Supply Voltage (V <sub>CC</sub> , I <sub>DATA</sub> )<br>Reverse Current $\leq$ 160 mA, t $\leq$ 80 ms<br>Continuous<br>Transient (< 10 µs)                                                                                                              | Vcc_rev<br>Vcc_max<br>Vcc_trans                                              | -0.7<br>+20.0<br>+25.0          | V<br>V<br>V      | (3)<br>(3)<br>(9)        |

| 4                   | V <sub>BUF,</sub> Test, BUS_SW                                                                                                                                                                                                                           |                                                                              | -0.3 to +4.2                    | V                | (3)                      |

| 5                   | V <sub>REG</sub> , V <sub>REGA,</sub> SCLK, CS, D <sub>IN</sub> , D <sub>OUT</sub> , PCM                                                                                                                                                                 |                                                                              | -0.3 to +3.0                    | V                | (3)                      |

| 6                   | Powered Shock (six sides, 0.5 ms duration)                                                                                                                                                                                                               | 9 <sub>pms</sub>                                                             | ±2000                           | g                | (3)                      |

| 7                   | Unpowered Shock (six sides, 0.5 ms duration)                                                                                                                                                                                                             | 9 <sub>shock</sub>                                                           | ±2500                           | g                | (3)                      |

| 8                   | Drop Shock (to concrete, tile or steel surface, 10 drops, any orientation)                                                                                                                                                                               | h <sub>DROP</sub>                                                            | 1.2                             | m                | (5)                      |

| 9<br>10<br>11<br>12 | Electrostatic Discharge (per AEC-Q100)<br>External Pins (V <sub>CC</sub> , I <sub>DATA</sub> , V <sub>SS</sub> , V <sub>SSA</sub> ), HBM (100 pF, 1.5 k $\Omega$ )<br>HBM (100 pF, 1.5 k $\Omega$ )<br>CDM (R = 0 $\Omega$ )<br>MM (200 pF, 0 $\Omega$ ) | V <sub>ESD</sub><br>V <sub>ESD</sub><br>V <sub>ESD</sub><br>V <sub>ESD</sub> | ±4000<br>±2000<br>±1500<br>±200 | V<br>V<br>V<br>V | (5)<br>(5)<br>(5)<br>(5) |

| 13<br>14            | Temperature Range<br>Storage<br>Junction                                                                                                                                                                                                                 | T <sub>stg</sub><br>T <sub>J</sub>                                           | -40 to +125<br>-40 to +150      | °C<br>°C         | (3)<br>(9)               |

| 15                  | Thermal Resistance                                                                                                                                                                                                                                       | θ <sub>JC</sub>                                                              | 2.5                             | °C/W             | (9, 14)                  |

| #        | Characteristic Symbol Min                                                                |                                       | Min                                            | Тур | Мах                                      | Units  |            |

|----------|------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------|-----|------------------------------------------|--------|------------|

| 16<br>17 | Supply Voltage                                                                           | V <sub>CC</sub><br>V <sub>CC_UV</sub> | V <sub>L</sub><br>4.2<br>V <sub>VCC_UV_F</sub> |     | V <sub>H</sub><br>17.0<br>V <sub>L</sub> | v<br>v | (1)<br>(9) |

| 18       | Programming Voltage ( $I_{DATA} \le 85 \text{ mA}$ )<br>Applied to $I_{DATA}$ , $V_{CC}$ | V <sub>PP</sub>                       | 14.0                                           | _   | _                                        | v      | (3)        |

| 19<br>20 | Operating Temperature Range                                                              | T <sub>A</sub><br>T <sub>A</sub>      | T <sub>L</sub><br>-40<br>-40                   |     | T <sub>H</sub><br>+105<br>+125           | ℃<br>℃ | (1)<br>(3) |

#

| #                    | Characteristic                                                                                                                                                                   | Symbol                                                                   | Min                                  | Тур                                  | Мах                                 | Units       |                                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------|-------------|-------------------------------------------|

| 21                   | Quiescent Supply Current *                                                                                                                                                       | I <sub>IDLE</sub>                                                        | 4.0                                  | —                                    | 8.0                                 | mA          | (1)                                       |

| 22                   | Modulation Supply Current *                                                                                                                                                      | I <sub>MOD</sub>                                                         | I <sub>IDLE</sub> + 22.0             | I <sub>IDLE</sub> + 26.0             | I <sub>IDLE</sub> + 30.0            | mA          | (1)                                       |

| 23                   | Inrush Current (Power On until $V_{BUF}$ , $V_{REG}$ , $V_{REGA}$ Stable)                                                                                                        | I <sub>INRUSH</sub>                                                      | —                                    | _                                    | 30                                  | mA          | (3)                                       |

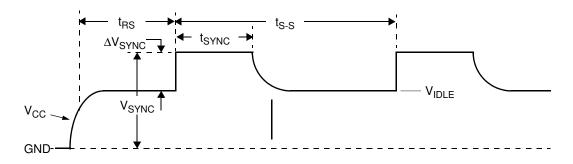

| 24<br>25<br>26       | Internally Regulated Voltages *<br>V <sub>BUF</sub> *<br>V <sub>REG</sub> *<br>V <sub>REGA</sub> *                                                                               | V <sub>BUF</sub><br>V <sub>REG</sub><br>V <sub>REGA</sub>                | 3.60<br>2.425<br>2.425               | 3.80<br>2.50<br>2.50                 | 4.00<br>2.575<br>2.575              | V<br>V<br>V | (1)<br>(1)<br>(1)                         |

| 27<br>28<br>29<br>30 | Low Voltage Detection Threshold<br>V <sub>CC</sub> Falling<br>V <sub>BUF</sub> Falling<br>V <sub>REG</sub> Falling<br>V <sub>REGA</sub> Falling<br>Hysteresis<br>V <sub>CC</sub> | Vvcc_uv_f<br>Vbuf_uv_f<br>Vreg_uv_f<br>Vrega_uv_f<br>Vcc_hyst            | 3.40<br>2.95<br>2.15<br>2.15<br>0.10 | 3.70<br>3.15<br>2.25<br>2.25<br>0.25 | 4.0<br>3.35<br>2.35<br>2.35<br>0.40 |             | (3, 6<br>(3, 6<br>(3, 6<br>(3, 6<br>(3, 6 |

| 32<br>33<br>34       | V <sub>BUF</sub><br>VREG<br>V <sub>REGA</sub>                                                                                                                                    | V <sub>BUF_HYST</sub><br>V <sub>REG_HYST</sub><br>V <sub>REGA_HYST</sub> | 0.05<br>0.05<br>0.05                 | 0.10<br>0.10<br>0.10                 | 0.15<br>0.15<br>0.15                | V<br>V<br>V | (3)<br>(3)<br>(3)                         |

| 35<br>36             | External Capacitor (V <sub>BUF</sub> , V <sub>REG</sub> , V <sub>REG</sub> )<br>Capacitance<br>ESR (including interconnect resistance)                                           | ESR                                                                      | 500<br>0                             | 1000<br>—                            | 1500<br>200                         | nF<br>mΩ    | (9)<br>(9)                                |

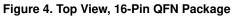

| 37<br>38             | Synchronization Pulse (Figure 5)<br>V <sub>IDLE</sub> Voltage Range *<br>DC Sync Pulse Detection Threshold *                                                                     | VIDLE<br>ΔV <sub>SYNC</sub>                                              | <br>V <sub>IDLE</sub> +1.4           | <br>V <sub>IDLE</sub> +2.0           | 15.4<br>V <sub>IDLE</sub> +2.6      | v<br>v      | (3, 1<br>(3, 6                            |

| 39                   | Sync Pulse Pulldown Current                                                                                                                                                      | I <sub>SYNC_PD</sub>                                                     | -                                    | I <sub>MOD</sub> - I <sub>IDLE</sub> | _                                   | mA          | (3)                                       |

| 40                   | Output High Voltage (DO)<br>I <sub>Load</sub> = 100 μA                                                                                                                           | V <sub>OH</sub>                                                          | V <sub>REG</sub> - 0.1               | _                                    | _                                   | v           | (9)                                       |

| 41                   | Output Low Voltage (DO)<br>I <sub>Load</sub> = 100 μA                                                                                                                            | V <sub>OL</sub>                                                          | _                                    | _                                    | 0.1                                 | v           | (9)                                       |

| 42                   | Inp <u>ut H</u> igh Voltage<br>CS, SCLK, DI                                                                                                                                      | V <sub>IH</sub>                                                          | 0.7 * V <sub>REG</sub>               | _                                    | _                                   | v           | (9)                                       |

| 43                   | Inp <u>ut L</u> ow Voltage<br>CS, SCLK, DI                                                                                                                                       | V <sub>IL</sub>                                                          | _                                    | _                                    | 0.3 * V <sub>REG</sub>              | v           | (9)                                       |

| 44<br>45             | Input Current<br>High (at V <sub>IH</sub> ) <u>(DI)</u><br>Low (at V <sub>IL</sub> ) (CS)                                                                                        | I <sub>IH</sub><br>I <sub>IL</sub>                                       | -100<br>10                           |                                      | -10<br>100                          | μΑ<br>μΑ    | (9)<br>(9)                                |

| 46                   | Pulldown Resistance (SCLK)                                                                                                                                                       | R <sub>PD</sub>                                                          | 20                                   | æ                                    | 100                                 | kΩ          | (9)                                       |

| 47                   | BUS_SW Output High Voltage (BUS_SW)<br>I <sub>Load</sub> = 100 μA                                                                                                                | V <sub>BUS_SW_OH</sub>                                                   | 3.15                                 | _                                    | V <sub>BUF</sub>                    | v           | (9)                                       |

| 48                   | Output Low Voltage (BUS_SW)<br>I <sub>Load</sub> = 100 μA                                                                                                                        | V <sub>BUS_SW_OL</sub>                                                   | 0.0                                  | _                                    | 0.45                                | v           | (9)                                       |

| 49                   | Daisy Chain Addressing Mode Sync Pulse Period                                                                                                                                    |                                                                          | -                                    | t <sub>S-S_PM_L</sub>                | _                                   | S           | (7)                                       |

| 50                   | Bus Switch Output Activation Time (C = 50 pF)<br>From last bit of "SetAdr" Response to 80% of V <sub>BUS_SW_OH</sub>                                                             | tBUS_SW                                                                  | _                                    | _                                    | 300                                 | μs          | (7)                                       |

| 51                   | Sync Pulse Blanking Time after "SetAdr" Command Received<br>From last bit of "SetAdr" Response                                                                                   | t <sub>DC_BLANKING</sub>                                                 |                                      | 200000 / f <sub>OSC</sub>            |                                     | s           | (7)                                       |

# 2.4 Electrical Characteristics - Sensor And Signal Chain

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified.}$

| #                                | Characteristic                                                                                                                                                                                                                                                                                                                               | Symbol                                                                                                    | Min                              | Тур              | Мах                        | Units                            |                                        |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|------------------|----------------------------|----------------------------------|----------------------------------------|

| 52<br>53<br>54<br>55             | Sensitivity (10-bit output @ 100 Hz, referenced to 0 Hz)<br>±60g Range<br>±120g Range<br>±240g Range<br>±480g Range<br>Total Sensitivity Error (including non-linearity)                                                                                                                                                                     | SENS<br>SENS<br>SENS<br>SENS                                                                              | <br>                             | 8<br>4<br>2<br>1 | <br>                       | LSB/g<br>LSB/g<br>LSB/g<br>LSB/g | (1)<br>(1)<br>(1)<br>(1)               |

| 56<br>57<br>58<br>59<br>60<br>61 | $ \begin{array}{l} T_A = 25^{\circ}C, \leq \pm 240g \\ T_L \leq T_A \leq T_H, \leq \pm 240g \\ T_L \leq T_A \leq T_H, \leq \pm 240g, \\ V_{VCC\_UV\_F} \leq V_{CC} \leq V_L \\ T_A = 25^{\circ}C, > \pm 240g \\ T_L \leq T_A \leq T_H, > \pm 240g \\ T_L \leq T_A \leq T_H, > \pm 240g, \\ V_{VCC\_UV\_F} \leq V_{CC} \leq V_L \end{array} $ | ΔSENS_240   ΔSENS_240   ΔSENS_240   ΔSENS_240   ΔSENS_480   ΔSENS_480   ΔSENS_480   ΔSENS_480   ΔSENS_480 | -5<br>-7<br>-7<br>-5<br>-7<br>-7 |                  | +5<br>+7<br>+5<br>+7<br>+7 | %<br>%<br>%<br>%                 | (1)<br>(1)<br>(9)<br>(1)<br>(1)<br>(9) |

| 62<br>63                         | Digital Offset Before Offset Cancellation 10-bit 10-bit, $T_L \le T_A \le T_H$ , $V_{VCC\_UV\_F} \le V_{CC} \le V_L$                                                                                                                                                                                                                         | OFF <sub>10Bit</sub><br>OFF <sub>10Bit</sub>                                                              | -52<br>-52                       | 0<br>0           | +52<br>+52                 | LSB<br>LSB                       | (1)<br>(9)                             |

| 64<br>65                         | 10-DIL, 0.3 HZ HPF 01 0.1 HZ HPF                                                                                                                                                                                                                                                                                                             | OFF <sub>10Bit</sub><br>OFF <sub>10Bit</sub>                                                              | -1<br>-2                         | 0<br>0           | +1<br>+2                   | LSB<br>LSB                       | (1)<br>(9)                             |

| 66                               | Continuous Offset Monitor Limit<br>10-bit output, before compensation                                                                                                                                                                                                                                                                        | OFF <sub>MON</sub>                                                                                        | -66                              | _                | +66                        | LSB                              | (3)                                    |

| 67                               | Range of Output (10-bit Mode)<br>Acceleration                                                                                                                                                                                                                                                                                                | RANGE                                                                                                     | -480                             | _                | +480                       | LSB                              | (3)                                    |

| 68<br>69                         | Cross-Axis Sensitivity<br>Z-axis to X-axis<br>Y-axis to X-axis                                                                                                                                                                                                                                                                               | V <sub>ZX</sub><br>V <sub>YX</sub>                                                                        | -5<br>-5                         |                  | +5<br>+5                   | %<br>%                           | (3)<br>(3)                             |

| 70                               | System Output Noise Peak (10-bit Mode, 1 Hz - 1 kHz, All Ranges)                                                                                                                                                                                                                                                                             | n <sub>Peak</sub>                                                                                         | -4                               | —                | +4                         | LSB                              | (3)                                    |

| 71                               | System Output Noise RMS (10-bit mode, 1 Hz - 1 kHz, All Ranges)                                                                                                                                                                                                                                                                              | * n <sub>RMS</sub>                                                                                        | _                                | —                | +1.0                       | LSB                              | (3)                                    |

| 72<br>73                         | Non-linearity<br>10-bit output, ≤ ±240g<br>10-bit output, > ±240g                                                                                                                                                                                                                                                                            | NL <sub>OUT_240g</sub><br>NL <sub>OUT_480g</sub>                                                          | -2<br>-2                         |                  | +2<br>+2                   | %<br>%                           | (3)<br>(3)                             |

# 2.5 Electrical Characteristics - Self-Test and Overload

$V_L \leq (V_{CC} \text{ - } V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, \Delta T \leq 25 \text{ K/min, unless otherwise specified.}$

| #                    | Characteristic                                                                                                             | Symbol                                                      | Min                  | Тур      | Мах                      | Units                    | [                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------|--------------------------|--------------------------|--------------------------|

| 74<br>75<br>76<br>77 | 10-Bit Output During Active Self-Test ( $T_L \le T_A \le T_H$ )<br>±60g Range<br>±120g Range<br>±240g Range<br>±480g Range | * 9st10_60X<br>* 9st10_120X<br>* 9st10_240X<br>* 9st10_480X | 120<br>40<br>56<br>8 | <br><br> | 280<br>160<br>184<br>112 | LSB<br>LSB<br>LSB<br>LSB | (3)<br>(3)<br>(3)<br>(3) |

| 78                   | Acceleration (without hitting internal g-cell stops)<br>±60g Range Positive/Negative                                       | g <sub>g-cell_</sub> Clip60X                                | 400                  | 456      | 500                      | g                        | (9)                      |

| 79                   | Acceleration (without hitting internal g-cell stops)<br>±120g Range Positive/Negative                                      | gg-cell_Clip120X                                            | 400                  | 456      | 500                      | g                        | (9)                      |

| 80                   | Acceleration (without hitting internal g-cell stops)<br>±240g Range Positive/Negative                                      | gg-cell_Clip240X                                            | 1750                 | 2065     | 2300                     | g                        | (9)                      |

| 81                   | Acceleration (without hitting internal g-cell stops)<br>±480g Range Positive/Negative                                      | gg-cell_Clip480X                                            | 1750                 | 2065     | 2300                     | g                        | (9)                      |

| 82                   | $\Sigma\Delta$ and Sinc Filter Clipping Limit $\pm 60g$ Range Positive/Negative                                            | gadc_clip60X                                                | 191                  | 210      | 233                      | g                        | (9)                      |

| 83                   | $\Sigma\Delta$ and Sinc Filter Clipping Limit $\pm 120g$ Range Positive/Negative                                           | GADC_Clip120X                                               | 353                  | 380      | 410                      | g                        | (9)                      |

| 84                   | ΣΔ and Sinc Filter Clipping Limit<br>±240g Range Positive/Negative                                                         | gADC_Clip240X                                               | 928                  | 1055     | 1218                     | g                        | (9)                      |

| 85                   | ΣΔ and Sinc Filter Clipping Limit<br>±480g Range Positive/Negative                                                         | gADC_Clip480X                                               | 1690                 | 1879     | 2106                     | g                        | (9)                      |

# 2.6 Dynamic Electrical Characteristics - PSI5

$V_L \le (V_{CC} - V_{SS}) \le V_H, T_L \le T_A \le T_H, \Delta T \le 25$  K/min, unless otherwise specified

| #                                                                                        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol                                                                                                                                                                                                                                                                                                             | Min                                                                                              | Тур                                                                                                                                                                      | Max                                                                                              | Units                                                                                                          | ]                                                                                                                                                        |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 86<br>87<br>88<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>100<br>101 | Initialization Timing<br>Phase 1<br>Phase 2 (10-Bit, Synchronous Mode, k = 4)<br>Phase 2 (8-Bit, Synchronous Mode 0, k = 8)<br>Phase 2 (8-Bit, Asynchronous Mode 0, k = 8)<br>Phase 2 (8-Bit, Asynchronous Mode 0, k = 16)<br>Phase 3 (10-Bit, Synchronous Mode, ST_RPT = 0)<br>Phase 3 (10-Bit, Asynchronous Mode, ST_RPT = 0)<br>Phase 3 (10-Bit, Asynchronous Mode 0, ST_RPT = 0)<br>Phase 3 (10-Bit, Asynchronous Mode 0, ST_RPT = 0)<br>Phase 3 (8-Bit, Asynchronous Mode 0, ST_RPT = 0)<br>Phase 3 (8-Bit, Asynchronous Mode 0, ST_RPT = 0)<br>Offset Cancellation Stage 1 Operating Time<br>Offset Cancellation Stage 1 Operating Time<br>Self-Test Stage 1 Operating Time<br>Self-Test Stage 2 Operating Time<br>Self-Test Stage 3 Operating Time<br>Self-Test Repetitions<br>Programming Mode Entry Window | tpsi5_INIT1   tpsi5_INIT2_10s   tpsi5_INIT2_10a   tpsi5_INIT2_10a0   tpsi5_INIT2_8a0   tpsi5_INIT3_10a   tpsi5_INIT3_10a0   tpsi5_INIT3_10a0   tpsi5_INIT3_8a   tpsi5_INIT3_8a   tpsi5_INIT3_10a0   tpsi5_INIT3_8a0   tocc1   toc2   tST1   tST2   tST3   ST_RPT   tPME                                            | <br><br><br><br>0                                                                                | 532000 / fosc<br>256 * ts-s<br>288 * ts-s<br>512 * tasync<br>576 * tasync<br>2 * ts-s<br>19 * tasync<br>320000 / fosc<br>128000 / fosc<br>128000 / fosc<br>300000 / fosc |                                                                                                  | \$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$ | (7)<br>(7)<br>(7)<br>(7, 12)<br>(7, 12)<br>(7, 12)<br>(7, 12)<br>(7, 12)<br>(7, 12)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7 |

| 102<br>103<br>104<br>105<br>106<br>107<br>108<br>109<br>110<br>111<br>112<br>113         | Synchronization Pulse (Figure 5, Figure 28 and Figure 32)<br>Reset to first sync pulse (Program Mode Entry)<br>Reset to first sync pulse (Normal Mode)<br>Sync Pulse Period<br>Sync Pulse Width<br>Sync Pulse Reference LPF time constant<br>Sync Pulse Reference Discharge Activation Time<br>Sync Pulse Reference Discharge Activation Time<br>Sync Pulse Detection Disable Time (BLANKTIME = 0)<br>Analog Delay of Sync Pulse Detection<br>Sync Pulse Pulldown Function Delay Time<br>Sync Pulse Pulldown Function Delay Time<br>Sync Pulse Detection Jitter                                                                                                                                                                                                                                                     | <sup>t</sup> RS_PM<br>tRS<br><sup>t</sup> S-S<br><sup>t</sup> SYNC<br><sup>t</sup> SYNC_LPF<br><sup>t</sup> SYNC_LPF_RST_ST<br><sup>t</sup> SYNC_LPF_RST<br><sup>t</sup> SYNC_LPF_RST<br><sup>t</sup> SYNC_DF_500<br><sup>t</sup> A_SYNC_DLY<br><sup>t</sup> PD_DLY<br><sup>t</sup> PD_ON<br><sup>t</sup> SYNC_JIT | 58<br>tpsis_init1<br>tsync_off<br>9<br>120<br>—<br>—<br>50<br>—<br>50<br>—<br>0                  |                                                                                                                                                                          |                                                                                                  | ms<br>s<br>μs<br>μs<br>s<br>s<br>s<br>s<br>s<br>s<br>s<br>s<br>s<br>s                                          | (7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)                                                                                       |

| 114<br>115                                                                               | Data Transmission Single Bit Time (PSI5 Low Bit Rate)<br>Data Transmission Single Bit Time (PSI5 High Bit Rate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <sup>t</sup> віт_low<br><sup>t</sup> віт_ні                                                                                                                                                                                                                                                                        | 7.6000<br>4.9875                                                                                 | 8.0000<br>5.2500                                                                                                                                                         | 8.4000<br>5.5125                                                                                 | μs<br>μs                                                                                                       | (7)<br>(7)                                                                                                                                               |

| 116<br>117                                                                               | Modulation Current (20% to 80% of I <sub>MOD</sub> - I <sub>IDLE</sub> )<br>Rise Time<br>Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <sup>t</sup> RISE<br><sup>t</sup> FALL                                                                                                                                                                                                                                                                             | 324<br>324                                                                                       | 463<br>463                                                                                                                                                               | 602<br>602                                                                                       | ns<br>ns                                                                                                       | (3)<br>(3)                                                                                                                                               |

| 118<br>119                                                                               | Position of bit transition (PSI5 Low Baud Rate)<br>Position of bit transition (PSI5 High Baud Rate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t <sub>Bittrans_LowBaud</sub>                                                                                                                                                                                                                                                                                      | 49<br>47                                                                                         | 50<br>æ                                                                                                                                                                  | 51<br>53                                                                                         | %<br>%                                                                                                         | (7)<br>(7)                                                                                                                                               |

| 120                                                                                      | Asynchronous Response Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tASYNC                                                                                                                                                                                                                                                                                                             | —                                                                                                | 912 / f <sub>OSC</sub>                                                                                                                                                   | æ                                                                                                | s                                                                                                              | (7)                                                                                                                                                      |

| 121<br>122<br>123<br>124<br>125<br>126<br>127<br>128                                     | Time Slots<br>Minimum Programmed Time Slot (TIMESLOTx = 0x001)<br>Maximum Programmed Time Slot (TIMESLOTx = 0x3FF)<br>Default Time Slot (TIMESLOTx = 0x000)<br>Time Slot Resolution<br>Sync Pulse to Daisy Chain Default Time Slot 1<br>Sync Pulse to Daisy Chain Default Time Slot 2<br>Sync Pulse to Daisy Chain Default Time Slot 3<br>Sync Pulse to Daisy Chain Programming Time Slot                                                                                                                                                                                                                                                                                                                                                                                                                           | <sup>t</sup> TIMESLOTx_MIN<br><sup>t</sup> TIMESLOTx_MAX<br><sup>t</sup> TIMESLOT_DFLT<br><sup>t</sup> TIMESLOT_C1<br><sup>t</sup> TIMESLOT_DC1<br><sup>t</sup> TIMESLOT_DC2<br><sup>t</sup> TIMESLOT_DC3<br><sup>t</sup> TIMESLOT_DCP                                                                             |                                                                                                  | 2 / f <sub>OSC</sub><br>2046 / fosc<br>186 / fosc<br>2 / fosc<br>186 / fosc<br>186 / fosc<br>1400 / fosc<br>186 / fosc                                                   |                                                                                                  | s<br>s<br>s/LSB<br>s<br>s<br>s<br>s                                                                            | (7, 9)<br>(3, 7)<br>(3, 7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)                                                                              |

| 129<br>130<br>131<br>132                                                                 | Data Interpolation Latency (Figure 35, Figure 36)<br>Data Setup Time - Synchronous Mode (Figure 36)<br>Data Setup Time - Double Sample Rate Mode (Figure 37)<br>Data Setup Time - 16-bit Resolution Mode (Figure 39)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tLAT_INTERP<br>tDATASETUP_synch<br>tDATASETUP_double<br>tDATASETUP_16                                                                                                                                                                                                                                              | 64 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub> | <br>                                                                                                                                                                     | 65 / f <sub>OSC</sub><br>56 / f <sub>OSC</sub><br>60 / f <sub>OSC</sub><br>60 / f <sub>OSC</sub> | S<br>S<br>S<br>S                                                                                               | (7)<br>(7)<br>(7)<br>(7)                                                                                                                                 |

| 133<br>134<br>135<br>136<br>137                                                          | Programming Mode Timing<br>Programming Mode Sync Pulse Period<br>Programming Mode Command Timeout<br>OTP Write Command to $V_{CC} = V_{PP}$<br>OTP Write CMD Response to OTP programming start<br>Time to program the OTP User Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ts-s_pm_l<br>tpm_timeout<br>tprog_hold<br>tprog_delay<br>tprog_array                                                                                                                                                                                                                                               | 495<br>—<br>—<br>—<br>70                                                                         | 500<br>4 * t <sub>S-S_PM</sub><br>—<br>—<br>—                                                                                                                            | 505<br>—<br>20<br>40<br>—                                                                        | μs<br>μs<br>μs<br>ms<br>ms                                                                                     | (7)<br>(7)<br>(7)<br>(7)<br>(7)                                                                                                                          |

# **2.7 Dynamic Electrical Characteristics - Signal Chain** $V_L \leq (V_{CC} - V_{SS}) \leq V_H, T_L \leq T_A \leq T_H, \Delta T \leq 25$ K/min, unless otherwise specified

| #                                                                                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol                                                                                                                                                                                             | Min                              | Тур                                                                                                                                                                                          | Мах                              | Units                                                            | ]                                                                            |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|

| 138                                                                                            | Internal Oscillator Frequency *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | fosc                                                                                                                                                                                               | 3.80                             | 4                                                                                                                                                                                            | 4.20                             | MHz                                                              | (1                                                                           |

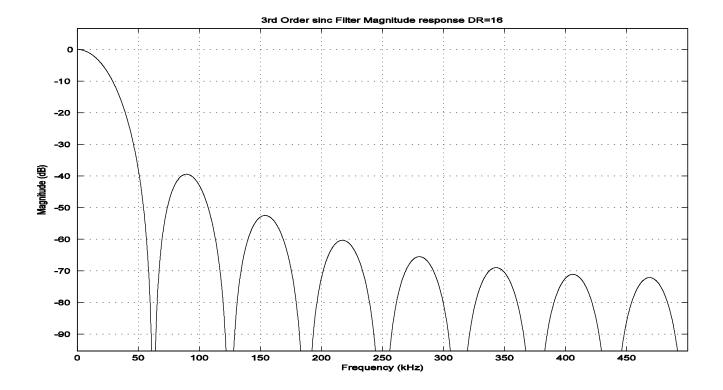

| 139<br>140<br>141<br>142                                                                       | DSP Low-Pass Filter (Note15)<br>Cutoff frequency LPF0 (referenced to 0 Hz) *<br>Filter Order LPF0 *<br>Cutoff frequency LPF1 (referenced to 0 Hz) *<br>Filter Order LPF1 *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f <u>c_l</u> pf0<br>O <sub>LPF0</sub><br>fc_lpf1<br>O <sub>LPF1</sub>                                                                                                                              |                                  | 400<br>3<br>400<br>4                                                                                                                                                                         |                                  | Hz<br>1<br>Hz<br>1                                               | (7<br>(7<br>(7<br>(7                                                         |

| 143<br>144<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154<br>155<br>156 | DSP Offset Cancellation Low-Pass Filter (Note 15)<br>Offset Cancellation Low-Pass Filter Input Sample Rate<br>Stage 1 Cutoff frequency, Startup Phase 1<br>Stage 1 Filter Order, Startup Phase 1<br>Stage 2 Cutoff frequency, Startup Phase 1<br>Stage 2 Filter Order, Startup Phase 1<br>Cutoff frequency, Option 0<br>Filter Order, Option 0<br>Offset Cancellation Output Update Rate (8-Bit Mode)<br>Offset Cancellation Output Update Rate (10-Bit Mode)<br>Offset Cancellation Output Update Rate (10-Bit Mode)<br>Offset Cancellation Output Step Size (10-Bit Mode)<br>Offset Monitor Update Frequency<br>Offset Monitor Count Limit<br>Offset Monitor Counter Size | <sup>t</sup> OC_SampleRate<br>fc_OC10<br>OOC10<br>fc_OC03<br>OOC03<br>fc_OC0<br>OCC0<br>tOffRate_8<br>OFF Step_8<br>tOffRate_10<br>OFF Step_10<br>OFF MON_OSC<br>OFFMON_CNTLIMIT<br>OFFMON_CNTSIZE |                                  | 256<br>10.0<br>1<br>0.300<br>1<br>0.100<br>1<br>f <sub>OSC</sub> / 2e6<br>0.125<br>f <sub>OSC</sub> / 2e6<br>0.5<br>f <sub>OSC</sub> / 2e6<br>0.5<br>f <sub>OSC</sub> / 2000<br>4096<br>8192 |                                  | μs<br>Hz<br>1<br>Hz<br>1<br>S<br>LSB<br>S<br>LSB<br>Hz<br>1<br>1 | (7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7)<br>(7)<br>(7 |

| 157<br>158<br>159<br>160                                                                       | Sensing Element Natural Frequency<br>±60g<br>±120g<br>±240g<br>±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | fgcell_X60<br>fgcell_X120<br>fgcell_X240<br>fgcell_X240<br>fgcell_X480                                                                                                                             | 12651<br>12651<br>26000<br>26000 | <br>                                                                                                                                                                                         | 13871<br>13871<br>28700<br>28700 | Hz<br>Hz<br>Hz<br>Hz                                             | (9<br>(9<br>(9<br>(9                                                         |

| 161<br>162<br>163<br>164                                                                       | Sensing Element Rolloff Frequency (-3 db)<br>±60g<br>±120g<br>±240g<br>±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | fgcell_X60<br>fgcell_X120<br>fgcell_X240<br>fgcell_X240<br>fgcell_X480                                                                                                                             | 938<br>938<br>3952<br>3952       |                                                                                                                                                                                              | 2592<br>2592<br>14370<br>14370   | Hz<br>Hz<br>Hz<br>Hz                                             | (9<br>(9<br>(9<br>(9                                                         |

| 165<br>166<br>167<br>168                                                                       | Sensing Element Damping Ratio<br>±60g<br>±120g<br>±240g<br>±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ζgcell_X60<br>ζgcell_X120<br>ζgcell_X240<br>ζgcell_X480                                                                                                                                            | 2.760<br>2.760<br>1.260<br>1.260 | <br>                                                                                                                                                                                         | 6.770<br>6.770<br>3.602<br>3.602 | <br><br>                                                         | (9<br>(9<br>(9                                                               |

| 169<br>170<br>171<br>172                                                                       | Sensing Element Delay (@100 Hz)<br>±60g<br>±120g<br>±240g<br>±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <sup>f</sup> gcell_delay_X60<br><sup>f</sup> gcell_delay_X120<br><sup>f</sup> gcell_delay_X240<br><sup>f</sup> gcell_delay_X240                                                                    | 63<br>63<br>13<br>13             | <br>                                                                                                                                                                                         | 170<br>170<br>40<br>40           | μs<br>μs<br>μs<br>μs                                             | (9<br>(9<br>(9<br>(9                                                         |

| 173                                                                                            | Package Resonance Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f <sub>Package</sub>                                                                                                                                                                               | 100                              | _                                                                                                                                                                                            |                                  | kHz                                                              | (9                                                                           |

# 2.8 Dynamic Electrical Characteristics - Supply and SPI

$V_{I} \leq (V_{CC} - V_{SS}) \leq V_{H}, T_{I} \leq T_{A} \leq T_{H}, \Delta T \leq 25$  K/min, unless otherwise specified

| #                                       | Characteristic                                                                                                                                                                                                                                                                                                                                                                                       | Symbol                                                                                                                                     | Min                   | Тур                                                                                | Max      | Units                                                                           |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------|

| 74                                      | Quiescent Current Settling Time (Power Applied to $Iq = I_{IDLE} \pm 2mA$ )                                                                                                                                                                                                                                                                                                                          | t <sub>SET</sub>                                                                                                                           | —                     | —                                                                                  | 5        | ms                                                                              |

| 75                                      | Reset Recovery Internal Delay (After internal POR)                                                                                                                                                                                                                                                                                                                                                   | t <sub>INT_INIT</sub>                                                                                                                      | —                     | 16000 / f <sub>OSC</sub>                                                           |          | s                                                                               |

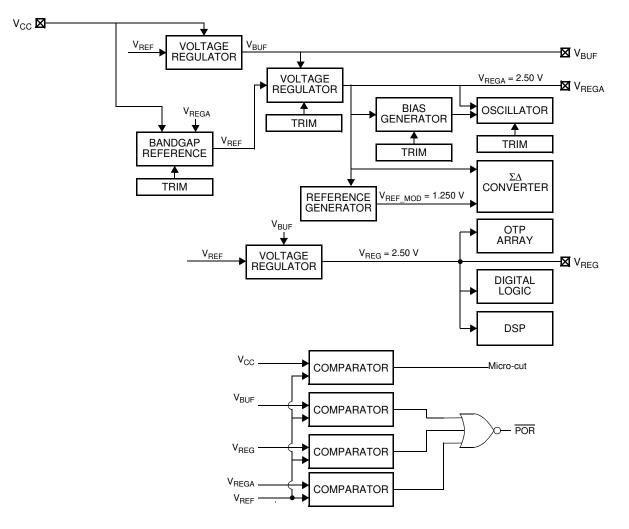

| 76<br>77<br>78                          | $\label{eq:VCC} \begin{array}{l} V_{CC} \mbox{ Micro-cut} \ (C_{BUF}=C_{REG}=C_{REGA}=1 \ \mu F) \\ Survival \ Time \ (V_{CC} \ disconnect \ without \ Reset, \ C_{BUF}=C_{REG}=C_{REGA}=700 \ nF) \\ Survival \ Time \ (V_{CC} \ disconnect \ without \ Reset, \ C_{BUF}=C_{REG}=C_{REGA}=1 \ \mu F) \\ Reset \ Time \ (V_{CC} \ disconnect \ above \ which \ Reset \ is \ guaranteed) \end{array}$ | tvcc_MICROCUTmin<br>tvcc_MICROCUT<br>tvcc_RESET                                                                                            | 30<br>50              |                                                                                    | <br>1000 | μs<br>μs<br>μs                                                                  |

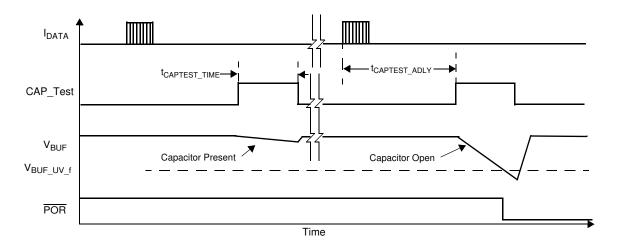

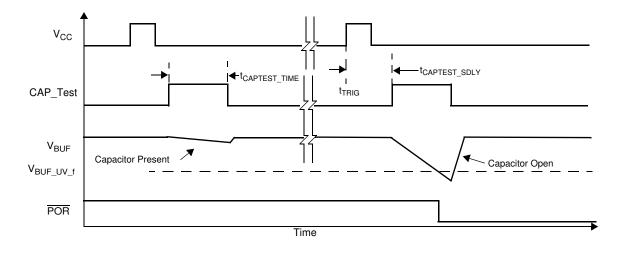

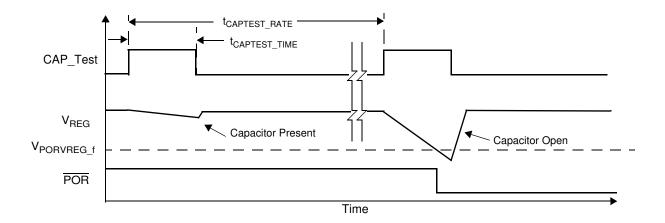

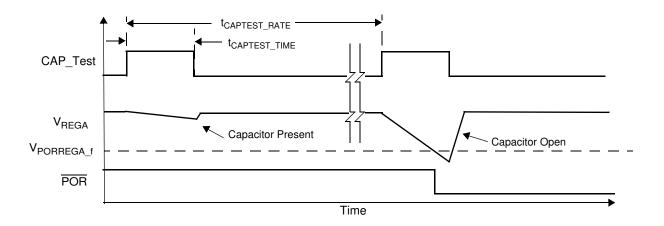

| 19<br>10<br>11<br>12                    | V <sub>BUF</sub> , Capacitor Monitor Disconnect Time (Figure 10)<br>POR to first Capacitor Test Disconnect<br>Disconnect Time (Figure 10)<br>Disconnect Delay, Asynchronous Mode (Figure 10)<br>Disconnect Delay, Synchronous Mode (Figure 11)                                                                                                                                                       | <sup>t</sup> POR_CAPTEST<br><sup>t</sup> CAPTEST_TIME<br><sup>t</sup> CAPTEST_ADLY<br><sup>t</sup> CAPTEST_SDLY                            |                       | 12000 / f <sub>OSC</sub><br>1.5<br>688 / f <sub>OSC</sub><br>72 / f <sub>OSC</sub> | 5.0<br>— | s<br>µs<br>s<br>s                                                               |