# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The Future of Analog IC Technology

## DESCRIPTION

The MP2005 is a micropower, ultra low-dropout LDO linear regulator. It has a 1.0V to 5.5V input voltage range and can regulate the output voltage from as low as 0.5V. The MP2005 can supply up to 800mA of load current with a typical dropout voltage of 90mV. It requires a bias supply (2.7V to 5.5V) separate from  $V_{IN}$  to run the internal reference and LDO drive circuitry. The output current comes directly from the input voltage supply for high efficiency regulation. The 0.5V internal reference voltage allows the output to be programmed to a wide range of voltages (0.5V to 4V).

A low bias current of 100 $\mu$ A makes the MP2005 ideal for use in battery-powered applications. The bias supply V<sub>BIAS</sub> can be directly applied from the battery while V<sub>IN</sub> is powered from the high efficiency buck regulator (or other secondary supply). This reduces output noise and the size of the decoupling capacitor.

Other features of MP2005 include thermal overload and current limit protection, stability with ultra low ESR ceramic capacitors as low as  $1\mu$ F, and fast transient response. The MP2005 is available in a 8-pin QFN (2mm x 3mm) package.

#### FEATURES

- Wide 1.0V to 5.5V Input Voltage Range

- Stable with 1µF Ceramic Capacitor

- Ultra-Low Dropout (ULDO) voltage: 90mV@800mA

- 2% Accurate Output Voltage

- Adjustable Output Range of 0.5V to 4V

- High PSRR

- o 65dB at 1KHz

- o 48dB at 1MHz

- Better Than 0.0005%/mA Load Regulation

- Stable With Low-ESR Output Capacitors

- Low 100µA Ground Current

- Internal Thermal Protection

- Current Limit Protection

- 1µA Typical Quiescent Current at Shutdown

#### **APPLICATIONS**

- Low Current Regulators

- Low Power Handheld Devices

- Battery Powered Systems

- Cellular Phones

- Portable Electronic Equipment

- Post Regulation for Switching Power Supplies

- Power Supplies

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

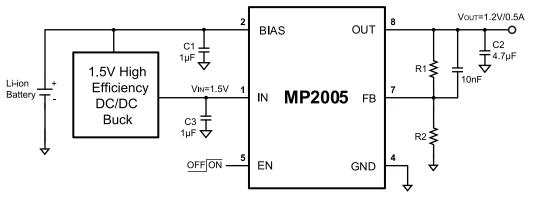

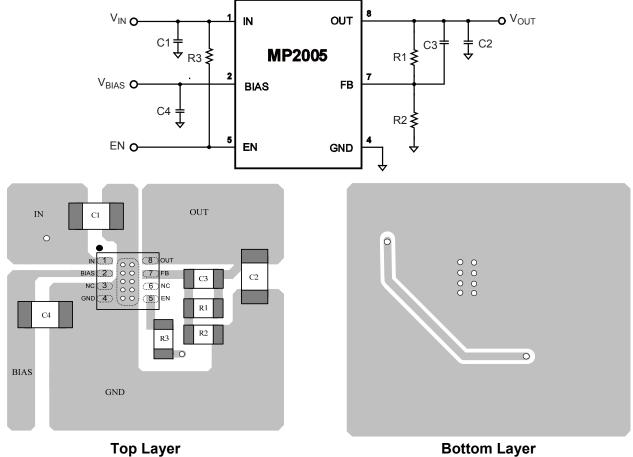

## TYPICAL APPLICATION

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2017 MPS. All Rights Reserved.

#### **ORDERING INFORMATION**

| Part Number* | Package           | Top Marking |

|--------------|-------------------|-------------|

| MP2005DD     | QFN-8 (2mm x 3mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP2005DD–Z) For RoHS compliant packaging, add suffix –LF (e.g. MP2005DD–LF–Z)

### **TOP MARKING**

N3YW LLL

N3: product code of MP2005DD; Y: year code; W: week code: LLL: lot number;

#### PACKAGE REFERENCE

#### ABSOLUTE MAXIMUM RATINGS (1)

|                                            | I KATINGS                               |

|--------------------------------------------|-----------------------------------------|

| V <sub>BIAS</sub> , V <sub>IN</sub> to GND | –0.3V to +6V                            |

| FB, EN to GND                              | –0.3V to 6V                             |

| OUT                                        |                                         |

| Continuous Power Dissipation               | (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                            | 2.3W                                    |

| Junction Temperature                       | 150°C                                   |

| Lead Temperature                           | 260°C                                   |

| Storage Temperature                        | –65°C to +150°C                         |

| Recommended Operating                      | Conditions <sup>(3)</sup>               |

| Input Voltage V <sub>IN</sub>              | 1.0V to 5.5V                            |

| Input Voltage V <sub>BIAS</sub>            | 2.7V to 5.5V                            |

| Output Voltage                             | 0.5V to 4.0V                            |

| Load Current                               | .800mA Maximum                          |

| Operating Temperature                      | –40°C to +85°C                          |

## Thermal Resistance $^{(4)}$ $\theta_{JA}$ $\theta_{JC}$

QFN-8 (2mm x 3mm)..... 55 ..... 12... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 1.5V$ ,  $V_{BIAS} = 3.6V$ ,  $V_{OUT} = 1.2V$ , C2 =4.7 $\mu$ F, C3 = 1 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                           | Symbol | Condition                                                                                                | Min   | Тур    | Max   | Units |

|-------------------------------------|--------|----------------------------------------------------------------------------------------------------------|-------|--------|-------|-------|

| V <sub>IN</sub> Operating Voltage   |        |                                                                                                          | 1.0   |        | 5.5   | V     |

| V <sub>BIAS</sub> Operating Voltage |        |                                                                                                          | 2.7   |        | 5.5   | V     |

| V <sub>IN</sub> Operating Current   |        | V <sub>OUT</sub> = 1.2V                                                                                  |       | 4      | 10    | μA    |

| V <sub>BIAS</sub> Operating Current |        | I <sub>OUT</sub> = 10μA, V <sub>OUT</sub> = 1.2V                                                         |       | 100    | 150   | μA    |

|                                     |        | I <sub>OUT</sub> = 1mA to 800mA                                                                          | 0.490 | 0.500  | 0.510 | - V   |

| FB Regulation Voltage               |        | $-40^{\circ}C \le T_A \le +85^{\circ}C, V_{OUT}$ = 0.5 V                                                 | 0.487 | 0.500  | 0.512 |       |

| Dropout Voltage                     |        | $I_{OUT}$ = 800mA, $V_{BIAS}$ = 3.6V                                                                     |       | 70     | 90    | mV    |

| V <sub>IN</sub> Line Regulation     |        | $I_{OUT} = 1mA,$<br>$V_{IN} = 1.0V \text{ to } 5.5V$<br>$V_{BIAS} = 3.6V V_{OUT} = 0.5V$                 |       | 0.002  |       | %/V   |

| V <sub>BIAS</sub> Line Regulation   |        | $I_{OUT}$ = 100mA,<br>V <sub>BIAS</sub> = 2.7V to 5.5V V <sub>OUT</sub> = 0.5V<br>V <sub>IN</sub> = 1.5V |       | 0.04   |       | %/V   |

| Load Regulation                     |        | I <sub>OUT</sub> = 1mA to 800mA                                                                          |       | 0.0005 |       | %/mA  |

| PSRR                                |        | V <sub>IN</sub> > V <sub>OUT</sub> + 0.5V, C2 = 10µF,<br>V <sub>IN</sub> (AC) = 100mV, f = 1MHz          |       | 48     |       | dB    |

| EN Input High Voltage               |        |                                                                                                          | 1.3   |        |       | V     |

| EN Input Low Voltage                |        |                                                                                                          |       |        | 0.8   | V     |

| EN Input Bias Current               |        | V <sub>EN</sub> = 1.2V                                                                                   | -1    |        | +1    | μA    |

| Thermal Protection                  |        |                                                                                                          |       | 155    |       | °C    |

| Thermal Protection Hysteresis       |        |                                                                                                          |       | 30     |       | °C    |

| GND Current                         |        | $I_{LOAD} = 500 \text{mA}$                                                                               |       | 110    | 150   | μA    |

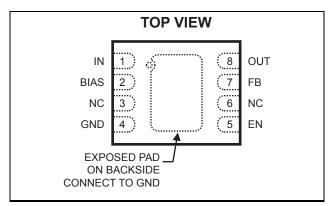

## **PIN FUNCTIONS**

| Pin # | Name | Description                                                                                                                   |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------|

| 1     | IN   | Power Source Input. Bypass IN to GND with a 1µF or greater capacitor.                                                         |

| 2     | BIAS | Bias Voltage. Bypass to GND with a 1µF capacitor (or greater)                                                                 |

| 3, 6  | NC   | No Connect.                                                                                                                   |

| 4     | GND  | Ground.                                                                                                                       |

| 5     | EN   | Enable Input. Drive EN high to turn on the MP2005, drive EN low to turn it off. For automatic startup, connect EN to Bias.    |

| 7     | FB   | Feedback Input. Connect a resistive voltage divider from OUT to FB to set the output voltage. OUT feedback threshold is 0.5V. |

| 8     | OUT  | Regulator Output. OUT is the output of the linear regulator. Bypass OUT to GND with a $1\mu$ F or greater capacitor.          |

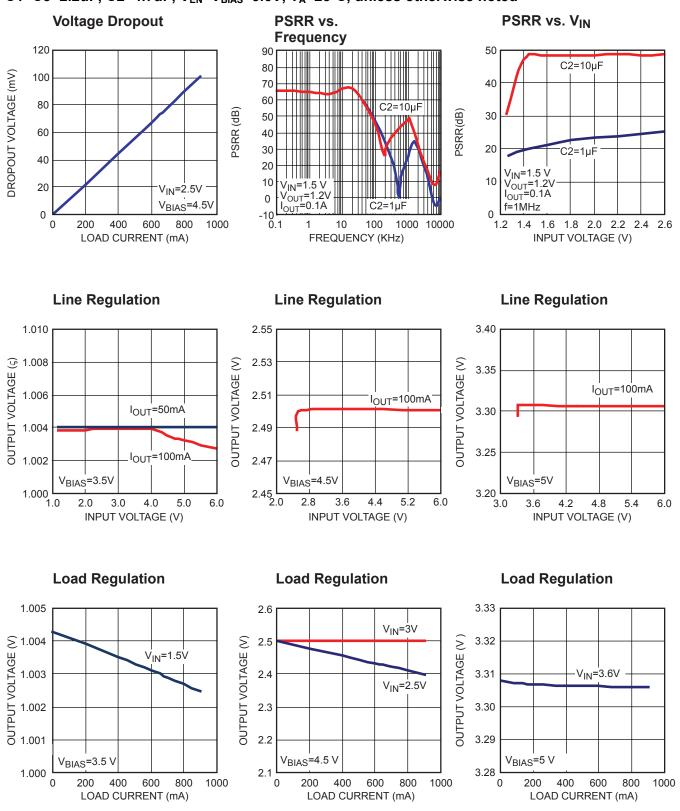

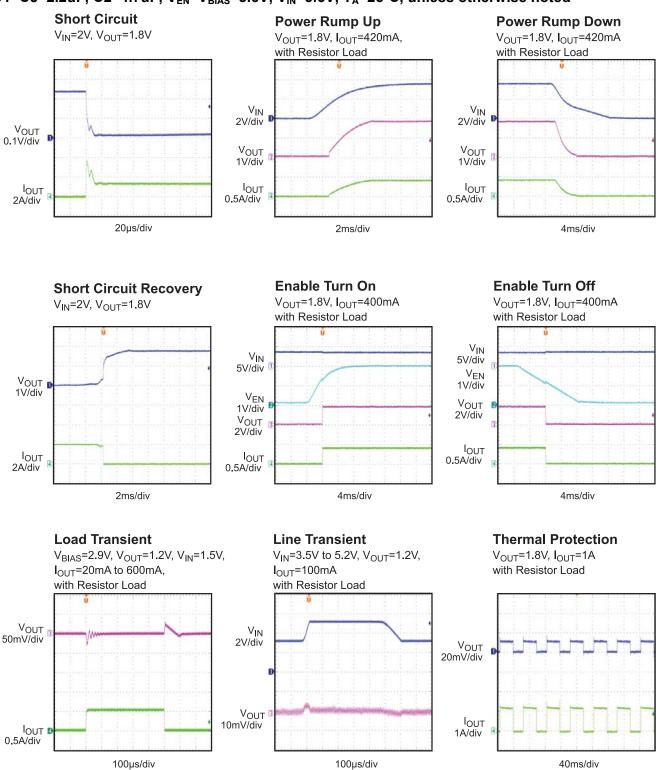

#### TYPICAL PERFORMANCE CHARACTERISTICS

C1=C3=2.2uF, C2=4.7uF, V<sub>EN</sub>=V<sub>BIAS</sub>=3.6V, T<sub>A</sub>=25°C, unless otherwise noted

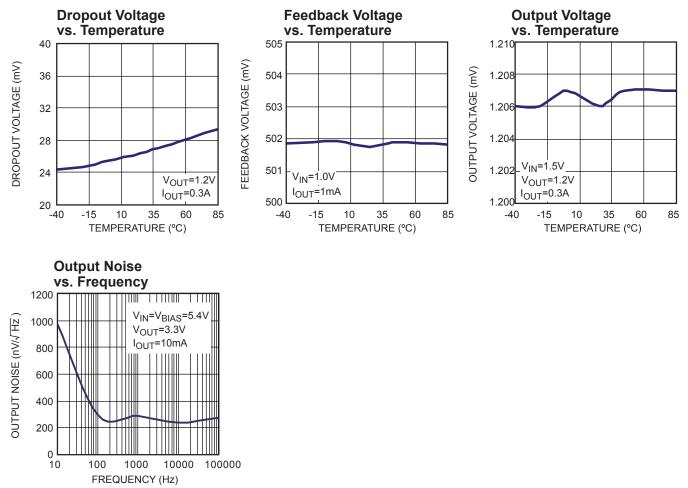

#### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

C1=C3=2.2uF, C2=4.7uF,  $V_{EN}$ =V<sub>BIAS</sub>=3.6V, T<sub>A</sub>=25°C, unless otherwise noted

#### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

C1=C3=2.2uF, C2=4.7uF, V<sub>EN</sub>=V<sub>BIAS</sub>=3.6V, V<sub>IN</sub>=3.6V, T<sub>A</sub>=25°C, unless otherwise noted

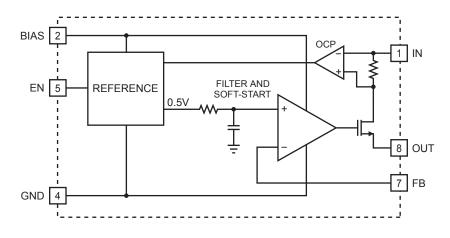

### **BLOCK DIAGRAM**

Figure 1—Block Diagram of Super Low Dropout Regulator

#### **APPLICATION INFORMATION**

#### Setting the Output Voltage

The MP2005 has an adjustable output voltage, set by using a resistive voltage divider from the output voltage to FB pin. The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \frac{R2}{R1 + R2}$$

Where  $V_{FB}$  is the feedback threshold voltage ( $V_{FB} = 0.5V$ ), and  $V_{OUT}$  is the output voltage.

Thus the output voltage is:

$$V_{OUT} = 0.5 \times \frac{R1 + R2}{R2}$$

R2 can be as high as  $100k\Omega$ , but a typical value is  $10k\Omega$ . Using that value, R1 is determined by:

$$R1 = R2 \times \left(\frac{V_{OUT} - V_{FB}}{V_{FB}}\right)$$

For example, for a 1.8V output voltage, R2 is  $10k\Omega$ , and R1 is  $26k\Omega$ . You can select a standard  $26k\Omega$  (±1%) resistor for R1.

The following table lists the selected R1 for various output voltages.

Table 1—Adjustable Output Voltages R1 Values

| V <sub>OUT</sub> (V) | R1 (kΩ) | R2 (kΩ) |

|----------------------|---------|---------|

| 1.25                 | 15      |         |

| 1.5                  | 20      |         |

| 1.8                  | 26      |         |

| 2                    | 30      |         |

| 2.5                  | 40      | 10      |

| 2.8                  | 46      |         |

| 3                    | 50      |         |

| 3.3                  | 56      |         |

| 4                    | 70      |         |

#### **Bias Input**

The bias input is designed for low drop application. The bias pin must be at least 2.7V, and at least 1.5V higher than the output. If  $V_{IN}$  supply voltage meets these requirements, the bias pin can be tied to  $V_{IN}$ .

#### **Feed Forward Capacitor**

Feed forward capacitor which a ceramic type capacitor parallels with R1 affects loop stability. According to actual application, MP2005 improves load transient performance by add a suitable feed forward capacitor.

#### **PCB Layout Guide**

PCB layout is very important to achieve good regulation, ripple rejection, transient response and thermal performance. It is highly recommended to duplicate EVB layout for optimum performance.

If change is necessary, please follow these guidelines and take Figure 2 for reference.

- Input and output bypass ceramic capacitors are suggested to be put close to the IN Pin and OUT 1) Pin respectively.

- Ensure all feedback connections are short and direct. Place the feedback resistors and 2) compensation components as close to the chip as possible.

- 3) Connect IN, OUT and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

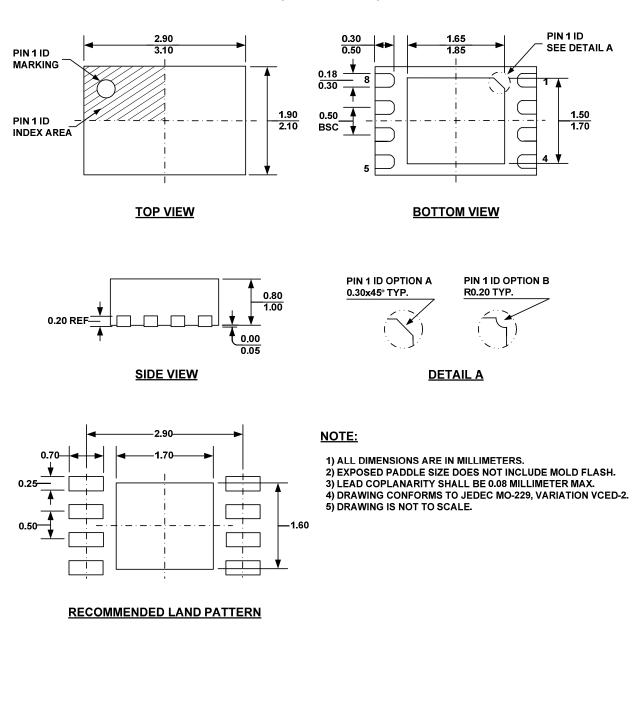

## PACKAGE INFORMATION

QFN8 (2mm x 3mm)

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.