Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MP62550/MP62551

Precision 60mA-1.7A Programmable Current-Limited Power Distribution Switch

#### DESCRIPTION

MP62550/MP62551 Power Distribution Switch is designed for precision current limiting and provides up to 1.5A continuous output current. It offers programmable current limit between 60mA and 1.7A (typ) with  $\pm 10\%$  accuracy by an external resistor. The switch includes an  $88m\Omega$  N-channel Power MOSFET and operates from 2.5V to 5.5V input voltage.

The device has built-in protection for both over current and increased thermal stress. For over current, the device will limit the current by changing to a constant current mode. It will shutdown when its internal temperature reaches unsafe levels and recover once the device temperature reduces approx 10°C.

It provides built-in soft-start which controls the rise and fall times of the output voltage to limit the initial inrush current and voltage surges.

The reverse-voltage protection feature turns off the MOSFET to protect the device.

The FLAG output will report a fail mode (low level) when over current or over temperature is encountered. The FLAG will not change state when the input UVLO is triggered.

The MP62550/MP62551 is available in space saving 6-pin TQFN 2x2mm package and TSOT23-6 package.

#### **FEATURES**

- Up to 1.5A Continuous Output Current

- ±10% Current-Limit Accuracy

- Adjustable Current-Limit, 60mA -1700mA (typ)

- Fast Over-current Response 2µs (typ)

- 2.5V to 5.5V Supply Range

- 88mΩ MOSFET (TQFN Package)

- 1.5µA Maximum Standby Supply Current

- Reverse Input-Output Voltage Protection

- Built-in Soft-Start

- Thermal-Shutdown Protection

- Automatic-on after Fault Removed

- Under-Voltage Lockout

- Deglitched Fault Report

- FLAG won't Change State at Input UVLO Transition

- Bidirectional Fault Deglitch Time

- Active Low & Active High Options

#### **APPLICATIONS**

- Smart Phone and PDA

- Portable GPS Device

- Notebook PC

- Set-top-box

- Telecom and Network Systems

- PC Card Hot Swap

- USB Power Distribution

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page.

"MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

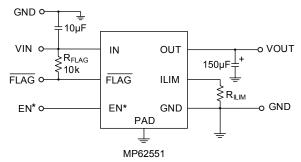

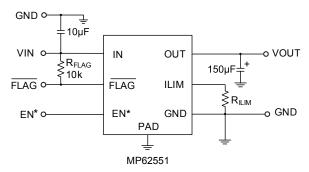

#### TYPICAL APPLICATION

(\*EN active low for MP62550)

#### ORDERING INFORMATION

| Part Number* | Enable      | Switch  | Maximum<br>Continuous Load<br>Current | Package       | Top Marking | Free Air<br>Temperature (T <sub>A</sub> ) |

|--------------|-------------|---------|---------------------------------------|---------------|-------------|-------------------------------------------|

| MP62550DGT   | Active Low  | Single  | 1.5A                                  | TQFN6 (2x2mm) | 5Y          | -40°C to +85°C                            |

| MP62551DGT   | Active High | Olligio | 1.0/ (                                | TQFN6 (2x2mm) | AJ          | -40 0 10 100 0                            |

| MP62550DJ    | Active Low  | Single  | 1.5A                                  | TSOT23-6      | 5Y          | -40°C to +85°C                            |

| MP62551DJ    | Active High | Single  | 1.5/4                                 | TSOT23-6      | AAN         | - <del>-</del> 0 0 10 103 0               |

\* For Tape & Reel, add suffix –Z (e.g. MP62551DGT–Z). For RoHS compliant packaging, add suffix –LF (e.g. MP62551DGT–LF–Z)

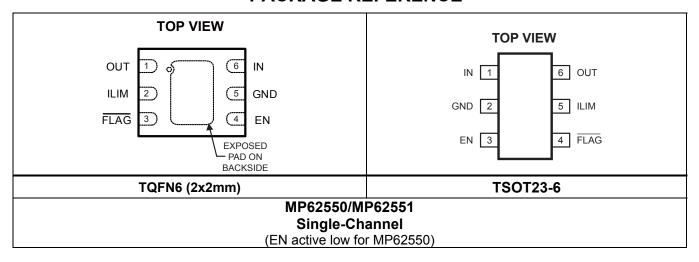

#### PACKAGE REFERENCE

# **ABSOLUTE MAXIMUM RATINGS (1)**

| IN to GND                                        | 0.3V to +6.5V                 |

|--------------------------------------------------|-------------------------------|

| ILIM, EN, FLAG, OUT to GND.                      | $12.4k\Omega$ to $210k\Omega$ |

| Continuous Power Dissipation TQFN(2x2)-6TSOT23-6 | 1.56W                         |

| Lead Temperature Storage Temperature             | 260°C                         |

| Maximum Junction Temp. (T <sub>J</sub> )         |                               |

| Thermal Resistance (3) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |       |

|------------------------|-------------------------|-------------------------|-------|

| TQFN6 (2x2mm)          | 80                      | 16                      | .°C/W |

| TSOT23-6               | 220                     | 110.                    | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the

maximum junction temperature  $T_J(MAX)$ , the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX)=(T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

3) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$T_A = +25^{\circ}C, \ 2.5V \leq V_{IN} \leq 5.5V, \ 12.4k\Omega \leq R_{ILIM} \leq 210k\Omega, \ R_{FLAG} = 10k\Omega, \ unless \ otherwise \ noted.$

| Parameters                                                       | Symbol                | Test Conditions                                                 |                                     | Min  | Тур  | Max  | Units |

|------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------|-------------------------------------|------|------|------|-------|

| IN Voltage Range                                                 | $V_{IN}$              |                                                                 |                                     | 2.5  |      | 5.5  | V     |

| FET On_Resistance                                                | R <sub>DS(on)</sub>   | V <sub>IN</sub> =5V,<br>I <sub>OUT</sub> =100mA                 | TQFN2x2-6                           |      | 88   | 135  | mΩ    |

|                                                                  |                       | -40°C≤T <sub>A</sub> ≤+85°C                                     | TSOT23-6                            |      | 100  | 135  |       |

| Supply Current                                                   | I <sub>IN_ON</sub>    | Device Enabled, V <sub>OUT</sub> =float, V <sub>IN</sub> =5.5V  |                                     |      | 125  | 145  | μΑ    |

| Shutdown Current                                                 | I <sub>IN_OFF</sub>   | Device Disabled, V <sub>OUT</sub> =float, V <sub>IN</sub> =5.5V |                                     |      |      | 1.5  | μΑ    |

| Reverse Leakage<br>Current                                       | I <sub>REV</sub>      | V <sub>IN</sub> =0V, V <sub>OUT</sub> =5.5V                     |                                     |      | 0.01 | 1    | μΑ    |

|                                                                  |                       | $R_{ILIM}$ =13k $\Omega$                                        |                                     | 1530 | 1700 | 1870 | mA    |

|                                                                  |                       | $R_{ILIM}$ =20k $\Omega$                                        | -40°C≤T <sub>A</sub> ≤85°C,         | 960  | 1190 | 1360 |       |

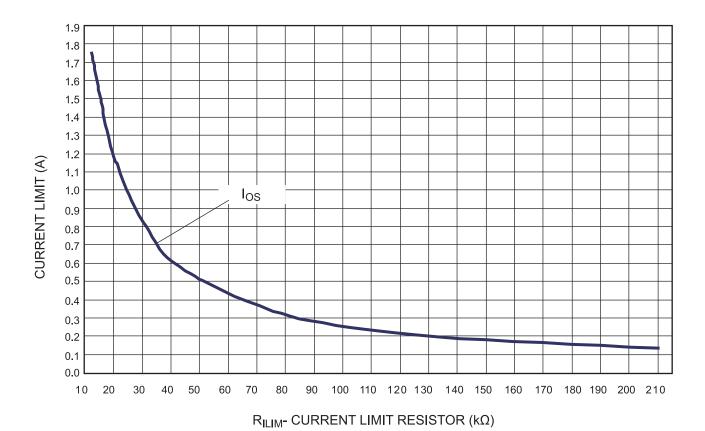

| Current Limit<br>(See Figure 2)                                  | $I_{OS}$              | $R_{ILIM}$ =49.9k $\Omega$                                      | OUT connected                       | 450  | 510  | 570  |       |

| ,                                                                |                       | R <sub>ILIM</sub> =210kΩ                                        | to GND                              | 105  | 135  | 166  |       |

|                                                                  |                       | ILIM Shorted to IN                                              | 1                                   | 45   | 60   | 85   |       |

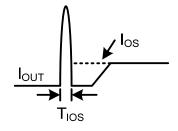

| Short Current Response Time                                      | T <sub>IOS</sub>      | V <sub>IN</sub> =5V (See Figure 2)                              |                                     |      | 2    |      | μs    |

| Under-voltage Lockout                                            | $INUV_{VTH}$          | V <sub>IN</sub> Rising Edge                                     |                                     |      | 2.25 | 2.45 | V     |

| Under-voltage Hysteresis                                         | $INUV_{HYS}$          |                                                                 |                                     |      | 130  |      | mV    |

| EN Input Logic High<br>Voltage                                   | $VIH_{EN}$            |                                                                 |                                     | 1.1  |      |      | V     |

| EN Input Logic Low Voltage                                       | VIL <sub>EN</sub>     |                                                                 |                                     |      |      | 0.66 | V     |

| EN Input Leakage<br>Current                                      | I <sub>EN</sub>       | V <sub>EN</sub> =0-5.5V                                         |                                     | -0.5 |      | 0.5  | μΑ    |

| FLAG Output Logic Low<br>Voltage                                 | $V_{OL}$              | I <sub>FLAG</sub> =1mA                                          |                                     |      |      | 180  | mV    |

| FLAG Output High<br>Leakage Current                              | I <sub>FLAG_OFF</sub> | V <sub>FLAG</sub> =5.5V                                         |                                     |      |      | 1    | μΑ    |

| FLAG Deglitch Time                                               | T <sub>FLAG_DEG</sub> | •                                                               | assertion or de-<br>to over-current | 3.5  | 7.5  | 10   | ms    |

| Reverse-Voltage<br>Comparator Trip Point<br>$(V_{OUT} - V_{IN})$ | $V_{R\_TRIP}$         |                                                                 | ,                                   |      | 135  |      | mV    |

| Time from Reverse-<br>Voltage to MOSFET Turn<br>Off              | $T_{R_RES}$           | V <sub>IN</sub> =5V                                             |                                     |      | 5    |      | ms    |

ELECTRICAL CHARACTERISTICS  $^{(4)}$  (continued)  $T_A$ =+25°C, 2.5V $\leq$ V $_{IN}$  $\leq$ 5.5V, 12.4k $\Omega$  $\leq$ R $_{ILIM}$  $\leq$ 210k $\Omega$ ,  $R_{FLAG}$ =10k $\Omega$ , unless otherwise noted.

| Parameters                                             | Symbol                          | Test Conditions                                  |                       | Min | Тур  | Max    | Units |

|--------------------------------------------------------|---------------------------------|--------------------------------------------------|-----------------------|-----|------|--------|-------|

| Thermal Shutdown Threshold                             | $T_J$                           |                                                  |                       | 155 |      |        | °C    |

| Thermal Shutdown Threshold in Current- Limit Condition | $T_{J\_CL}$                     |                                                  |                       | 135 |      |        | °C    |

| Thermal Shutdown<br>Hysteresis                         | T <sub>J_HYS</sub>              |                                                  |                       |     | 10   |        | °C    |

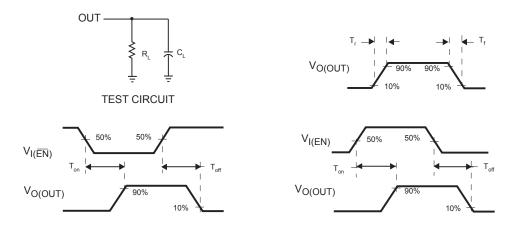

| V <sub>OUT</sub> Rising Time                           | T <sub>r</sub> <sup>(5)</sup>   | $R_{LOAD}$ =100 $\Omega$ , $C_{LOAD}$ =1 $\mu$ F | V <sub>IN</sub> =5.5V |     | 0.5  | 1.5 ms | ms    |

| V <sub>OUT</sub> Kising Time                           |                                 |                                                  | V <sub>IN</sub> =2.5V |     | 0.75 |        | 1113  |

| V <sub>OUT</sub> Falling Time                          | T <sub>f</sub> <sup>(6)</sup>   | R <sub>LOAD</sub> =100Ω,                         | V <sub>IN</sub> =5.5V | 0.1 |      | 0.4    |       |

| V <sub>OUT</sub> Failing Time                          | <b>I</b> f                      | C <sub>LOAD</sub> =1µF                           | V <sub>IN</sub> =2.5V | 0.1 |      | 0.4    |       |

| Turn On Time                                           | T <sub>on</sub> <sup>(7)</sup>  | $R_{LOAD}$ =100Ω, $C_{LOAD}$ =100μF              |                       |     |      | 3      | me    |

| Turn Off Time                                          | T <sub>off</sub> <sup>(8)</sup> |                                                  |                       |     |      | 30     | ms    |

#### Notes:

- 4) Production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

- 5) Measured from 10% to 90% output signal.

- 6) Measured from 90% to 10% output signal.7) Measured from 50% EN signal to 90% output signal.

- 8) Measured from 50% EN signal to 10% output signal.

# **PIN FUNCTIONS**

| TQFN6 <sup>(9)</sup><br>Pin # | TSOT23<br>Pin # | Name | I/O | Description                                                                                                             |

|-------------------------------|-----------------|------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 1                             | 6               | OUT  | 0   | Switch output. The $V_{\text{OUT}}$ of the internal power FET and output terminal of the IC.                            |

| 2                             | 5               | ILIM | 0   | External resistor used to set current-limit, recommended $12.4k\Omega \le R_{\text{ILIM}} \le 210k\Omega$ .             |

| 3                             | 4               | FLAG | 0   | Fault status. Logic Low when over-current, over-temperature. Open Drain.                                                |

| 4                             | 3               | EN   | I   | Enable input. Active Low: (MP62550), Active High: (MP62551).                                                            |

| 5                             | 2               | GND  |     | Ground. Externally connected to PAD.                                                                                    |

| 6                             | 1               | IN   | I   | Input Voltage. Accepts 2.5V to 5.5V input.                                                                              |

| PAD                           |                 | PAD  |     | Internally connected to GND. Used to heat-sink the part to the circuit board traces. Connect PAD to GND pin externally. |

#### Notes

# PARAMETER MEASUREMENT INFORMATION

**VOLTAGE WAVEFORMS**

Figure 1—Definition of T<sub>r</sub>, T<sub>f</sub>, T<sub>on</sub>, and T<sub>off</sub>

Figure 2—Short Circuit Response Time

<sup>9)</sup> The part has thermal pad on the backside and the pad is GND.

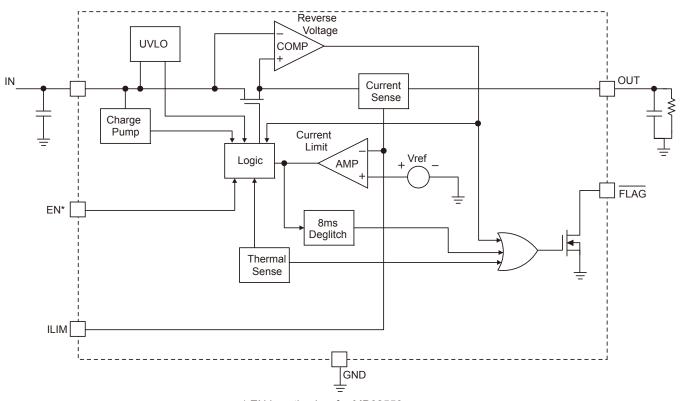

# **BLOCK DIAGRAM**

\* EN is active low for MP62550

Figure 3—Function Block Diagram

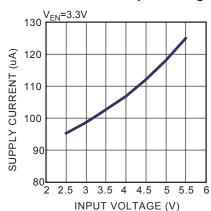

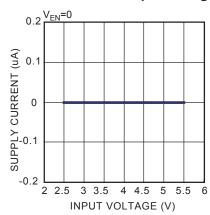

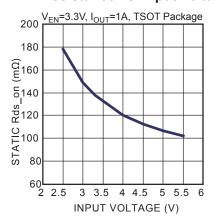

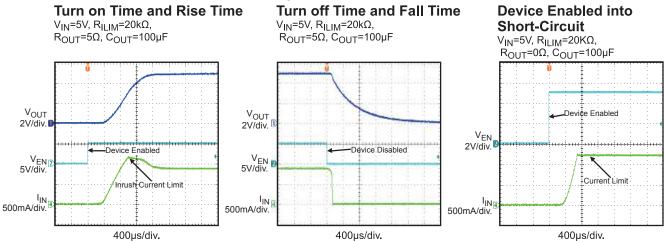

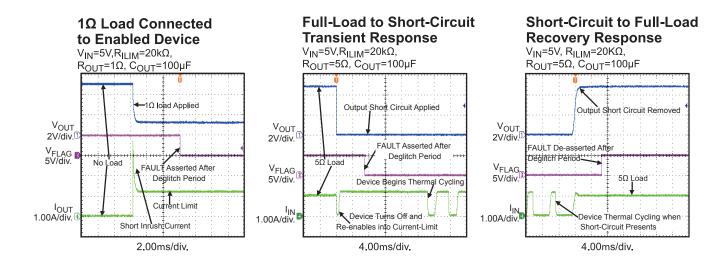

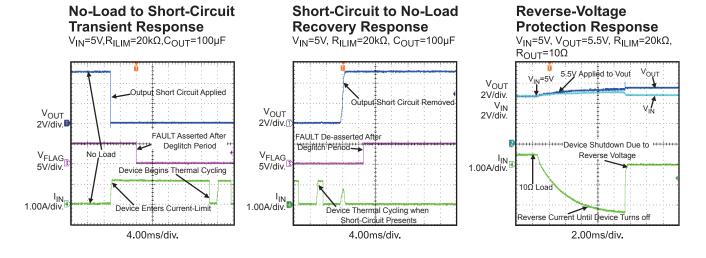

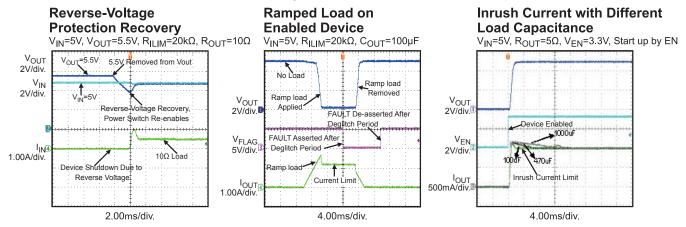

#### TYPICAL PERFORMANCE CHARACTERISTICS

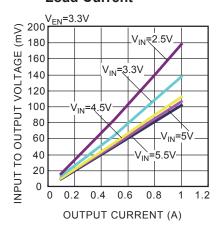

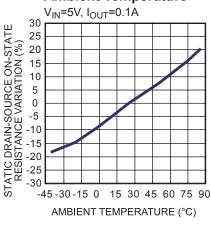

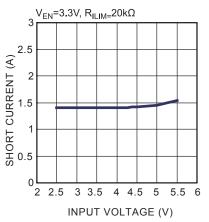

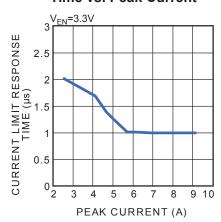

$V_{IN}$ =5V,  $R_{ILIM}$ =20k $\Omega$ ,  $R_{FLAG}$ =10k $\Omega$ ,  $C_{OUT}$ =100 $\mu$ F,  $T_A$ =+25°C, unless otherwise noted.

**Supply Current, Output Enabled vs. Input Voltage**

**Supply Current, Output Disabled vs. Input Voltage**

Static Drain-Source On-State Resistance vs. Input Voltage

Input to Output Voltage vs. Load Current

Static Drain-Source On-State Resistance Variation vs. Ambient Temperature

Current Limit vs. Input Voltage

# Short Circuit Response Time vs. Peak Current

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$ =5V,  $R_{\text{ILIM}}$ =20k $\Omega$ ,  $R_{\text{FLAG}}$ =10k $\Omega$ ,  $C_{\text{OUT}}$ =100 $\mu$ F,  $T_{\text{A}}$ =+25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}\text{=}5V\text{, }R_{\text{ILIM}}\text{=}20\text{k}\Omega\text{, }R_{\text{FLAG}}\text{=}10\text{k}\Omega\text{, }C_{\text{OUT}}\text{=}100\mu\text{F, }T_{\text{A}}\text{=}+25^{\circ}\text{C, unless otherwise noted.}$

#### **DETAILED DESCRIPTION**

The MP62550/MP62551 is a precision current-limit power distribution switch which can provide up to 1.5A continuous output current. It allows the user to program the current-limit between 60mA and 1.7A (typ) with ±10% accuracy via an external resistor connected between ILIM and GND pins.

The switch includes an N-channel power MOSFET and an internal charge pump to generate the gate driver voltage which is higher than input. The charge pump can work from input as low as 2.5V.

The device has built-in protection for both over current and increased thermal stress. For over current, the device will limit the current by changing to a constant current mode. It will shutdown when its internal temperature reaches unsafe levels and recover once the device temperature reduces approx 10°C.

It provides built-in soft-start which controls the rise and fall times of the output voltage to limit the initial inrush current and voltage surges.

The reverse-voltage protection feature turns off the MOSFET to protect the device.

The FLAG output will report a fail mode (low level) when over current or over temperature is encountered. The FLAG will not change state when the input UVLO is triggered.

#### **Over Current**

MP62550/MP62551 switches into to a constant-current mode when responding to over-current conditions. It ramps the output current to current limit value  $I_{OS}$  and reduces the output voltage accordingly. MP62550/MP62551 will be thermal cycles only if the over current condition stays long enough to trigger thermal protection.

Trigger over current protection for different overload conditions occurring in applications:

- The output has been shorted or overloaded before the device is enabled or input applied. MP62550/MP62551 detects the short or overload and switches into constant-current mode immediately.

- 2) A short or an overload occurs after the device is enabled. The device responds to the over-

current condition within time  $T_{\rm IOS}$ . The current sense amplifier is overdriven, so high current may flow during this period of time and the internal current-limit MOSFET is disabled momentarily before the current-limit circuit can react. Then the current-sense amplifier recovers switches into constant-current mode. Similar to the previous case, the MP62550/MP62551 will limit the current to  $I_{\rm OS}$  until the overload condition is removed or the device entering thermal cycle.

3) Output current has been gradually increased beyond the recommended operating current. The load current rises until the current-limit threshold is reached or until the thermal limit of the device is exceeded. The MP62550/MP62551 is capable of delivering current up to the current-limit without damaging the device.

#### **Reverse-Voltage Protection**

To prevent damage the device on the input side of MP62550/MP62551, the N-channel MOSFET will be turned off immediately whenever the output voltage exceeds the input voltage by 135mV (typ). There is an internal comparator which compares the voltage difference betweens drain and source of N-channel MOSFET. The reverse voltage protection circuit only activates when R<sub>DS(on)</sub> x I<sub>Reverse</sub>>135mV, that means there must be a temporary large reverse current from output to input that can trigger the reversevoltage protection. After the comparator is triggered, the internal driver circuit starts to discharge the gate voltage via a constant current. It needs several milliseconds to fully turn off the N-channel MOSFET.

This protection could prevent significant current sinking into the input side.

The MP62550/MP62551 exist the protection mode and enter to normal state once the reverse-voltage condition is removed. No need to recycle the input power or enable logic.

There is no reverse current flow through the switch at the condition of 0V input and 5.5V output whatever the enable is high or low.

#### Flag Response

The FLAG pin is an open drain configuration. When over current or over temperature is encountered, FLAG will report a fail mode (low level).

For over current, 7.5ms deglitch time-out is needed. This is used to ensure that no false fault signal is reported. This internal deglitch circuit eliminates the need for components.

For over temperature, the FLAG pin is not deglitched.

The FLAG will not change state when the input UVLO is triggered.

#### **Under-voltage Lockout (UVLO)**

This circuit is used to monitor the input voltage to ensure that the MP62550/MP62551 is operating correctly. This UVLO circuit also ensures that there is no operation until the input voltage reaches the minimum spec. Built-in 130mV hysteresis prevents unwanted on/off power cycling due to input voltage drop from large current surges.

#### **Enable**

The logic pin disables the chip to reduce the supply current. Enable high activate the MP62551 while enable low activate the MP62550. The device will operate once the enable signal reaches the appropriate level. There is no hysteresis for enable pin. The input is compatible with both COMS and TTL.

#### **Thermal Protection**

The purpose of thermal protection is to prevent damage in the IC by allowing exceptive current to flow and heat the junction. The die temperature is internally monitored by two independent thermal sensing circuits until the thermal limit is reached. The first thermal sensor turns off the power switch when the die temperature exceeds 135°C (min) and the part is in current limit. The second thermal sensor turns off the power-switch when the die temperature exceeds 155°C (min) regardless of whether the switch is in current limit. Both two thermal sensors have built-in hysteresis. It will turn on the switch once it is cooled down 10°C approximately. MP62550/MP62551 continues to cycle off and on until the fault is removed.

#### **APPLICATION INFORMATION**

#### **Power-Supply Considerations**

Over 10µF capacitor between IN and GND is recommended. This precaution reduces power-supply transients that may cause ringing on the input and improves the immunity of the device to short-circuit transients.

In order to achieve smaller output load transient ripple, placing a high-value electrolytic capacitor on the output pin is recommended when the load is heavy.

A 0.01µF to 0.1µF ceramic bypassing capacitor is recommended to improve the immunity of the device to transient conditions and noise.

\* EN is active low for MP62550

#### Figure 4—Application Circuit

### **Programming the Current-Limit**

The current-limit is programmed via an external resistor from ILIM to GND. The recommended 1% resistor range of  $R_{\text{ILIM}}$  is  $12.4 \text{k}\Omega \leq R_{\text{ILIM}} \leq 210 \text{k}\Omega$ . The ILIM pin can be connected to IN to set the current-limit at its minimum level of 60mA (typ).

It's important to consider the tolerance of current limit when selecting a value for R<sub>ILIM</sub>. Some applications require that the minimum current limit is above a certain current level, while some applications require the maximum current limit is below a certain current level.

Figure 5 can be used to calculate the current limit value for a given ILIM resistor and also can be used to select ILIM resistor for a certain current limit.

R<sub>ILIM</sub> can be selected to provide a current limit that occurs 1) above a minimum load current or 2) below a maximum load current.

To determine above a minimum current limit, find the maximum desired load current on the  $I_{os(min)}$  curve and choose a value of  $R_{ILIM}$  below this value. The resulting maximum current limit is the intersection of the selected value of  $R_{ILIM}$  and the  $I_{os(max)}$  curve.

To determine below a maximum current limit, find the maximum desired load current on the  $I_{os(max)}$  curve and choose a value of  $R_{ILIM}$  above this value. The resulting minimum current limit is the intersection of the selected value of  $R_{ILIM}$  and the  $I_{os(min)}$  curve.

In theory, the result of current limit multiplied by  $R_{\rm ILIM}$  is a constant. But the internal amplifier has offset, as a result the current limit vs  $1/R_{\rm ILIM}$  is not linear at small programming resistor range. The theoretical current limit calculation formula is given as following:

$$\begin{split} I_{OSnom}(A) &= \frac{18.818 V}{R_{ILIM}^{0.9248} k \Omega} \\ I_{OSmin}(A) &= \frac{18.489 V}{R_{ILIM}^{0.9342} k \Omega} \\ I_{OSmax}(A) &= \frac{18.229 V}{R_{ILIM}^{0.8944} k \Omega} \end{split}$$

Where:

$$12.4k\Omega \le R_{\text{ILIM}} \le 210k\Omega \, .$$

For better accuracy current limit setting, Table1 and Figure5 are highly recommended. Those curve or data are provided basing on large amount experimental test results.

Figure 5—Current-Limit vs RILIM

Table 1 shows the common  $R_{\text{ILIM}}$  vs. current limit data. 1% accuracy resistor is recommended for general applications. If a precision current limit is needed, it's better to use more tightly tolerance resistors, e.g. 0.5% or 0.1%. Resistor accuracy tolerance is not included in Table 1.

Table 1—Common R<sub>ILIM</sub> Resistor Selections (10)

| 1% Accuracy      | Current Limit (A) |

|------------------|-------------------|

| Resistor (kΩ)    | IOS               |

| 12.4             | 1.749             |

| 13               | 1.700             |

| 15               | 1.533             |

| 15.8             | 1.467             |

| 16.9             | 1.370             |

| 18.2             | 1.293             |

| 20               | 1.190             |

| 21.5             | 1.130             |

| 23.2             | 1.053             |

| 26.1             | 0.947             |

| 28.7             | 0.861             |

| 32.4             | 0.772             |

| 37.4             | 0.650             |

| 43.2             | 0.579             |

| 49.9             | 0.510             |

| 52.3             | 0.495             |

| 66.5             | 0.391             |

| 88.7             | 0.286             |

| 133              | 0.198             |

| 210              | 0.135             |

| Short ILIM to IN | 0.060             |

#### Notes:

While the maximum recommended value of  $R_{ILIM}$  is 210k $\Omega$ , there is one additional configuration that allows for a lower current limit. The ILIM pin may be connected directly to IN to provide a 60 mA (typ) current limit.

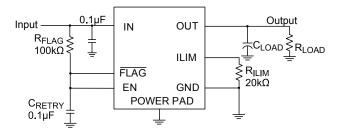

#### **Auto-Retry Function**

Figure 6 shows an auto-retry circuit implanted by an external resistor and capacitor.

Figure 6—Auto-Retry Application

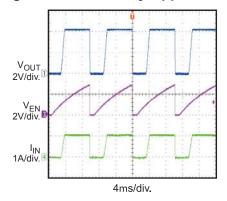

Figure 7—Auto-Retry Waveform

When over-current happens the FLAG will report a low level, EN is pulled down immediately and thus the part is shutdown.

During the moment of EN shutdown, the  $\overline{\text{FLAG}}$  changes to high impedance allowing  $C_{\text{RETRY}}$  to begin charging. After a time delay determined by the RC constant, the EN voltage reaches its turn-on threshold and re-enables the part. The part will continue to cycle in this manner until the fault condition is removed.

Above current limit vs. RILIM data is typical value only and NOT guaranteed by production. Refer to EC table for more accurate current limit setting.

### **PACKAGE INFORMATION**

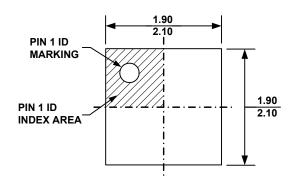

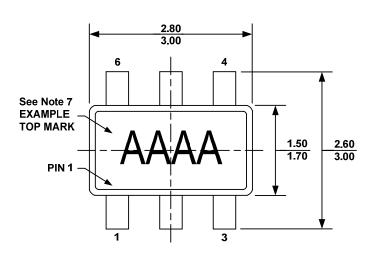

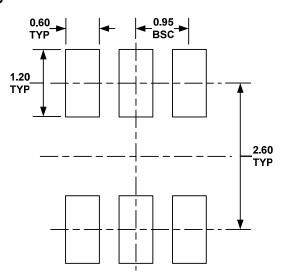

#### TQFN6 (2x2mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

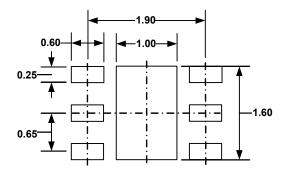

#### **RECOMMENDED LAND PATTERN**

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) JEDEC REFERENCE IS MO-229, VARIATION VCCC.

- 5) DRAWING IS NOT TO SCALE.

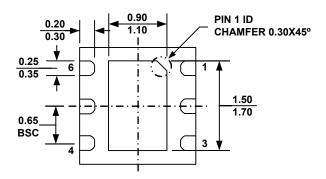

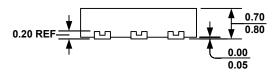

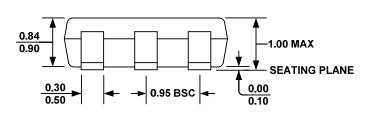

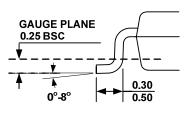

#### **TSOT23-6**

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

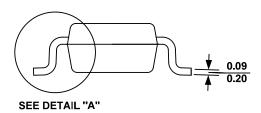

**SIDE VIEW**

DETAIL "A"

### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AB.

- 6) DRAWING IS NOT TO SCALE.

- 7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.