Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The Future of Analog IC Technology

# MP6302 Energy Storage and Release Control IC

#### **DESCRIPTION**

The MP6302 is an energy storage and release controller. It charges storage capacitor from input during normal operation. Once the storage capacitor is charged to the selected voltage, the charge is stopped, and the storage capacitor is separated from the input. The charging circuit maintains the storage voltage after the charge is completed.

The MP6302 keeps monitoring the input voltage, and releases the charge from storage capacitor to the input capacitor when the input voltage is lower than a selected release voltage. It regulates the input voltage close to release voltage for as long as possible.

The MP6302 has built-in current limit circuit during the charging of the storage capacitor. The storage and release voltage can be programmed to user desired value by external resistors.

MP6302 comes in a tiny 2mmx3mm QFN10 package and requires a minimum number of readily available standard external components.

#### **FEATURES**

- Wide 4.2V to 18V input operating range

- 2.5A dumping current from storage to Vin

- Built-in 250mA current limit for charging storage capacitor

- User programmable storage and release voltage

- Indicators for storage and input voltage

- Available in a 2mmx3mm QFN10 package

#### **APPLICATIONS**

- Hard Disk Drives

- Solid State Drives

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

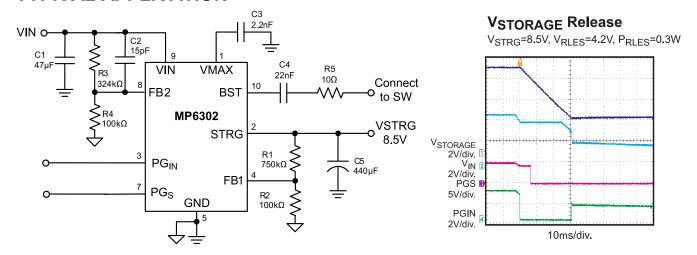

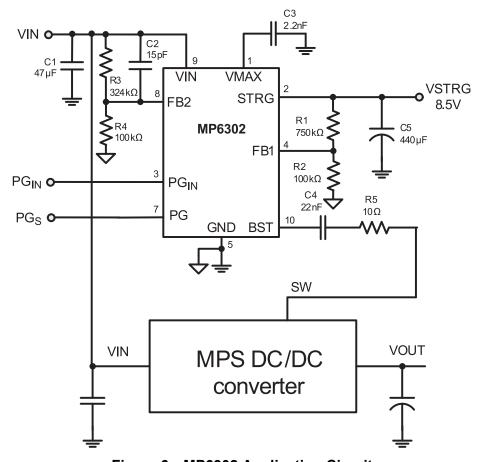

#### TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number* | Package       | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|---------------|-------------|----------------------------------------|

| MP6302DD     | QFN10 (2x3mm) | ABC         | -40°C to +85°C                         |

\* For Tape & Reel, add suffix -Z (e.g. MP6302DD-Z);

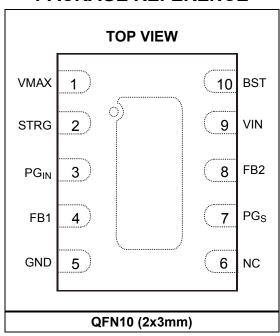

#### PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| ,                              |

|--------------------------------|

| 0.3V to 22V                    |

| 0.3V to 40V                    |

| 0.3V to 25V                    |

| 0.3V to 42V                    |

| 0.3V to 25V                    |

| 0.3V to 32V                    |

| 0.3V to 25V                    |

| 0.3V to 22V                    |

| 0.3V to 6.5V                   |

| 150°C                          |

| 260°C                          |

| $_{4}$ = +25°C) <sup>(2)</sup> |

| 1.2W                           |

| 150°C                          |

| onditions <sup>(3)</sup>       |

| 4.5V to 18V                    |

|                                |

Storage Voltage  $V_{STRG}$  ..... $V_{IN}$  to  $2xV_{IN}(32V max)$  Maximum Junction Temp  $(T_{I})$  .....+125°C

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}_{JC}$ |       |

|------------------------|-------------------------|----------------------------|-------|

| QFN10 (2x3mm)          | 70                      | . 15                       | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J (MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

7/17/2015

# **ELECTRICAL CHARACTERISTICS** (5)

$V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                                                     | Symbol                       | Condition                                                                     | Min                   | Тур                    | Max                   | Units            |

|-------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------------------|

| Input Supply Voltage Range                                                    | V <sub>IN</sub>              |                                                                               | 4.2                   |                        | 18                    | V                |

| Supply Current (Shutdown)                                                     | Is                           | V <sub>EN</sub> = 0V                                                          |                       | 1                      |                       | μΑ               |

| Supply Current (Quiescent)                                                    | Ι <sub>α</sub>               | $V_{EN}$ = 2V, $V_{FB}$ = 1.1V                                                |                       | 250                    |                       | μΑ               |

| VIN Under Voltage Lockout<br>Threshold Rising                                 | INUV <sub>Vth</sub>          |                                                                               | 3.0                   | 3.5                    | 4.0                   | ٧                |

| VIN Under Voltage Lockout<br>Threshold Hysteresis                             | INUV <sub>HYS</sub>          |                                                                               |                       | 350                    |                       | mV               |

| Feedback Voltage                                                              | $V_{FB1}, V_{FB2}$           |                                                                               | 0.97                  | 1                      | 1.03                  | V                |

| Vstorage Refresh Threshold-<br>High                                           | V <sub>FB1_H</sub>           |                                                                               |                       | V <sub>FB</sub> +0.025 | V <sub>FB</sub> +0.05 | V                |

| Vstorage Refresh Threshold-<br>Low                                            | V <sub>FB1_L</sub>           |                                                                               | V <sub>FB</sub> -0.05 | V <sub>FB</sub> -0.025 |                       | V                |

| Vstorage Refresh Threshold-<br>Hysteresis                                     | V <sub>FB1_Hys</sub>         |                                                                               |                       | 50                     |                       | mV               |

| Feedback Current                                                              | I <sub>FB</sub>              | V <sub>FB1</sub> = V <sub>FB2</sub> =1V                                       |                       | 10                     | 50                    | nA               |

| PG <sub>S</sub> High Threshold                                                | VTH <sub>PGS</sub>           |                                                                               |                       | 0.9                    |                       | $V_{FB1}$        |

| PG <sub>S</sub> Low Threshold                                                 | VTL <sub>PGS</sub>           |                                                                               |                       | 0.85                   |                       | $V_{\text{FB1}}$ |

| PG <sub>S</sub> Delay                                                         | $PG_{S.Td}$                  |                                                                               |                       | 25                     |                       | μs               |

| PG <sub>s</sub> Sink Current<br>Capability                                    | $V_{PGS}$                    | Sink 4mA                                                                      |                       | 0.2                    |                       | V                |

| PG <sub>S</sub> Leakage Current                                               | I <sub>PGS LEAK</sub>        | V <sub>PGS</sub> =3.3V                                                        |                       | 10                     |                       | nA               |

| PG <sub>IN</sub> High Threshold                                               | VTH <sub>PGIN</sub>          |                                                                               |                       | 1.05                   |                       | $V_{FB2}$        |

| PG <sub>IN</sub> Low Threshold                                                | VTL <sub>PGIN</sub>          |                                                                               |                       | 1                      |                       | $V_{\text{FB2}}$ |

| PG <sub>IN</sub> Delay                                                        | $PG_{IN.Td}$                 |                                                                               |                       | 2                      |                       | μs               |

| PG <sub>IN</sub> Sink Current<br>Capability                                   | $V_{PGIN}$                   | Sink 4mA                                                                      |                       | 0.2                    |                       | V                |

| PG <sub>IN</sub> Leakage Current                                              | I <sub>PGIN_LEAK</sub>       | V <sub>PGIN</sub> =3.3V                                                       |                       | 10                     |                       | nA               |

| Input Inrush Current Limit for Charging Storage Capacitor                     | I <sub>PRECHARGE_LIMIT</sub> | V <sub>IN</sub> =12V, Charging C <sub>STORAGE</sub> from 0 to V <sub>IN</sub> |                       | 0.25                   |                       | Α                |

| Current limit for Dumping Charge from C <sub>STORAGE</sub> to V <sub>IN</sub> | I <sub>DUMP_LIMIT</sub>      |                                                                               |                       | 2.5                    | 4                     | Α                |

| Thermal Shutdown                                                              | T <sub>SD</sub>              |                                                                               |                       | 150                    |                       | °C               |

| Thermal Shutdown Hysteresis                                                   | T <sub>HYS</sub>             |                                                                               |                       | 30                     |                       | °C               |

#### Note:

5) Guaranteed by design.

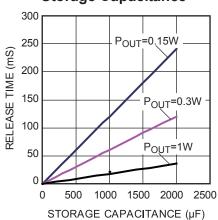

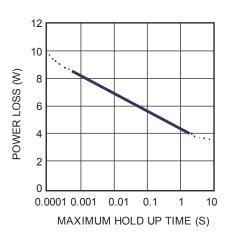

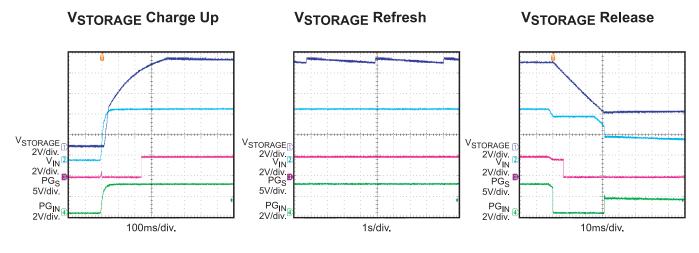

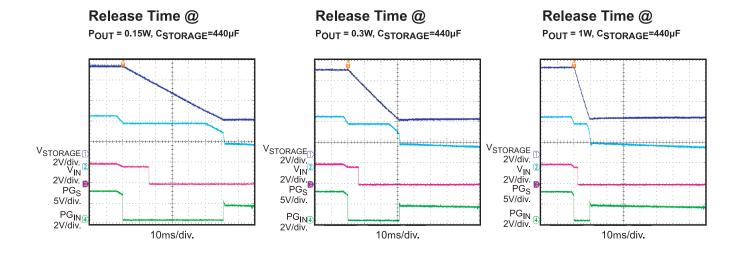

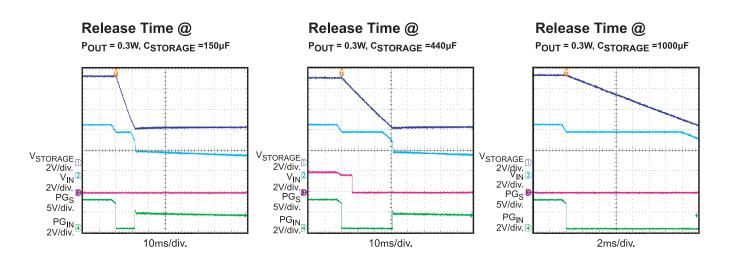

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\text{IN}}$  = 5V,  $V_{\text{STORAGE}}$  = 8.5V,  $V_{\text{RELEASE}}$  = 4.2V, For DCDC Converter:  $P_{\text{OUT}}$  = 0.3W,  $V_{\text{OUT}}$  = 1.8V,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

#### Release Time vs. Storage Capacitance

#### **Thermal Performance**

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$  = 5V,  $V_{\text{STORAGE}}$  = 8.5V,  $V_{\text{RELEASE}}$ =4.2V, For DCDC Converter:  $P_{\text{OUT}}$ =0.3W,  $V_{\text{OUT}}$ =1.8V,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

# **PIN FUNCTIONS**

| QFN2x3<br>Pin # | Name             | Description                                                                                                                                       |  |  |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1               | VMAX             | Internal Supply. A 2.2nF ceramic capacitor is required for decoupling. Place this capacitor as close to the pin as possible.                      |  |  |

| 2               | STRG             | Connect to storage capacitor for energy storage and release operation.                                                                            |  |  |

| 3               | PG <sub>IN</sub> | Open drain output to indicate input power availability.                                                                                           |  |  |

| 4               | FB1              | Feedback to set storage voltage.                                                                                                                  |  |  |

| 5               | GND              | System Ground. This pin is the reference ground of the regulated output voltage. For this reason care must be taken in PCB layout.                |  |  |

| 6               | N/C              | The pin should not be connected.                                                                                                                  |  |  |

| 7               | PGs              | Open drain output to indicate storage voltage availability.                                                                                       |  |  |

| 8               | FB2              | Feedback to set release voltage.                                                                                                                  |  |  |

| 9               | VIN              | Supply Voltage. The MP6302 operates from a +4.2V to +18V input rail. Input decoupling capacitor is needed to decouple the input rail.             |  |  |

| 10              | BST              | Bootstrap. A capacitor and a resistor in series connected between this pin and DC/DC converter's SW node is required to charge storage capacitor. |  |  |

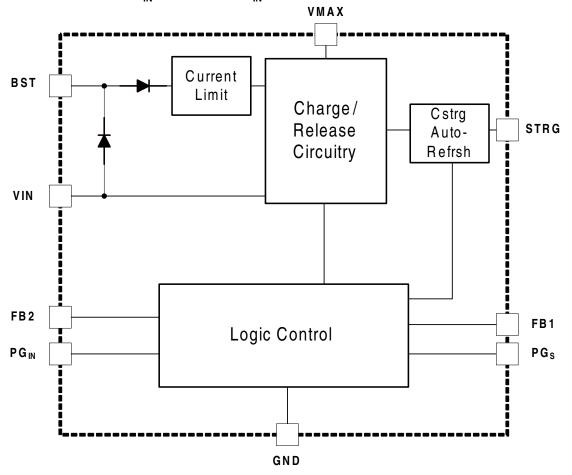

#### **OPERATION**

The MP6302 is an energy storage and release control IC. It charges the storage capacitors from input supply during power start up and keeps refreshing the storage voltage at a regulated value during normal operation. The MP6302 continuously monitors the input voltage. Once the input voltage is lower than a selected release voltage as in the case of losing input power, it releases the charge from the storage capacitors to input side, and keeps the input voltage regulated to the release voltage for as long as possible. This allows the system to respond to input power failure.

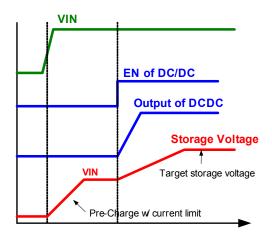

#### Start-up

During power start-up, there are two periods to charge the storage voltage. In the first period, the MP6302 pre-charges the large storage capacitors from 0 to VIN with built-in inrush current limit. Once the storage voltage is close to the input voltage, an internal boost circuitry will continuously charge and regulate the storage capacitors to the target voltage. The BST pin of MP6302 should connect to the DCDC switch node. Figure1 shows the charging process of MP6302.

Figure 1—Timing of Charging

#### **Storage Power Good Indicator**

When the voltage on FB1 pin is lower than  $0.85 \text{XV}_{\text{FB1}}$ , the PGs pin will be internally pulled low. When the FB1 is above  $0.9 \text{XV}_{\text{FB1}}$ , this pin can be driven to the high logic.

#### Storage Voltage

After the start up period of MP6302, the storage voltage can automatically regulated at a selected output voltage. With the hysteretic mechanism, when the storage voltage is lower than selected voltage, an internal controlled switch is turned on and charges the storage capacitor. Once the storage voltage is charged up, the switch turns off and waits for the next refresh cycle.

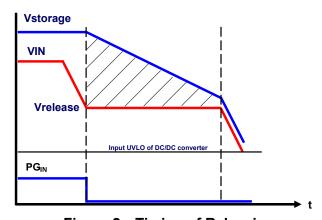

#### Release

The MP6302 keeps monitoring the input voltage. Once the input voltage is lower than the selected release voltage as in the case of losing input power, the MP6302 moves the charge from high voltage storage capacitor to low input voltage capacitor through an internal controlled release path. MP6302 must charge Vs up till PGs rises to high before a release can be executed. The release voltage can determined by choosing appropriate input resistance divider. The maximum release current can be as high as 2.5A. The release process is shown in Figure 2.

Figure 2—Timing of Releasing

#### **Input Power Good Indicator**

When the FB2 voltage, feedback voltage for the input power, is higher than  $1.05 \text{XV}_{\text{FB2}}$ , the PG\_{IN} pin can be pulled up to high logic. Connect a resistor across VIN and PG\_{IN} can drive PG\_{IN}

high. When the FB voltage is lower than  $1.00 \text{XV}_{\text{FB2}}$ , the PG\_{IN} voltage will be internally pulled low.

Figure 3—Functional Block Diagram

#### APPLICATION INFORMATION

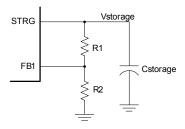

#### **Setting the Storage Voltage**

The storage voltage can be set by choosing appropriate external feedback resistors R1 and R2 which is shown in Figure 4.

Figure 4—Feedback Circuit for Storage Voltage

The storage voltage can be calculated by:

$$V_{\text{STORAGE}} = (1 + \frac{R1}{R2}) \times V_{\text{FB1}}$$

For example, if the storage voltage is set to be 8.5V, choose R2 to be  $100k\Omega$ , R1 will be then given by:

$$R1 = \frac{100k\Omega \times (8.5V - 1V)}{1V} = 750k\Omega$$

Table 1 lists the recommended resistors for different storage voltage settings.

Table 1—Resistor Selection for Different Storage Voltages

| V <sub>STORAGE</sub> (V) | R1 (kΩ) | R2 (kΩ) |

|--------------------------|---------|---------|

| 8.5                      | 750     | 100     |

| 12                       | 750     | 68      |

| 15                       | 750     | 53.6    |

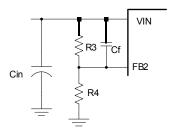

# **Setting the Release Voltage and Input Capacitors Selection**

The release voltage can be set by external feedback resistors R3 and R4 shown in Figure 5.

Figure 5—Feedback Circuit for Realease Voltage

The release voltage can be calculatedt by:

$$V_{RELEASE} = (1 + \frac{R3}{R4}) \times V_{FB2}$$

The selection of R3 and R4 not only determines the release voltage, but also impacts the stability of the release circuit. The  $300k\Omega$ -  $500k\Omega$  R3 and a  $47\mu F$   $C_{IN}$  are recommended. Table 2 lists the recommended resistors for different release voltage settings. A 15pF feed-forward capacitor is recommended for good release dynamic performance.

Table 2—Resistor and Capacitors Selection for Different Release Voltages

| V <sub>RELEASE</sub> (V) | R3 (kΩ) | R4 (kΩ) | Cf (pF) | C <sub>IN</sub> (µF) |

|--------------------------|---------|---------|---------|----------------------|

| 11                       | 475     | 47.5    | 15      | 47                   |

| 10.2                     | 464     | 49.9    | 15      | 47                   |

| 4.2                      | 324     | 100     | 15      | 47                   |

#### **Storage Capacitor Selection**

The storage capacitor is used for energy storage during normal operation and the energy will be released to VIN in case of losing input power. Usually, the small ceramic capacitors or poscap can be used based on different applications.

The voltage rating of storage capacitor needs to be higher than the targeted storage voltage. The voltage rating of storage capacitor can be fully utilized since the voltage of storage capacitor is very stable during normal operation.

The necessary storage capacitance can be estimated by:

$$Cs = \frac{I_{\text{RELEASE}} \times T_{\text{HOLD}}}{V_{\text{STORAGE}} - V_{\text{RELEASE}}}$$

Here, I<sub>RELEASE</sub>: release current

V<sub>RELEASE</sub>: release voltage

T<sub>HOLD</sub>: Hold up time

V<sub>STORAGE</sub>: voltage on C<sub>STORAGE</sub>

For example, if  $I_{RELEASE}$ =0.5A,  $T_{HOLD}$ =20ms,  $V_{STORAGE}$ =8.5V,  $V_{RELEASE}$ =4.2V the needed storage capacitance is around 2200 $\mu$ F.

#### **PCB Layout Guide**

PCB layout is important to achieve good performance operation for MP6302. Follow guidelines below and use the EVB board layout as a reference.

- Connect the BST pin as close as possible to the SW node of DCDC converter through a resistor and a small ceramic capacitor. Try to avoid interconnect the feedback path.

- Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 3) Keep the connection of the storage capacitors and STRG pin as short and wide as possible.

# TYPICAL APPLICATION CIRCUITS

Figure 6—MP6302 Application Circuit

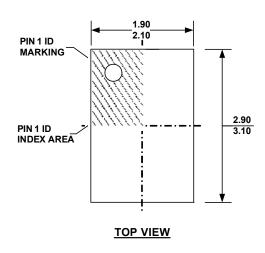

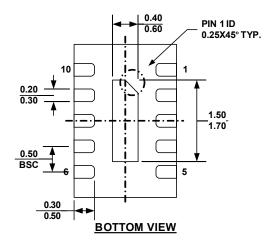

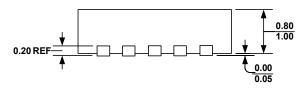

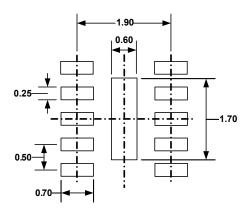

#### PACKAGE INFORMATION

## QFN10 (2x3mm)

**SIDE VIEW**

RECOMMENDED LAND PATTERN

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH

- 3) LEAD COPLANARITY SHALL BED.10 MILLIMETER MAX

- 4) JEDEC REFERENCE DRAWING IS JEDEC MO220

- 5) DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.