# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The Future of Analog IC Technology

## DESCRIPTION

The MP8003A is an IEEE, 802.3af/at, Power over Ethernet (PoE) compliant, powered device (PD), interface controller. The MP8003A has all the functions of IEEE 802.3af/at, including detection, 1-event and 2-event classification, input current control, and a 100V hot-swap MOSFET.

The MP8003A sets the inrush current limit at about 120mA during start-up and switches to 840mA when the output pass MOSFET is turned on completely. A PG signal set to high indicates when the output is fully charged and pulls low when the output drops under the overload condition. The MP8003A also provides a T2P signal when it is connected to Type-2 power sourcing equipment (PSE).

An auxiliary power input detector (AUX) provides a smooth power switch from PSE to an auxiliary wall adapter. The MP8003A also features built-in thermal protection and a wide-input UVLO hysteresis.

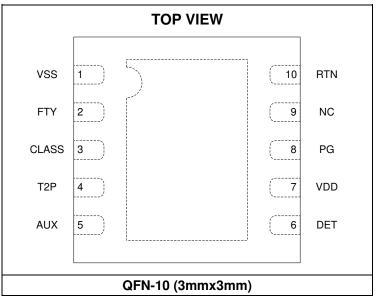

The MP8003A is available in a QFN-10 (3mmx3mm) package.

## **FEATURES**

- Compatible with 802.3af/at Specifications

- 100V, 0.48Ω Integrated Pass Switch

- 120mA Inrush Current Limit

- 840mA Operation Current Limit

- 2-Event Classification

- Auxiliary Adapter O-Ring Power Supply

- Self-Driving Power Good Inductor

- Open-Drain Type-2 PSE Indicator

- Over-Temperature Protection (OTP)

- Available in QFN-10 (3mmx3mm) Package

## **APPLICATIONS**

- IEEE 802.3af/at-Compliant Devices

- Security Cameras

- VoIP Phones

- WLAN Access Points

- IoT Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

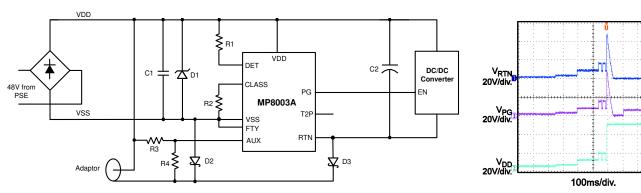

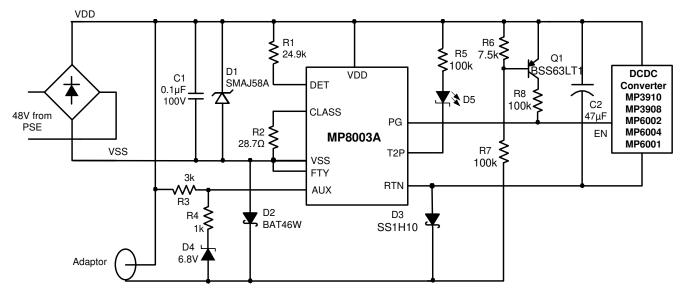

## TYPICAL APPLICATION

#### Start-Up by PSE

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

#### **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking |

|--------------|------------------|-------------|

| MP8003AGQ    | QFN-10 (3mmx3mm) | See Below   |

\* For Tape & Reel, add suffix -Z (e.g. MP8003AGQ-Z)

## **TOP MARKING**

## ANUY

$\mathbf{LLL}$

ANU: Product code of MP8003AGQ Y: Year code LLL: Lot number

## PACKAGE REFERENCE

## **ABSOLUTE MAXIMUM RATINGS (1)**

| VDD, RTN, DET, T2P, AUX to V    |                             |

|---------------------------------|-----------------------------|

|                                 |                             |

| CLASS, FTY to VSS               | 0.3V to +6.5V               |

| PG to RTN                       | 0.3V to +6.5V               |

| AUX to VDD6                     | .5V to +0.3V <sup>(2)</sup> |

| T2P sinking current             |                             |

| AUX sinking current             | 5mA <sup>(2)</sup>          |

| PG sinking current              | 1mA <sup>(3)</sup>          |

| Continuous power dissipation (T |                             |

|                                 |                             |

| Junction temperature            |                             |

| Lead temperature                | 260°C                       |

| Storage temperature6            |                             |

#### Recommended Operating Conditions <sup>(5)</sup>

| . 0V to 57V          |

|----------------------|

| 5mA                  |

| 3mA <sup>(2)</sup>   |

| 0.6mA <sup>(3)</sup> |

| to +125°C            |

|                      |

## Thermal Resistance<sup>(6)</sup> θ<sub>JA</sub> θ<sub>JC</sub>

QFN-10 (3mmx3mm) ..... 50...... 12 ... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) When VDD to the adapter ground voltage is high, the AUX-VDD voltage may exceed -6.5V if the divider resistor is not appropriate. In this condition, VDD clamps the -6.5V voltage on AUX, but the current should be limited by the external resistor.

- If PG is pulled up higher than 6.5V externally, the pull-up current should be limited. Refer to the Power Good (PG) Indicator Signal section on page 14 for more details.

- 4) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 5) The device is not guaranteed to function outside of its operating conditions.

- 6) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

VDD = 48V, all voltages are with respect to VSS,  $R_{DET}$  = 24.9k $\Omega$ ,  $R_{CLASS}$  = 28.7 $\Omega$ ,  $T_J$  = -40°C to +125°C, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                  | Symbol                | Condition                                                                             | Min  | Тур   | Max  | Units |

|--------------------------------------------|-----------------------|---------------------------------------------------------------------------------------|------|-------|------|-------|

| Detection                                  |                       |                                                                                       |      |       |      |       |

| Detection on                               | VDET-ON               | V <sub>DD</sub> rising                                                                |      | 1.9   |      | V     |

| Detection off                              | VDET-OFF              | V <sub>DD</sub> rising                                                                |      | 11    |      | V     |

| DET leakage current                        | Idet-lk               | VDET = VDD = 57V, measure IDET                                                        |      | 0.1   | 5    | μA    |

| Bias current                               |                       | V <sub>DD</sub> = 10.1V, float DET, not in<br>mark event, measure I <sub>SUPPLY</sub> |      |       | 12   | μA    |

| Detection current                          | loca                  | VDD = 2.5V, measure ISUPPLY                                                           | 96   | 99    | 102  | μA    |

| Detection current                          | IDET                  | $V_{DD} = 10.1V$ , measure Isupply                                                    | 395  | 410   | 425  | μA    |

| Classification                             |                       |                                                                                       |      |       |      |       |

| Classification stability time              |                       |                                                                                       |      | 90    |      | μs    |

| V <sub>CLASS</sub> output voltage          | V <sub>CLASS</sub>    | $13V < V_{DD} < 21V$<br>$1mA < I_{CLASS} < 42mA$                                      | 1.1  | 1.16  | 1.21 | V     |

|                                            |                       | $13 \le V_{VDD} \le 21V$ , guaranteed by $V_{CLASS}$                                  |      |       |      |       |

|                                            |                       | $R_{\text{CLASS}} = 578\Omega,  13V \leq V_{\text{DD}} \leq 21V$                      | 1.8  | 2     | 2.4  | mA    |

| Classification current                     | ICLASS                | $R_{CLASS} = 110\Omega, \ 13V \le V_{DD} \le 21V$                                     | 9.9  | 10.55 | 11.3 |       |

| Olassification current                     | ICLASS                | $R_{CLASS} = 62\Omega, 13V \le V_{DD} \le 21V$                                        | 17.7 | 18.7  | 19.8 |       |

|                                            |                       | $R_{CLASS} = 41.2\Omega, \ 13V \le V_{DD} \le 21V$                                    | 26.6 | 28.15 | 29.7 |       |

|                                            |                       | $R_{CLASS} = 28.7\Omega, 13V \le V_{DD} \le 21V$                                      | 38.2 | 40.4  | 42.6 |       |

| Classification lower<br>threshold          | V <sub>CL-ON</sub>    | Regulator turns on, $V_{DD}$ rising                                                   | 11.8 | 12.5  | 13   | V     |

| Classification upper threshold             |                       | Regulator turns off, $V_{DD}$ rising                                                  | 21   | 22    | 23   | V     |

| Classification bystoresis                  | V <sub>CL-HYS</sub>   | Low-side hysteresis                                                                   |      | 0.8   |      | v     |

| Classification hysteresis                  |                       | High-side hysteresis                                                                  |      | 0.5   |      | v     |

| Mark event reset threshold                 | V <sub>MARK-L</sub>   |                                                                                       | 4.5  | 5     | 5.5  | V     |

| Max mark event voltage                     | Vmark-h               |                                                                                       | 11   | 11.5  | 12   | V     |

| Mark event current                         | Imark                 |                                                                                       | 0.5  | 1.5   | 2    | mA    |

| Mark event resistance                      | RMARK                 | 2-point measure at 7V and 10V                                                         |      |       | 12   | kΩ    |

| IC supply current during<br>classification | I <sub>IN-CLASS</sub> | $V_{DD} = 17.5V$ , CLASS floating                                                     |      | 220   | 300  | μA    |

| CLASS leakage current                      | ILEAKAGE              | $V_{\text{CLASS}}=0V,V_{\text{DD}}=57V$                                               |      |       | 1    | μA    |

| UVLO                                       |                       |                                                                                       |      |       |      |       |

| VDD turn on threshold                      | VDD-VSS-R             | V <sub>DD</sub> rising                                                                | 35   | 37.5  | 40   | V     |

| VDD turn off threshold                     | VDD-VSS-F             | V <sub>DD</sub> falling                                                               | 29   | 31    | 33   | V     |

| VDD UVLO hysteresis                        | VDD-VSS-HYS           |                                                                                       | 4.9  |       |      | V     |

| IC supply current during operation         | lin                   |                                                                                       |      | 450   |      | μA    |

### ELECTRICAL CHARACTERISTICS (continued)

VDD = 48V, all voltages are with respect to VSS,  $R_{DET} = 24.9k\Omega$ ,  $R_{CLASS} = 28.7\Omega$ ,  $T_J = -40^{\circ}C$  to +125°C, typical values are tested at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                     | Symbol           | Condition                                          | Min  | Тур  | Мах  | Units |

|-----------------------------------------------|------------------|----------------------------------------------------|------|------|------|-------|

| Pass Device and Current Li                    | mit              |                                                    |      |      |      |       |

| On resistance                                 | Ron-RTN          | I <sub>RTN</sub> = 600mA                           |      | 0.48 |      | Ω     |

| Leakage current                               | Irtn-lk          | $V_{\text{DD}} = V_{\text{RTN}} = 57V$             |      | 1    | 15   | μA    |

| Current limit                                 | ILIMIT           | V <sub>RTN</sub> = 1V                              | 720  | 840  | 920  | mA    |

| Inrush limit                                  | IINRUSH          | $V_{RTN} = 2V$                                     |      | 120  |      | mA    |

| Inrush current termination                    |                  | VRTN falling                                       |      | 1.2  |      | V     |

| Inrush to operation mode delay                | TDELAY           |                                                    | 80   | 100  |      | ms    |

| Current foldback threshold                    |                  | V <sub>RTN</sub> rising                            |      | 10   |      | V     |

| Foldback deglitch time                        |                  | V <sub>RTN</sub> rising to inrush current foldback |      | 1    |      | ms    |

| T2P                                           |                  |                                                    |      |      |      |       |

| T2P output low voltage                        |                  | IT2P = 2mA, respect to VSS                         |      | 0.1  | 0.3  | V     |

| T2P high leakage current                      |                  | V <sub>T2P</sub> = 48V                             |      |      | 1    | μA    |

| AUX                                           |                  |                                                    |      |      |      |       |

| AUX high threshold voltage <sup>(7)</sup>     |                  | Respect to VDD                                     |      |      | -2.3 | V     |

| AUX low threshold voltage <sup>(7)</sup>      |                  | Respect to VDD                                     | -0.6 |      |      | V     |

| AUX leakage current                           |                  | V <sub>DD</sub> - V <sub>AUX</sub> = 6V            |      |      | 2    | μA    |

| PG                                            |                  |                                                    |      |      |      |       |

| PG output high voltage                        |                  | PG floating                                        |      | 5.5  |      | V     |

| PG source current                             |                  | PG = high, force PG = 4V                           | 7    |      |      | μA    |

| PG pull-down resistance                       |                  | PG is logic low, pull PG up to 1V                  |      | 1000 |      | kΩ    |

| Thermal Shutdown                              |                  |                                                    |      |      |      |       |

| Thermal shutdown temperature <sup>(8)</sup>   | T <sub>SD</sub>  |                                                    |      | 150  |      | °C    |

| Thermal shutdown<br>hysteresis <sup>(8)</sup> | T <sub>HYS</sub> |                                                    |      | 20   |      | °C    |

NOTES:

VDD - AUX > 2.3V, IC enable adapter input. If VDD - AUX < 0.6V, IC enables the PSE input. Refer to the Wall Power Adapter Detection and Operation section on page 12 for the AUX setting.

8) Guaranteed by engineering sample characterization.

5

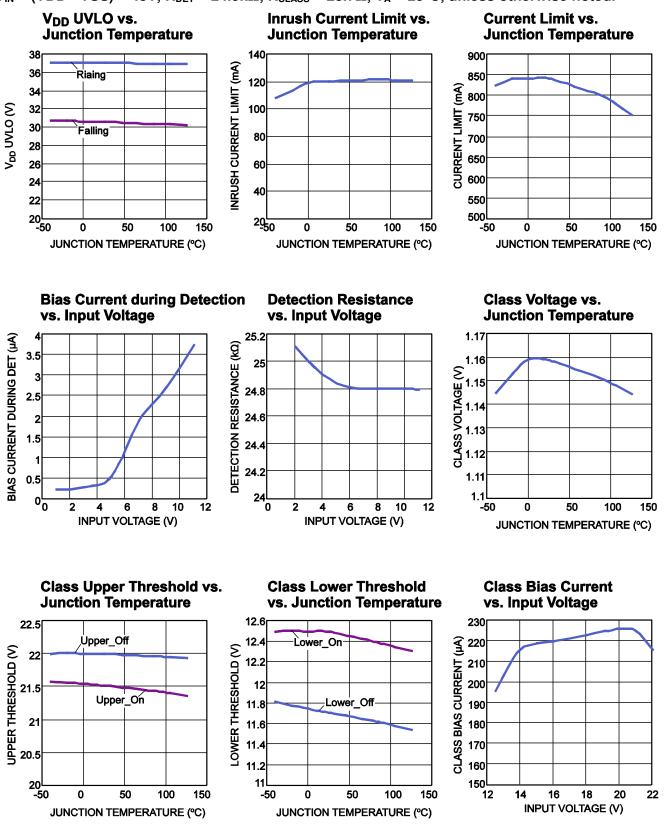

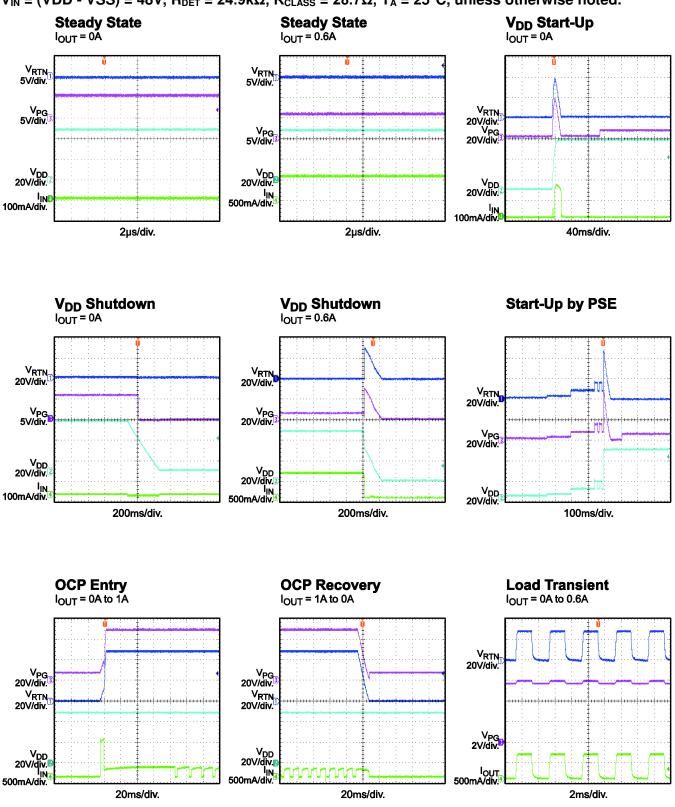

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN} = (VDD - VSS) = 48V$ ,  $R_{DET} = 24.9k\Omega$ ,  $R_{CLASS} = 28.7\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

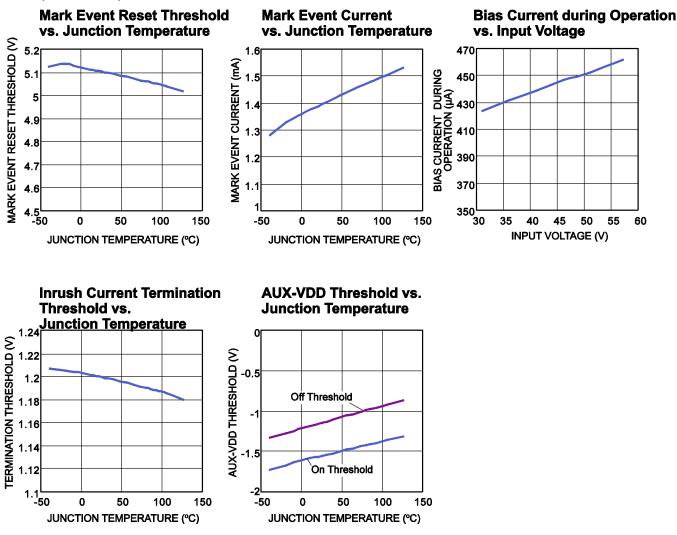

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN} = (VDD - VSS) = 48V$ ,  $R_{DET} = 24.9k\Omega$ ,  $R_{CLASS} = 28.7\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN} = (VDD - VSS) = 48V$ ,  $R_{DET} = 24.9k\Omega$ ,  $R_{CLASS} = 28.7\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

## **PIN FUNCTIONS**

╻╽╼└═

| PIN# | Name  | Description                                                                                                                                                                                                              |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VSS   | Negative power supply terminal from the PoE input power rail.                                                                                                                                                            |

| 2    | FTY   | Factory use only. FTY must be connected to VSS during application.                                                                                                                                                       |

| 3    | CLASS | <b>Power class.</b> Connect resistor from CLASS to VSS to program the classification current.                                                                                                                            |

| 4    | T2P   | <b>Type-2 PSE indictor, open-drain output.</b> T2P is pulled low to VSS to indicate the presence of a Type-2 PSE or if AUX is enabled.                                                                                   |

| 5    | AUX   | <b>Auxiliary power input detector.</b> Use AUX for adapter auxiliary power applications.<br>Drive VDD - AUX higher than 2.3V to disable the hot-swap MOSFET and CLASS function and force T2P and PG active.              |

| 6    | DET   | <b>Detection.</b> Connect a 24.9k $\Omega$ resistor between VDD and DET for PoE detection.                                                                                                                               |

| 7    | VDD   | Positive power supply terminal from the PoE input power rail.                                                                                                                                                            |

| 8    | PG    | <b>PD supply power good indicator.</b> The PG signal can be used to enable the downstream DC/DC converter. PG is pulled up by an internal current source in output-high condition and can be floated during application. |

| 9    | NC    | <b>No connection.</b> NC is not connected internally, but can be connected to VSS and the exposed thermal pad during layout.                                                                                             |

| 10   | RTN   | <b>Drain of PD hot-swap MOSFET.</b> Connect the next stage DC/DC converter's power return terminal to RTN.                                                                                                               |

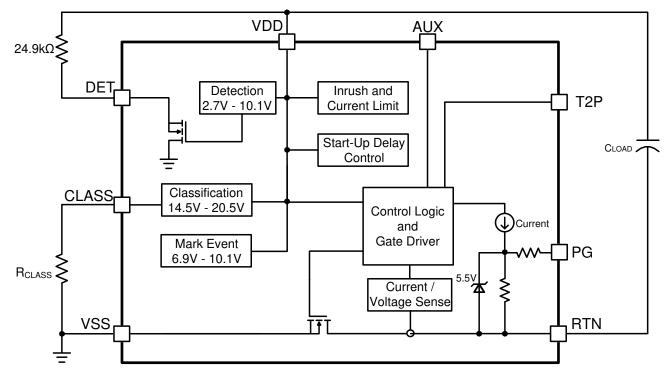

## **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

## MP8003A – IEEE 802.3af/at, PoE, POWERED DEVICE, INTERFACE CONTROLLER

### **OPERATION**

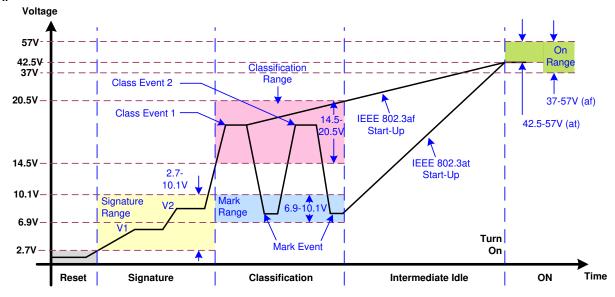

Compared with IEEE 802.3af, the IEEE 802.3at standard establishes a higher power allocation Ethernet (PoE) for Power over while maintaining backwards compatibility with existing IEEE 802.3af systems. Power sourcing equipment (PSE) and powered devices (PD) are distinguished as Type-1 (complying with 802.3af power levels) or Type-2 IEEE (complying with the IEEE 802.3at power levels). The IEEE 802.3af/at standard establishes a method of communication between PD and PSE with detection, classification, and event mark.

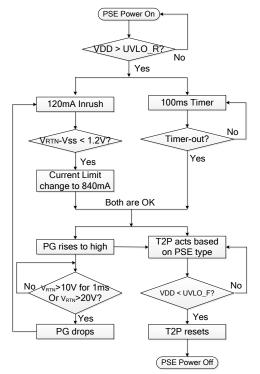

The MP8003A is an IEEE 802.3af/at PoE PD interface. The MP8003A operates as a safety device that supplies voltage only when the power sourcing equipment recognizes a unique, tightly specified resistance at the end of an unknown length of Ethernet cable. If the PSE sees the correct load, then it increases the applied voltage further to enter the classification operation range and switch on the nominal 48V power to the load. Figure 2 shows the typical PD interface power operation sequence.

#### Detection

RDET connected between DET and VDD is presented as a load to the PSE in detection mode. When the PSE applies two safe voltages between 2.7V to 10.1V while measuring the change in current drawn to determine the load resistance. A 24.9k $\Omega$  (1%) resistor between VDD and DET is recommended to present one correct signature. The valid signature resistance seen from the power interface (PI) is between 23.7k $\Omega$  and 26.3k $\Omega$ .

The detection resistance seen from the PI is the result of the input bridge resistance in series with the VDD load. The input bridge resistance is cancelled partially by the effective leakage resistance during detection.

#### Classification

The classification mode can specify the expected load range of the device under power to the PSE so that the PSE can distribute power intelligently to as many loads as it can within its maximum current capability. The classification mode is active between 14.5V and 20.5V. The MP8003A presents a current in classification mode (see Table 1).

| Class | Max Input<br>Power to PD<br>(W) | Classification<br>Current (mA) | R <sub>CLASS</sub><br>(Ω) |

|-------|---------------------------------|--------------------------------|---------------------------|

| 0     | 12.95                           | 2                              | 578                       |

| 1     | 3.84                            | 10.55                          | 110                       |

| 2     | 6.49                            | 18.7                           | 62                        |

| 3     | 12.95                           | 28.15                          | 41.2                      |

| 4     | 25.5                            | 40.4                           | 28.7                      |

Table 1: Class Resistor Selection

#### 2-Event Classification

The MP8003A can be used as a Type-1 PD class 0-3 (as shown in Table 1). It also distinguishes class 4 with 2-event classification.

In 2-event classification, the Type-2 PSE reads the power classification twice. Figure 2 shows an example of a 2-event classification. The first classification event occurs when the PSE presents a voltage between 14.5V to 20.5V to the MP8003A, and the MP8003A presents a class-4 load current. The PSE then drops the input voltage into the mark voltage range of 6.9V to 10.1V signaling the first mark event. The MP8003A presents a load current between 0.5mA to 2mA in the mark event voltage range.

The PSE repeats this sequence, signaling the second classification and second mark event. The PSE then applies power to the MP8003A, which charges up the downstream DC/DC input capacitor (C2) with a controlled inrush current. When C2 is fully charged, T2P presents an active low signal with respect to VSS after  $T_{DELAY}$ . The T2P output becomes inactive when the MP8003A input voltage (VDD) falls below UVLO (see Figure 3).

## Under-Voltage Lockout (UVLO) and Current Limit

When the PD voltage is powered by PSE, and VDD is higher than the turn-on threshold, the hot-swap switch starts passing a limited current (I<sub>INRUSH</sub>) to charge the downstream DC/DC converter's input capacitor. The start-up charging current is around 120mA.

If RTN drops below 1.2V, the hot-swap current limit switches to 840mA. After the  $T_{DELAY}$  from UVLO begins, the MP8003A asserts the PG signal and switches from start-up mode to normal operation mode. The PG signal can enable the downstream DC/DC converter directly.

If VDD - VSS drops below the input falling UVLO threshold, the hot-swap MOSFET is disabled.

If the output current overloads on the internal pass MOSFET, the current limit works, and  $V_{\text{RTN}}$  - VSS rises. If  $V_{\text{RTN}}$  rises above 10V for longer than 1ms or rises above 20V, the current limit reverts to the inrush value and pulls down PG simultaneously.

Figure 3 shows the current limit, PG, and T2P work logic during start-up from the PSE power supply.

Figure 3: Start-Up Sequence

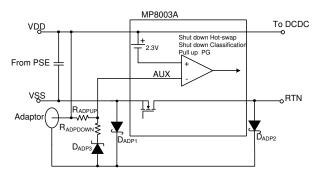

## Wall Power Adapter Detection and Operation

For applications where an auxiliary power source such as a wall adapter is used to power the device, the MP8003A features wall power adapter detection (see Figure 4). Once the input voltage (VDD - VSS) exceeds about 11.5V, the MP8003A enables wall adapter detection. The wall power adapter detection resistor divider is connected from VDD to the negative terminal of an adapter.  $D_{ADP3}$  in Figure 4 is added for more accurate hysteresis. There is a -2.3V turn-on voltage from AUX to VDD for adapter detection.

The adapter is detected when Equation (1) is met:

$$V_{\text{DD}} - V_{\text{AUX}} = (V_{\text{ADP}} - V_{\text{DADP3}}) \times \frac{R_{\text{ADPUP}}}{R_{\text{ADPUP}} + R_{\text{ADPDOWN}}} > 2.3V \quad (1)$$

Where  $V_{ADP}$  is the adapter voltage,  $V_{DADP3}$  is the Zener voltage, and  $R_{ADPUP}$  and  $R_{ADPDOWN}$  are the AUX divider resistors from the adapter power.

If applied adapter voltage is much higher than the design adapter voltage, the VDD -  $V_{AUX}$ voltage is high. If the applied adapter voltage is higher than 6.5V, the MP8003A inner circuit clamps the VDD -  $V_{AUX}$  voltage at 6.5V. A current then flows out through AUX. The current should be limited below 3mA by an external resistor (R<sub>ADPUP</sub>/R<sub>ADPDOWN</sub> or R<sub>T</sub> from the resistor divider to AUX).

To make the MP8003A work stably with adapter power, one Schottky diode (D<sub>ADP1</sub>, D2 in the schematic on page 1) is required between the negative terminal of the adapter and VSS. D<sub>ADP2</sub> (D3 in the schematic on page 1) is used to block reverse current between the adapter and PSE power source. When a wall adapter is detected, the internal MOSFET between RTN and VSS turns off, the classification current is disabled, and T2P becomes active. The PG signal is active when the adapter power is detected so that it can enable the downstream DC/DC converter, even if the input hot-swap MOSFET is disabled.

Figure 4: Adapter Power Detection

#### **Power Good Indicator (PG)**

The PG signal is driven by the internal current source. After  $T_{DELAY}$  from UVLO starts, and RTN drops to 1.2V, or a wall power adapter is detected, the PG signal is pulled high to indicate the output power condition and enable the downstream DC/DC converter. Figure 3 shows the PG logic when powered from PSE. PG is high if the adapter is detected.

#### Thermal Shutdown

The MP8003A has a temperature protection circuit. When the junction temperature exceeds 150°C, the IC shuts down. The IC recovers with limited inrush current if the junction temperature drops below 130°C.

## **APPLICATION INFORMATION**

#### **Detection Resistor**

In detection mode, a resistor connected between DET and VDD is required as a load to the PSE. The resistance is calculated as  $\Delta V/\Delta I$  with an acceptable range of 23.7k $\Omega$  to 26.3k $\Omega$ . Use a typical value of 24.9k $\Omega$  as a detection resistor.

#### **Classification Resistor**

To distribute power to as many loads as possible from PSE, a resistor between CLASS and VSS is used to classify the PD power level, which draws a fixed current set by the classification resistor. The supplied power set by the classification resistor is shown in Table 1. The typical voltage on CLASS is 1.16V in the classification range and produces about 47mW of power loss on the CLASS resistor, even in class-4 condition.

#### **Protection TVS**

To limit the input transient voltage within the absolute maximum ratings, a TVS across the rectified voltage (VDD - VSS) must be used. A SMAJ58A TVS or equivalent is recommended for general indoor applications. Outdoor transient levels or special applications require additional protection.

#### **PD Input Capacitor**

A  $0.05\mu$ F to  $0.12\mu$ F input bypass capacitor from VDD to VSS is needed for IEEE 802.3at standard specifications. Typically, a  $0.1\mu$ F, 100V, ceramic capacitor is sufficient.

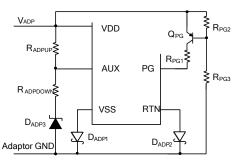

#### Wall Power Adapter Detection Circuit

When an auxiliary power source, such as a wall power adapter, is used to power the device, the divider resistors,  $R_{ADPUP}$ ,  $R_{ADPDOWN}$ , and  $D_{ADP3}$  should be chosen to satisfy Equation (1) for correct wall power adapter detection (see Figure 5).

$R_{ADPUP}$  with a typical  $3k\Omega$  value is recommended to balance power loss and  $D_{ADP1}$  and  $D_{ADP2}$  leakage current discharge.

Figure 5: Wall Adapter Detection Circuit

One small Schottky diode with a 100V voltage rating, such as BAT46W, is suggested for  $D_{ADP1}$ , typically. The voltage rating of  $D_{ADP2}$  must also be 100V or higher, while the current rating must be higher than the load current. A low voltage drop Schottky diode, such as SS1H10, is recommended to reduce conduction power loss. The MP8003A enables wall adapter detection when VDD is 11.5V. If one adapter power with a lower voltage rating (such as 10V) is used to power the converter, one external PG pull-up circuit is necessary to enable the downstream DC/DC converter.

#### Power Good (PG) Indicator Signal

The MP8003A integrates one PG indicator. Since PG is pulled high through an internal pullup current source when the logic is high, it can be used to enable the downstream DC/DC converter without an external pull-up circuit. PG disables the internal pull-up current and is pulled low through a  $1M\Omega$  internal resistor when PG is in a logic-low state. If there is a low resistance pulling down on EN of the downstream converter, some external PG pullup current is needed. The MP8003A can provide 7µA of pull-up current. If PG is pulled up higher than the 5.5V power source, the PG sink current should be limited to protect the internal clamp Zener diode. Normally, an input current 0.6mA or lower on PG is suggested.

If one adapter power less than 11.5V is connected to supply the converter, the PG function cannot work with such a low input. The external PG pull-up circuit is recommended (see Figure 5). Typically,  $Q_{PG}$  requires a  $V_{CE}$  voltage higher than 100V, such as BSS63LT1. Choose  $R_{PG2} = 7.5 k\Omega$  and  $R_{PG3} = 100 k\Omega$  for a 12V adapter with some adapter regulation margin, and choose  $R_{PG1} = 100 k\Omega$  to limit the PG sink current.

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

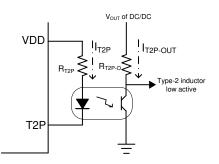

#### **T2P Indicator Connection**

T2P is an active-low, open-drain output which indicates the presence of a Type-2 PSE or adapter power. An optocoupler is used as the interface from T2P to the circuitry on the output of the converter, typically (see Figure 6). A high-gain optocoupler and a high-impedance receiver (i.e.: CMOS) are recommended.

Figure 6: T2P Inductor Circuit

Considering the T2P sinking current (typically 2mA), the T2P output low voltage 0.1V, and the diode forward voltage drop, choose  $R_{T2P}$  to be 23.7k $\Omega$ . Suppose V<sub>OUT</sub> of the DC/DC converter is 12V. To match the typical 48V input, choose  $R_{T2P-O} = 20k\Omega$  based on the CRT, though it may vary with temperature, LED bias current, and aging.

If using an LED from VDD to T2P to indicate T2P activity, the  $R_{T2P}$ 's resistance can be higher to match the LED's max current and reduce power loss.

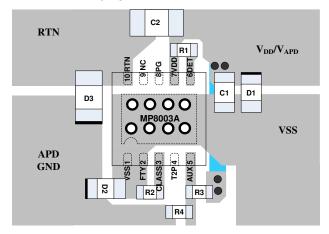

#### **PCB Layout Guidelines**

Efficient layout of the PoE front end should guarantee solid performance, low power loss, and no EMI/ESD problems. The spacing between VDD (48V) and VSS must comply with safety standards such as IEC60950. For best results, refer to Figure 7 and follow the guidelines below.

- Ensure that all component placement follows the power flow from RJ-45 to the Ethernet transformer to the diode bridges to TVS to the 0.1µF capacitor to the DC/DC converter input bulk capacitor.

- 2. Make all leads as short as possible with wide power traces.

- 3. Place the MP8003A local ground planes referenced to VSS.

- 4. Place the next-stage DC/DC converter ground planes referenced to RTN.

- 5. Connect the exposed pad to VSS, since it is used to heat sink the part to the circuit board traces.

- 6. Place large copper traces and vias on the exposed pad and VSS trace for thermal dissipation.

Figure 7 shows the recommended component placement for the MP8003A based on the schematic on page 1.

Figure 7: Recommended Layout

#### Design Example

Table 2 is a design example following the application guidelines for the following specifications.

| Table | 2: | Design | Example |

|-------|----|--------|---------|

| Table | ۷. | Design | LAINPIC |

|                  | * •    |

|------------------|--------|

| VDD - VSS        | 48V    |

| R <sub>DET</sub> | 24.9kΩ |

| RCLASS           | 28.7Ω  |

| VADAPTER         | 12V    |

The typical application circuit in Figure 8 shows the detailed application schematic, and is the basis for the Typical Performance Characteristics section. Typically, the device is powered by PSE (VDD - VSS = 48V). When an adapter voltage above 9.6V is present, the internal MOSFET between RTN and VSS turns off. Instead, the device is powered by the adapter regardless of what the PSE voltage is. For more detailed device applications, please refer to the related evaluation board datasheet.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

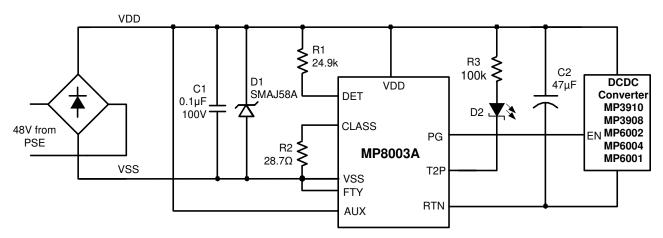

## **TYPICAL APPLICATION CIRCUITS**

Figure 8: Typical Application Circuit, VDD - VSS = 48V, V<sub>ADAPTER</sub> = 12V

Figure 9: Typical Application Circuit, VDD - VSS = 48V, No Adapter Input

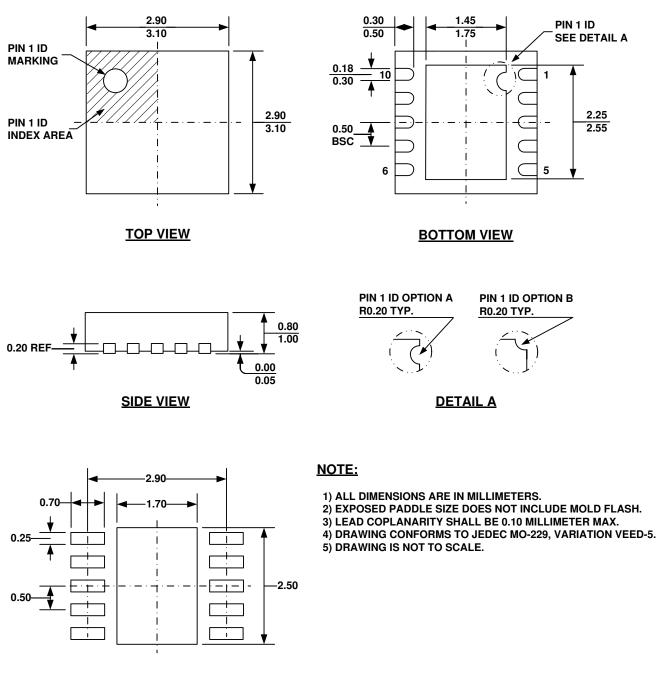

## **PACKAGE INFORMATION**

#### QFN-10 (3mmx3mm)

**RECOMMENDED LAND PATTERN**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.