# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Freescale Semiconductor

Document Number: MPC755EC Rev. 8, 02/2006

# MPC755 RISC Microprocessor Hardware Specifications

This document is primarily concerned with the MPC755; however, unless otherwise noted, all information here also applies to the MPC745. The MPC755 and MPC745 are reduced instruction set computing (RISC) microprocessors that implement the PowerPC<sup>TM</sup> instruction set architecture. This document describes pertinent physical characteristics of the MPC755. For information on specific MPC755 part numbers covered by this or other specifications, see Section 10, "Ordering Information." For functional characteristics of the processor, refer to the *MPC750 RISC Microprocessor Family User's Manual.*

To locate any published errata or updates for this document, refer to the website listed on the back cover of this document.

# 1 Overview

The MPC755 is targeted for low-cost, low-power systems and supports the following power management features—doze, nap, sleep, and dynamic power management. The MPC755 consists of a processor core and an internal L2 tag combined with a dedicated L2 cache interface and a 60x bus. The MPC745 is identical to the MPC755 except it does not support the L2 cache interface.

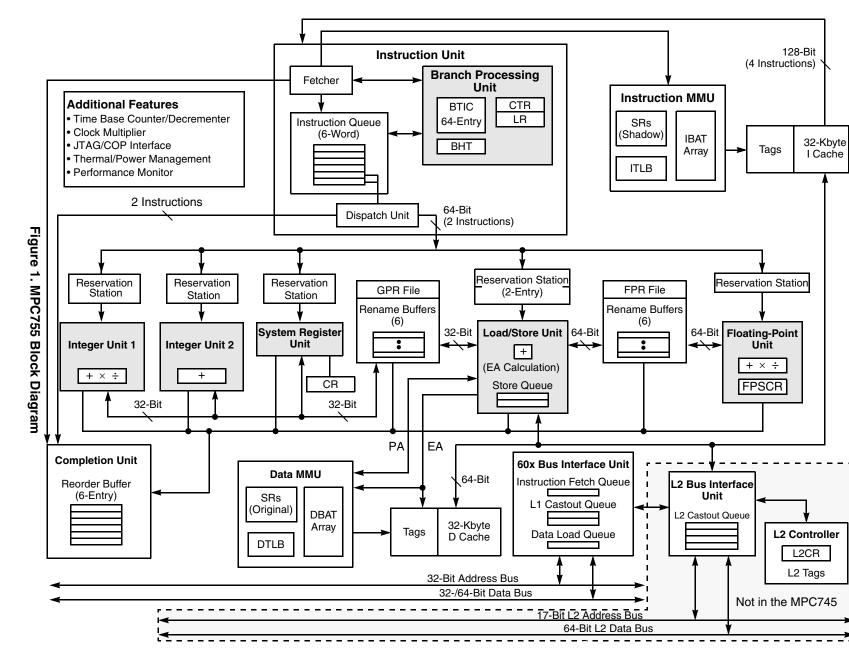

Figure 1 shows a block diagram of the MPC755.

#### Contents

| 1.  | Overview                                 |

|-----|------------------------------------------|

| 2.  | Features                                 |

| 3.  | General Parameters 5                     |

| 4.  | Electrical and Thermal Characteristics 6 |

| 5.  | Pin Assignments 25                       |

| 6.  | Pinout Listings 27                       |

| 7.  | Package Description 32                   |

| 8.  | System Design Information                |

| 9.  | Document Revision History 50             |

| 10. | Ordering Information 53                  |

© Freescale Semiconductor, Inc., 2006. All rights reserved.

Overview

MPC755 RISC Microprocessor Hardware Specifications, Rev.

ω

Freescale Semiconductor

N

# 2 Features

This section summarizes features of the MPC755 implementation of the PowerPC architecture. Major features of the MPC755 are as follows:

- Branch processing unit

- Four instructions fetched per clock

- One branch processed per cycle (plus resolving two speculations)

- Up to one speculative stream in execution, one additional speculative stream in fetch

- 512-entry branch history table (BHT) for dynamic prediction

- 64-entry, four-way set-associative branch target instruction cache (BTIC) for eliminating branch delay slots

- Dispatch unit

- Full hardware detection of dependencies (resolved in the execution units)

- Dispatch two instructions to six independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, floating-point)

- Serialization control (predispatch, postdispatch, execution serialization)

- Decode

- Register file access

- Forwarding control

- Partial instruction decode

- Completion

- Six-entry completion buffer

- Instruction tracking and peak completion of two instructions per cycle

- Completion of instructions in program order while supporting out-of-order instruction execution, completion serialization, and all instruction flow changes

- Fixed point units (FXUs) that share 32 GPRs for integer operands

- Fixed Point Unit 1 (FXU1)-multiply, divide, shift, rotate, arithmetic, logical

- Fixed Point Unit 2 (FXU2)—shift, rotate, arithmetic, logical

- Single-cycle arithmetic, shifts, rotates, logical

- Multiply and divide support (multi-cycle)

- Early out multiply

- Floating-point unit and a 32-entry FPR file

- Support for IEEE standard 754 single- and double-precision floating-point arithmetic

- Hardware support for divide

- Hardware support for denormalized numbers

- Single-entry reservation station

- Supports non-IEEE mode for time-critical operations

- Three-cycle latency, one-cycle throughput, single-precision multiply-add

Features

- Three-cycle latency, one-cycle throughput, double-precision add

- Four-cycle latency, two-cycle throughput, double-precision multiply-add

- System unit

- Executes CR logical instructions and miscellaneous system instructions

- Special register transfer instructions

- Load/store unit

- One-cycle load or store cache access (byte, half-word, word, double word)

- Effective address generation

- Hits under misses (one outstanding miss)

- Single-cycle unaligned access within double-word boundary

- Alignment, zero padding, sign extend for integer register file

- Floating-point internal format conversion (alignment, normalization)

- Sequencing for load/store multiples and string operations

- Store gathering

- Cache and TLB instructions

- Big- and little-endian byte addressing supported

- Level 1 cache structure

- 32K, 32-byte line, eight-way set-associative instruction cache (iL1)

- 32K, 32-byte line, eight-way set-associative data cache (dL1)

- Cache locking for both instruction and data caches, selectable by group of ways

- Single-cycle cache access

- Pseudo least-recently-used (PLRU) replacement

- Copy-back or write-through data cache (on a page per page basis)

- MEI data cache coherency maintained in hardware

- Nonblocking instruction and data cache (one outstanding miss under hits)

- No snooping of instruction cache

- Level 2 (L2) cache interface (not implemented on MPC745)

- Internal L2 cache controller and tags; external data SRAMs

- 256K, 512K, and 1 Mbyte two-way set-associative L2 cache support

- Copy-back or write-through data cache (on a page basis, or for all L2)

- Instruction-only mode and data-only mode

- 64-byte (256K/512K) or 128-byte (1M) sectored line size

- Supports flow through (register-buffer) synchronous BurstRAMs, pipelined (register-register) synchronous BurstRAMs (3-1-1-1 or strobeless 4-1-1-1) and pipelined (register-register) late write synchronous BurstRAMs

- L2 configurable to cache, private memory, or split cache/private memory

- Core-to-L2 frequency divisors of  $\div 1$ ,  $\div 1.5$ ,  $\div 2$ ,  $\div 2.5$ , and  $\div 3$  supported

- 64-bit data bus

- Selectable interface voltages of 2.5 and 3.3 V

- Parity checking on both L2 address and data

- Memory management unit

- 128-entry, two-way set-associative instruction TLB

- 128-entry, two-way set-associative data TLB

- Hardware reload for TLBs

- Hardware or optional software tablewalk support

- Eight instruction BATs and eight data BATs

- Eight SPRGs, for assistance with software tablewalks

- Virtual memory support for up to 4 exabytes  $(2^{52})$  of virtual memory

- Real memory support for up to 4 gigabytes  $(2^{32})$  of physical memory

- Bus interface

- Compatible with 60x processor interface

- 32-bit address bus

- 64-bit data bus, 32-bit mode selectable

- Bus-to-core frequency multipliers of 2x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 10x supported

- Selectable interface voltages of 2.5 and 3.3 V

- Parity checking on both address and data buses

- Power management

- Low-power design with thermal requirements very similar to MPC740/MPC750

- Three static power saving modes: doze, nap, and sleep

- Dynamic power management

- Integrated thermal management assist unit

- On-chip thermal sensor and control logic

- Thermal management interrupt for software regulation of junction temperature

- Testability

- LSSD scan design

- IEEE 1149.1 JTAG interface

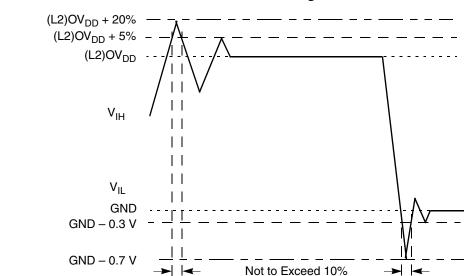

# **3 General Parameters**

The following list provides a summary of the general parameters of the MPC755:

| Technology       | 0.22 µm CMOS, six-layer metal                              |

|------------------|------------------------------------------------------------|

| Die size         | $6.61 \text{ mm} \times 7.73 \text{ mm} (51 \text{ mm}^2)$ |

| Transistor count | 6.75 million                                               |

| Logic design     | Fully-static                                               |

| Packages          | MPC745: Surface mount 255 plastic ball grid array (PBGA)<br>MPC755: Surface mount 360 ceramic ball grid array (CBGA)<br>Surface mount 360 plastic ball grid array (PBGA) |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core power supply | 2.0 V $\pm$ 100 mV DC (nominal; some parts support core voltages down to 1.8 V; see Table 3 for recommended operating conditions)                                        |

| I/O power supply  | 2.5 V $\pm$ 100 mV DC or<br>3.3 V $\pm$ 165 mV DC (input thresholds are configuration pin selectable)                                                                    |

# 4 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC755.

### 4.1 DC Electrical Characteristics

Table 1 through Table 7 describe the MPC755 DC electrical characteristics. Table 1 provides the absolute maximum ratings.

|                              | Characteristic        |                    | Maximum Value                      | Unit | Notes |

|------------------------------|-----------------------|--------------------|------------------------------------|------|-------|

| Core supply voltage          |                       | V <sub>DD</sub>    | -0.3 to 2.5                        | V    | 4     |

| PLL supply voltage           |                       | AV <sub>DD</sub>   | -0.3 to 2.5                        | V    | 4     |

| L2 DLL supply voltage        |                       | L2AV <sub>DD</sub> | -0.3 to 2.5                        | V    | 4     |

| Processor bus supply voltage |                       | OV <sub>DD</sub>   | -0.3 to 3.6                        | V    | 3     |

| L2 bus supply voltage        | L2 bus supply voltage |                    | -0.3 to 3.6                        | V    | 3     |

| Input voltage                | Processor bus         | V <sub>in</sub>    | -0.3 to OV <sub>DD</sub> + 0.3 V   | V    | 2, 5  |

|                              | L2 bus                | V <sub>in</sub>    | -0.3 to L2OV <sub>DD</sub> + 0.3 V | V    | 2, 5  |

|                              | JTAG signals          | V <sub>in</sub>    | -0.3 to 3.6                        | V    |       |

| Storage temperature range    |                       | T <sub>stg</sub>   | -55 to 150                         | °C   |       |

#### Table 1. Absolute Maximum Ratings<sup>1</sup>

Notes:

- 1. Functional and tested operating conditions are given in Table 3. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution: Vin must not exceed OV<sub>DD</sub> or L2OV<sub>DD</sub> by more than 0.3 V at any time including during power-on reset.

- 3. **Caution:** L2OV<sub>DD</sub>/OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/L2AV<sub>DD</sub> by more than 1.6 V during normal operation. During power-on reset and power-down sequences, L2OV<sub>DD</sub>/OV<sub>DD</sub> may exceed V<sub>DD</sub>/AV<sub>DD</sub>/L2AV<sub>DD</sub> by up to 3.3 V for up to 20 ms, or by 2.5 V for up to 40 ms. Excursions beyond 3.3 V or 40 ms are not supported.

- 4. Caution: V<sub>DD</sub>/AV<sub>DD</sub>/L2AV<sub>DD</sub> must not exceed L2OV<sub>DD</sub>/OV<sub>DD</sub> by more than 0.4 V during normal operation. During power-on reset and power-down sequences, V<sub>DD</sub>/AV<sub>DD</sub>/L2AV<sub>DD</sub> may exceed L2OV<sub>DD</sub>/OV<sub>DD</sub> by up to 1.0 V for up to 20 ms, or by 0.7 V for up to 40 ms. Excursions beyond 1.0 V or 40 ms are not supported.

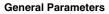

- 5. This is a DC specifications only. V<sub>in</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

Figure 2 shows the allowable undershoot and overshoot voltage on the MPC755.

of t<sub>SYSCLK</sub>

The MPC755 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC755 core voltage must always be provided at nominal 2.0 V (see Table 3 for actual recommended core voltage). Voltage to the L2 I/Os and processor interface I/Os are provided through separate sets of supply pins and may be provided at the voltages shown in Table 2. The input voltage threshold for each bus is selected by sampling the state of the voltage select pins BVSEL and L2VSEL during operation. These signals must remain stable during part operation and cannot change. The output voltage will swing from GND to the maximum voltage applied to the  $OV_{DD}$  or  $L2OV_{DD}$  power pins.

Table 2 describes the input threshold voltage setting.

| Table 2. | Input | Threshold | Voltage | Setting |

|----------|-------|-----------|---------|---------|

|----------|-------|-----------|---------|---------|

| Part<br>Revision | BVSEL Signal | Processor Bus<br>Interface Voltage | L2VSEL Signal | L2 Bus<br>Interface Voltage |

|------------------|--------------|------------------------------------|---------------|-----------------------------|

| E                | 0            | Not Available                      | 0             | Not Available               |

|                  | 1            | 2.5 V/3.3 V                        | 1             | 2.5 V/3.3 V                 |

Caution: The input threshold selection must agree with the  $OV_{DD}/L2OV_{DD}$  voltages supplied.

**Note:** The input threshold settings above are different for all revisions prior to Rev. 2.8 (Rev. E). For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

Table 3 provides the recommended operating conditions for the MPC755.

|                          |               |                    |         | Recomme            | nded Value |                    |      |       |

|--------------------------|---------------|--------------------|---------|--------------------|------------|--------------------|------|-------|

| Characteristic           |               | Symbol             | 300 MHz | , 350 MHz          | 400        | MHz                | Unit | Notes |

|                          |               |                    | Min     | Мах                | Min        | Мах                |      |       |

| Core supply voltage      |               | V <sub>DD</sub>    | 1.80    | 2.10               | 1.90       | 2.10               | V    | 3     |

| PLL supply voltage       |               | AV <sub>DD</sub>   | 1.80    | 2.10               | 1.90       | 2.10               | V    | 3     |

| L2 DLL supply voltage    |               | L2AV <sub>DD</sub> | 1.80    | 2.10               | 1.90       | 2.10               | V    | 3     |

| Processor bus supply     | BVSEL = 1     | OV <sub>DD</sub>   | 2.375   | 2.625              | 2.375      | 2.625              | V    | 2, 4  |

| voltage                  |               |                    | 3.135   | 3.465              | 3.135      | 3.465              |      | 5     |

| L2 bus supply voltage    | L2VSEL = 1    | L2OV <sub>DD</sub> | 2.375   | 2.625              | 2.375      | 2.625              | V    | 2, 4  |

|                          |               |                    | 3.135   | 3.465              | 3.135      | 3.465              |      | 5     |

| Input voltage            | Processor bus | V <sub>in</sub>    | GND     | OV <sub>DD</sub>   | GND        | OV <sub>DD</sub>   | V    |       |

|                          | L2 bus        | V <sub>in</sub>    | GND     | L2OV <sub>DD</sub> | GND        | L2OV <sub>DD</sub> | V    |       |

|                          | JTAG signals  | V <sub>in</sub>    | GND     | OV <sub>DD</sub>   | GND        | OV <sub>DD</sub>   | V    |       |

| Die-junction temperature |               | Тj                 | 0       | 105                | 0          | 105                | °C   |       |

#### Table 3. Recommended Operating Conditions<sup>1</sup>

#### Notes:

1. These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

2. Revisions prior to Rev. 2.8 (Rev. E) offered different I/O voltage support. For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

3. 2.0 V nominal.

4. 2.5 V nominal.

5. 3.3 V nominal.

Table 4 provides the package thermal characteristics for the MPC755 and MPC745. The MPC755 was initially sampled in a CBGA package, but production units are currently provided in both a CBGA and a PBGA package. Because of the better long-term device-to-board interconnect reliability of the PBGA package, Freescale recommends use of a PBGA package except where circumstances dictate use of a CBGA package. The MPC745 is offered in a PBGA package only.

| Characteristic                                                                         | Symbol              | MPC755<br>CBGA | MPC755<br>PBGA | MPC745<br>PBGA | Unit | Notes |

|----------------------------------------------------------------------------------------|---------------------|----------------|----------------|----------------|------|-------|

| Junction-to-ambient thermal resistance, natural convection                             | R <sub>θJA</sub>    | 24             | 31             | 34             | °C/W | 1, 2  |

| Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board    | R <sub>θJMA</sub>   | 17             | 25             | 26             | °C/W | 1, 3  |

| Junction-to-ambient thermal resistance, 200 ft/min airflow, single-layer (1s) board    | R <sub>θJMA</sub>   | 18             | 25             | 27             | °C/W | 1, 3  |

| Junction-to-ambient thermal resistance, 200 ft/min<br>airflow, four-layer (2s2p) board | R <sub>θJMA</sub>   | 14             | 21             | 22             | °C/W | 1, 3  |

| Junction-to-board thermal resistance                                                   | $R_{\theta JB}$     | 8              | 17             | 17             | °C/W | 4     |

| Junction-to-case thermal resistance                                                    | $R_{	ext{	heta}JC}$ | <0.1           | <0.1           | <0.1           | °C/W | 5     |

#### Table 4. Package Thermal Characteristics <sup>6</sup>

Notes:

1. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. The actual value of  $R_{\theta JC}$  for the part is less than 0.1°C/W.

6. Refer to Section 8.8, "Thermal Management Information," for more details about thermal management.

The MPC755 incorporates a thermal management assist unit (TAU) composed of a thermal sensor, digital-to-analog converter, comparator, control logic, and dedicated special-purpose registers (SPRs). See the *MPC750 RISC Microprocessor Family User's Manual* for more information on the use of this feature. Specifications for the thermal sensor portion of the TAU are found in Table 5.

#### **Table 5. Thermal Sensor Specifications**

At recommended operating conditions (see Table 3)

| Characteristic           | Min | Мах | Unit | Notes |

|--------------------------|-----|-----|------|-------|

| Temperature range        | 0   | 127 | °C   | 1     |

| Comparator settling time | 20  | _   | μs   | 2, 3  |

| Resolution               | 4   | _   | °C   | 3     |

| Accuracy                 | -12 | +12 | °C   | 3     |

Notes:

- 1. The temperature is the junction temperature of the die. The thermal assist unit's raw output does not indicate an absolute temperature, but must be interpreted by software to derive the absolute junction temperature. For information about the use and calibration of the TAU, see Freescale Application Note AN1800/D, *Programming the Thermal Assist Unit in the MPC750 Microprocessor.*

- 2. The comparator settling time value must be converted into the number of CPU clocks that need to be written into the THRM3 SPR.

- 3. Guaranteed by design and characterization.

#### Table 6 provides the DC electrical characteristics for the MPC755.

#### **Table 6. DC Electrical Specifications**

At recommended operating conditions (see Table 3)

| Characteristic                                                                   | Nominal<br>Bus<br>Voltage <sup>1</sup> | Symbol           | Min  | Max                        | Unit | Notes   |

|----------------------------------------------------------------------------------|----------------------------------------|------------------|------|----------------------------|------|---------|

| Input high voltage (all inputs except SYSCLK)                                    | 2.5                                    | V <sub>IH</sub>  | 1.6  | (L2)OV <sub>DD</sub> + 0.3 | V    | 2, 3    |

|                                                                                  | 3.3                                    | V <sub>IH</sub>  | 2.0  | (L2)OV <sub>DD</sub> + 0.3 | V    | 2, 3    |

| Input low voltage (all inputs except SYSCLK)                                     | 2.5                                    | V <sub>IL</sub>  | -0.3 | 0.6                        | V    | 2       |

|                                                                                  | 3.3                                    | V <sub>IL</sub>  | -0.3 | 0.8                        | V    |         |

| SYSCLK input high voltage                                                        | 2.5                                    | KV <sub>IH</sub> | 1.8  | OV <sub>DD</sub> + 0.3     | V    |         |

|                                                                                  | 3.3                                    | KV <sub>IH</sub> | 2.4  | OV <sub>DD</sub> + 0.3     | V    |         |

| SYSCLK input low voltage                                                         | 2.5                                    | κν <sub>il</sub> | -0.3 | 0.4                        | V    |         |

|                                                                                  | 3.3                                    | κν <sub>il</sub> | -0.3 | 0.4                        | V    |         |

| Input leakage current,<br>V <sub>in</sub> = L2OV <sub>DD</sub> /OV <sub>DD</sub> |                                        | l <sub>in</sub>  | _    | 10                         | μΑ   | 2, 3    |

| High-Z (off-state) leakage current,<br>$V_{in} = L2OV_{DD}/OV_{DD}$              |                                        | I <sub>TSI</sub> | _    | 10                         | μΑ   | 2, 3, 5 |

| Output high voltage, I <sub>OH</sub> = -6 mA                                     | 2.5                                    | V <sub>OH</sub>  | 1.7  | —                          | V    |         |

|                                                                                  | 3.3                                    | V <sub>OH</sub>  | 2.4  | —                          | V    |         |

| Output low voltage, I <sub>OL</sub> = 6 mA                                       | 2.5                                    | V <sub>OL</sub>  | —    | 0.45                       | V    |         |

|                                                                                  | 3.3                                    | V <sub>OL</sub>  | _    | 0.4                        | V    |         |

#### Table 6. DC Electrical Specifications (continued)

At recommended operating conditions (see Table 3)

| Characteristic                                | Nominal<br>Bus<br>Voltage <sup>1</sup> | Symbol          | Min | Max | Unit | Notes |

|-----------------------------------------------|----------------------------------------|-----------------|-----|-----|------|-------|

| Capacitance, V <sub>in</sub> = 0 V, f = 1 MHz |                                        | C <sub>in</sub> | —   | 5.0 | pF   | 3, 4  |

Notes:

1. Nominal voltages; see Table 3 for recommended operating conditions.

2. For processor bus signals, the reference is OV<sub>DD</sub> while L2OV<sub>DD</sub> is the reference for the L2 bus signals.

3. Excludes test signals (LSSD\_MODE, L1\_TSTCLK, L2\_TSTCLK) and IEEE 1149.1 boundary scan (JTAG) signals.

4. Capacitance is periodically sampled rather than 100% tested.

5. The leakage is measured for nominal  $OV_{DD}$  and  $V_{DD}$ , or both  $OV_{DD}$  and  $V_{DD}$  must vary in the same direction (for example, both  $OV_{DD}$  and  $V_{DD}$  vary by either +5% or -5%).

Table 7 provides the power consumption for the MPC755.

| Table 7. Power Consumption for MPC75 | 55 |

|--------------------------------------|----|

|--------------------------------------|----|

| Proc              | essor (CPU) Freq                                                                                                                          | uency                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 300 MHz           | 350 MHz                                                                                                                                   | 400 MHz                                                                                                                                                                                                                                                                                                           | Unit                                                                                                                                                                                                                                                                                                                      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Full-Powe         | er Mode                                                                                                                                   |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1               | 3.6                                                                                                                                       | 5.4                                                                                                                                                                                                                                                                                                               | W                                                                                                                                                                                                                                                                                                                         | 1, 3, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.5               | 6.0                                                                                                                                       | 8.0                                                                                                                                                                                                                                                                                                               | W                                                                                                                                                                                                                                                                                                                         | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Doze M            | lode                                                                                                                                      |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.8               | 2.0                                                                                                                                       | 2.3                                                                                                                                                                                                                                                                                                               | W                                                                                                                                                                                                                                                                                                                         | 1, 2, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Nap M             | lode                                                                                                                                      |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.0               | 1.0                                                                                                                                       | 1.0                                                                                                                                                                                                                                                                                                               | W                                                                                                                                                                                                                                                                                                                         | 1, 2, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Sleep I           | Mode                                                                                                                                      |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 550               | 550                                                                                                                                       | 550                                                                                                                                                                                                                                                                                                               | mW                                                                                                                                                                                                                                                                                                                        | 1, 2, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Sleep Mode (PLL a | nd DLL Disabled)                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 510               | 510                                                                                                                                       | 510                                                                                                                                                                                                                                                                                                               | mW                                                                                                                                                                                                                                                                                                                        | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | 300 MHz       Full-Powe       3.1       4.5       Doze M       1.8       Nap M       1.0       Sleep I       550       Sleep Mode (PLL a) | 300 MHz         350 MHz           S300 MHz         350 MHz           Full-Power Mode         3.1           3.1         3.6           4.5         6.0           Doze Mode         0           1.8         2.0           Nap Mode         1.0           1.0         1.0           Sleep Mode (PLL and DLL Disabled) | Full-Power Mode         Full-Power Mode         3.1       3.6       5.4         4.5       6.0       8.0         Doze Mode         Doze Mode         1.8       2.0       2.3         Nap Mode         1.0       1.0       1.0         Sleep Mode         550       550       550         Sleep Mode (PLL and DLL Disabled) | Image: State of the s |

Notes:

1. These values apply for all valid processor bus and L2 bus ratios. The values do not include I/O supply power ( $OV_{DD}$  and  $L2OV_{DD}$ ) or PLL/DLL supply power ( $AV_{DD}$  and  $L2AV_{DD}$ ).  $OV_{DD}$  and  $L2OV_{DD}$  power is system dependent, but is typically <10% of  $V_{DD}$  power. Worst case power consumption for  $AV_{DD}$  = 15 mW and  $L2AV_{DD}$  = 15 mW.

Maximum power is measured at nominal V<sub>DD</sub> (see Table 3) while running an entirely cache-resident, contrived sequence of instructions which keep the execution units maximally busy.

3. Typical power is an average value measured at the nominal recommended V<sub>DD</sub> (see Table 3) and 65°C in a system while running a typical code sequence.

4. Not 100% tested. Characterized and periodically sampled.

## 4.2 AC Electrical Characteristics

This section provides the AC electrical characteristics for the MPC755. After fabrication, functional parts are sorted by maximum processor core frequency as shown in Section 4.2.1, "Clock AC Specifications," and tested for conformance to the AC specifications for that frequency. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG[0:3] signals. Parts are sold by maximum processor core frequency; see Section 10, "Ordering Information."

### 4.2.1 Clock AC Specifications

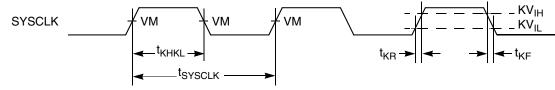

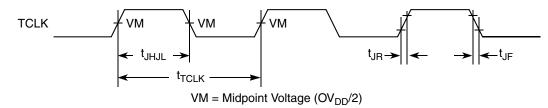

Table 8 provides the clock AC timing specifications as defined in Figure 3.

| Table 8. Clock AC Timing Specification | Table 8. Cl | lock AC | Timina S | Specifications |

|----------------------------------------|-------------|---------|----------|----------------|

|----------------------------------------|-------------|---------|----------|----------------|

At recommended operating conditions (see Table 3)

|                                           |                                            |     | Maximum | Process | or Core F | requency | ,    |      |       |

|-------------------------------------------|--------------------------------------------|-----|---------|---------|-----------|----------|------|------|-------|

| Characteristic                            | Symbol                                     | 300 | MHz     | 350     | MHz       | 400      | MHz  | Unit | Notes |

|                                           |                                            | Min | Max     | Min     | Max       | Min      | Max  |      |       |

| Processor frequency                       | f <sub>core</sub>                          | 200 | 300     | 200     | 350       | 200      | 400  | MHz  | 1     |

| VCO frequency                             | f <sub>VCO</sub>                           | 400 | 600     | 400     | 700       | 400      | 800  | MHz  | 1     |

| SYSCLK frequency                          | f <sub>SYSCLK</sub>                        | 25  | 100     | 25      | 100       | 25       | 100  | MHz  | 1     |

| SYSCLK cycle time                         | t <sub>SYSCLK</sub>                        | 10  | 40      | 10      | 40        | 10       | 40   | ns   |       |

| SYSCLK rise and fall time                 | t <sub>KR</sub> , t <sub>KF</sub>          | —   | 2.0     | —       | 2.0       | —        | 2.0  | ns   | 2     |

|                                           | t <sub>KR</sub> , t <sub>KF</sub>          | —   | 1.4     | —       | 1.4       | —        | 1.4  | ns   | 2     |

| SYSCLK duty cycle measured at $OV_{DD}/2$ | t <sub>KHKL</sub> /<br>t <sub>SYSCLK</sub> | 40  | 60      | 40      | 60        | 40       | 60   | %    | 3     |

| SYSCLK jitter                             |                                            | —   | ±150    | —       | ±150      | —        | ±150 | ps   | 3, 4  |

| Internal PLL relock time                  |                                            | —   | 100     | —       | 100       | —        | 100  | μS   | 3, 5  |

#### Notes:

- 1. **Caution:** The SYSCLK frequency and PLL\_CFG[0:3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:3] signal description in Section 8.1, "PLL Configuration," for valid PLL\_CFG[0:3] settings.

- Rise and fall times measurements are now specified in terms of slew rates, rather than time to account for selectable I/O bus interface levels. The minimum slew rate of 1 V/ns is equivalent to a 2 ns maximum rise/fall time measured at 0.4 and 2.4 V (OV<sub>DD</sub> = 3.3 V) or a rise/fall time of 1 ns measured at 0.4 and 1.8 V (OV<sub>DD</sub> = 2.5 V).

- 3. Timing is guaranteed by design and characterization.

- 4. This represents total input jitter-short term and long term combined-and is guaranteed by design.

- 5. Relock timing is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

Figure 3 provides the SYSCLK input timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 3. SYSCLK Input Timing Diagram

### 4.2.2 **Processor Bus AC Specifications**

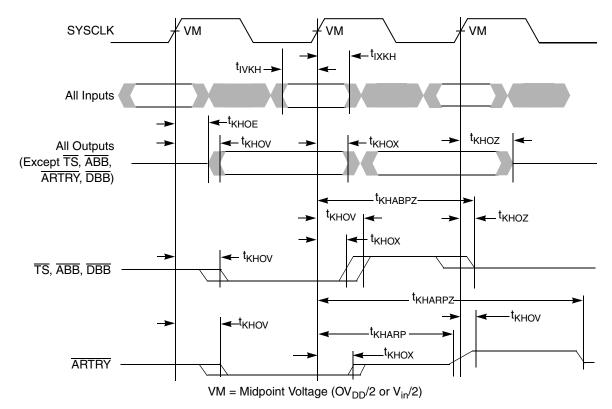

Table 9 provides the processor bus AC timing specifications for the MPC755 as defined in Figure 4 and Figure 6. Timing specifications for the L2 bus are provided in Section 4.2.3, "L2 Clock AC Specifications."

#### Table 9. Processor Bus Mode Selection AC Timing Specifications<sup>1</sup>

At recommended operating conditions (see Table 3)

| Parameter                         | Symbol <sup>2</sup> | All Spee | d Grades | Unit                | Notes            |

|-----------------------------------|---------------------|----------|----------|---------------------|------------------|

| i arameter                        | Symbol              | Min      | Max      | Onit                | Notes            |

| Mode select input setup to HRESET | t <sub>MVRH</sub>   | 8        | _        | t <sub>sysclk</sub> | 3, 4, 5,<br>6, 7 |

| HRESET to mode select input hold  | t <sub>MXRH</sub>   | 0        | _        | ns                  | 3, 4, 6,<br>7, 8 |

#### Notes:

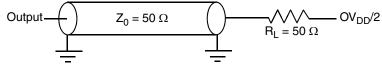

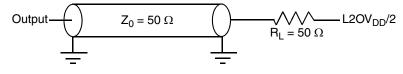

- All input specifications are measured from the midpoint of the signal in question to the midpoint of the rising edge of the input SYSCLK. All output specifications are measured from the midpoint of the rising edge of SYSCLK to the midpoint of the signal in question. All output timings assume a purely resistive 50-Ω load (see Figure 5). Input and output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbology used for timing specifications herein follows the pattern of t<sub>(signal)(state)(reference)(state)</sub> for inputs and t<sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>IVKH</sub> symbolizes the time input signals (I) reach the valid state (V) relative to the SYSCLK reference (K) going to the high (H) state or input setup time. And t<sub>KHOV</sub> symbolizes the time from SYSCLK (K) going high (H) until outputs (O) are valid (V) or output valid time. Input hold time can be read as the time that the input signal (I) went invalid (X) with respect to the rising clock edge (KH)—note the position of the reference and its state for inputs—and output hold time can be read as the time from the rising edge (KH) until the output went invalid (OX).

- 3. The setup and hold time is with respect to the rising edge of HRESET (see Figure 4).

- 4. This specification is for configuration mode select only. Also note that the HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

- 5. t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 6. Mode select signals are BVSEL, L2VSEL, PLL\_CFG[0:3], and TLBISYNC.

- 7. Guaranteed by design and characterization.

- 8. Bus mode select pins must remain stable during operation. Changing the logic states of BVSEL or L2VSEL during operation will cause the bus mode voltage selection to change. Changing the logic states of the PLL\_CFG pins during operation will cause the PLL division ratio selection to change. Both of these conditions are considered outside the specification and are not supported. Once HRESET is negated the states of the bus mode selection pins must remain stable.

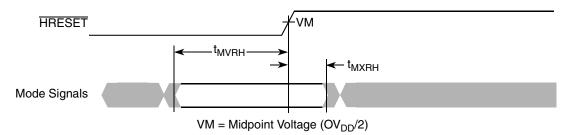

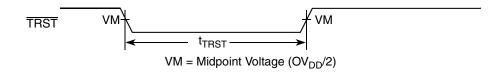

Figure 4 provides the mode select input timing diagram for the MPC755.

Figure 4. Mode Input Timing Diagram

Figure 5 provides the AC test load for the MPC755.

Figure 5. AC Test Load

#### Table 10. Processor Bus AC Timing Specifications <sup>1</sup>

At recommended operating conditions (see Table 3)

| Devenuetor                                                   | Cumbal              | All Spee | d Grades | 11 14               | Neter   |

|--------------------------------------------------------------|---------------------|----------|----------|---------------------|---------|

| Parameter                                                    | Symbol              | Min      | Max      | Unit                | Notes   |

| Setup times: All inputs                                      | t <sub>IVKH</sub>   | 2.5      | _        | ns                  |         |

| Input hold times: TLBISYNC, MCP, SMI                         | t <sub>IXKH</sub>   | 0.6      | —        | ns                  | 6       |

| Input hold times: All inputs, except TLBISYNC, MCP, SMI      | t <sub>IXKH</sub>   | 0.2      | —        | ns                  | 6       |

| Valid times: All outputs                                     | t <sub>KHOV</sub>   | —        | 4.1      | ns                  |         |

| Output hold times: All outputs                               | t <sub>KHOX</sub>   | 1.0      | —        | ns                  |         |

| SYSCLK to output enable                                      | t <sub>KHOE</sub>   | 0.5      | —        | ns                  | 2       |

| SYSCLK to output high impedance (all except ABB, ARTRY, DBB) | t <sub>KHOZ</sub>   | —        | 6.0      | ns                  | 2       |

| SYSCLK to ABB, DBB high impedance after precharge            | t <sub>KHABPZ</sub> | —        | 1.0      | t <sub>sysclk</sub> | 2, 3, 4 |

| Maximum delay to ARTRY precharge                             | t <sub>KHARP</sub>  | —        | 1        | t <sub>sysclk</sub> | 2, 3, 5 |

| SYSCLK to ARTRY high impedance after precharge               | t <sub>KHARPZ</sub> | —        | 2        | t <sub>sysclk</sub> | 2, 3, 5 |

#### Notes:

1. Revisions prior to Rev. 2.8 (Rev. E) were limited in performance and did not conform to this specification. For more information, refer to Section 10.2, "Part Numbers Not Fully Addressed by This Document."

- 2. Guaranteed by design and characterization.

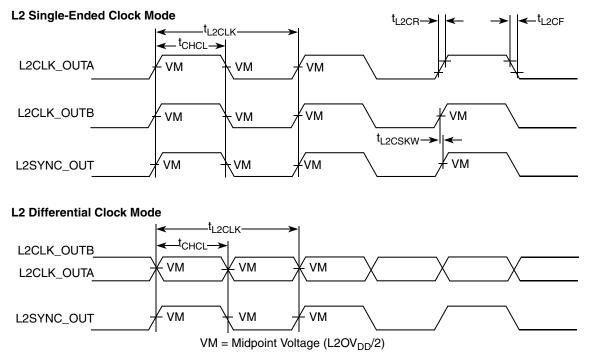

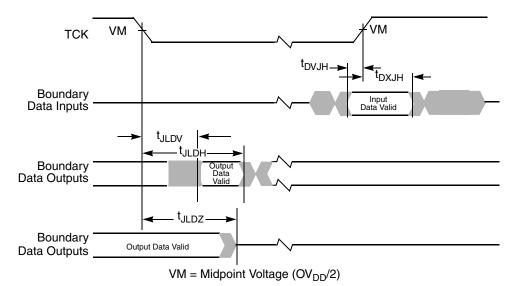

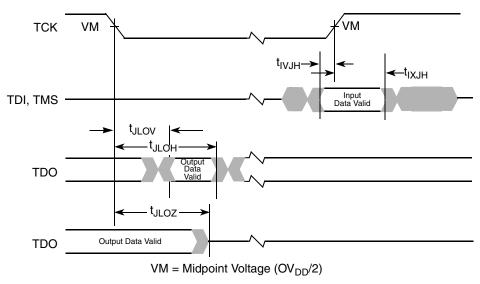

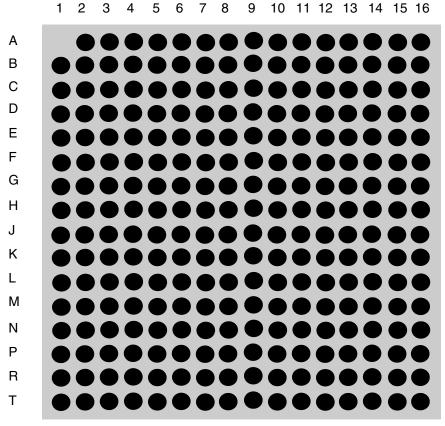

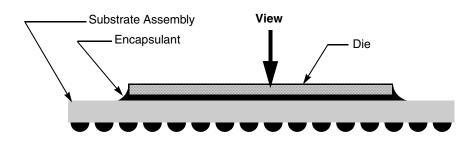

- 3. t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.