## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## MRF24J40 Data Sheet

IEEE 802.15.4<sup>™</sup> 2.4 GHz RF Transceiver

$\ensuremath{\textcircled{}^{\odot}}$  2010 Microchip Technology Inc.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-459-9

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### IEEE 802.15.4<sup>™</sup> 2.4 GHz RF Transceiver

#### Features:

- IEEE 802.15.4™ Standard Compliant RF Transceiver

- Supports ZigBee<sup>®</sup>, MiWi™, MiWi P2P and Proprietary Wireless Networking Protocols

- Simple, 4-Wire Serial Peripheral Interface (SPI)

- Integrated 20 MHz and 32.768 kHz Crystal Oscillator Circuitry

- Low-Current Consumption:

- RX mode: 19 mA (typical)

- TX mode: 23 mA (typical)

- Sleep: 2 µA (typical)

- Small, 40-Pin Leadless QFN 6x6 mm<sup>2</sup> Package

#### **RF/Analog Features:**

- · ISM Band 2.405-2.48 GHz Operation

- Data Rate: 250 kbps (IEEE 802.15.4); 625 kbps (Turbo mode)

- -95 dBm Typical Sensitivity with +5 dBm Maximum Input Level

- +0 dBm Typical Output Power with 36 dB TX Power Control Range

- Differential RF Input/Output with Integrated TX/RX Switch

- Integrated Low Phase Noise VCO, Frequency Synthesizer and PLL Loop Filter

- Digital VCO and Filter Calibration

- Integrated RSSI ADC and I/Q DACs

- Integrated LDO

- · High Receiver and RSSI Dynamic Range

#### **MAC/Baseband Features:**

- Hardware CSMA-CA Mechanism, Automatic Acknowledgement Response and FCS Check

- Independent Beacon, Transmit and GTS FIFO

- · Supports all CCA modes and RSSI/ED

- · Automatic Packet Retransmit Capability

- Hardware Security Engine (AES-128) with CTR, CCM and CBC-MAC modes

- Supports Encryption and Decryption for MAC Sublayer and Upper Layer

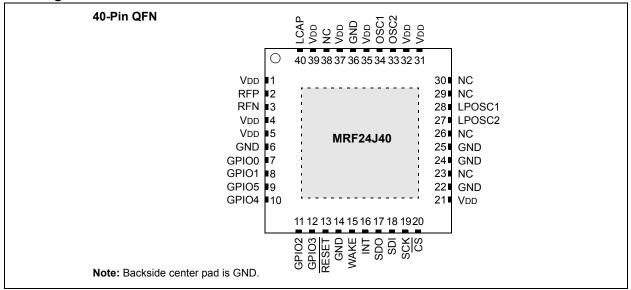

#### Pin Diagram:

## **MRF24J40**

| 1.0                                  | Overview                      | 5     |  |  |  |

|--------------------------------------|-------------------------------|-------|--|--|--|

| 2.0                                  | Hardware Description          | 7     |  |  |  |

|                                      | Functional Description        |       |  |  |  |

| 4.0                                  | Applications                  | . 135 |  |  |  |

| 5.0                                  | Electrical Characteristics    | . 141 |  |  |  |

| 6.0                                  | Packaging Information         | . 145 |  |  |  |

| Appe                                 | ndix A: Revision History      | . 147 |  |  |  |

| Index                                |                               | . 149 |  |  |  |

| The N                                | licrochip Web Site            | . 153 |  |  |  |

| Customer Change Notification Service |                               |       |  |  |  |

| Customer Support                     |                               |       |  |  |  |

| Reader Response                      |                               |       |  |  |  |

|                                      | Product Identification System |       |  |  |  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

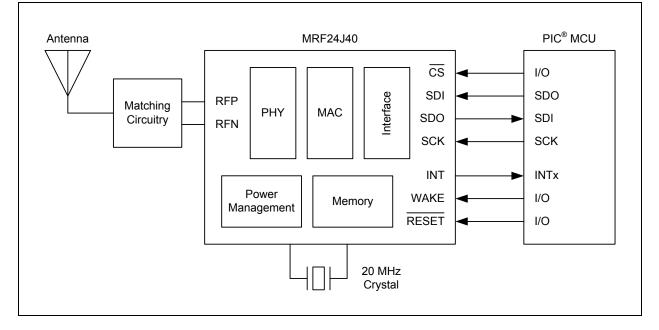

#### 1.0 OVERVIEW

The MRF24J40 is an IEEE 802.15.4<sup>™</sup> Standard compliant 2.4 GHz RF transceiver. It integrates the PHY and MAC functionality in a single chip solution. Figure 1-1 shows a simplified block diagram of a MRF24J40 wireless node. The MRF24J40 creates a low-cost, low-power, low data rate (250 or 625 kbps) Wireless Personal Area Network (WPAN) device. The MRF24J40 interfaces to many popular Microchip PIC<sup>®</sup> microcontrollers via a 4-wire serial SPI interface, interrupt, wake and Reset pins.

The MRF24J40 provides hardware support for:

- · Energy Detection

- Carrier Sense

- Three CCA Modes

- CSMA-CA Algorithm

- Automatic Packet Retransmission

- · Automatic Acknowledgment

- Independent Transmit, Beacon and GTS FIFO Buffers

- Security Engine supports Encryption and Decryption for MAC Sublayer and Upper Layer

These features reduce the processing load, allowing the use of low-cost 8-bit microcontrollers.

The MRF24J40 is compatible with Microchip's ZigBee<sup>®</sup>, MiWi™ and MiWi P2P software stacks. Each software stack is available as a free download, including source code, from the Microchip web site: http://www.microchip.com/wireless.

FIGURE 1-1: WIRELESS NODE BLOCK DIAGRAM

#### 1.1 IEEE 802.15.4-2003 Standard

The MRF24J40 is compliant with the IEEE 802.15.4<sup>™</sup>-2003 Standard. The Standard specifies the physical (PHY) and Media Access Controller (MAC) functions that form the basis for a wireless network device. Figure 1-2 shows the structure of the PHY packet and MAC frame.

It is highly recommended that the design engineer be familiar with the IEEE 802.15.4-2003 Standard in order to best understand the configuration and operation of the MRF24J40. The Standard can be downloaded from the IEEE web site: http://www.ieee.org.

#### FIGURE 1-2: IEEE 802.15.4<sup>™</sup> PHY PACKET AND MAC FRAME STRUCTURE

|                  |                      |                   |                 | 2                | 1                  | 2 octe              | ets                         |               |                              |                |     |        |

|------------------|----------------------|-------------------|-----------------|------------------|--------------------|---------------------|-----------------------------|---------------|------------------------------|----------------|-----|--------|

| MAC Sublayer     | Ack                  | nowledgn<br>Frame | nent            | Frame<br>Control | Sequence<br>Number | FCS                 |                             |               |                              |                |     |        |

|                  |                      |                   |                 | М                | HR                 | MFR                 |                             |               |                              |                |     |        |

|                  |                      |                   |                 |                  |                    |                     |                             |               |                              |                | ·   |        |

|                  |                      |                   |                 | 2                | 1                  | 4 to 20             |                             |               | n                            |                | 2   | octets |

| MAC Sublayer     |                      | Data<br>Frame     |                 | Frame<br>Control | Sequence<br>Number | Adressing<br>Fields |                             |               | Data Payload                 |                | FCS |        |

|                  |                      |                   |                 |                  | M                  | łR                  |                             |               | MSDU                         |                | MFR |        |

|                  |                      |                   |                 | 2                | 1                  | 4 to 20             | 1                           |               | r                            | n              | 2   | octets |

| MAC Sublayer     | MAC Command<br>Frame |                   | and             | Frame<br>Control | Sequence<br>Number | Adressing<br>Fields | Command<br>Type             |               | Command                      | d Payload      | FCS |        |

|                  |                      |                   |                 |                  | M                  | IR                  |                             |               | MSDU                         |                | MFR |        |

|                  |                      |                   |                 | 2                | 1                  | 4 or 10             | 2                           | k             | m                            | п              | 2   | octets |

| MAC Sublayer     |                      | Beacon<br>Frame   |                 | Frame<br>Control | Sequence<br>Number | Adressing<br>Fields | Superframe<br>Specification | GTS<br>Fields | Pending<br>Address<br>Fields | Beacon Payload | FCS |        |

|                  |                      |                   |                 |                  | M                  | IR                  |                             |               | MSDU                         |                | MFR |        |

|                  | 4                    | 1                 | 1               | 1                |                    |                     |                             | 5 – 127       |                              |                |     | octets |

| PHY Layer        | Preamble             | SFD               | Frame<br>Length |                  |                    |                     |                             | PSDU          |                              |                |     |        |

|                  | SI                   | IR                | PHR             |                  |                    |                     |                             | PHY Payload   |                              |                |     |        |

|                  | i<br>!               |                   |                 |                  |                    |                     |                             |               |                              |                |     |        |

| On air<br>packet |                      |                   |                 |                  |                    |                     | PPDU                        |               |                              |                |     |        |

#### 2.0 HARDWARE DESCRIPTION

#### 2.1 2.1 Overview

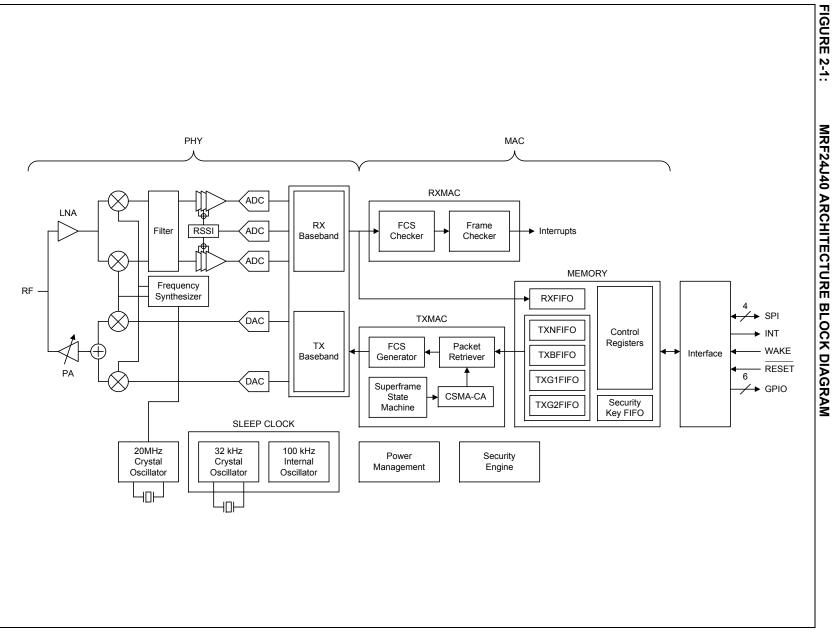

The MRF24J40 is an IEEE 802.15.4 Standard compliant 2.4 GHz RF transceiver. It integrates the PHY and MAC functionality in a single chip solution. Figure 2-1 is a block diagram of the MRF24J40 circuitry.

A frequency synthesizer is clocked by an external 20 MHz crystal and generates a 2.4 GHz RF frequency.

The receiver is a low-IF architecture consisting of a Low Noise Amplifier (LNA), down conversion mixers, polyphase channel filters and baseband limiting amplifiers with a Receiver Signal Strength Indicator (RSSI).

The transmitter is a direct conversion architecture with a 0 dBm maximum output (typical) and 36 dB power control range.

An internal Transmit/Receive (TR) switch combines the transmitter and receiver circuits into differential RFP and RFN pins. These pins are connected to impedance matching circuitry (balun) and antenna. An external Power Amplifier (PA) and/or LNA can be controlled via the GPIO pins.

Six General Purpose Input/Output (GPIO) pins can be configured for control or monitoring purposes. They can also be configured to control external PA/LNA RF switches.

The power management circuitry consists of an integrated Low Dropout (LDO) voltage regulator. The MRF24J40 can be placed into a very low-current (2  $\mu$ A typical) Sleep mode. An internal 100 kHz oscillator or 32 kHz external crystal oscillator can be used for Sleep mode timing.

The Media Access Controller (MAC) circuitry verifies reception and formats for transmission IEEE 802.15.4 Standard compliant packets. Data is buffered in Transmit and Receive FIFOs. Carrier Sense Multiple Access-Collision Avoidance (CSMA-CA), superframe constructor, receive frame filter and security engine functionality are implemented in hardware. The security engine provides hardware circuitry for AES-128 with CTR, CCM and CBC-MAC modes.

Control of the transceiver is via a 4-wire SPI, interrupt, wake and Reset pins.

# 2.2 **Block Diagram**

MRF24J40 ARCHITECTURE BLOCK DIAGRAM

DS39776C-page 8

#### 2.3 Pin Descriptions

| TABLE 2-1: | MRF24J40 PIN DESCRIPTIONS |

|------------|---------------------------|

|            |                           |

| D P N D D D D 00 01 05 04 02 03 ET D C T                              | Power<br>AIO<br>Power<br>Power<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO | RF power supply. Bypass with a capacitor as close to the pin as possible.<br>Differential RF input/output (+).<br>Differential RF input/output (-).<br>RF power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring ground.<br>General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O. |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N<br>D<br>D<br>00<br>01<br>05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T | AIO<br>Power<br>Ground<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO                       | Differential RF input/output (-).<br>RF power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring ground.<br>General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.                                                   |

| D<br>D<br>D<br>O1<br>O5<br>O4<br>O2<br>O3<br>ET<br>D<br>KE<br>T       | Power<br>Power<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO                               | RF power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring ground.<br>General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.                                                                                        |

| D<br>D<br>00<br>01<br>05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T      | Power<br>Ground<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO                                     | Guard ring power supply. Bypass with a capacitor as close to the pin as possible.<br>Guard ring ground.<br>General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.                                                                                                                                                         |

| D<br>00<br>05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T                 | Ground<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO                                              | Guard ring ground.<br>General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O, also used as external TX/RX switch control.                                                                                                                                                                                                                                  |

| 00<br>01<br>05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T                | DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DI                                                  | General purpose digital I/O, also used as external PA enable.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.                                                                                                                                                                                                                                                                                                    |

| 01<br>05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T                      | DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DIO                                                               | General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.                                                                                                                                                                                                                                                                                                                                                                     |

| 05<br>04<br>02<br>03<br>ET<br>D<br>KE<br>T                            | DIO<br>DIO<br>DIO<br>DIO<br>DIO<br>DI                                                                | General purpose digital I/O.<br>General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 04<br>02<br>03<br>ET<br>D<br>KE<br>T                                  | DIO<br>DIO<br>DIO<br>DI                                                                              | General purpose digital I/O.<br>General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 02<br>03<br>ET<br>D<br>KE<br>T                                        | DIO<br>DIO<br>DI                                                                                     | General purpose digital I/O, also used as external TX/RX switch control.<br>General purpose digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| O3<br>ET<br>D<br>KE<br>T                                              | DIO<br>DI                                                                                            | General purpose digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ET<br>D<br>KE<br>T                                                    | DI                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D<br>KE<br>T                                                          |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| KE<br>T                                                               | Ground                                                                                               | Global hardware Reset pin active-low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Т                                                                     | 0.00110                                                                                              | Ground for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                       | DI                                                                                                   | External wake-up trigger (must be enabled in software).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ~                                                                     | DO                                                                                                   | Interrupt pin to microcontroller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                                                                     | DO                                                                                                   | Serial interface data output from MRF24J40.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| )                                                                     | DI                                                                                                   | Serial interface data input to MRF24J40.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| K                                                                     | DI                                                                                                   | Serial interface clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5                                                                     | DI                                                                                                   | Serial interface enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D                                                                     | Power                                                                                                | Digital circuit power supply. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D                                                                     | Ground                                                                                               | Ground for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2                                                                     |                                                                                                      | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D                                                                     | Ground                                                                                               | Ground for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D                                                                     | Ground                                                                                               | Ground for digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2                                                                     |                                                                                                      | No Connection. (Allow pin to float; do not connect signal.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SC2                                                                   | AI                                                                                                   | 32 kHz crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SC1                                                                   | AI                                                                                                   | 32 kHz crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| )                                                                     |                                                                                                      | No Connection. (Allow pin to float; do not connect signal.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| )                                                                     | _                                                                                                    | No Connection. (Allow pin to float; do not connect signal.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D                                                                     | Power                                                                                                | Power supply for band gap reference circuit. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D                                                                     | Power                                                                                                | Power supply for analog circuit. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C2                                                                    | AI                                                                                                   | 20 MHz crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C1                                                                    | AI                                                                                                   | 20 MHz crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D                                                                     | Power                                                                                                | PLL power supply. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D                                                                     | Ground                                                                                               | Ground for PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D                                                                     | Power                                                                                                | Charge pump power supply. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                       | —                                                                                                    | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                                                                     | Power                                                                                                | VCO supply. Bypass with a capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C<br>D                                                                | _                                                                                                    | PLL loop filter external capacitor. Connected to external 100 pF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D<br>D                                                                | 1<br>)<br>)<br>>                                                                                     | 1 Al<br>Power<br>O Ground<br>Power<br>—<br>Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

**Legend:** A = Analog, D = Digital, I = Input, O = Output

#### 2.4 Power and Ground Pins

Recommended bypass capacitors are listed in Table 2-2. VDD pins 1 and 31 require two bypass capacitors to ensure sufficient bypass decoupling. Minimize trace length from the VDD pin to the bypass capacitors and make them as short as possible.

| <b>TABLE 2-2:</b> | RECOMMENDED BYPASS |

|-------------------|--------------------|

|                   | CAPACITOR VALUES   |

| VDD Pin | Bypass Capacitor  |

|---------|-------------------|

| 1       | 47 pF and 0.01 μF |

| 4       | 47 pF             |

| 5       | 0.1 μF            |

| 21      | 0.01 μF           |

| 31      | 47 pF and 0.01 μF |

| 32      | 47 pF             |

| 35      | 47 pF             |

| 37      | 0.01 μF           |

| 39      | 1 μF              |

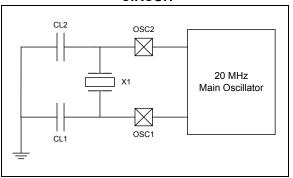

#### 2.5 20 MHz Main Oscillator

The 20 MHz main oscillator provides the main frequency (MAINCLK) signal to internal RF, baseband and MAC circuitry. An external 20 MHz quartz crystal is connected to the OSC1 and OSC2 pins as shown in Figure 2-2. The crystal parameters are listed in Table 2-3.

## TABLE 2-3:20 MHz CRYSTALPARAMETERS<sup>(1)</sup>

| Parameter                                               | Value                  |

|---------------------------------------------------------|------------------------|

| Frequency                                               | 20 MHz                 |

| Frequency Tolerance at 25°C                             | ±20 ppm <sup>(2)</sup> |

| Frequency Stability over Operating<br>Temperature Range | ±20 ppm <sup>(2)</sup> |

| Mode                                                    | Fundamental            |

| Load Capacitance                                        | 10-15 pF               |

| ESR                                                     | 80Ω max.               |

**Note 1:** These values are for design guidance only.

2: IEEE 802.15.4<sup>™</sup> Standard specifies transmitted center frequency tolerance shall be ±40 ppm maximum.

#### FIGURE 2-2: 20 MHz MAIN OSCILLATOR CRYSTAL CIRCUIT

#### 2.6 Phase-Locked Loop

The Phase-Locked Loop (PLL) circuitry requires one external capacitor connected to pin 40 (LCAP). The recommended value is 100 pF. The PCB layout around the capacitor and pin 40 should be designed carefully such as to minimize interference to the PLL.

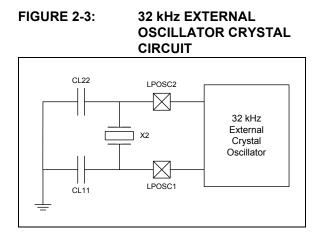

#### 2.7 32 kHz External Crystal Oscillator

The 32 kHz external crystal oscillator provides one of two Sleep clock (SLPCLK) frequencies to Sleep mode counters. The Sleep mode counters time the Beacon Interval (BI) and inactive period for a beacon-enabled device and the Sleep interval for a nonbeacon-enabled device. Refer to **Section 3.15** "**Sleep**" for more information.

The SLPCLK frequency is selectable between the 32 kHz external crystal oscillator or 100 kHz internal oscillator. The 32 kHz external crystal oscillator provides better frequency accuracy and stability than the 100 kHz internal oscillator. An external 32 kHz tuning fork crystal is connected to the LPOSC1 and LPOSC2 pins, as shown in Figure 2-3. The crystal parameters are listed in Table 2-4.

## TABLE 2-4:32 kHz CRYSTALPARAMETERS(1)

| Parameter           | Value      |

|---------------------|------------|

| Frequency           | 32.768 kHz |

| Frequency Tolerance | ±20 ppm    |

| Load Capacitance    | 12.5 pF    |

| ESR                 | 70 kΩ max. |

Note 1: These values are for design guidance only.

#### 2.8 100 kHz Internal Oscillator

The 100 kHz internal oscillator requires no external components and provides one of two Sleep clock (SLPCLK) frequencies to Sleep mode counters. The Sleep mode counters time the Beacon Interval (BI) and inactive period for a beacon-enabled device and the Sleep interval for a nonbeacon-enabled device. Refer to **Section 3.15 "Sleep"** for more information.

The SLPCLK frequency is selectable between the 32 kHz external crystal oscillator or 100 kHz internal oscillator. The 32 kHz external crystal oscillator provides better frequency accuracy and stability than the 100 kHz internal oscillator. It is recommended that the 100 kHz internal oscillator be calibrated before use. The calibration procedure is given in **Section 3.15.1.2 "Sleep Clock Calibration"**.

#### 2.9 Reset (RESET) Pin

An external hardware Reset can be performed by asserting the RESET pin 13 low. The MRF24J40 will be released from Reset approximately 250  $\mu$ s after the RESET pin is released. The RESET pin has an internal weak pull-up resistor.

#### 2.10 Interrupt (INT) Pin

The Interrupt (INT) pin 16 provides an interrupt signal to the host microcontroller from the MRF24J40. The polarity is configured via the INTEDGE bit in the SLPCON0 (0x211<1>) register. Interrupts have to be enabled and unmasked before the INT pin is active. Refer to **Section 3.3 "Interrupts"** for a functional description of interrupts.

| Note: | The                                         | INTEDGE | polarity | defaults | to, |

|-------|---------------------------------------------|---------|----------|----------|-----|

|       | 0 = Falling Edge. Ensure that the interrupt |         |          |          |     |

|       | polarity matches the interrupt pin polarity |         |          |          |     |

|       | on the host microcontroller.                |         |          |          |     |

| Note: | The INT pin will remain high or low,   |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|

|       | depending on INTEDGE polarity setting, |  |  |  |  |

|       | until INSTAT register is read.         |  |  |  |  |

#### 2.11 Wake (WAKE) Pin

The Wake (WAKE) pin 15 provides an external wake-up signal to the MRF24J40 from the host microcontroller. It is used in conjunction with the Sleep modes of the MRF24J40. The WAKE pin is disabled by default. Refer to **Section 3.15.2** "**Immediate Sleep and Wake-up Mode**" for a functional description of the Immediate Sleep and Wake-up modes.

#### 2.12 General Purpose Input/Output (GPIO) Pins

Six GPIO pins can be configured individually for control or monitoring purposes. Input or output selection is configured by the TRISGPIO (0x34) register. GPIO data can be read/written to via the GPIO (0x33) register.

The GPIO pins have limited output drive capability. Table 2-5 lists the individual GPIO pin source current limits.

| Pin   | Maximum Current Sourced |  |  |  |

|-------|-------------------------|--|--|--|

| GPIO0 | 4 mA                    |  |  |  |

| GPIO1 | 1 mA                    |  |  |  |

| GPIO2 | 1 mA                    |  |  |  |

| GPIO3 | 1 mA                    |  |  |  |

| GPIO4 | 1 mA                    |  |  |  |

| GPIO5 | 1 mA                    |  |  |  |

| TABLE 2-5: | GPIO SOURCE CURRENT |

|------------|---------------------|

|            | LIMITS              |

GPIO0, GPIO1 and GPIO2 can be configured to control external PA, LNA and RF switches by the internal RF state machine. This allows the external PA and LNA to be controlled by the MRF24J40 without any host microcontroller intervention. Refer to **Section 4.2 "External PA/LNA Control"** for control register configuration, timing diagrams and application information.

#### 2.13 Serial Peripheral Interface (SPI) Port Pins

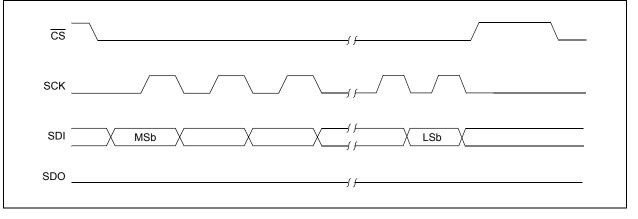

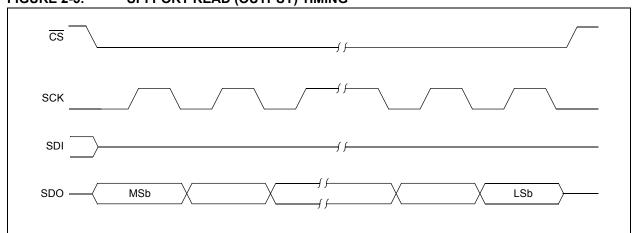

The MRF24J40 communicates with a host microcontroller via a 4-wire SPI port as a slave device. The MRF24J40 supports SPI (mode 0,0) which requires that SCK idles in a low state. The CS pin must be held low while communicating with the MRF24J40. Figure 2-4 shows timing for a write operation. Data is received by the MRF24J40 via the SDI pin and is clocked in on the rising edge of SCK. Figure 2-5 shows timing for a read operation. Data is sent by the MRF24J40 via the SDO pin and is clocked out on the falling edge of SCK. Note: The SDO pin 17 defaults to a low state when CS is high (the MRF24J40 is not selected). If the MRF24J40 is to share a SPI bus, a tri-state buffer should be placed on the SDO signal to provide a high-impedance signal to the SPI bus. See Section 4.4 "MRF24J40 Schematic and Bill of Materials" for an example application circuit.

#### FIGURE 2-5: SPI PORT READ (OUTPUT) TIMING

provide control, status and device addressing for MRF24J40 operations. FIFOs serve as temporary

buffers for data transmission, reception and security

keys. Memory is accessed via two addressing

methods: Short and Long.

#### 2.14 Memory Organization

ſ

Memory in the MRF24J40 is implemented as static RAM and is accessible via the SPI port. Memory is functionally divided into control registers and data buffers (FIFOs), as shown in Figure 2-6. Control registers

FIGURE 2-6: MEMORY MAP FOR MRF24J40

|            | Short Address<br>Memory Space |          |                                  | Long Address<br>Memory Space  |           |

|------------|-------------------------------|----------|----------------------------------|-------------------------------|-----------|

| 0x0<br>0x3 |                               | 64 bytes | 0x000<br>0x07F                   | TX Normal FIFO                | 128 bytes |

|            |                               |          | 0x07F<br>0x080                   | TX Beacon FIFO                | 128 bytes |

|            |                               |          | 0x100<br>0x17F                   | TX GTS1 FIFO                  | 128 bytes |

|            |                               |          | 0x180                            | TX GTS2 FIFO                  | 128 bytes |

|            |                               |          | 0x200<br>0x27F                   | Control Registers             | 128 bytes |

|            |                               |          | 0x280<br>0x2BF<br>0x2C0<br>0x2FF | Security Key FIFO<br>Reserved | 64 bytes  |

|            |                               |          | 0x300                            | RX FIFO                       | 144 bytes |

|            |                               |          | 0x38F                            |                               |           |

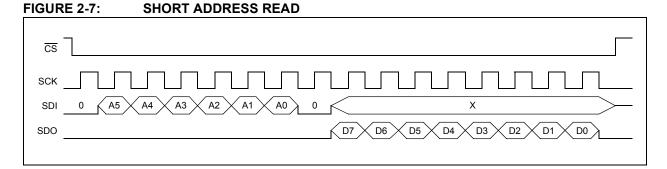

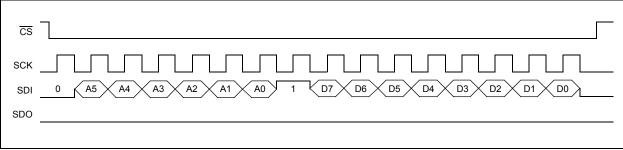

#### 2.14.1 SHORT ADDRESS REGISTER **INTERFACE**

The short address memory space contains control registers with a 6-bit address range of 0x00 to 0x3F. Figure 2-7 shows a short address read and Figure 2-8 shows a short address write. The 8-bit SPI transfer

begins with a '0' to indicate a short address transaction. It is followed by the 6-bit register address, Most Significant bit (MSb) first. The 8th bit indicates if it is a read ('0') or write ('1') transaction.

#### FIGURE 2-8: SHORT ADDRESS WRITE

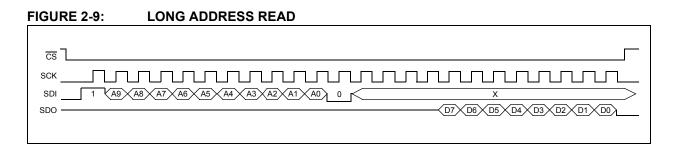

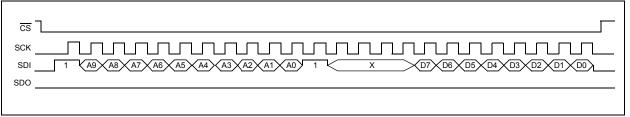

## 2.14.2 LONG ADDRESS REGISTER INTERFACE

The long address memory space contains control registers and FIFOs with a 10-bit address range of 0x000 to 0x38F. Figure 2-9 shows a long address read and Figure 2-10 shows a long address write. The 12-bit

SPI transfer begins with a '1' to indicate a long address transaction. It is followed by the 10-bit register address, Most Significant bit (MSb) first. The 12<sup>th</sup> bit indicates if it is a read ('0') or write ('1') transaction.

#### FIGURE 2-10: LONG ADDRESS WRITE

#### 2.15 Control Register Description

Control registers provide control, status and device addressing for MRF24J40 operations. The following figures, tables and register definitions describe the control register operation.

#### 2.15.1 CONTROL REGISTER MAP

#### FIGURE 2-11: SHORT ADDRESS CONTROL REGISTER MAP FOR MRF24J40

| 0x00 | RXMCR    | 0x10 | ORDER    | 0x20 | ESLOTG67  | 0x30 | RXSR     |

|------|----------|------|----------|------|-----------|------|----------|

| 0x01 | PANIDL   | 0x11 | TXMCR    | 0x21 | TXPEND    | 0x31 | INTSTAT  |

| 0x02 | PANIDH   | 0x12 | ACKTMOUT | 0x22 | WAKECON   | 0x32 | INTCON   |

| 0x03 | SADRL    | 0x13 | ESLOTG1  | 0x23 | FRMOFFSET | 0x33 | GPIO     |

| 0x04 | SADRH    | 0x14 | SYMTICKL | 0x24 | TXSTAT    | 0x34 | TRISGPIO |

| 0x05 | EADR0    | 0x15 | SYMTICKH | 0x25 | TXBCON1   | 0x35 | SLPACK   |

| 0x06 | EADR1    | 0x16 | PACON0   | 0x26 | GATECLK   | 0x36 | RFCTL    |

| 0x07 | EADR2    | 0x17 | PACON1   | 0x27 | TXTIME    | 0x37 | SECCR2   |

| 0x08 | EADR3    | 0x18 | PACON2   | 0x28 | HSYMTMRL  | 0x38 | BBREG0   |

| 0x09 | EADR4    | 0x19 | Reserved | 0x29 | HSYMTMRH  | 0x39 | BBREG1   |

| 0x0A | EADR5    | 0x1A | TXBCON0  | 0x2A | SOFTRST   | 0x3A | BBREG2   |

| 0x0B | EADR6    | 0x1B | TXNCON   | 0x2B | Reserved  | 0x3B | BBREG3   |

| 0x0C | EADR7    | 0x1C | TXG1CON  | 0x2C | SECCON0   | 0x3C | BBREG4   |

| 0x0D | RXFLUSH  | 0x1D | TXG2CON  | 0x2D | SECCON1   | 0x3D | Reserved |

| 0x0E | Reserved | 0x1E | ESLOTG23 | 0x2E | TXSTBL    | 0x3E | BBREG6   |

| 0x0F | Reserved | 0x1F | ESLOTG45 | 0x2F | Reserved  | 0x3F | CCAEDTH  |

#### FIGURE 2-12: LONG ADDRESS CONTROL REGISTER MAP FOR MRF24J40

| 0x200 | RFCON0   | 0x210 | RSSI     | 0x220 | SLPCON1   | ox230 | ASSOEADR0     | 0x240 | UPNONCE0  |

|-------|----------|-------|----------|-------|-----------|-------|---------------|-------|-----------|

| 0x201 | RFCON1   | 0x211 | SLPCON0  | 0x221 | Reserved  | 0x231 | ASSOEADR1     | 0x241 | UPNONCE1  |

| 0x202 | RFCON2   | 0x212 | Reserved | 0x222 | WAKETIMEL | 0x232 | ASSOEADR2     | 0x242 | UPNONCE2  |

| 0x203 | RFCON3   | 0x213 | Reserved | 0x223 | WAKETIMEH | 0x233 | ASSOEADR3     | 0x243 | UPNONCE3  |

| 0x204 | Reserved | 0x214 | Reserved | 0x224 | REMCNTL   | 0x234 | ASSOEADR4     | 0x244 | UPNONCE4  |

| 0x205 | RFCON5   | 0x215 | Reserved | 0x225 | REMCNTH   | 0x235 | ASSOEADR5     | 0x245 | UPNONCE5  |

| 0x206 | RFCON6   | 0x216 | Reserved | 0x226 | MAINCNT0  | 0x236 | ASSOEADR6     | 0x246 | UPNONCE6  |

| 0x207 | RFCON7   | 0x217 | Reserved | 0x227 | MAINCNT1  | 0x237 | ASSOEADR7     | 0x247 | UPNONCE7  |

| 0x208 | RFCON8   | 0x218 | Reserved | 0x228 | MAINCNT2  | 0x238 | ASSOSADR0     | 0x248 | UPNONCE8  |

| 0x209 | SLPCAL0  | 0x219 | Reserved | 0x229 | MAINCNT3  | 0x239 | ASSOSADR1     | 0x249 | UPNONCE9  |

| 0x20A | SLPCAL1  | 0x21A | Reserved | 0x22A | Reserved  | 0x23A | Reserved      | 0x24A | UPNONCE10 |

| 0x20B | SLPCAL2  | 0x21B | Reserved | 0x22B | Reserved  | 0x23B | Reserved      | 0x24B | UPNONCE11 |

| 0x20C | Reserved | 0x21C | Reserved | 0x22C | Reserved  | 0x23C | Unimplemented | 0x24C | UPNONCE12 |

| 0x20D | Reserved | 0x21D | Reserved | 0x22D | Reserved  | 0x23D | Unimplemented | ]     |           |

| 0x20E | Reserved | 0x21E | Reserved | 0x22E | Reserved  | 0x23E | Unimplemented | ]     |           |

| 0x20F | RFSTATE  | 0x21F | Reserved | 0x22F | TESTMODE  | 0x23F | Unimplemented |       |           |

#### 2.15.2 CONTROL REGISTER SUMMARY

| Addr. | File Name | Bit 7      | Bit 6      | Bit 5     | Bit 4               | Bit 3             | Bit 2      | Bit 1     | Bit 0    | Value on<br>POR | Details<br>on<br>Page: |

|-------|-----------|------------|------------|-----------|---------------------|-------------------|------------|-----------|----------|-----------------|------------------------|

| 0x00  | RXMCR     | r          | r          | NOACKRSP  | r                   | PANCOORD          | COORD      | ERRPKT    | PROMI    | 0000            | 22                     |

| 0x01  | PANIDL    |            |            | I         | PAN ID Low Byte     | e (PANIDL<7:0>)   |            |           |          | 0000            | 23                     |

| 0x02  | PANIDH    |            |            |           | PAN ID High Byte    | (PANIDH<15:8>)    |            |           |          | 0000            | 23                     |

| 0x03  | SADRL     |            |            | 5         | Short Address Low   | Byte (SADRL<7:0>  | )          |           |          | 0000            | 24                     |

| 0x04  | SADRH     |            |            | S         | hort Address High E | Byte (SADRH<15:8  | >)         |           |          | 0000            | 24                     |

| 0x05  | EADR0     |            |            | 64-       | Bit Extended Addre  | ess bits (EADR0<7 | :0>)       |           |          | 0000            | 25                     |

| 0x06  | EADR1     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR1<15 | i:8>)      |           |          | 0000            | 25                     |

| 0x07  | EADR2     |            |            | 64-E      | it Extended Addres  | s bits (EADR2<23  | 16>)       |           |          | 0000            | 25                     |

| 0x08  | EADR3     |            |            | 64-E      | it Extended Addres  | s bits (EADR3<31  | 24>)       |           |          | 0000            | 26                     |

| 0x09  | EADR4     |            |            | 64-E      | it Extended Addres  | s bits (EADR4<39  | 32>)       |           |          | 0000            | 26                     |

| 0x0A  | EADR5     |            |            | 64-E      | it Extended Addres  | s bits (EADR5<47: | 40>)       |           |          | 0000            | 26                     |

| 0x0B  | EADR6     |            |            | 64-E      | it Extended Addres  | s bits (EADR6<55  | 48>)       |           |          | 0000            | 27                     |

| 0x0C  | EADR7     |            |            | 64-E      | it Extended Addres  | s bits (EADR7<63  | 56>)       |           |          | 0000            | 27                     |

| 0x0D  | RXFLUSH   | r          | WAKEPOL    | WAKEPAD   | r                   | CMDONLY           | DATAONLY   | BCNONLY   | RXFLUSH  | 0000            | 28                     |

| 0x0E  | Reserved  | r          | r          | r         | r                   | r                 | r          | r         | r        | 0000            | -                      |

| 0x0F  | Reserved  | r          | r          | r         | r                   | r                 | r          | r         | r        | 0000            | -                      |

| 0x10  | ORDER     | BO3        | BO2        | BO1       | BO0                 | SO3               | SO2        | SO1       | SO0      | 1111<br>1111    | 29                     |

| 0x11  | TXMCR     | NOCSMA     | BATLIFEXT  | SLOTTED   | MACMINBE1           | MACMINBE0         | CSMABF2    | CSMABF1   | CSMABF0  | 0001            | 30                     |

| 0x12  | ACKTMOUT  | DRPACK     | MAWD6      | MAWD5     | MAWD4               | MAWD3             | MAWD2      | MAWD1     | MAWD0    | 0011            | 31                     |

| 0x13  | ESLOTG1   | GTS1-3     | GTS1-2     | GTS1-1    | GTS1-0              | CAP3              | CAP2       | CAP1      | CAP0     | 0000            | 32                     |

| 0x14  | SYMTICKL  | TICKP7     | TICKP6     | TICKP5    | TICKP4              | TICKP3            | TICKP2     | TICKP1    | TICKP0   | 0100            | 33                     |

| 0x15  | SYMTICKH  | TXONT6     | TXONT5     | TXONT4    | TXONT3              | TXONT2            | TXONT1     | TXONT0    | TICKP8   | 0101<br>0001    | 33                     |

| 0x16  | PACON0    | PAONT7     | PAONT6     | PAONT5    | PAONT4              | PAONT3            | PAONT2     | PAONT1    | PAONT0   | 0010<br>1001    | 34                     |

| 0x17  | PACON1    | r          | r          | r         | PAONTS3             | PAONTS2           | PAONTS1    | PAONTS0   | PAONT8   | 0000            | 34                     |

| 0x18  | PACON2    | FIFOEN     | r          | TXONTS3   | TXONTS2             | TXONTS1           | TXONTS0    | TXONT8    | TXONT7   | 1000<br>1000    | 35                     |

| 0x19  | Reserved  | r          | r          | r         | r                   | r                 | r          | r         | r        | 0000            | -                      |

| 0x1A  | TXBCON0   | r          | r          | r         | r                   | r                 | r          | TXBSECEN  | TXBTRIG  | 0000            | 36                     |

| 0x1B  | TXNCON    | r          | r          | r         | FPSTAT              | INDIRECT          | TXNACKREQ  | TXNSECEN  | TXNTRIG  | 0000            | 37                     |

| 0x1C  | TXG1CON   | TXG1RETRY1 | TXG1RETRY0 | TXG1SLOT2 | TXG1SLOT1           | TXG1SLOT0         | TXG1ACKREQ | TXG1SECEN | TXG1TRIG | 0000            | 38                     |

| 0x1D  | TXG2CON   | TXG2RETRY1 | TXG2RETRY0 | TXG2SLOT2 | TXG2SLOT1           | TXG2SLOT0         | TXG2ACKREQ | TXG2SECEN | TXG2TRIG | 0000            | 38                     |

Legend: r = reserved

© 2010 Microchip Technology Inc.

|       | LE 2-6:   |           |            |            |            |           |            |            |            |                 | T                      |

|-------|-----------|-----------|------------|------------|------------|-----------|------------|------------|------------|-----------------|------------------------|

| Addr. | File Name | Bit 7     | Bit 6      | Bit 5      | Bit 4      | Bit 3     | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Details<br>on<br>Pages |

| 0x1E  | ESLOTG23  | GTS3-3    | GTS3-2     | GTS3-1     | GTS3-0     | GTS2-3    | GTS2-2     | GTS2-1     | GTS2-0     | 0000<br>0000    | 39                     |

| 0x1F  | ESLOTG45  | GTS5-3    | GTS5-2     | GTS5-1     | GTS5-0     | GTS4-3    | GTS4-2     | GTS4-1     | GTS4-0     | 0000            | 39                     |

| 0x20  | ESLOTG67  | r         | r          | r          | r          | GTS6-3    | GTS6-2     | GTS6-1     | GTS6-0     | 0000            | 39                     |

| 0x21  | TXPEND    | MLIFS5    | MLIFS4     | MLIFS3     | MLIFS2     | MLIFS1    | MLIFS0     | GTSSWITCH  | FPACK      | 1000<br>0100    | 40                     |

| 0x22  | WAKECON   | IMMWAKE   | REGWAKE    | INTL       | INTL       | INTL      | INTL       | INTL       | INTL       | 0000            | 41                     |

| 0x23  | FRMOFFSET | OFFSET7   | OFFSET6    | OFFSET5    | OFFSET4    | OFFSET3   | OFFSET2    | OFFSET1    | OFFSET0    | 0000            | 42                     |

| 0x24  | TXSTAT    | TXNRETRY1 | TXNRETRY0  | CCAFAIL    | TXG2FNT    | TXG1FNT   | TXG2STAT   | TXG1STAT   | TXNSTAT    | 0000            | 43                     |

| 0x25  | TXBCON1   | TXBMSK    | WU/BCN     | RSSINUM1   | RSSINUM0   | r         | r          | r          | r          | 0011<br>0000    | 44                     |

| 0x26  | GATECLK   | r         | r          | r          | r          | GTSON     | r          | r          | r          | 0000            | 45                     |

| 0x27  | TXTIME    | TURNTIME3 | TURNTIME2  | TURNTIME1  | TURNTIME0  | r         | r          | r          | r          | 0100<br>1000    | 46                     |

| 0x28  | HSYMTMRL  | HSYMTMR7  | HSYMTMR6   | HSYMTMR5   | HSYMTMR4   | HSYMTMR3  | HSYMTMR2   | HSYMTMR1   | HSYMTMR0   | 0000            | 47                     |

| 0x29  | HSYMTMRH  | HSYMTMR15 | HSYMTMR14  | HSYMTMR13  | HSYMTMR12  | HSYMTMR11 | HSYMTMR10  | HSYMTMR09  | HSYMTMR08  | 0000<br>0000    | 47                     |

| 0x2A  | SOFTRST   | r         | r          | r          | r          | r         | RSTPWR     | RSTBB      | RSTMAC     | 0000<br>0000    | 48                     |

| 0x2B  | Reserved  | r         | r          | r          | r          | r         | r          | r          | r          | 0000            | -                      |

| 0x2C  | SECCON0   | SECIGNORE | SECSTART   | RXCIPHER2  | RXCIPHER1  | RXCIPHER0 | TXNCIPHER2 | TXNCIPHER1 | TXNCIPHER0 | 0000<br>0000    | 49                     |

| 0x2D  | SECCON1   | r         | TXBCIPHER2 | TXBCIPHER1 | TXBCIPHER0 | r         | r          | DISDEC     | DISENC     | 0000            | 50                     |

| 0x2E  | TXSTBL    | RFSTBL3   | RFSTBL2    | RFSTBL1    | RFSTBL0    | MSIFS3    | MSIFS2     | MSIFS1     | MSIFS0     | 0111<br>0101    | 51                     |

| 0x2F  | Reserved  | r         | r          | r          | r          | r         | r          | r          | r          | 0000            | -                      |

| Addr. | File Name | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR | Details<br>on<br>Pages |

|-------|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------------|------------------------|

| 0x30  | RXSR      | r           | UPSECERR    | BATIND      | r           | r           | SECDECERR   | r           | r           | 0000            | 52                     |

| 0x31  | INTSTAT   | SLPIF       | WAKEIF      | HSYMTMRIF   | SECIF       | RXIF        | TXG2IF      | TXG1IF      | TXNIF       | 0000<br>0000    | 53                     |

| 0x32  | INTCON    | SLPIE       | WAKEIE      | HSYMTMRIE   | SECIE       | RXIE        | TXG2IE      | TXG1IE      | TXNIE       | 1111<br>1111    | 54                     |

| 0x33  | GPIO      | r           | r           | GPIO5       | GPIO4       | GPIO3       | GPIO2       | GPIO1       | GPIO0       | 0000            | 55                     |

| 0x34  | TRISGPIO  | r           | r           | TRISGP5     | TRISGP4     | TRISGP3     | TRISGP2     | TRISGP1     | TRISGP0     | 0000            | 55                     |

| 0x35  | SLPACK    | SLPACK      | WAKECNT6    | WAKECNT5    | WAKECNT4    | WAKECNT3    | WAKECNT2    | WAKECNT1    | WAKECNT0    | 0000            | 56                     |

| 0x36  | RFCTL     | r           | r           | r           | WAKECNT8    | WAKECNT7    | RFRST       | RFTXMODE    | RFRXMODE    | 0000            | 57                     |