# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Low-Power, 2.4 GHz ISM-Band IEEE 802.15.4<sup>TM</sup> RF Transceiver with Extended Proprietary Features

#### Features

- IEEE 802.15.4<sup>™</sup>-2003 and IEEE 802.15.4-2006 Standard Compliant RF transceiver

- · Multiple air-data-rates:

- 250 kbps (IEEE 802.15.4)

- 125, 500, 1000, 2000 kbps, co-existence with standard networks

- Configurable TX output power: -19 to 1 dBm

- Frame header duration scales with the selected data rate

- On-the-fly, per frame air-data-rate detection (link-by-link independent air-data-rates)

- Inferred destination addressing (to further save on framing overheads; optional)

#### **Full-Featured MCU Support**

- · Hardware frame parser

- Hardware CSMA-CA controller, automatic Acknowledgment (ACK) and Frame Check Sequence (FCS)

- Supports all Clear Channel Assessment (CCA) modes

- · Reports ED, RSSI, LQI, and CFO

- Channel Agility with acknowledgments

- Two independent 128 byte frame buffers

- · Streaming mode to maximize throughput

- · Automatic packet retransmit capability

- Hardware Security Engine (AES-128) and configurable Encryption/Decryption mode

#### Low-Power

- · Extreme minimization of radio ON time

- Highest channel-admissible data rate used

- 20%-70% overall reduction through framing

- 2 Mbps frames can reduce radio ON time by a factor of 4 to 8 with respect to 250 kbps frames

- 27.5 mA TX current (typical at 0 dBm)

- · 13.5 mA RX current in RX Listen Power-Saving mode

- 15.5-16.5 mA RX current in RX Packet Demodulation mode (data rate and device Configuration dependent)

- Deep Sleep, Sleep, Crystal ON, and RX Listen

Power-Saving modes

- Memory retention in Deep Sleep mode (<40 nA typical)

- Automated functions minimize MCU ON time

#### General

- · Low external component count

- · Best-in-class battery life preservation

- Supply range: 1.5V to 3.6V

- Compact 32-pin 5x5 mm<sup>2</sup> QFN package

- Temperature range: -40°C to +85°C

- · Certified turnkey-ready solutions available

#### Applications

- IEEE 802.15.4/ZigBee<sup>®</sup> systems (RF4CE and MiWi<sup>TM</sup> network)

- · Industrial monitoring and control

- IEEE 1588 precise timing protocol networks

- · Automatic meter reading

- · Home building automation

- Low-power wireless sensor networks

- · Consumer electronics, voice and audio

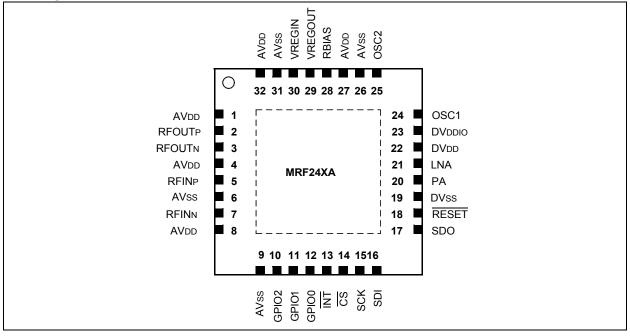

## Pin Diagram

#### **Table of Contents**

| 1.0 Device Overview                                            | 5   |

|----------------------------------------------------------------|-----|

| 2.0 Hardware Description                                       | 7   |

| 3.0 Functional Description                                     | 71  |

| <ul> <li>2.0 Hardware Description</li></ul>                    | 89  |

| 5.0 IEEE 802.15.4™ Compliant Frame Format and Frame Processing | 133 |

| 6.0 Proprietary Frame Format and Frame Processing              |     |

| 7.0 Advanced Link Behavior in Proprietary Packet Mode          | 180 |

| 8.0 Bridging                                                   | 197 |

| 8.0 Bridging 9.0 Physical layer Functions                      | 199 |

| 10.0 Battery Life Optimization                                 | 237 |

| 11.0 Electrical Characteristics                                |     |

| 12.0 Packaging Information                                     | 245 |

| 12.0 Packaging Information                                     |     |

| The Microchip Web Site                                         | 251 |

| Customer Change Notification Service                           | 251 |

| Customer Support                                               |     |

| The Microchip Web Site                                         |     |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

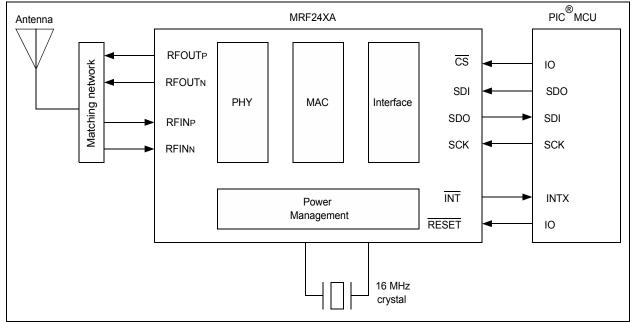

### 1.0 DEVICE OVERVIEW

MRF24XA is an IEEE 802.15.4™ Standard compliant 2.4 GHz RF transceiver with feature extensions. MRF24XA integrates the PHY and MAC functionality in a single-chip solution. MRF24XA implements a lowcost, low-power, high data rate (125 kbps to 2 Mbps) Wireless Personal Area Network (WPAN) device. All the data rates contains the same spectral shape requiring identical bandwidth. At 125 kbps data rate Direct Sequence Spread Spectrum (DSSS) is combined with error correction and coding for maximum range and robustness against interference. The 2 Mbps data rate is used to minimize radio ON time, therefore extending battery life. Figure 1-1 illustrates a simplified block diagram of a MRF24XA wireless node. MRF24XA interfaces to many popular Microchip PIC<sup>®</sup> microcontrollers through a 4-wire serial SPI interface, interrupt, GPIO, and RESET pins.

MRF24XA can also handle external Power Amplifier (PA) and Low Noise Amplifier (LNA).

MRF24XA provides hardware support for:

- Energy detection

- · Carrier sense

- Four CCA modes

- CSMA-CA algorithm

- Automatic packet retransmission

- · Automatic acknowledgement

- Independent transmit and receive buffers

- Security engine supports encryption and decryption for MAC sublayer and upper layer

- Inferred destination addressing

- Channel agility with ACKs

- · Battery monitoring

These features reduce the processing load, allowing the use of low-cost 8-bit microcontrollers.

MRF24XA is compatible with Microchip's ZigBee<sup>®</sup>, MiWi™ and MiWi P2P software stacks. Each software stack is available as a free download, including source code, from the Microchip web site:

http://www.microchip.com/wireless.

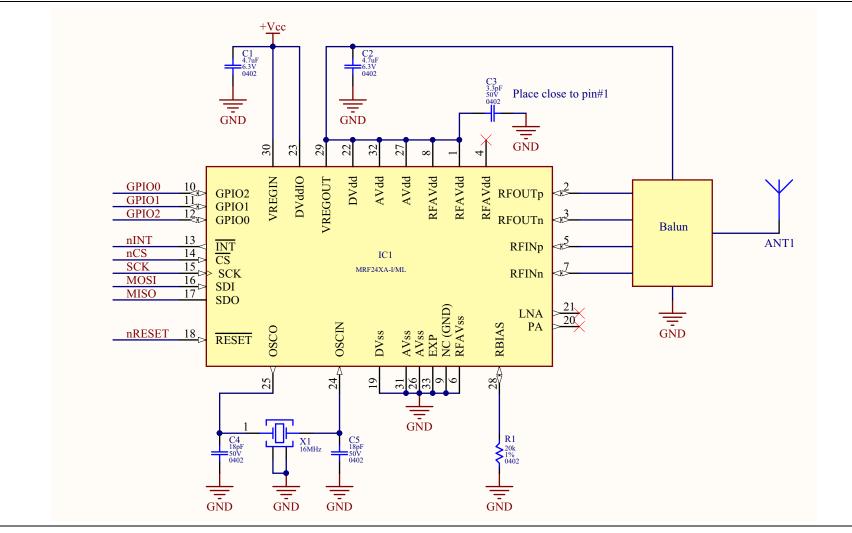

#### FIGURE 1-1: MRF24XA WIRELESS NODE BLOCK DIAGRAM

NOTES:

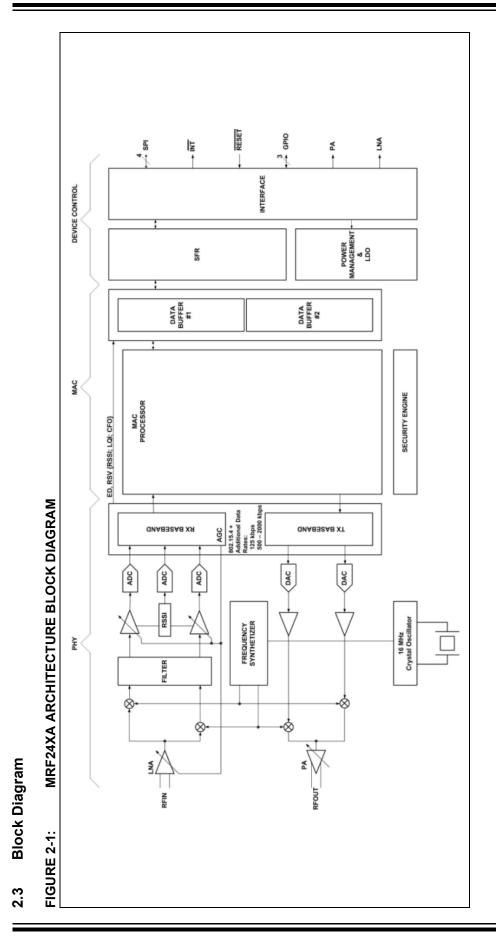

#### 2.0 HARDWARE DESCRIPTION

#### 2.1 Overview

MRF24XA is an IEEE 802.15.4 Standard compliant 2.4 GHz RF transceiver with extended feature set for longer battery life, higher throughput and increased operating range.

MRF24XA integrates the PHY and MAC functionality in a single-chip solution. Figure 2-1 illustrates a block diagram of the MRF24XA circuitry.

An external 16 MHz crystal clocks the frequency synthesizer and generates a 2.4 GHz frequency RF carrier.

The receiver is a zero-IF architecture consisting of a Low-Noise Amplifier, down conversion mixers, channel filters and baseband amplifiers with a Received Signal Strength Indicator (RSSI).

The transmitter is a direct conversion architecture with a 1 dBm maximum output (typical) and 20 dB power control range.

The internal transmitter and receiver circuits contains separate RFP and RFN input/output pins that connects to impedance matching circuitry (balun) and antenna. An external Power Amplifier or Low Noise Amplifier, or both is controlled through the PA and LNA pins.

Three general purpose Input/Output (GPIO) pins are configurable for control or monitoring purposes.

The power management circuitry consists of an integrated Low Dropout (LDO) voltage regulator and a 5-bit resolution Battery Monitor Block. MRF24XA is placed into a low-current (<40 nA typical) Deep Sleep mode.

The Media Access Controller (MAC) circuitry can sequence the transmit, receive and automatically enable the security operations. The host MCU can control these mechanisms through reaister configurations and Frame Control (FCtrl) field embedded in the downloaded formatted frames. Three alternative frame formats are supported: IEEE 802.15.4 2003, 2006 compliant MAC frame formats and a flexible and power-efficient advanced MAC frame format, which is proprietary. Before launching transmission, the host must load the buffer with a formatted frame. The hardware can optionally perform encryption and message integrity code appending as configured, then sends the frame appending a Frame Check Sequence (FCS).

Hardware can autonomously sequence acknowledge reception and automatic retransmissions.

In reception, the format of the demodulated frame is verified. Depending on the Configuration, duplicate frames, frames with corrupted FCS or address mismatch are discarded. On reception of valid frames, automatic acknowledge sending, decryption and message integrity checking are supported.

As the default, separate buffers are reserved for transmission and reception. Alternatively, either the Transmit Streaming (TX-Streaming) or the Receive Streaming (RX-Streaming) modes are selected whereby buffers are used by alternating between the two for servicing a single direction of data flow. The AES-128 engine are governed to perform network-layer security processing and supports complete security suites such as CTR, CBC-MAC and CCM\*.

Transceiver is controlled through a 4-wire SPI, interrupt and RESET pins.

#### 2.2 Operating Modes

Table 2-1summarizestheOperatingmodesofMRF24XA.

|                      |          | Internal Functional Blocks |             |                 |                |          |  |  |  |  |  |

|----------------------|----------|----------------------------|-------------|-----------------|----------------|----------|--|--|--|--|--|

| Operating Mode       | 1.2V LDO | Crystal<br>Oscillator      | Synthesizer | RX Front<br>End | RX<br>Baseband | TX Chain |  |  |  |  |  |

| Deep Sleep           | OFF      | OFF                        | OFF         | OFF             | OFF            | OFF      |  |  |  |  |  |

| Sleep                | ON       | OFF                        | OFF         | OFF             | OFF            | OFF      |  |  |  |  |  |

| RFOFF Crystal ON     | ON       | ON                         | OFF         | OFF             | OFF            | OFF      |  |  |  |  |  |

| RFOFF Synthesizer ON | ON       | ON                         | ON          | OFF             | OFF            | OFF      |  |  |  |  |  |

| RX Listen Power-Save | ON       | ON                         | ON          | ON              | OFF            | OFF      |  |  |  |  |  |

| RX Listen            | ON       | ON                         | ON          | ON              | ON             | OFF      |  |  |  |  |  |

| ТХ                   | ON       | ON                         | ON          | OFF             | OFF            | ON       |  |  |  |  |  |

#### TABLE 2-1: MRF24XA POWER MODES

© 2015 Microchip Technology Inc.

### 2.4 Pin Descriptions

| <b>TABLE 2-2:</b> | MRF24XA PIN DESCRIPTIONS |

|-------------------|--------------------------|

|-------------------|--------------------------|

| Pin | Symbol  | Туре   | Description                                                                       |

|-----|---------|--------|-----------------------------------------------------------------------------------|

| 1   | AVDD    | Power  | 1.2V supply, normally connected to VREGOUT (pin 29)                               |

| 2   | RFOUTP  | AO     | Differential RF Output (+)                                                        |

| 3   | RFOUTN  | AO     | Differential RF Output (–)                                                        |

| 4   | AVdd    | Power  | 1.2V supply, normally connected to VREGOUT (pin 29) <sup>(1)</sup>                |

| 5   | RFINP   | AI     | Differential RF Input (+)                                                         |

| 6   | AVss    | Ground | Ground                                                                            |

| 7   | RFINN   | AI     | Differential RF Input (–)                                                         |

| 8   | AVdd    | Power  | 1.2V supply, normally connected to VREGOUT (pin 29)                               |

| 9   | AVss    | Power  | Ground <sup>(1)</sup>                                                             |

| 10  | GPIO2   | DIO    | GPIO2                                                                             |

| 11  | GPIO1   | DIO    | GPIO1                                                                             |

| 12  | GPIO0   | DIO    | GPIO0                                                                             |

| 13  | INT     | DO     | Interrupt Output, active-low                                                      |

| 14  | CS      | DI     | SPI Chip Select Pin, active-low                                                   |

| 15  | SCK     | DI     | SPI serial clock                                                                  |

| 16  | SDI     | DI     | SPI serial data Input                                                             |

| 17  | SDO     | DO     | SPI serial data Output                                                            |

| 18  | RESET   | DI     | Reset Input, active-low                                                           |

| 19  | DVss    | Ground | Digital ground                                                                    |

| 20  | PA      | DO     | External PA enable Output                                                         |

| 21  | LNA     | DO     | External LNA enable Output                                                        |

| 22  | DVdd    | Power  | Digital 1.2V supply, normally connected to VREGOUT (pin 29)                       |

| 23  | DVDDIO  | Power  | Digital 1.5V–3.6V supply for the IO blocks, normally connected to VREGIN (pin 30) |

| 24  | OSC1    | AI     | Crystal oscillator Pin 1, External Clock Input                                    |

| 25  | OSC2    | AO     | Crystal oscillator Pin 2                                                          |

| 26  | AVss    | Ground | Ground                                                                            |

| 27  | AVdd    | Power  | 1.2V supply, normally connected to VREGOUT (pin 29)                               |

| 28  | RBIAS   | AO     | External resistor reference pin                                                   |

| 29  | VREGOUT | Power  | 1.2V regulated Output                                                             |

| 30  | VREGIN  | Power  | 1.5V–3.6V regulator Input                                                         |

| 31  | AVss    | Ground | Ground                                                                            |

| 32  | AVdd    | Power  | 1.2V supply, normally connected to VREGOUT (pin 29)                               |

**Legend:** A = Analog, D = Digital, I = Input, O = Output

**Note** 1: In case PCB runs out of space, disconnect these pins.

#### 2.4.1 POWER AND GROUND PINS

Table 2-3 lists the recommended bypass capacitors. VDD pins 29 and 30 are power pins, which require different bypass capacitors to ensure sufficient bypass decoupling and stability. Bypass capacitors must have low serial resistance. The 4.7  $\mu$ F capacitors must be made of ceramic or high-performance tantalum.

On PCB layout minimize trace length from the VDD pin to the bypass capacitors and connect capacitors to the pads as short as possible. PCB tracks must be wide enough to minimize voltage drop and serial inductance of the power line.

Analog and digital power lines must follow a star topology, where the common point is the bypass capacitor on pin 30.

#### TABLE 2-3:RECOMMENDED BYPASS CAPACITOR VALUES

| VDD Pin | Symbol  | Bypass Capacitor |

|---------|---------|------------------|

| 1       | AVDD    | 3.3 pF           |

| 29      | VREGOUT | 4.7 µF           |

| 30      | VREGIN  | 10 nF + 4.7 μF   |

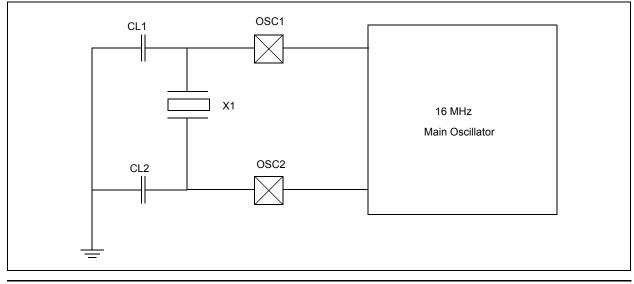

#### 2.4.2 16 MHz MAIN OSCILLATOR PINS

The 16 MHz oscillator is connected to OSC1 and OSC2 pins as shown in Figure 2-2, which provides the reference frequency for the internal RF, MAC and BB circuitry. Table 2-4 lists the crystal parameters.

To minimize parasitic effects on pins, the crystal must be put as close as possible to MRF24XA. It keeps the tracks short. Crystal must be surrounded with ground pour to minimize cross coupling effects. Crystal load capacitors must be placed close to the crystal.

#### TABLE 2-4: 16 MHz CRYSTAL PARAMETERS<sup>(1)</sup>

| Parameters                                                                                                    | Value                  |

|---------------------------------------------------------------------------------------------------------------|------------------------|

| Frequency                                                                                                     | 16 MHz                 |

| Frequency tolerance for 500, 250 and 125 kbps data rates (including manufac-<br>turing aging and temperature) | ±60 ppm <sup>(1)</sup> |

| Frequency tolerance for 2 and 1 Mbps data rates (including manufacturing aging and temperature)               | ±40 ppm <sup>(2)</sup> |

| Mode                                                                                                          | Fundamental            |

| Load Capacitance                                                                                              | 18 pF                  |

| ESR                                                                                                           | 80 Ohm max             |

**Note 1:** IEEE 802.15.4 defines ±40 ppm.

2: These values are only used for design guidance .

#### FIGURE 2-2: 16 MHz MAIN OSCILLATOR CRYSTAL CIRCUIT

#### 2.4.3 RESET (RESET) PIN

An <u>external</u> Hardware Reset is performed by asserting the RESET pin 18 low. If the RESET pin is deasserted, MRF24XA starts the internal Calibration process. RDYIF <u>interrup</u>t is set when the device is ready to use. The RESET pin contains an internal weak pull-up resistor.

#### 2.4.4 INTERRUPT (INT) PIN

The Interrupt (INT) pin 13 provides an interrupt signal to the host MCU from MRF24XA where the signal is active-low polarity. Interrupt sources must be enabled and unmasked before the INT pin becomes active.

Refer to **Section 3.2 "Interrupts"** for the functional description of interrupts.

#### 2.4.5 GENERAL PURPOSE INPUT/ OUTPUT (GPIO) PINS

Three GPIO pins are configured individually for control or monitoring purposes. The TRISGPIOx bits in the GPIO register (0x0D) configures the input or output selection. GPIO data is read or written through the GPIO bits of GPIO register. The GPIO interrupt polarity is selected through GPIOxP bits in the STGPIO (0x0E) register.

GPIO lines in Input mode are used in Schmitt Trigger Input mode. STENGPIOx bits of STGPIO register enables Schmitt Triggers. GPIOs are also used to monitor the internal blocks. The GPIOMODE bits <3:0> of the PINCON (0x0C) register selects these monitoring functions.

#### 2.4.6 SERIAL PERIPHERAL INTERFACE (SPI) PORT PINS

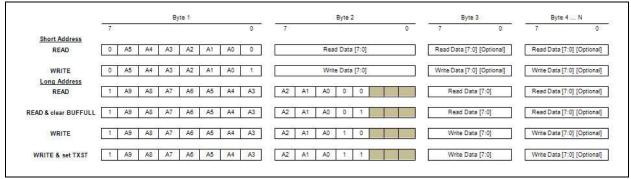

MRF24XA communicates with a host MCU through a 4-wire SPI port as a slave device. MRF24XA supports SPI mode 0,0, which requires that SCK idles in a low state. The CS pin must be held low while communicating with MRF24XA. Figure 2-3 illustrates timing for a read and a write operation. MRF24XA receives the data through the SDI pin and clocks in on the rising edge of SCK. MRF24XA sends data through the SDO pin and clocks out on the falling edge of SCK. The SDO lines preserve its HiZ state in Deep Sleep mode.

#### 2.5 Application Example

Figure 2-3 illustrates the schematic of a recommended application circuit for MRF24XA.

#### FIGURE 2-3: MRF24XA APPLICATION CIRCUIT

DS70005023C-page 12

#### 2.6 Memory Organization

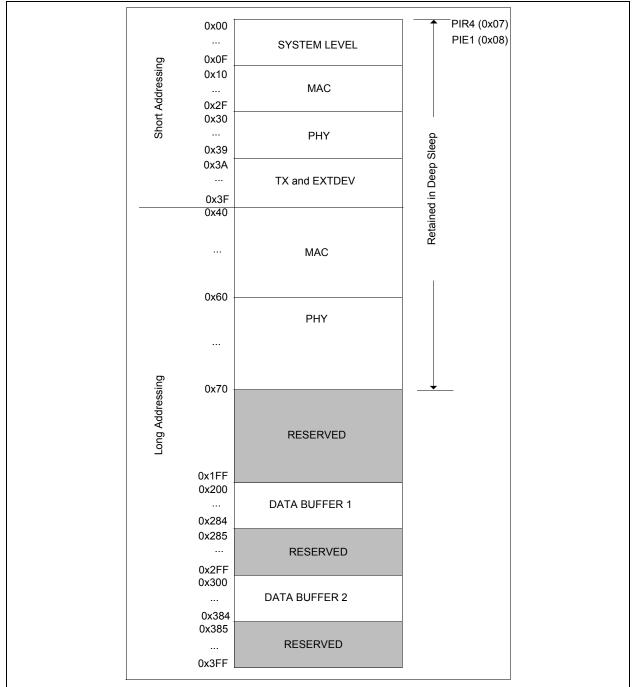

Table 2-5 shows that memory is functionally divided into Special Function Registers (SFR) and data buffers.

The SFRs provide control, status and device Configuration addressing for MRF24XA operations. Data buffers serve as temporary buffers for data transmission and reception. Memory is accessed through two addressing methods: Short (1 byte) and Long (2 bytes).

#### 2.6.1 ADDRESS OVERVIEW

MRF24XA contains two Addressing modes:

- Short Address Mode: Requires one byte for address, and may be used to access the first 64 on-chip control registers.

- Long Address Mode: Requires two bytes for address, and may be used to access all on-chip registers and data buffers. Figure 2-4 illustrates these modes.

#### TABLE 2-5: MRF24XA MEMORY MAP

# DS70005023C-page 14

Architecture Address

MAC

| SYSTEM      | 0x00         | REGRST     | r          | r            |              |              | REGR                | ST<5:0>     |             |             | 71 |

|-------------|--------------|------------|------------|--------------|--------------|--------------|---------------------|-------------|-------------|-------------|----|

| LEVEL       | 0x01         | FSMRST     | r          | r            | r            |              |                     | FSMRST<4:0> |             |             | 71 |

|             | 0x02         | OPSTATUS   | r          |              | MACOF        | 2<3:0>       |                     |             | RFOP<2:0>   |             | 18 |

|             | 0x03         | STATUS     | INITDONESF | XTALSF       | REGSF        | CALST        | XTALDIS             | DSLEEP      | IDLESF      | POR         | 19 |

|             | 0x04         | PIR1       | VREGIF     | r            | RDYIF        | IDLEIF       | r                   | CALSOIF     | CALHAIF     | r           | 20 |

|             | 0x05         | PIR2       | TXIF       | TXENCIF      | TXMAIF       | TXACKIF      | TXCSMAIF            | TXSZIF      | TXOVFIF     | FRMIF       | 21 |

|             | 0x06         | PIR3       | RXIF       | RXDECIF      | RXTAGIF      | r            | RXIDENTIF           | RXFLTIF     | RXOVFIF     | STRMIF      | 22 |

|             | 0x07         | PIR4       | TXSFDIF    | RXSFDIF      | ERRORIF      | WARNIF       | EDCCAIF             | GPIO2IF     | GPI01IF     | GPIO0IF     | 23 |

|             | 0x08         | PIE1       | r          | r            | RDYIE        | IDLEIE       | r                   | CALSOIE     | CALHAIE     | r           | 24 |

|             | 0x09         | PIE2       | TXIE       | TXENCIE      | TXMAIE       | TXACKIE      | TXCSMAIE            | TXSZIE      | TXOVFIE     | FRMIE       | 25 |

|             | 0x0A         | PIE3       | RXIE       | RXDECIE      | RXTAGIE      | r            | RXIDENTIE           | RXFLTIE     | RXOVFIE     | STRMIE      | 26 |

|             | 0x0B         | PIE4       | TXSFDIE    | RXSFDIE      | ERRORIE      | WARNIE       | EDCCAIE             | GPIO2IE     | GPIO1IE     | GPIO0IE     | 27 |

|             | 0x0C         | PINCON     | r          | GIE          | r            | IRQIF        |                     | GPIOM       | ODE<3:0>    |             | 28 |

|             | 0x0D         | GPIO       | GPIOEN     | TRISGPIO2    | TRISGPIO1    | TRISGPI00    | r                   | GPIO2       | GPIO1       | GPIO0       | 29 |

|             | 0x0E         | STGPIO     | r          | GPIO2P       | GPIO1P       | GPIO0P       | r                   | STENGPIO2   | STENGPIO1   | STENGPIO0   | 30 |

|             | 0x0F         | PULLGPIO   | r          | PULLDIRGPIO2 | PULLDIRGPI01 | PULLDIRGPI00 | r                   | PULLENGPIO2 | PULLENGPIO1 | PULLENGPIO0 | 31 |

| MAC         | 0x10         | MACCON1    | TRXM       | ODE<1:0>     |              | ADDRSZ<2:0>  |                     | CRCSZ       | FRMFMT      | SECFLAGOVR  | 32 |

|             | 0x11         | MACCON2    |            | CHAN         | NEL<3:0>     |              |                     | SECSU       | IITE<3:0>   |             | 34 |

|             | 0x12         | TXCON      | TXST       | DTSM         | TXENC        | TXBUFEMPTY   | CSMAEN              |             | DR<2:0>     |             | 35 |

|             | 0x13         | RXACKWAIT  |            |              |              | RXACKW       | AIT<7:0>            |             |             |             | 37 |

|             | 0x14         | RETXCOUNT  |            | RETXM        | ICNT<3:0>    |              |                     | RETXC       | CNT<3:0>    |             | 37 |

|             | 0x15         | RXCON1     | RXEN       | NOPA         | RXDEC        | RXVLQIEN     | RSVRSSIEN           | RSVCHDREN   | RSVCFOEN    | r           | 38 |

|             | 0x16         | RXCON2     | RXBUFFUL   | IDENTREJ     | ACKRXFP      | ACKTXFP      | AUTORPTEN           | AUTOACKEN   | ADPTCHEN    | ADPTDREN    | 39 |

|             | 0x17         | TXACKTO    |            |              |              | TXACKT       | <sup>-</sup> O<7:0> |             |             |             | 41 |

|             | 0x18         | RXFILTER   | PANCRDN    | CRCREJ       | CMDREJ       | DATAREJ      | UNIREJ              | NOTMEREJ    | BCREJ       | NSTDREJ     | 42 |

|             | 0x19         | TMRCON     |            | BOMCNT<2:0>  |              |              |                     | BASETM<4:0> |             |             | 44 |

|             | 0x1A         | CSMABE     |            | MAXI         | BE<3:0>      |              |                     | MINB        | E<3:0>      |             | 45 |

|             | 0x1B         | BOUNIT     |            |              |              | BOUNI        | T<7:0>              |             |             |             | 46 |

|             | 0x1C         | STRMTOL    |            |              |              | STRMT        | 0<7:0>              |             |             |             | 46 |

|             | 0x1D         | STRMTOH    |            |              |              | STRMTO       | )<15:8>             |             |             |             | 46 |

|             | 0x1E         | OFFTM      |            |              |              | OFFTM        | 1<7:0>              |             |             |             | 47 |

| _egend: r = | Reserved, re | ad as '0'. |            |              |              |              |                     |             |             |             |    |

#### TABLE 2-6: SHORT ADDRESS REGISTER SUMMARY FOR MRF24XA

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

Name

**Legend:** r = Reserved, read as '0'.

| Architecture     | Address | Name       | Bit 7    | Bit 6         | Bit 5     | Bit 4    | Bit 3          | Bit 2        | Bit 1       | Bit 0    | Page |  |  |  |

|------------------|---------|------------|----------|---------------|-----------|----------|----------------|--------------|-------------|----------|------|--|--|--|

|                  | 0x1F    | ADDR1      |          |               |           | ADDR     | R<7:0>         |              |             |          | 48   |  |  |  |

|                  | 0x20    | ADDR2      |          |               |           | ADDR     | <15:8>         |              |             |          | 48   |  |  |  |

|                  | 0x21    | ADDR3      |          | ADDR<23:16>   |           |          |                |              |             |          |      |  |  |  |

|                  | 0x22    | ADDR4      |          | ADDR<31:24>   |           |          |                |              |             |          |      |  |  |  |

|                  | 0x23    | ADDR5      |          |               |           | ADDR<    | <39:32>        |              |             |          | 48   |  |  |  |

|                  | 0x24    | ADDR6      |          |               |           | ADDR<    | <47:40>        |              |             |          | 48   |  |  |  |

|                  | 0x25    | ADDR7      |          |               |           | ADDR<    | <55:48>        |              |             |          | 48   |  |  |  |

|                  | 0x26    | ADDR8      |          |               |           | ADDR<    | <63:56>        |              |             |          | 48   |  |  |  |

|                  | 0x27    | SHADDRL    |          |               |           | SHADD    | )R<7:0>        |              |             |          | 49   |  |  |  |

|                  | 0x28    | SHADDRH    |          |               |           | SHADD    | R<15:8>        |              |             |          | 49   |  |  |  |

|                  | 0x29    | PANIDL     |          |               |           | PANIC    | )<7:0>         |              |             |          | 49   |  |  |  |

|                  | 0x2A    | PANIDH     |          |               |           | PANID    | <15:8>         |              |             |          | 49   |  |  |  |

|                  | 0x2B    | SECHDRINDX | r        |               |           | SI       | ECHDRINDX<6:0  | >            |             |          | 50   |  |  |  |

|                  | 0x2C    | SECPAYINDX | r        |               |           | S        | ECPAYINDX<6:0> | >            |             |          | 50   |  |  |  |

|                  | 0x2D    | SECENDINDX | r        |               |           | S        | ECENDINDX<6:0  | >            |             |          | 51   |  |  |  |

|                  | 0x2E    | MACDEBUG   | BUF1TXPP | BUF2TXPP      | BUF1RXPP  | BUF2RXPP | TXRDBUF        | RXWRBUF      | BUSRDBUF    | BUSWRBUF | 52   |  |  |  |

| PHY              | 0x2F    | CCACON1    | CCABUSY  | CCAST         |           |          | RSSITI         | HR<5:0>      |             |          | 53   |  |  |  |

|                  | 0x30    | CCACON2    |          | CST           | HR<3:0>   |          | CCAL           | EN<1:0>      | CCAMO       | DE<1:0>  | 53   |  |  |  |

|                  | 0x31    | EDCON      | r        | r             | EDMODE    | EDST     |                | EDLE         | EN<3:0>     |          | 54   |  |  |  |

|                  | 0x32    | EDMEAN     |          |               | •         | EDMEA    | N<7:0>         |              |             |          | 54   |  |  |  |

|                  | 0x33    | EDPEAK     |          |               |           | EDPEA    | K<7:0>         |              |             |          | 55   |  |  |  |

|                  | 0x34    | CFOCON     |          | CFO           | TX<3:0>   |          |                | CFO          | RX<3:0>     |          | 55   |  |  |  |

|                  | 0x35    | CFOMEAS    |          |               |           | CFOME    | AS<7:0>        |              |             |          | 56   |  |  |  |

|                  | 0x36    | RATECON    | DIS2000  | DIS1000       | DIS500    | DIS250   | DISSTD         | DIS125       | OPTIMAL     | PSAV     | 57   |  |  |  |

|                  | 0x37    | POWSAVE    |          | DESEN         | STHR<3:0> |          |                | PSAV1        | [HR<3:0>    |          | 58   |  |  |  |

|                  | 0x38    | BBCON      | RNDMOD   | AFCOVR        | RXGAI     | N<1:0>   | PRMBHOLD       |              | PRMBSZ<2:0> |          | 59   |  |  |  |

|                  | 0x39    | IFGAP      | r        | r             | r         |          |                | IFGAP<4:0>   |             |          | 60   |  |  |  |

| TX AND<br>EXTDEV | 0x3A    | TXPOW      |          | CHIPBOOST<2:0 | )>        |          |                | TXPOW<4:0>   |             |          | 60   |  |  |  |

|                  | 0x3B    | TX2IDLE    | r        | r             | r         |          |                | TX2IDLE<4:0> |             |          | 61   |  |  |  |

|                  | 0x3C    | TX2TXMA    | r        | r             | r         |          |                | TX2TXMA<4:0> |             |          | 61   |  |  |  |

|                  | 0x3D    | EXTPA      | r        | EXTPA_P       | PAEN      |          |                | PA2TXMA<4:0> |             |          | 62   |  |  |  |

|                  | 0x3E    | EXTLNA     | r        | EXTLNA_P      | LNAEN     |          |                | LNADLY<4:0>  |             |          | 62   |  |  |  |

|                  | 0x3F    | BATMON     | r        | r             | BATMONPD  |          |                | BATMON<4:0>  |             |          | 63   |  |  |  |

#### TABLE 2-6: SHORT ADDRESS REGISTER SUMMARY FOR MRF24XA (CONTINUED)

Legend: r = Reserved, read as '0'.

| TABL | E 2-7:  | LONG ADDRE  | SS REGI         | STER SU       | MMARY | FORM     | RF24X/   | 4     |       |       |      |  |

|------|---------|-------------|-----------------|---------------|-------|----------|----------|-------|-------|-------|------|--|

|      | Address | Name        | Bit 7           | Bit 6         | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Page |  |

| MAC  | 0x40    | SECKEY1     |                 |               |       | SECKEY   | <7:0>    |       |       |       | 63   |  |

|      | 0x41    | SECKEY2     |                 |               |       | SECKEY<  | :15:8>   |       |       |       | 63   |  |

|      | 0x42    | SECKEY3     |                 |               |       | SECKEY<  | 23:16>   |       |       |       | 63   |  |

|      | 0x43    | SECKEY4     | SECKEY<31:24>   |               |       |          |          |       |       |       | 63   |  |

|      | 0x44    | SECKEY5     |                 |               |       | SECKEY<  | 39:32>   |       |       |       | 63   |  |

|      | 0x45    | SECKEY6     |                 |               |       | SECKEY<  | 47:40>   |       |       |       | 63   |  |

|      | 0x46    | SECKEY7     |                 | SECKEY<55:48> |       |          |          |       |       |       |      |  |

|      | 0x47    | SECKEY8     |                 |               |       | SECKEY<  | 63:56>   |       |       |       | 63   |  |

|      | 0x48    | SECKEY9     |                 |               |       | SECKEY<  | 71:64>   |       |       |       | 63   |  |

|      | 0x49    | SECKEY10    |                 |               |       | SECKEY<  | 79:72>   |       |       |       | 63   |  |

|      | 0x4A    | SECKEY11    |                 |               |       | SECKEY<  | 87:80>   |       |       |       | 63   |  |

|      | 0x4B    | SECKEY12    |                 |               |       | SECKEY<  | 95:88>   |       |       |       | 63   |  |

|      | 0x4C    | SECKEY13    |                 |               | S     | SECKEY<1 | 03:96>   |       |       |       | 63   |  |

|      | 0x4D    | SECKEY14    |                 |               | ç     | SECKEY11 | 1:104>   |       |       |       | 63   |  |

|      | 0x4E    | SECKEY15    |                 |               | S     | ECKEY<1  | 19:112>  |       |       |       | 63   |  |

|      | 0x4F    | SECKEY16    |                 |               | S     | ECKEY<1  | 27:120>  |       |       |       | 63   |  |

|      | 0x50    | SECNONCE1   |                 |               | S     | SECNONC  | E<7:0>   |       |       |       | 65   |  |

|      | 0x51    | SECNONCE2   |                 |               | S     | ECNONCE  | E<15:8>  |       |       |       | 65   |  |

|      | 0x52    | SECNONCE3   |                 |               |       |          |          |       |       |       | 65   |  |

|      | 0x53    | SECNONCE4   |                 |               |       |          |          |       |       | 65    |      |  |

|      | 0x54    | SECNONCE5   | SECNONCE<39:32> |               |       |          |          |       |       | 65    |      |  |

|      | 0x55    | SECNONCE6   |                 |               | SI    | ECNONCE  | <47:40>  |       |       |       | 65   |  |

|      | 0x56    | SECNONCE7   |                 |               | SI    | ECNONCE  | <55:48>  |       |       |       | 65   |  |

|      | 0x57    | SECNONCE8   |                 |               | SI    | ECNONCE  | <63:56>  |       |       |       | 65   |  |

|      | 0x58    | SECNONCE9   |                 |               | SI    | ECNONCE  | <71:64>  |       |       |       | 65   |  |

|      | 0x59    | SECNONCE10  |                 |               | SI    | ECNONCE  | <79:72>  |       |       |       | 65   |  |

|      | 0x5A    | SECNONCE11  |                 |               | SI    | ECNONCE  | <87:80>  |       |       |       | 65   |  |

|      | 0x5B    | SECNONCE12  |                 |               | SI    | ECNONCE  | <95:88>  |       |       |       | 65   |  |

|      | 0x5C    | SECNONCE13  |                 |               | SE    | CNONCE   | <103:96> |       |       |       | 65   |  |

|      | 0x5D    | SECENCFLAG  |                 |               | SI    | ECENCFL  | 4G<7:0>  |       |       |       |      |  |

|      | 0x5E    | SECAUTHFLAG |                 |               | SE    | CAUTHFL  | AG<7:0>  |       |       |       |      |  |

|      | 0x5F    |             |                 |               | r     |          |          |       |       |       |      |  |

| PHY  | 0x60    | SFD1        |                 |               |       | SFD1<7   | 7:0>     |       |       |       | 66   |  |

|      | 0x61    | SFD2        |                 |               |       | SFD2<7   | 7:0>     |       |       |       | 67   |  |

|      | 0x62    | SFD3        |                 |               |       | SFD3<7   | 7:0>     |       |       |       | 67   |  |

|      | 0x63    | SFD4        |                 |               |       | SFD4<7   | 7:0>     |       |       |       | 68   |  |

|      | 0x64    | SFD5        |                 |               |       | SFD5<7   | 7:0>     |       |       |       | 68   |  |

|      | 0x65    | SFD6        |                 |               |       | SFD6<7   | 7:0>     |       |       |       | 69   |  |

|      | 0x66    | SFD7        |                 |               |       | SFD7<7   | 7:0>     |       |       |       | 69   |  |

|      | 0x67    |             |                 |               | r     |          |          |       |       |       |      |  |

|      | 0x68    |             |                 |               | r     |          |          |       |       |       |      |  |

|      | 0x69    |             |                 |               | r     |          |          |       |       |       |      |  |

|      | 0x6A    |             |                 |               | r     |          |          |       |       |       |      |  |

|      | 0x6B    |             | r<br>r<br>r     |               |       |          |          |       |       |       |      |  |

|      | 0x6C    |             |                 |               |       |          |          |       |       |       |      |  |

|      | 0x6D    |             |                 |               |       |          |          |       |       |       |      |  |

|      | 0x6E    | SFDTO       |                 |               | S     | FDTIMEO  | JT<7:0>  |       |       |       |      |  |

|      | 0x7F    |             |                 |               | r     |          |          |       |       |       |      |  |

#### TABLE 2-7: LONG ADDRESS REGISTER SUMMARY FOR MRF24XA

#### 2.6.2 ADDRESS

When using a Short Addressing mode, the Address field is 6 bits wide to reduce framing overhead while accessing the mostly active registers (0x00..0x3F). In Long Addressing mode, the Address field is 10 bits wide (0x00..0x3FF) thus all the address is available for SPI operation.

#### 2.6.3 AUTOMATIC TX START FEATURE

When a write to TRXBUF is done using Long Addressing mode and the 3rd bit of Byte 2 is set, the TXST bit automatically sets after the  $\overline{CS}$  pin is released, and then MRF24XA sends the packet.

#### 2.6.4 AUTOMATIC BUFFER FLUSH FEATURE

When a read from TRXBUF is done using Long Addressing mode and the 3rd bit of Byte 2 is set, the BUFFULL bit automatically becomes cleared after the CS pin is negated.

#### 2.6.5 ADDRESS AUTO-INCREMENT FEATURE

After the starting address is loaded, the first byte of data is read from or written to this address. The second byte (assuming the  $\overline{CS}$  pin is not negated between bytes) is read from or written to the starting address plus one, and so on.

If the memory map end is reached, the effective address rolls over to the beginning of the memory map. It is the sole responsibility of the software to handle this situation correctly. Figure 2-4 illustrates the available Address modes.

FIGURE 2-4: SPI FRAMING TYPES

#### 2.7 **Register Details**

#### **OPSTATUS (OPERATION STATUS)**<sup>(3)</sup> **REGISTER 2-1:** R/HS/HC-0 R/HS/HC-0 R/HS/HC-0 R/HS/HC-0 R/HS/HC-0 R-0 R/HS/HC-0 R/HS/HC-0 RFOP<2:0> MACOP<3:0> r bit 7 bit 0 Legend: R = Readable W = Writable bit U = Unimplemented bit, read as '0' bit -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown

bit 7 Reserved: Maintain as '0'

r = Reserved

#### bit 6-3 MACOP<3:0>: MAC Operation Register bits<sup>(1, 2)</sup>

Provides status information on the current MAC state machine state. Encoding on MACOP<3:1>:

HS = Hardware Set

- 111 = Transmitting Acknowledge (TXACK)

- 110 = Receiving a packet (RXBUSY)

- 101 = Receiver listening to the channel waiting for packet (RX)

- 100 = Receiving (or waiting for) Acknowledge (RXACK)

HC = Hardware Clear

- 011 = Transmitting a packet (TX)

- 010 = Performing Clear Channel Assessment (CCA)

- 001 = Back-off before repeated CCA (BO)

- 000 = MAC does not perform any o ation (IDLE)

#### bit 2-0 RFOP<2:0>: Radio Operation Register bits

Provides status information on the current radio state. Encoding on RFOP<2:0>:

- 111 = TX with external PA is turned on (TX+PA)

- 110 = RX with external LNA is turned on (RX+LNA)

- 101 = Synthesizer and external PA or LNA is turned on (SYNTH+PA/LNA)

- 100 = Radio calibrates if the host MCU sets the CALST, otherwise, device malfunction occurs (CAL/MAL)

- 011 = Analog transmit chain is activated (TX)

- 010 = Analog receiver chain is active (RX). Digital may be partially shut off

- 001 = Synthesizer is steady or ramping up or channel change is issued (SYNTH)

- 000 = Only the crystal oscillator is ON (OFF), (except when XTALSF = 1)

- Note 1: GPIO<2:0> is dedicated to output MACOP<3:1> or RFOP<2:0>. Refer to the PINCON register, which specifies the pin Configuration.

- MACOP<0> is connected to the RXBUFFUL register bit. It cannot be output over GPIO's.

- 3: The OPSTATUS register is sent on the SDO pin during the first byte of the SPI operation.

Address: 0x02

| R/HS            | R/HS           | R/HS             | R/W/HC-0                           | R/W-0                                | R/W-0            | R/HS            | R/W/HC          |

|-----------------|----------------|------------------|------------------------------------|--------------------------------------|------------------|-----------------|-----------------|

| INITDONESF      | XTALSF         | REGSF            | CALST                              | XTALDIS                              | DSLEEP           | IDLESF          | POR             |

| bit 7           | XII/LEOI       | TLEOOI           | 0,1201                             | XIIILEBIO                            | DOLLEI           | IDEEOI          | bit (           |

|                 |                |                  |                                    |                                      |                  |                 | bit             |

| Legend: R =     | Readable bit   | W = Writable     | e bit                              | U = Unimplem                         | nented bit, read | as '0'          |                 |

| -n = Value at P |                | '1' = Bit is se  | t                                  | '0' = Bit is clea                    |                  | x = Bit is unk  | nown            |

| r = Reserved    |                | HC = Hardw       | are Clear                          | HS = Hardwa                          | re Set           |                 |                 |

|                 |                |                  |                                    |                                      |                  |                 |                 |

| bit 7           | INITDONES      | F: Device Initia | lization Status                    | Flag bit                             |                  |                 |                 |

|                 |                |                  |                                    | since the LDC                        |                  |                 |                 |

|                 | DEVFRST ar     | nd PINRST).      |                                    |                                      |                  |                 |                 |

| bit 6           | -              | ystal Status Fla | -                                  |                                      |                  |                 |                 |

|                 |                |                  |                                    | em clock (from<br>s set or reset (F  |                  |                 | ive. This bit i |

|                 |                |                  |                                    | llator is either p                   |                  |                 | is ramping u    |

|                 |                |                  |                                    | system clock is                      |                  | ,               |                 |

| oit 5           | REGSF: Cor     | nfiguration Reg  | jisters Status F                   | lag bit                              |                  |                 |                 |

|                 |                |                  |                                    | ster content is                      |                  |                 |                 |

|                 |                |                  | from the retent                    | loes not hold ar<br>ion memory.      | iy data to resto | re, or the regi | ster configura  |

|                 |                |                  |                                    | 08-0x6E are inv                      |                  |                 |                 |

|                 |                |                  |                                    | not complete the<br>VFRST, and PI    |                  | ore operation   | yet. This bit   |

| bit 4           |                | bration Start bi |                                    |                                      | Nixor).          |                 |                 |

|                 |                |                  |                                    | dure after a CAL                     | SOIF or CALH     | AIF interrupt o | occurred. MC    |

|                 | may not clea   | ar it to abort C | alibration. The                    | device clears                        | CALST when th    | he Calibration  | is complete     |

|                 |                |                  |                                    | IF = 1 indicates                     |                  | ig CALST ope    | eration withou  |

| bit 3           |                | rystal Disable   |                                    | y effect on the                      | uevice.          |                 |                 |

|                 |                | •                |                                    | TAL OFF state (                      | roachable from   | roady state)    |                 |

|                 |                |                  |                                    | cess is perform                      |                  |                 |                 |

| bit 2           |                | ep-Sleep bit     | U U                                |                                      |                  |                 | 0               |

|                 |                |                  |                                    | eep Sleep state                      | •                |                 |                 |

|                 |                |                  |                                    | ust be quite, un<br>ansitions throug |                  |                 |                 |

|                 | LDO is powe    |                  |                                    |                                      | Integister back  | up (laking cca  |                 |

| bit 1           |                | Status Flag b    | it                                 |                                      |                  |                 |                 |

|                 | Indicates Idle | e state of the d | evice when all                     | of the following                     | bits are deasse  | erted:          |                 |

|                 |                |                  | e it is transmitte                 |                                      |                  |                 |                 |

|                 |                |                  | nished (TXENC                      | )                                    |                  |                 |                 |

|                 |                | gine finished (F | -                                  | · · · ·                              |                  |                 |                 |

|                 |                | -                | finished (EDST<br>ent finished (CC |                                      |                  |                 |                 |

| bit 0           |                | -on-Reset Flag   | -                                  |                                      |                  |                 |                 |

|                 |                |                  |                                    | sets this only                       | on 3.3V nowe     | r-up (ea wi     | nen hatterv i   |

|                 |                | -                |                                    | e to sense a Bro                     |                  |                 | -               |

| R/HS-1          | R-0           | R/HS-0                           | R/W/HC-0         | R-0              | R/W/HS-0          | R/W/HS-0                     | R-0            |

|-----------------|---------------|----------------------------------|------------------|------------------|-------------------|------------------------------|----------------|

| VREGIF          | r             | RDYIF                            | IDLEIF           | r                | CALSOIF           | CALHAIF                      | r              |

| bit 7           |               |                                  |                  |                  |                   |                              | bit            |

|                 |               |                                  |                  |                  |                   |                              |                |

| Legend: R =     |               | W = Writable                     |                  |                  | mented bit, rea   |                              |                |

| -n = Value at P | OR            | '1' = Bit is se                  | t                | '0' = Bit is cle | eared             | x = Bit is unkno             | own            |

| r = Reserved    |               | HC = Hardw                       | are Clear        | HS = Hardwa      | are Set           |                              |                |

|                 |               |                                  |                  |                  |                   |                              |                |

| bit 7           |               | • •                              | r On Interrupt F | •                |                   |                              |                |

|                 |               |                                  |                  |                  |                   | et except for PIN            |                |

| hit C           | •             | nen reading P<br>Iaintain as '0' | IR1. Note that   | the correspond   | aing ie bit is no | ot implemented <sup>(1</sup> | <b>'</b> .     |

| bit 6           |               |                                  |                  |                  |                   |                              |                |

| bit 5           |               | dy State Interru                 |                  | al.              |                   |                              |                |

|                 |               | •                                | state is reached | u:               |                   |                              |                |

|                 |               | oration ended (                  | (INITDONESF      | (- 1)            |                   |                              |                |

|                 |               |                                  | p (XTALSF = $1$  | ,                |                   |                              |                |

|                 | •             | ared when PIF                    | • •              | -)               |                   |                              |                |

| bit 4           |               | State Interrupt                  |                  |                  |                   |                              |                |

|                 |               | -                                | -                | I did not triggo | r this change 1   | This is unchange             | d whon MC      |

|                 |               |                                  |                  |                  |                   | bits. This bit is c          |                |

|                 | PIR1 is read. |                                  | ,                | .,,,             |                   |                              |                |

| bit 3           | Reserved: N   | <b>laintain as</b> '0'           |                  |                  |                   |                              |                |

| bit 2           | CALSOIF: C    | alibration Soft                  | Interrupt Flag I | bit              |                   |                              |                |

|                 | CALSOIF = 1   | indicates that                   | Calibration is r | needed (CALS     | T) although the   | radio is still fund          | tional. It als |

|                 |               |                                  |                  |                  |                   | consumption, a               | nd a risk o    |

|                 |               |                                  | -                |                  | n PIR1 is read.   |                              |                |

| bit 1           | CALHAIF: C    | alibration Harc                  | l Interrupt Flag | bit              |                   |                              |                |

|                 |               |                                  |                  | •                | ,                 | ory, otherwise the           |                |

|                 |               | functional. The<br>read.         | e device enters  | s into malfunct  | tion state. This  | bit is cleared w             | hen PIR1       |

| bit 0           |               | laintain as '0'                  |                  |                  |                   |                              |                |

|                 | iteseiveu. IV | iaiiiaiii as U                   |                  |                  |                   |                              |                |

#### **Note 1:** Generated non-maskable interrupt is gated off until the 1.2V reset is released.

| R/W/HS/HC-0     | R/W/HS/HC-0                                          | R/W/HS/HC-0       | R/W/HS/HC-0      | R/W/HS/HC-0                        | R/W/HS/HC-0                                              | R/W/HS/HC-0      | R/W/HS/HC-0     |  |  |  |

|-----------------|------------------------------------------------------|-------------------|------------------|------------------------------------|----------------------------------------------------------|------------------|-----------------|--|--|--|

| TXIF            | TXENCIF                                              | TXMAIF            | TXACKIF          | TXCSMAIF                           | TXSZIF                                                   | TXOVFIF          | FRMIF           |  |  |  |

| bit 7           |                                                      |                   |                  |                                    |                                                          |                  | bit (           |  |  |  |

| Legend: R =     | Readable bit                                         | W = Writable      | bit              | U = Unimplen                       | nented bit, read                                         | as '0'           |                 |  |  |  |

| -n = Value at F | POR                                                  | '1' = Bit is set  |                  | '0' = Bit is clea                  | ared                                                     | x = Bit is unkr  | nown            |  |  |  |

| r = Reserved    |                                                      | HC = Hardwa       | re Clear         | HS = Hardwa                        | re Set                                                   |                  |                 |  |  |  |

| bit 7           | TXIF: Transm                                         | ission Done Int   | errupt Flag bit  |                                    |                                                          |                  |                 |  |  |  |

|                 |                                                      | K packet com      |                  |                                    | d. This event is<br>when a packet                        |                  |                 |  |  |  |

| bit 6           | TXENCIF: Tra                                         | insmit Encrypti   | on Interrupt Fla | ag bit                             |                                                          |                  |                 |  |  |  |

|                 |                                                      |                   |                  |                                    | ed, or both wit<br>cleared. Nonpe                        |                  |                 |  |  |  |

| bit 5           | TXMAIF: Transmitter Medium Access Interrupt Flag bit |                   |                  |                                    |                                                          |                  |                 |  |  |  |

|                 |                                                      |                   |                  | essed specifica<br>red by SPI read | ally when the fi<br>d.                                   | rst sample in th | ne preamble i   |  |  |  |

| bit 4           | TXACKIF: Tra                                         | ansmission Una    | acknowledged     | Failure Interrup                   | ot Flag bit                                              |                  |                 |  |  |  |

|                 | mission retrie                                       | s RETXMCNT        | <3:0>, provide   |                                    | r the configured<br>ame Control fic                      |                  |                 |  |  |  |

| bit 3           | TXCSMAIF: T                                          | ransmitter CSI    | MA Failure Inte  | errupt Flag bit                    |                                                          |                  |                 |  |  |  |

|                 | •                                                    |                   |                  | channel busy f                     | or BOMCNT<2:<br>/ SPI read.                              | 0> number of ti  | imes, provide   |  |  |  |

| bit 2           | TXSZIF: Trans                                        | smit Packet Siz   | ze Error Interru | ipt Flag bit                       |                                                          |                  |                 |  |  |  |

|                 | maximum size<br>user. Please r                       | e that the buffer | can support.     | Automatic size                     | uffer) is found to<br>check is perfor<br>ength after CRC | med after TXS    | T is set by the |  |  |  |

| bit 1           | TXOVFIF: Tra                                         | insmitter Overf   | low Interrupt F  | lag bit                            |                                                          |                  |                 |  |  |  |

|                 | The Host Con                                         | troller attempte  | ed to write a Τλ | K buffer that wa                   | s not empty (T                                           | XBUFEMPTY =      | = 0).           |  |  |  |

|                 | Nonpersistent                                        | , cleared by SF   | PI read.         |                                    |                                                          |                  |                 |  |  |  |

| bit 0           | FRMIF: Frame                                         | e Format Error    | Interrupt Flag   | bit                                |                                                          |                  |                 |  |  |  |

|                 | Set if the trans<br>corrupted in d                   |                   | fails to parse   | the frame in the                   | e buffer (it is no                                       | t as it must be  | or it is        |  |  |  |

| R/W/HS/HC-0   | R/W/HS/HC-0                                                                                                                                                                           | R/W/HS/HC-0      | R-0           | R/W/HS/HC-0                                                 | R/W/HS/HC-0       | R/W/HS/HC-0 | R/W/HS/HC-0 |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------------------------------------------------|-------------------|-------------|-------------|--|--|--|

| RXIF          | RXDECIF                                                                                                                                                                               | RXTAGIF          | r             | RXIDENTIF                                                   | RXFLTIF           | RXOVFIF     | STRMIF      |  |  |  |

| bit 7         |                                                                                                                                                                                       |                  |               |                                                             |                   |             | bit (       |  |  |  |

|               |                                                                                                                                                                                       |                  |               |                                                             |                   | (0)         |             |  |  |  |

| •             |                                                                                                                                                                                       | W = Writable k   | Dit           | •                                                           | nented bit, read  |             |             |  |  |  |

| -n = Value at | POR                                                                                                                                                                                   | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown                     |                   |             |             |  |  |  |

| r = Reserved  |                                                                                                                                                                                       | HC = Hardwar     | e Clear       | HS = Hardwa                                                 | re Set            |             |             |  |  |  |

| bit 7         | RXIF: Receive                                                                                                                                                                         | ed Successful I  | nterrupt Flag | j bit                                                       |                   |             |             |  |  |  |

|               | flag is only set                                                                                                                                                                      | once for a pack  | et and is not | cket filtering and a set when the pac<br>busly received fra | ket is the duplic |             |             |  |  |  |

|               | Nonpersistent, cleared by SPI read.                                                                                                                                                   |                  |               |                                                             |                   |             |             |  |  |  |

| bit 6         | RXDECIF: Receiver Decryption/Authentication Passed Interrupt Flag bit                                                                                                                 |                  |               |                                                             |                   |             |             |  |  |  |

|               | Set by the device when decryption/authentication finished without error.                                                                                                              |                  |               |                                                             |                   |             |             |  |  |  |

|               | Nonpersistent, cleared by SPI read.                                                                                                                                                   |                  |               |                                                             |                   |             |             |  |  |  |

| bit 5         | <b>RXTAGIF:</b> Receiver Decryption/Authentication Failure Interrupt Flag bit                                                                                                         |                  |               |                                                             |                   |             |             |  |  |  |

|               | Set by the device when decryption/authentication finished with error.                                                                                                                 |                  |               |                                                             |                   |             |             |  |  |  |

|               | Nonpersistent                                                                                                                                                                         | , cleared by SF  | l read.       |                                                             |                   |             |             |  |  |  |

| bit 4         | Reserved: Ma                                                                                                                                                                          | aintain as '0'   |               |                                                             |                   |             |             |  |  |  |

| bit 3         | <b>RXIDENTIF:</b> Received Packet Identical Interrupt Flag bit                                                                                                                        |                  |               |                                                             |                   |             |             |  |  |  |

|               | •                                                                                                                                                                                     | •                |               | duplicate of a re sly received fram                         |                   | • •         |             |  |  |  |

| bit 2         | RXFLTIF: Received Packet Filtered Interrupt Flag bit                                                                                                                                  |                  |               |                                                             |                   |             |             |  |  |  |

|               | Set by the device when a packet is received, but rejected by one or more RX Filters, refer to Register 2 23.                                                                          |                  |               |                                                             |                   |             |             |  |  |  |

|               | Nonpersistent, cleared by SPI read.                                                                                                                                                   |                  |               |                                                             |                   |             |             |  |  |  |

| bit 1         | RXOVFIF: Receiver Overflow Error Interrupt Flag bit                                                                                                                                   |                  |               |                                                             |                   |             |             |  |  |  |

|               | Set by the device to indicate that a packet was received, but all RX buffers were full. Consequently th packet was not received, but was discarded instead <sup>(1)</sup> .           |                  |               |                                                             |                   |             |             |  |  |  |

|               | Nonpersistent, cleared by SPI read.                                                                                                                                                   |                  |               |                                                             |                   |             |             |  |  |  |

| bit 0         | STRMIF: Receive Stream Time-Out Error Interrupt Flag bit                                                                                                                              |                  |               |                                                             |                   |             |             |  |  |  |

|               | Set by the device to indicate that the duration specified in STRMTO elapsed since the last received packet while in RX-Streaming mode, and the MAC clears the stored sequence number. |                  |               |                                                             |                   |             |             |  |  |  |

|               | Nonpersistent                                                                                                                                                                         | cleared by SP    | Iread         |                                                             |                   |             |             |  |  |  |

**Note 1:** In Packet mode, use a single buffer for received frames. In RX-Streaming mode, use both buffers for reception.

| R/W/H5/HC-U   | R/W/HS/HC-0                                                                                                                                                                                     | R/W/HS/HC-0      | R/W/HS/HC-0       | R/W/HS/HC-0                                     | R/W/HS/HC-0      | R/W/HS/HC-0    | R/W/HS/HC-0    |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------------------------------------|------------------|----------------|----------------|--|--|--|--|

| TXSFDIF       | RXSFDIF                                                                                                                                                                                         | ERRORIF          | WARNIF            | EDCCAIF                                         | GPIO2IF          | GPI01IF        | <b>GPIO0IF</b> |  |  |  |  |

| bit 7         | 1                                                                                                                                                                                               |                  |                   | I                                               |                  | 1              | bit (          |  |  |  |  |

|               |                                                                                                                                                                                                 |                  |                   |                                                 |                  |                |                |  |  |  |  |

| •             | = Readable bit                                                                                                                                                                                  |                  | oit               | -                                               | nented bit, read |                |                |  |  |  |  |