Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**Data Sheet**

Document Number: MSC7110

Rev. 11, 4/2008

# **MSC7110**

# MAP-BGA-400 17 mm × 17 mm

# Low-Cost 16-bit DSP with DDR Controller

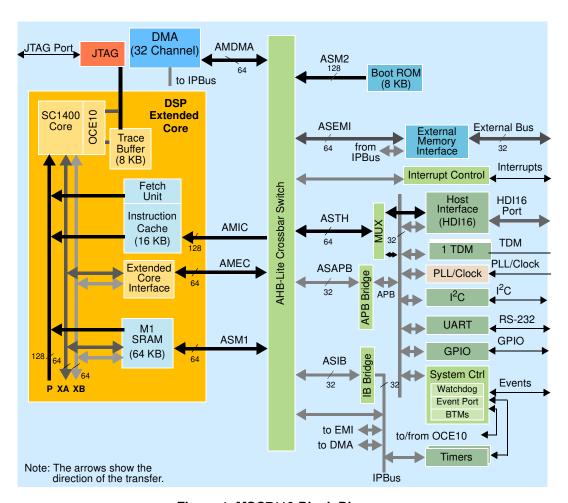

- StarCore<sup>®</sup> SC1400 DSP extended core with one SC1400 DSP core, 64 Kbyte of internal SRAM M1 memory, 16 way 16 Kbyte instruction cache (ICache), four-entry write buffer, programmable interrupt controller (PIC), and low-power Wait and Stop processing modes.

- 8 Kbyte boot ROM.

- AHB-Lite crossbar switch that allows parallel data transfers between four master ports and six slave ports, where each port connects to an AHB-Lite bus; fixed or round robin priority programmable at each slave port; programmable bus parking at each slave port; low power mode.

- Internal PLL generates up to 266 MHz clock for the SC1400 core and up to 133 MHz for the crossbar switch, DMA channels, and other peripherals.

- Clock synthesis module provides predivision of PLL input clock; independent clocking of the internal timers and DDR module; programmable operation in the SC1400 low power Stop mode; independent shutdown of different regions of the device.

- Enhanced 16-bit wide host interface (HDI16) provides a glueless connection to industry-standard microcomputers, microprocessors, and DSPs and can also operate with an 8-bit host data bus, making if fully compatible with the DSP56300 HI08 from the external host side.

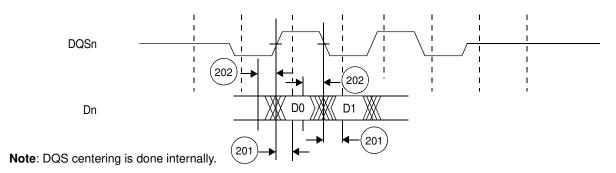

- DDR memory controller that supports byte enables for up to a 32-bit data bus; glueless interface to 133 MHz 14-bit page mode DDR-RAM; 14-bit external address bus supporting up to 1 Gbyte; and 16-bit or 32-bit external data bus.

- Programmable memory interface with independent read buffers, programmable predictive read feature for each buffer, and a write buffer.

- System control unit performs software watchdog timer function; includes programmable bus time-out monitors on AHB-Lite slave buses; includes bus error detection and programmable time-out monitors on AHB-Lite master buses; and has address out-of-range detection on each crossbar switch buses.

- Event port collects and counts important signal events including DMA and interrupt requests and trigger events such as interrupts, breakpoints, DMA transfers, or wake-up events; units operate independently, in sequence, or triggered externally; can be used standalone or with the OCE10.

- Multi-channel DMA controller with 32 time-multiplexed unidirectional channels, priority-based time-multiplexing between channels using 32 internal priority levels, fixed- or round-robin-priority operation, major-minor loop structure, and DONE or DRACK protocol from requesting units.

- One TDM module with independent receive and transmit, programmable sharing of frame sync and clock, programmable word size (8 or 16-bit), hardware-base A-law/μ-law conversion, up to 50 Mbps data rate, up to 128 channels, with glueless interface to E1/T1 frames and MVIP, SCAS, and H.110 buses.

- UART with full-duplex operation up to 5.0 Mbps.

- Up to 41 general-purpose input/output (GPIO) ports.

- I<sup>2</sup>C interface that allows booting from EEPROM devices up to 1 Mbyte.

- Two quad timer modules, each with sixteen configurable 16-bit timers.

- fieldBIST<sup>TM</sup> unit detects and provides visibility into unlikely field failures for systems with high availability to ensure structural integrity, that the device operates at the rated speed, is free from reliability defects, and reports diagnostics for partial or complete device inoperability.

- Standard JTAG interface allows easy integration to system firmware and internal on-chip emulation (OCE10) module.

- Optional booting external host via 8-bit or 16-bit access through the HDI16, I<sup>2</sup>C, or SPI using in the boot ROM to access serial SPI Flash/EEPROM devices; different clocking options during boot with the PLL on or off using a variety of input frequency ranges.

# **Table of Contents**

| 1   |         | ssignments4                                       | Figure 6.  | DDR DRAM Output Timing Diagram               |    |

|-----|---------|---------------------------------------------------|------------|----------------------------------------------|----|

|     | 1.1     | MAP-BGA Ball Layout Diagrams                      | Figure 7.  | DDR DRAM AC Test Load                        | 26 |

|     | 1.2     | Signal List By Ball Location6                     | Figure 8.  | TDM Receive Signals                          | 27 |

| 2   | Speci   | ifications                                        | Figure 9.  | TDM Transmit Signals                         | 27 |

|     | 2.1     | Maximum Ratings                                   | Figure 10. | Read Timing Diagram, Single Data Strobe      | 29 |

|     | 2.2     | Recommended Operating Conditions18                | Figure 11. | Read Timing Diagram, Double Data Strobe      | 30 |

|     | 2.3     | Thermal Characteristics                           | Figure 12. | Write Timing Diagram, Single Data Strobe     | 30 |

|     | 2.4     | DC Electrical Characteristics                     | Figure 13. | Write Timing Diagram, Double Data Strobe     | 31 |

|     | 2.5     | AC Timings                                        | Figure 14. | Host DMA Read Timing Diagram, HPCR[OAD] = 0  | 31 |

| 3   | Hardy   | ware Design Considerations38                      | Figure 15. | Host DMA Write Timing Diagram, HPCR[OAD] = 0 | 32 |

|     | 3.1     | Thermal Design Considerations                     | Figure 16. | I2C Timing Diagram                           | 33 |

|     | 3.2     | Power Supply Design Considerations                |            | UART Input Timing                            |    |

|     |         | Estimated Power Usage Calculations                |            | UART Output Timing                           |    |

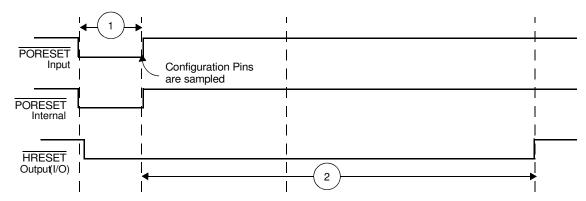

|     | 3.4     | Reset and Boot                                    |            | EE Pin Timing                                |    |

|     | 3.5     | DDR Memory System Guidelines 50                   |            | EVNT Pin Timing                              |    |

| 4   |         | ring Information53                                |            | GPI/GPO Pin Timing                           |    |

| 5   | Packa   | age Information54                                 |            | Test Clock Input Timing Diagram              |    |

| 6   | Produ   | uct Documentation                                 |            | Boundary Scan (JTAG) Timing Diagram          |    |

| 7   | Revis   | ion History                                       |            | Test Access Port Timing Diagram              |    |

|     |         |                                                   | Figure 25. | TRST Timing Diagram                          | 37 |

| LIS | St Ot I | Figures                                           |            | Voltage Sequencing Case 1                    |    |

| Fig | ure 1.  | MSC7110 Block Diagram                             |            | Voltage Sequencing Case 2                    |    |

| Fig | ure 2.  | MSC7110 Molded Array Process-Ball Grid Array      | •          | Voltage Sequencing Case 3                    |    |

|     |         | (MAP-BGA), Top View 4                             | -          | Voltage Sequencing Case 4                    |    |

| Fig | ure 3.  | MSC7110 Molded Array Process-Ball Grid Array      |            | Voltage Sequencing Case 5                    |    |

|     |         | (MAP-BGA), Bottom View 5                          |            | PLL Power Supply Filter Circuits             |    |

| Fig | ure 4.  | Timing Diagram for a Reset Configuration Write 24 |            | SSTL Termination Techniques                  |    |

| Fig | ure 5.  | DDR DRAM Input Timing Diagram 24                  |            | SSTL Power Value                             |    |

Figure 1. MSC7110 Block Diagram

# 1 Pin Assignments

This section includes diagrams of the MSC7110 package ball grid array layouts and pinout allocation tables.

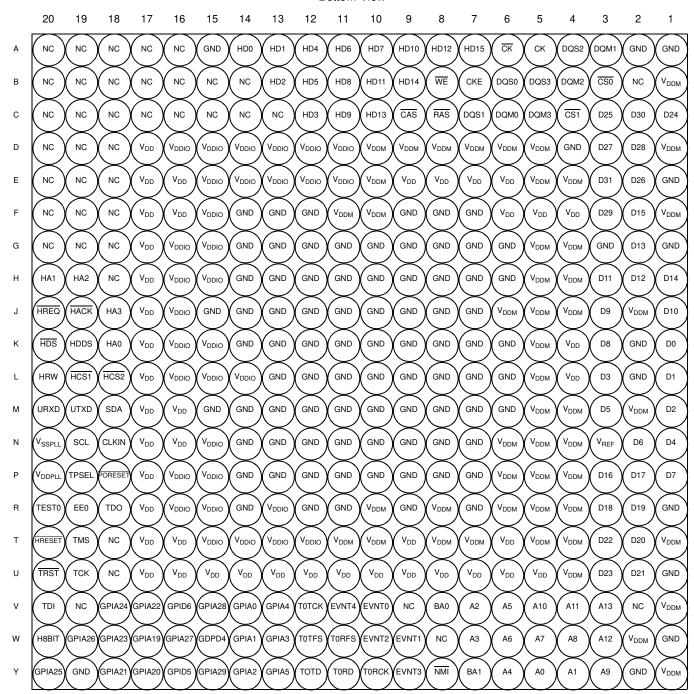

## 1.1 MAP-BGA Ball Layout Diagrams

Top and bottom views of the MAP-BGA package are shown in Figure 2 and Figure 3 with their ball location index numbers.

Top View 10 1 5 6 12 13 14 15 16 17 18 19 20 HD15 HD12 HD10 GND DQM1 DQS2 HD7 HD6 HD4 HD1 HD0 GND NC NC CS0 DQM2 DQS3 DQS0 CKE WE HD14 HD11 HD5 HD2 HD8 NC В  $V_{DDM}$ CS1 DQM3 RAS CAS D25 DQM0 DQS1 HD13 HD9 HD3 D30 NC GND  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$ V<sub>DDIO</sub> V<sub>DDIC</sub> V<sub>DDIO</sub> V<sub>DDIO</sub> V<sub>DDIO</sub> V<sub>DDIO</sub>  $V_{DDC}$ NC D GND D26 D31 NC  $V_{\mathsf{DDM}}$  $V_{DDM}$  $V_{\text{DDC}}$  $V_{DDC}$  $V_{DDC}$  $V_{DDC}$  $V_{\text{DDM}}$  $V_{DDIO}$ V<sub>DDIC</sub> V<sub>DDIO</sub>  $V_{DDIO}$  $V_{DDIO}$  $V_{DDC}$ Ε D15 D29  $V_{DDC}$  $V_{DDC}$ GND GND GND  $V_{DDM}$  $V_{DDM}$ GND GND GND NC G  $V_{DDM}$  $V_{DDM}$ V<sub>DDIO</sub> V<sub>DDIO</sub>  $V_{DDC}$ NC D12 D11  $V_{DDM}$ GND GND GND GND GND GND GND GND GND HA1  $V_{\text{DDM}}$  $V_{DDIO}$ Н V<sub>DDM</sub>  $V_{\mathsf{DDM}}$ GND GND GND GND GND GND GND GND GND  $V_{DDIO}$  $V_{DDC}$ НАЗ HACK HREC D10 HDS  $V_{DDM}$  $V_{DDIO}$ Κ  $V_{DDC}$ V<sub>DDIO</sub> GND  $V_{DDC}$  $V_{DDM}$ GND GND GND GND GND GND GND GND  $V_{DDIO}$ V<sub>DDIO</sub> V<sub>DDIO</sub>  $V_{DDC}$ HCS2 HCS1 HRW GND GND GND  $V_{DDM}$  $V_{DDM}$ GND GND GND GND GND GND GND  $V_{DDC}$ UTXD URXD  $V_{DDM}$ D5 SDA V<sub>REF</sub>  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$  $V_{DDIO}$  $V_{DDC}$  $V_{DDC}$ CLKIN Ν V<sub>SSPLI</sub> D17 GND GND GND GND GND GND GND GND ORESE  $V_{DDM}$  $V_{DDM}$  $V_{DDIO}$ V<sub>DDIO</sub>  $V_{DDPL}$ D19 D18  $V_{DDM}$  $V_{DDM}$  $V_{DDM}$ GND  $V_{DDM}$ GND  $V_{\mathsf{DDM}}$ GND GND V<sub>DDIO</sub> GND V<sub>DDIC</sub>  $V_{DDIC}$  $V_{DDC}$ TDO EE0 TEST R D20  $V_{DDM}$  $V_{DDM}$  $V_{\text{DDC}}$  $V_{DDM}$  $V_{\text{DDM}}$  $V_{DDC}$  $V_{\mathsf{DDM}}$  $V_{DDM}$  $V_{DDIO}$  $V_{DDIO}$  $V_{DDIO}$ V<sub>DDIO</sub>  $V_{DDC}$ HRESE  $V_{DDC}$ TRST IJ D21  $V_{DDM}$  $V_{DDC}$  $V_{DDC}$ A10 EVNT4 , TOTCł GPIA4 GPIA28 NC A13 A11 Α5 A2 BA0 NC EVNT0 GPIA0 GPID , GPIA2 GPIA2 TDI T0TFS GPIA3 EVNT1 EVNT2 T0RFS GPIA1 GDPD4 GPIA2 GPIA19 GPIA2 H8BIT GND NMI . EVNT3 , TORCK T0RD TOTD GPIA5 GPIA2 GPIA29 GPID5  $V_{DDM}$

Note: The display is for mask set 1L44X. For mask set 1M88B, A16 is BM3 and B15 is BM2.

Figure 2. MSC7110 Molded Array Process-Ball Grid Array (MAP-BGA), Top View

MSC7110 Low-Cost 16-bit DSP with DDR Controller Data Sheet, Rev. 11

#### **Bottom View**

Note: The display is for mask set 1L44X. For mask set 1M88B, A16 is BM3 and B15 is BM2.

Figure 3. MSC7110 Molded Array Process-Ball Grid Array (MAP-BGA), Bottom View

# 1.2 Signal List By Ball Location

**Table 1** lists the signals sorted by ball number and configuration.

Table 1. MSC7110 Signals by Ball Designator

|             | Signal Names |                          |                      |              |         |           |  |  |  |

|-------------|--------------|--------------------------|----------------------|--------------|---------|-----------|--|--|--|

| Number      |              | Hardware Controlled      |                      |              |         |           |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled  | Primary | Alternate |  |  |  |

| A1          |              |                          | G                    | ND           |         |           |  |  |  |

| A2          |              |                          | G                    | ND           |         |           |  |  |  |

| A3          |              |                          | DC                   | QM1          |         |           |  |  |  |

| A4          |              |                          | DC                   | QS2          |         |           |  |  |  |

| A5          |              |                          | C                    | CK           |         |           |  |  |  |

| A6          |              |                          | C                    | <del>K</del> |         |           |  |  |  |

| A7          |              | GPIC7                    |                      | GPOC7        | Н       | D15       |  |  |  |

| A8          |              | GPIC4                    |                      | GPOC4        | Н       | D12       |  |  |  |

| A9          |              | GPIC2                    |                      | GPOC2        | Н       | D10       |  |  |  |

| A10         |              | rese                     | rved                 |              | Н       | D7        |  |  |  |

| A11         |              | rese                     | rved                 |              | Н       | D6        |  |  |  |

| A12         |              | rese                     | rved                 |              | HD4     |           |  |  |  |

| A13         |              | rese                     | rved                 |              | HD1     |           |  |  |  |

| A14         |              | rese                     | rved                 |              | Н       | D0        |  |  |  |

| A15         |              |                          | G                    | ND           |         |           |  |  |  |

| A16 (1L44X) |              |                          | N                    | IC           |         |           |  |  |  |

| A16 (1M88B) | ВМ3          | GP                       | ID8                  | GPOD7        | rese    | erved     |  |  |  |

| A17         |              |                          | N                    | IC           |         |           |  |  |  |

| A18         |              |                          | N                    | IC           |         |           |  |  |  |

| A19         |              |                          | N                    | IC           |         |           |  |  |  |

| A20         |              |                          | N                    | IC           |         |           |  |  |  |

| B1          |              |                          | V                    | DDM          |         |           |  |  |  |

| B2          |              |                          | N                    | IC           |         |           |  |  |  |

| B3          |              |                          | C                    | <u>S0</u>    |         |           |  |  |  |

| B4          |              |                          | DC                   | QM2          |         |           |  |  |  |

| B5          |              |                          | DC                   | QS3          |         |           |  |  |  |

| В6          |              |                          | DC                   | QS0          |         |           |  |  |  |

| В7          |              |                          | С                    | KE           |         |           |  |  |  |

| B8          |              |                          | V                    | VE           |         |           |  |  |  |

| В9          |              | GPIC6                    |                      | GPOC6        | н       | D14       |  |  |  |

| B10         |              | GPIC3                    |                      | GPOC3        | Н       | D11       |  |  |  |

| B11         |              | GPIC0                    |                      | GPOC0        | Н       | D8        |  |  |  |

| B12         |              | rese                     | rved                 |              | Н       | D5        |  |  |  |

| B13         |              | rese                     | rved                 |              | Н       | D2        |  |  |  |

| B14         |              |                          | N                    | IC           |         |           |  |  |  |

| B15 (1L44X) |              |                          | N                    | IC           |         |           |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|             | Signal Names |                          |                      |             |          |            |  |  |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|--|

| Number      |              | s                        | oftware Controlle    | ed          | Hardware | Controlled |  |  |  |  |

| Number      | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |  |

| B15 (1M88B) | BM2          | GP                       | ID7                  | GPOD7       | res      | erved      |  |  |  |  |

| B16         |              |                          | N                    | IC          |          |            |  |  |  |  |

| B17         |              |                          | N                    | IC          |          |            |  |  |  |  |

| B18         |              |                          | N                    | IC          |          |            |  |  |  |  |

| B19         |              |                          | Ν                    | IC          |          |            |  |  |  |  |

| B20         |              |                          | N                    | IC          |          |            |  |  |  |  |

| C1          |              |                          | D                    | 24          |          |            |  |  |  |  |

| C2          |              |                          | D                    | 30          |          |            |  |  |  |  |

| C3          |              |                          | D                    | 25          |          |            |  |  |  |  |

| C4          |              |                          | C                    | <u>S1</u>   |          |            |  |  |  |  |

| C5          |              |                          | DC                   | QM3         |          |            |  |  |  |  |

| C6          |              |                          | DC                   | QM0         |          |            |  |  |  |  |

| C7          | DQS1         |                          |                      |             |          |            |  |  |  |  |

| C8          |              |                          | R                    | AS          |          |            |  |  |  |  |

| C9          |              | CAS                      |                      |             |          |            |  |  |  |  |

| C10         |              | GPIC5                    |                      | GPOC5       | HD13     |            |  |  |  |  |

| C11         |              | GPIC1                    |                      | GPOC1       | F        | HD9        |  |  |  |  |

| C12         |              | rese                     | rved                 |             | F        | HD3        |  |  |  |  |

| C13         |              |                          | ٨                    | IC          |          |            |  |  |  |  |

| C14         |              |                          | Λ                    | IC          |          |            |  |  |  |  |

| C15         |              |                          | ٨                    | IC          |          |            |  |  |  |  |

| C16         |              |                          | Λ                    | IC          |          |            |  |  |  |  |

| C17         |              |                          | Λ                    | IC          |          |            |  |  |  |  |

| C18         |              |                          | Λ                    | IC          |          |            |  |  |  |  |

| C19         |              |                          | ٨                    | IC          |          |            |  |  |  |  |

| C20         |              |                          | ٨                    | IC          |          |            |  |  |  |  |

| D1          |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |  |  |

| D2          |              |                          | D                    | 28          |          |            |  |  |  |  |

| D3          |              |                          | D                    | 27          |          |            |  |  |  |  |

| D4          |              |                          | Gi                   | ND          |          |            |  |  |  |  |

| D5          |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |  |  |

| D6          |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |  |  |

| D7          |              |                          |                      | DDM         |          |            |  |  |  |  |

| D8          |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |  |  |

| D9          |              |                          |                      | DDM         |          |            |  |  |  |  |

| D10         |              |                          |                      | DDM         |          |            |  |  |  |  |

| D11         |              |                          |                      | DDIO        |          |            |  |  |  |  |

| D12         |              |                          |                      | ODIO        |          |            |  |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |          |            |  |  |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|--|

| Number |              | Sc                       | oftware Controlle    | ed          | Hardware | Controlled |  |  |  |  |

| rumso. | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |  |

| D13    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |  |

| D14    |              | V <sub>DDIO</sub>        |                      |             |          |            |  |  |  |  |

| D15    |              |                          | $V_{\square}$        | DIO         |          |            |  |  |  |  |

| D16    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |  |

| D17    |              |                          |                      | DDC         |          |            |  |  |  |  |

| D18    |              |                          |                      | IC          |          |            |  |  |  |  |

| D19    |              |                          | N                    | IC          |          |            |  |  |  |  |

| D20    |              |                          | N                    | IC          |          |            |  |  |  |  |

| E1     |              |                          | G                    | ND          |          |            |  |  |  |  |

| E2     |              |                          | D                    | 26          |          |            |  |  |  |  |

| E3     |              |                          | D                    | 31          |          |            |  |  |  |  |

| E4     |              |                          | V <sub>E</sub>       | DDM         |          |            |  |  |  |  |

| E5     |              |                          |                      | DDM         |          |            |  |  |  |  |

| E6     |              |                          |                      | DDC         |          |            |  |  |  |  |

| E7     |              |                          |                      | DDC         |          |            |  |  |  |  |

| E8     |              |                          |                      | DDC         |          |            |  |  |  |  |

| E9     |              |                          |                      | DDC         |          |            |  |  |  |  |

| E10    |              |                          |                      | DDM         |          |            |  |  |  |  |

| E11    |              |                          |                      | DIO         |          |            |  |  |  |  |

| E12    |              |                          |                      | DIO         |          |            |  |  |  |  |

| E13    |              |                          |                      | DIO         |          |            |  |  |  |  |

| E14    |              |                          |                      | DIO         |          |            |  |  |  |  |

| E15    |              |                          |                      | DIO         |          |            |  |  |  |  |

| E16    |              |                          |                      | DDC         |          |            |  |  |  |  |

| E17    |              |                          |                      | DDC         |          |            |  |  |  |  |

| E18    |              |                          |                      | IC          |          |            |  |  |  |  |

| E19    |              |                          |                      | IC          |          |            |  |  |  |  |

| E20    |              |                          |                      | IC          |          |            |  |  |  |  |

| F1     |              |                          |                      | DDM         |          |            |  |  |  |  |

| F2     |              |                          |                      | 15          |          |            |  |  |  |  |

| F3     |              |                          |                      | 29          |          |            |  |  |  |  |

| F4     |              |                          |                      | DDC         |          |            |  |  |  |  |

| F5     |              |                          |                      | DDC         |          |            |  |  |  |  |

| F6     |              |                          |                      | DDC         |          |            |  |  |  |  |

| F7     |              |                          |                      | ND          |          |            |  |  |  |  |

| F8     |              |                          |                      | ND          |          |            |  |  |  |  |

| F9     |              |                          |                      | ND          |          |            |  |  |  |  |

| F10    |              |                          |                      | DDM         |          |            |  |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |          |            |  |  |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|--|

| Number |              | So                       | oftware Controlle    | ed          | Hardware | Controlled |  |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |  |

| F11    |              | $V_{DDM}$                |                      |             |          |            |  |  |  |  |

| F12    |              |                          |                      | ND          |          |            |  |  |  |  |

| F13    |              |                          | G                    | ND          |          |            |  |  |  |  |

| F14    |              |                          | G                    | ND          |          |            |  |  |  |  |

| F15    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |  |

| F16    |              |                          | V                    | DDC         |          |            |  |  |  |  |

| F17    |              |                          | V <sub>[</sub>       | DDC         |          |            |  |  |  |  |

| F18    |              |                          | N                    | IC          |          |            |  |  |  |  |

| F19    |              |                          | N                    | IC          |          |            |  |  |  |  |

| F20    |              |                          | N                    | IC          |          |            |  |  |  |  |

| G1     |              |                          | G                    | ND          |          |            |  |  |  |  |

| G2     |              |                          | D                    | 13          |          |            |  |  |  |  |

| G3     |              | GND                      |                      |             |          |            |  |  |  |  |

| G4     |              |                          | V                    | DDM         |          |            |  |  |  |  |

| G5     |              |                          | V                    | DDM         |          |            |  |  |  |  |

| G6     |              |                          | G                    | ND          |          |            |  |  |  |  |

| G7     |              |                          | G                    | ND          |          |            |  |  |  |  |

| G8     |              |                          | G                    | ND          |          |            |  |  |  |  |

| G9     |              |                          | G                    | ND          |          |            |  |  |  |  |

| G10    |              |                          | G                    | ND          |          |            |  |  |  |  |

| G11    |              |                          | G                    | ND          |          |            |  |  |  |  |

| G12    |              |                          | G                    | ND          |          |            |  |  |  |  |

| G13    |              |                          | G                    | ND          |          |            |  |  |  |  |

| G14    |              |                          | G                    | ND          |          |            |  |  |  |  |

| G15    |              |                          | $V_{\mathbb{D}}$     | DDIO        |          |            |  |  |  |  |

| G16    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |  |

| G17    |              |                          | V                    | DDC         |          |            |  |  |  |  |

| G18    |              |                          |                      | IC          |          |            |  |  |  |  |

| G19    |              | NC                       |                      |             |          |            |  |  |  |  |

| G20    |              |                          | N                    | IC          |          |            |  |  |  |  |

| H1     |              |                          | D                    | 14          |          |            |  |  |  |  |

| H2     |              |                          | D                    | 12          |          |            |  |  |  |  |

| H3     |              |                          | D                    | 11          |          |            |  |  |  |  |

| H4     |              |                          | V <sub>E</sub>       | DDM         |          |            |  |  |  |  |

| H5     |              |                          |                      | DDM         |          |            |  |  |  |  |

| H6     |              |                          | G                    | ND          |          |            |  |  |  |  |

| H7     |              |                          | G                    | ND          |          |            |  |  |  |  |

| H8     |              |                          | G                    | ND          |          |            |  |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|             | Signal Names |                          |                      |             |           |              |  |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|-----------|--------------|--|--|--|

| Number      |              | s                        | oftware Controlle    | ed          | Hardware  | Controlled   |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary   | Alternate    |  |  |  |

| H9          |              | GND                      |                      |             |           |              |  |  |  |

| H10         |              |                          | GI                   | ND          |           |              |  |  |  |

| H11         |              |                          | GI                   | ND          |           |              |  |  |  |

| H12         |              |                          | GI                   | ND          |           |              |  |  |  |

| H13         |              |                          | GI                   | ND          |           |              |  |  |  |

| H14         |              |                          | GI                   | ND          |           |              |  |  |  |

| H15         |              |                          | V <sub>D</sub>       | DIO         |           |              |  |  |  |

| H16         |              |                          | V <sub>D</sub>       | DIO         |           |              |  |  |  |

| H17         |              |                          | V                    | DDC         |           |              |  |  |  |

| H18         |              |                          |                      | IC          |           |              |  |  |  |

| H19         |              | rese                     | Н                    | IA2         |           |              |  |  |  |

| H20         |              | rese                     | Н                    | IA1         |           |              |  |  |  |

| J1          | D10          |                          |                      |             |           |              |  |  |  |

| J2          | $V_{DDM}$    |                          |                      |             |           |              |  |  |  |

| J3          |              |                          | С                    | )9          |           |              |  |  |  |

| J4          |              | $V_{DDM}$                |                      |             |           |              |  |  |  |

| J5          |              |                          | V <sub>C</sub>       | DDM         |           |              |  |  |  |

| J6          |              |                          | V <sub>C</sub>       | DDM         |           |              |  |  |  |

| J7          |              |                          | Gi                   | ND          |           |              |  |  |  |

| J8          |              |                          | Gi                   | ND          |           |              |  |  |  |

| J9          |              |                          | Gl                   | ND          |           |              |  |  |  |

| J10         |              |                          | GI                   | ND          |           |              |  |  |  |

| J11         |              |                          | GI                   | ND          |           |              |  |  |  |

| J12         |              |                          | GI                   | ND          |           |              |  |  |  |

| J13         |              |                          | GI                   | ND          |           |              |  |  |  |

| J14         |              |                          | GI                   | ND          |           |              |  |  |  |

| J15         |              |                          | Gi                   | ND          |           |              |  |  |  |

| J16         |              |                          | V <sub>D</sub>       | DIO         |           |              |  |  |  |

| J17         |              |                          |                      | DDC         |           |              |  |  |  |

| J18 (1L44X) |              | rese                     | rved                 |             | Н         | IA3          |  |  |  |

| J18 (1M88B) |              | GPIC11                   |                      | GPOC11      | H         | IA3          |  |  |  |

| J19         |              | rese                     | rved                 |             | HACK/HACK | or HRRQ/HRRQ |  |  |  |

| J20         | HDSP         |                          | reserved             |             | HREQ/HREQ | or HTRQ/HTRQ |  |  |  |

| K1          |              |                          |                      | 00          |           |              |  |  |  |

| K2          |              |                          | GI                   | ND          |           |              |  |  |  |

| K3          |              |                          |                      | )8          |           |              |  |  |  |

| K4          |              |                          | V                    | DDC         |           |              |  |  |  |

| K5          |              |                          | V                    | DDM         |           |              |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|             | Signal Names |                          |                      |             |          |            |  |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|

| Number      |              | S                        | oftware Controlle    | ed          | Hardware | Controlled |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |

| K6          |              | GND                      |                      |             |          |            |  |  |  |

| K7          |              |                          | Gi                   | ND          |          |            |  |  |  |

| K8          |              |                          | Gi                   | ND          |          |            |  |  |  |

| K9          |              |                          | GI                   | ND          |          |            |  |  |  |

| K10         |              |                          | GI                   | ND          |          |            |  |  |  |

| K11         |              |                          | GI                   | ND          |          |            |  |  |  |

| K12         |              |                          | GI                   | ND          |          |            |  |  |  |

| K13         |              |                          | Gi                   | ND          |          |            |  |  |  |

| K14         |              |                          | Gi                   | ND          |          |            |  |  |  |

| K15         |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |

| K16         |              |                          |                      | DIO         |          |            |  |  |  |

| K17         |              | V <sub>DDC</sub>         |                      |             |          |            |  |  |  |

| K18         | reserved HA0 |                          |                      |             |          |            |  |  |  |

| K19         |              | rese                     | rved                 |             | H        | DDS        |  |  |  |

| K20         |              | rese                     | rved                 |             | HDS/HDS  | or HWR/HWR |  |  |  |

| L1          |              |                          | С                    | )1          |          |            |  |  |  |

| L2          |              |                          | GI                   | ND          |          |            |  |  |  |

| L3          |              |                          | С                    | 03          |          |            |  |  |  |

| L4          |              |                          | V <sub>E</sub>       | DDC         |          |            |  |  |  |

| L5          |              |                          |                      | DDM         |          |            |  |  |  |

| L6          |              |                          |                      | ND          |          |            |  |  |  |

| L7          |              |                          | GI                   | ND          |          |            |  |  |  |

| L8          |              |                          | Gl                   | ND          |          |            |  |  |  |

| L9          |              |                          | Gl                   | ND          |          |            |  |  |  |

| L10         |              |                          | GI                   | ND          |          |            |  |  |  |

| L11         |              |                          | GI                   | ND          |          |            |  |  |  |

| L12         |              |                          | Gl                   | ND          |          |            |  |  |  |

| L13         |              |                          | Gl                   | ND          |          |            |  |  |  |

| L14         |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |

| L15         |              |                          |                      | DIO         |          |            |  |  |  |

| L16         |              |                          |                      | DIO         |          |            |  |  |  |

| L17         |              |                          |                      | DDC         |          |            |  |  |  |

| L18 (1L44X) |              | rese                     | rved                 |             | HCS      | Z/HCS2     |  |  |  |

| L18 (1M88B) |              | GPIB11                   |                      | GPOB11      | HCS      | Z/HCS2     |  |  |  |

| L19         |              | rese                     | rved                 |             | HCS      | 1/HCS1     |  |  |  |

| L20         |              | rese                     | rved                 |             | HRW or   | HRD/HRD    |  |  |  |

| M1          |              |                          |                      | )2          |          |            |  |  |  |

| M2          |              |                          | Vr                   | DDM         |          |            |  |  |  |

MSC7110 Low-Cost 16-bit DSP with DDR Controller Data Sheet, Rev. 11

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names     |                          |                      |             |                     |           |  |  |  |

|--------|------------------|--------------------------|----------------------|-------------|---------------------|-----------|--|--|--|

| Number |                  | Software Controlled      |                      |             | Hardware Controlled |           |  |  |  |

|        | End of Reset     | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |  |  |

| M3     |                  |                          | Г                    | )5          |                     |           |  |  |  |

| M4     |                  |                          | V <sub>C</sub>       | DDM         |                     |           |  |  |  |

| M5     |                  |                          | V                    | DDM         |                     |           |  |  |  |

| M6     |                  |                          | Gi                   | ND          |                     |           |  |  |  |

| M7     |                  |                          | Gi                   | ND          |                     |           |  |  |  |

| M8     |                  |                          | G                    | ND          |                     |           |  |  |  |

| M9     |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| M10    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| M11    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| M12    |                  |                          | Gi                   | ND          |                     |           |  |  |  |

| M13    |                  |                          | Gi                   | ND          |                     |           |  |  |  |

| M14    |                  |                          | GI                   | ND          |                     |           |  |  |  |

| M15    |                  |                          | GI                   | ND          |                     |           |  |  |  |

| M16    |                  | V <sub>DDC</sub>         |                      |             |                     |           |  |  |  |

| M17    | V <sub>DDC</sub> |                          |                      |             |                     |           |  |  |  |

| M18    | GP               | IA14                     | IRQ15                | GPOA14      | S                   | SDA       |  |  |  |

| M19    | GP               | IA12                     | ĪRQ3                 | GPOA12      | U <sup>.</sup>      | TXD       |  |  |  |

| M20    | GP               | IA13                     | ĪRQ2                 | GPOA13      | UI                  | RXD       |  |  |  |

| N1     |                  | •                        | С                    | )4          |                     |           |  |  |  |

| N2     |                  |                          | С                    | 06          |                     |           |  |  |  |

| N3     |                  |                          | V <sub>F</sub>       | REF         |                     |           |  |  |  |

| N4     |                  |                          |                      | DDM         |                     |           |  |  |  |

| N5     |                  |                          |                      | DDM         |                     |           |  |  |  |

| N6     |                  |                          |                      | DDM         |                     |           |  |  |  |

| N7     |                  |                          |                      | ND          |                     |           |  |  |  |

| N8     |                  |                          | Gi                   | ND          |                     |           |  |  |  |

| N9     |                  |                          |                      | ND          |                     |           |  |  |  |

| N10    |                  |                          |                      | ND          |                     |           |  |  |  |

| N11    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| N12    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| N13    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| N14    |                  |                          | Gl                   | ND          |                     |           |  |  |  |

| N15    |                  |                          | V <sub>D</sub>       | DIO         |                     |           |  |  |  |

| N16    |                  |                          |                      | DDC         |                     |           |  |  |  |

| N17    |                  |                          |                      | DDC         |                     |           |  |  |  |

| N18    |                  |                          |                      | KIN         |                     |           |  |  |  |

| N19    | GP               | IA15                     | IRQ14                | GPOA15      | S                   | SCL       |  |  |  |

| N20    |                  |                          |                      | SPLL        |                     |           |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |                     |           |  |  |  |  |

|--------|--------------|--------------------------|----------------------|-------------|---------------------|-----------|--|--|--|--|

| Number |              | Software Controlled      |                      |             | Hardware Controlled |           |  |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |  |  |  |

| P1     |              |                          | Г                    | )7          |                     |           |  |  |  |  |

| P2     |              |                          | D                    | 17          |                     |           |  |  |  |  |

| P3     |              |                          | D                    | 16          |                     |           |  |  |  |  |

| P4     |              |                          | V                    | DDM         |                     |           |  |  |  |  |

| P5     |              |                          | V <sub>E</sub>       | DDM         |                     |           |  |  |  |  |

| P6     |              |                          | V                    | DDM         |                     |           |  |  |  |  |

| P7     |              |                          |                      | ND          |                     |           |  |  |  |  |

| P8     |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P9     |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P10    |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P11    |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P12    |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P13    |              | GND                      |                      |             |                     |           |  |  |  |  |

| P14    |              |                          | G                    | ND          |                     |           |  |  |  |  |

| P15    |              |                          | V <sub>D</sub>       | DIO         |                     |           |  |  |  |  |

| P16    |              |                          |                      | DIO         |                     |           |  |  |  |  |

| P17    |              |                          |                      | DDC         |                     |           |  |  |  |  |

| P18    |              |                          |                      | ESET        |                     |           |  |  |  |  |

| P19    |              |                          | TP                   | SEL         |                     |           |  |  |  |  |

| P20    |              |                          | V <sub>DI</sub>      | OPLL        |                     |           |  |  |  |  |

| R1     |              |                          |                      | ND          |                     |           |  |  |  |  |

| R2     |              |                          | D                    | 19          |                     |           |  |  |  |  |

| R3     |              |                          | D                    | 18          |                     |           |  |  |  |  |

| R4     |              |                          | V <sub>E</sub>       | DDM         |                     |           |  |  |  |  |

| R5     |              |                          |                      | DDM         |                     |           |  |  |  |  |

| R6     |              |                          |                      | DDM         |                     |           |  |  |  |  |

| R7     |              |                          |                      | ND          |                     |           |  |  |  |  |

| R8     |              |                          | V                    | DDM         |                     |           |  |  |  |  |

| R9     |              |                          |                      | ND          |                     |           |  |  |  |  |

| R10    |              |                          | V                    | DDM         |                     |           |  |  |  |  |

| R11    |              |                          |                      | ND          |                     |           |  |  |  |  |

| R12    |              |                          | G                    | ND          |                     |           |  |  |  |  |

| R13    |              |                          | V <sub>D</sub>       | OID         |                     |           |  |  |  |  |

| R14    |              |                          |                      | ND          |                     |           |  |  |  |  |

| R15    |              |                          | V <sub>D</sub>       | OID         |                     |           |  |  |  |  |

| R16    |              |                          |                      | DIO         |                     |           |  |  |  |  |

| R17    |              |                          |                      | DDC         |                     |           |  |  |  |  |

| R18    |              |                          |                      | 00          |                     |           |  |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |                     |         |           |  |  |  |  |

|--------|--------------|--------------------------|----------------------|---------------------|---------|-----------|--|--|--|--|

| Number |              | Se                       | oftware Controlle    | Hardware Controlled |         |           |  |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled         | Primary | Alternate |  |  |  |  |

| R19    |              | rese                     | rved                 |                     | EE0/D   | DBREQ     |  |  |  |  |

| R20    |              | TEST0                    |                      |                     |         |           |  |  |  |  |

| T1     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| T2     |              |                          | D                    | 20                  |         |           |  |  |  |  |

| Т3     |              |                          | D                    | 22                  |         |           |  |  |  |  |

| T4     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| T5     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| Т6     |              |                          | V                    | DDC                 |         |           |  |  |  |  |

| T7     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| T8     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| Т9     |              |                          | V                    | DDC                 |         |           |  |  |  |  |

| T10    |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| T11    |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| T12    |              |                          |                      | DIO                 |         |           |  |  |  |  |

| T13    |              |                          | V <sub>C</sub>       | DIO                 |         |           |  |  |  |  |

| T14    |              |                          |                      | DIO                 |         |           |  |  |  |  |

| T15    |              |                          |                      | OID                 |         |           |  |  |  |  |

| T16    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| T17    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| T18    |              |                          |                      | IC                  |         |           |  |  |  |  |

| T19    |              |                          | TI                   | MS                  |         |           |  |  |  |  |

| T20    |              |                          | HRE                  | SET                 |         |           |  |  |  |  |

| U1     |              |                          | G                    | ND                  |         |           |  |  |  |  |

| U2     |              |                          | D                    | 21                  |         |           |  |  |  |  |

| U3     |              |                          | D                    | 23                  |         |           |  |  |  |  |

| U4     |              |                          | V                    | DDM                 |         |           |  |  |  |  |

| U5     |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U6     |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U7     |              |                          | V <sub>[</sub>       | DDC                 |         |           |  |  |  |  |

| U8     |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U9     |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U10    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U11    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U12    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U13    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U14    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U15    |              |                          |                      | DDC                 |         |           |  |  |  |  |

| U16    |              |                          |                      | DDC                 |         |           |  |  |  |  |

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |                 |                   |                     |  |  |  |

|--------|--------------|--------------------------|----------------------|-----------------|-------------------|---------------------|--|--|--|

| Number |              | Software Controlled      |                      |                 |                   | Hardware Controlled |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled     | Primary           | Alternate           |  |  |  |

| U17    |              | $V_{	extsf{DDC}}$        |                      |                 |                   |                     |  |  |  |

| U18    |              |                          | N                    | IC              |                   |                     |  |  |  |

| U19    |              |                          | TO                   | CK              |                   |                     |  |  |  |

| U20    |              |                          | TR                   | IST             |                   |                     |  |  |  |

| V1     |              |                          | $V_{D}$              | DDM             |                   |                     |  |  |  |

| V2     |              |                          | N                    | IC              |                   |                     |  |  |  |

| V3     |              |                          | A                    | 13              |                   |                     |  |  |  |

| V4     |              |                          | A                    | 11              |                   |                     |  |  |  |

| V5     |              |                          | A                    | 10              |                   |                     |  |  |  |

| V6     |              |                          | А                    | 15              |                   |                     |  |  |  |

| V7     |              |                          | Д                    | A2              |                   |                     |  |  |  |

| V8     |              |                          | Вл                   | <b>A</b> 0      |                   |                     |  |  |  |

| V9     |              |                          | N                    | IC              |                   |                     |  |  |  |

| V10    |              | reser                    | ved                  | EVI             | NT0               |                     |  |  |  |

| V11    | SWTE         | GPIA16                   | ĪRQ12                | GPOA16          | EVI               | NT4                 |  |  |  |

| V12    | GP           | IA8                      | ĪRQ6                 | GPOA8           | TOT               | ГСК                 |  |  |  |

| V13    | GP           | IA4                      | ĪRQ1                 | GPOA4           | reserved          |                     |  |  |  |

| V14    | GP           | IA0                      | IRQ11                | GPOA0           | reserved          |                     |  |  |  |

| V15    | GPI          | A28                      | ĪRQ17                | GPOA28          | reserved reserved |                     |  |  |  |

| V16    |              | GPID6                    |                      | GPOD6           | reserved reserved |                     |  |  |  |

| V17    | GPI          | A22                      | ĪRQ22                | GPOA22 reserved |                   | rved                |  |  |  |

| V18    | GPI          | A24                      | IRQ24                | GPOA24          | rese              | erved               |  |  |  |

| V19    |              | <u>'</u>                 | N                    | IC              |                   |                     |  |  |  |

| V20    |              |                          | Т                    | DI              |                   |                     |  |  |  |

| W1     |              |                          | Gľ                   | ND              |                   |                     |  |  |  |

| W2     |              |                          | V <sub>D</sub>       | DDM             |                   |                     |  |  |  |

| W3     |              |                          |                      | 12              |                   |                     |  |  |  |

| W4     |              |                          |                      | 18              |                   |                     |  |  |  |

| W5     |              |                          |                      | .7              |                   |                     |  |  |  |

| W6     |              |                          |                      | 16              |                   |                     |  |  |  |

| W7     |              |                          | A                    | <b>13</b>       |                   |                     |  |  |  |

| W8     |              |                          |                      | IC              |                   |                     |  |  |  |

| W9     | GPI          | A17                      | ĪRQ13                | GPOA17          | EVNT1             | CLKO                |  |  |  |

| W10    | ВМ0          | GPI                      |                      | GPOC14          |                   | NT2                 |  |  |  |

| W11    |              | A10                      | ĪRQ5                 | GPOA10          |                   | RFS                 |  |  |  |

| W12    |              | IA7                      | ĪRQ7                 | GPOA7           | TO <sup>1</sup>   | ΓFS                 |  |  |  |

| W13    |              | IA3                      | ĪRQ8                 | GPOA3           |                   | erved               |  |  |  |

| W14    |              | IA1                      | IRQ10                | GPOA1           | rese              |                     |  |  |  |

MSC7110 Low-Cost 16-bit DSP with DDR Controller Data Sheet, Rev. 11

Table 1. MSC7110 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |          |           |  |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|-----------|--|--|--|

| Number |              | Hardware Controlled      |                      |             |          |           |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate |  |  |  |

| W15    |              | GPID4                    |                      | GPOD4       | reserved | reserved  |  |  |  |

| W16    | GPI          | A27                      | ĪRQ18                | GPOA27      | reserved | reserved  |  |  |  |

| W17    | GPI          | A19                      | ĪRQ19                | GPOA19      | rese     | rved      |  |  |  |

| W18    | GPI          | A23                      | ĪRQ23                | GPOA23      | rese     | rved      |  |  |  |

| W19    | GPI          | A26                      | ĪRQ26                | GPOA26      | rese     | rved      |  |  |  |

| W20    | H8BIT        |                          |                      | reserved    |          |           |  |  |  |

| Y1     |              |                          | V <sub>I</sub>       | DDM         |          |           |  |  |  |

| Y2     |              |                          | G                    | ND          |          |           |  |  |  |

| Y3     |              |                          | ,                    | <b>A</b> 9  |          |           |  |  |  |

| Y4     |              |                          | ,                    | <b>A</b> 1  |          |           |  |  |  |

| Y5     |              |                          | ,                    | <b>A</b> 0  |          |           |  |  |  |

| Y6     |              |                          | ,                    | <b>A</b> 4  |          |           |  |  |  |

| Y7     |              |                          | В                    | A1          |          |           |  |  |  |

| Y8     | rese         | erved                    | NMI                  |             | reserved |           |  |  |  |

| Y9     | BM1          | GPI                      | C15                  | GPOC15      | EVNT3    |           |  |  |  |

| Y10    | GPI          | A11                      | ĪRQ4                 | GPOA11      | TOF      | RCK       |  |  |  |

| Y11    |              | GPIA9                    |                      | GPOA9       | T0       | RD        |  |  |  |

| Y12    |              | GPIA6                    |                      | GPOA6       | Т0       | TD        |  |  |  |

| Y13    | GP           | IA5                      | ĪRQ0                 | GPOA5       | rese     | rved      |  |  |  |

| Y14    | GP           | IA2                      | ĪRQ9                 | GPOA2       | rese     | rved      |  |  |  |

| Y15    | GPI          | GPIA29                   |                      | GPOA29      | reserved | reserved  |  |  |  |

| Y16    |              | GPID5                    |                      | GPOD5       | reserved | reserved  |  |  |  |

| Y17    | GPI          | A20                      | ĪRQ20                | GPOA20      | reserved |           |  |  |  |

| Y18    | GPI          | A21                      | IRQ21                | GPOA21      | reserved |           |  |  |  |

| Y19    |              |                          | G                    | ND          |          |           |  |  |  |

| Y20    | GPI          | A25                      | IRQ25                | GPOA25      | rese     | rved      |  |  |  |

# 2 Specifications

This chapter covers power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the *MSC711x Reference Manual*.

**Note:** The MSC7110 electrical specifications are preliminary and many are from design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after thorough characterization and device qualifications have been completed.

## 2.1 Maximum Ratings

#### **CAUTION**

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

**Table 2** describes the maximum electrical ratings for the MSC7110.

**Table 2. Absolute Maximum Ratings**

| Rating                        | Symbol             | Value              | Unit |

|-------------------------------|--------------------|--------------------|------|

| Core supply voltage           | V <sub>DDC</sub>   | 1.5                | V    |

| Memory supply voltage         | $V_{DDM}$          | 4.0                | V    |

| PLL supply voltage            | V <sub>DDPLL</sub> | 1.5                | V    |

| I/O supply voltage            | V <sub>DDIO</sub>  | -0.2 to 4.0        | V    |

| Input voltage                 | V <sub>IN</sub>    | (GND – 0.2) to 4.0 | V    |

| Reference voltage             | V <sub>REF</sub>   | 4.0                | V    |

| Maximum operating temperature | TJ                 | 105                | °C   |

| Minimum operating temperature | T <sub>A</sub>     | -40                | °C   |

| Storage temperature range     | T <sub>STG</sub>   | -55 to +150        | °C   |

Notes: 1. Functional operating conditions are given in Table 3.

- 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

- 3. Section 3.1, Thermal Design Considerations includes a formula for computing the chip junction temperature (T<sub>J</sub>).

## 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

**Table 3. Recommended Operating Conditions**

| Rating                      | Symbol                           | Value                        | Unit                                   |

|-----------------------------|----------------------------------|------------------------------|----------------------------------------|

| Core supply voltage         | V <sub>DDC</sub>                 | 1.14 to 1.26                 | V                                      |

| Memory supply voltage       | V <sub>DDM</sub>                 | 2.38 to 2.63                 | V                                      |

| PLL supply voltage          | V <sub>DDPLL</sub>               | 1.14 to 1.26                 | V                                      |

| I/O supply voltage          | V <sub>DDIO</sub>                | 3.14 to 3.47                 | V                                      |

| Reference voltage           | V <sub>REF</sub>                 | 1.19 to 1.31                 | V                                      |

| Operating temperature range | T <sub>J</sub><br>T <sub>A</sub> | maximum: 105<br>minimum: –40 | °°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°° |

#### 2.3 Thermal Characteristics

Table 4 describes thermal characteristics of the MSC7110 for the MAP-BGA package.

Table 4. Thermal Characteristics for MAP-BGA Package

|                                                       |                | MAP-BGA 1             |                               |      |

|-------------------------------------------------------|----------------|-----------------------|-------------------------------|------|

| Characteristic                                        | Symbol         | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow | Unit |

| Junction-to-ambient <sup>1, 2</sup>                   | $R_{	hetaJA}$  | 39                    | 31                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup> | $R_{	hetaJA}$  | 23                    | 20                            | °C/W |