Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

MSC8101 Rev. 19, 5/2008

# **MSC8101**

#### Network Digital Signal Processor

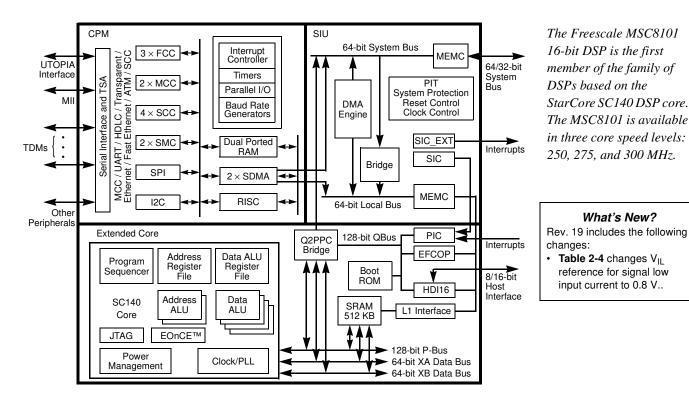

Figure 1. MSC8101 Block Diagram

The Freescale MSC8101 DSP is a very versatile device that integrates the high-performance SC140 four-ALU (arithmetic logic unit) DSP core along with 512 KB of internal memory, a communications processor module (CPM), a 64-bit bus, a very flexible System Integration Unit (SIU), and a 16-channel DMA engine on a single device. With its four-ALU core, the MSC8101 can execute up to four multiply-accumulate (MAC) operations in a single clock cycle. The MSC8101 CPM is a 32-bit RISC-based communications protocol engine that can network to time-division multiplexed (TDM) highways, Ethernet, and asynchronous transfer mode (ATM) backbones. The MSC8101 60x-compatible bus interface facilitates its connection to multi-master system architectures. The very large internal memory, 512 KB, reduces the need for external program and data memories. The MSC8101 offers 1500 DSP MMACS (1200 core and 300 EFCOP) performance using an internal 300 MHz clock with a 1.6 V core and independent 3.3 V input/output (I/O).

## **Table of Contents**

|              |                                        | 3101 Features                                 |             |  |  |  |  |

|--------------|----------------------------------------|-----------------------------------------------|-------------|--|--|--|--|

|              | υ                                      | t Applications                                |             |  |  |  |  |

| Chapter 1    | Sian                                   | Signals/Connections                           |             |  |  |  |  |

| •            | 1.1                                    | Power Signals                                 |             |  |  |  |  |

|              | 1.2                                    | Clock Signals                                 |             |  |  |  |  |

|              | 1.3                                    | Reset, Configuration, and EOnCE Event Signals |             |  |  |  |  |

|              | 1.4                                    | System Bus, HDI16, and Interrupt Signals      | 1-6         |  |  |  |  |

|              | 1.5                                    | Memory Controller Signals                     | 1-13        |  |  |  |  |

|              | 1.6                                    | CPM Ports                                     | 1-15        |  |  |  |  |

|              | 1.7                                    | JTAG Test Access Port Signals                 | 1-36        |  |  |  |  |

|              | 1.8                                    | Reserved Signals                              | 1-36        |  |  |  |  |

| Chapter 2    | Physical and Electrical Specifications |                                               |             |  |  |  |  |

| •            | 2.1                                    | Absolute Maximum Ratings                      | 2-1         |  |  |  |  |

|              | 2.2                                    | Recommended Operating Conditions              | 2-2         |  |  |  |  |

|              | 2.3                                    | Thermal Characteristics                       | 2-2         |  |  |  |  |

|              | 2.4                                    | DC Electrical Characteristics                 | 2-3         |  |  |  |  |

|              | 2.5                                    | Clock Configuration                           | 2-4         |  |  |  |  |

|              | 2.6                                    | AC Timings                                    | 2-7         |  |  |  |  |

| Chapter 3    | Pack                                   | aging                                         |             |  |  |  |  |

| •            | 3.1                                    | FC-PBGA Package Description                   |             |  |  |  |  |

|              | 3.2                                    | Lidded FC-PBGA Package Mechanical Drawing     |             |  |  |  |  |

| Chapter 4    | Design Considerations                  |                                               |             |  |  |  |  |

| •            | 4.1                                    | Thermal Design Considerations                 | 4-1         |  |  |  |  |

|              | 4.2                                    | Electrical Design Considerations              | 4-1         |  |  |  |  |

|              | 4.3                                    | Power Considerations                          |             |  |  |  |  |

|              | 4.4                                    | Layout Practices                              | 4-3         |  |  |  |  |

| Ondoning and | Contoot I                              | Information                                   | Pagir Cover |  |  |  |  |

### **Data Sheet Conventions**

| pin and pin-<br>out | Although the device package does not have pins, the term pins and pin-out are used for convenience and indicate specific signal locations within the ball-grid array. |                            |                              |                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|-----------------------|

| OVERBAR             | Used to indicate a signal that is active when pulled low (For example, the RESET pin is active when low.)                                                             |                            |                              |                       |

| "asserted"          | Means that a high true (a                                                                                                                                             | active high) signal is hig | gh or that a low true (activ | ve low) signal is low |

| "deasserted"        | Means that a high true (a                                                                                                                                             | active high) signal is lo  | w or that a low true (active | e low) signal is high |

| Examples:           | Signal/Symbol Logic State Signal State Voltage                                                                                                                        |                            |                              |                       |

|                     | PIN                                                                                                                                                                   | True                       | Asserted                     | $V_{IL}/V_{OL}$       |

|                     | PIN                                                                                                                                                                   | False                      | Deasserted                   | $V_{IH}/V_{OH}$       |

|                     | PIN                                                                                                                                                                   | True                       | Asserted                     | $V_{IH}/V_{OH}$       |

|                     | PIN                                                                                                                                                                   | False                      | Deasserted                   | $V_{IL}/V_{OL}$       |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

#### **MSC8101 Features**

- SC140 core

- Architecture optimized for efficient C/C++ code compilation

- Four 16-bit ALUs and two 32-bit AGUs

- 1200 DSP MMACS running at 300 MHz

- Very low power dissipation

- Variable-length execution set (VLES) execution model

- JTAG/Enhanced OnCE debug port

- Communications processor module (CPM)

- Programmable protocol machine using a 32-bit RISC engine

- 155 Mbps ATM interface (including AAL 0/1/2/5)

- 10/100 Mbit Ethernet interface

- Up to four E1/T1 interfaces or one E3/T3 interface and one E1/T1 interface

- HDLC support up to T3 rates, or 256 channels

- 64- or 32-bit wide bus interface

- Support for bursts for high efficiency

- Glueless interface to 60x-compatible bus systems

- Multi-master support

- Enhanced filter coprocessor (EFCOP)

- Independently and concurrently executes long filters (such as echo cancellation)

- Runs at 250/275/300 MHz and provides 250/275/300 MMACS performance

- Programmable memory controller

- Control for up to eight banks of external memory

- User-programmable machines (UPM) allowing glueless interface to various memory types (SRAM, DRAM, EPROM, and Flash memory) and other user-definable peripherals

- Dedicated pipelined SDRAM memory interface

- Large internal SRAM

- 256K 16-bit words (512 KB)

- Unified program and data space configurable by the application

- Word and byte addressable

- DMA controller

- 16 DMA channels, FIFO based, with burst capabilities

- Sophisticated addressing capabilities

- Small foot print package

- 17 mm × 17 mm lidded FC-PBGA lead-bearing or lead-free package

- Very low power consumption

- Separate power supply for internal logic (1.6 V) and for I/O (3.3 V)

- Enhanced 16-bit parallel host interface (HDI16)

- Supports a variety of microcontroller, microprocessor, and DSP bus interfaces

- Phase-lock loops (PLLs)

- System PLL

- CPM DPLLs (SCC and SCM)

- Process technology

- 0.13 micron copper interconnect process technology

## **Target Applications**

The MSC8101 targets applications requiring very high performance, very large amounts of internal memory, and such networking capabilities as:

- Third-generation wideband wireless infrastructure systems

- Packet Telephony systems

- Multi-channel modem banks

- Multi-channel xDSL

### **Product Documentation**

The documents listed in **Table 1** are required for a complete description of the MSC8101 and are necessary to design properly with the part. Documentation is available from the following sources (see back cover for details):

- A local Freescale distributor

- A Freescale Semiconductor sales office

- A Freescale Semiconductor Literature Distribution Center

- The world wide web (WWW)

Table 1. MSC8101 Documentation

| Name                            | Description                                                                                              | Order Number                    |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------|--|

| MSC8101<br>Technical Data       | MSC8101 features list and physical, electrical, timing, and package specifications                       | MSC8101/D                       |  |

| MSC8101 User's Guide            | Detailed functional description of the MSC8101 memory configuration, operation, and register programming | MSC8101UG/D                     |  |

| MSC8101 Pocket Guide            | Quick reference information for application development.                                                 | MSC8101PG/D                     |  |

| MSC8101 Reference Manual        | Detailed description of the MSC8101 processor core and instruction set                                   | MSC8101RM/D                     |  |

| SC140 DSP Core Reference Manual | Detailed description of the SC140 family processor core and instruction set                              | MNSC140CORE/D                   |  |

| Application Notes               | Documents describing specific applications or optimized device operation including code examples         | See the MSC8101 product website |  |

# Signals/Connections

1

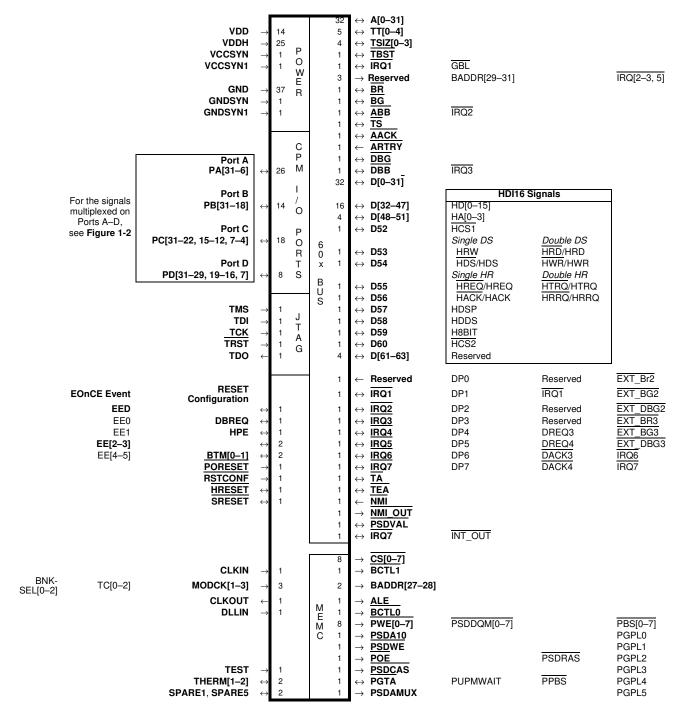

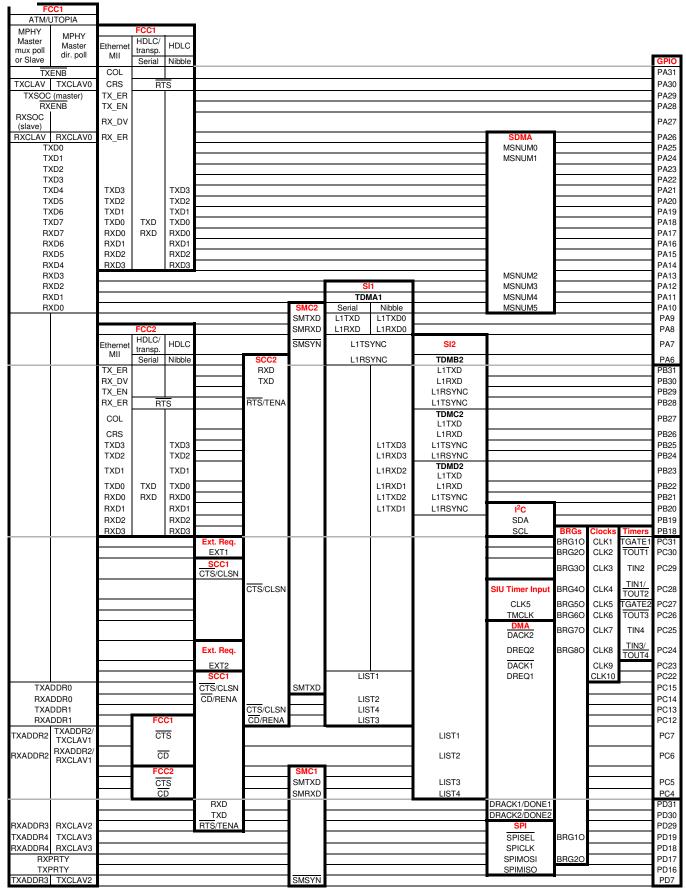

The MSC8101 external signals are organized into functional groups, as shown in **Table 1-1**, **Figure 1-1**, and **Figure 1-2**. **Table 1-1** lists the functional groups, states the number of signal connections in each group, and references the table that gives details on multiplexed signals within each group. **Figure 1-1** shows MSC8101 external signals organized by function. **Figure 1-2** indicates how the parallel input/output (I/O) ports signals are multiplexed. Because the parallel I/O design supported by the MSC8101 communications processor module (CPM) is a subset of the parallel I/O signals supported by the MPC8260 device, port pins are not numbered sequentially.

Table 1-1. MSC8101 Functional Signal Groupings

| Functional Group                                        | Number of Signal<br>Connections | Detailed Description           |                                |

|---------------------------------------------------------|---------------------------------|--------------------------------|--------------------------------|

| Power (V <sub>CC</sub> , V <sub>DD</sub> , and GND)     |                                 | 80                             | <b>Table 1-2</b> on page 1-4   |

| Clock                                                   |                                 | 6                              | <b>Table 1-3</b> on page 1-4   |

| Reset, configuration, and EOnCE                         |                                 | 11                             | <b>Table 1-4</b> on page 1-5   |

| System bus, HDI16, and interrupts                       |                                 | 133                            | <b>Table 1-5</b> on page 1-7   |

| Memory Controller                                       | 27                              | <b>Table 1-6</b> on page 1-13  |                                |

| CPM Input/Output Parallel Ports                         | Port A                          | 26                             | <b>Table 1-7</b> on page 1-16  |

|                                                         | Port B                          | 14                             | <b>Table 1-8</b> on page 1-21  |

|                                                         | Port C                          | 18                             | <b>Table 1-9</b> on page 1-24  |

|                                                         | Port D                          | 8                              | <b>Table 1-10</b> on page 1-33 |

| JTAG Test Access Port                                   | 5                               | <b>Table 1-11</b> on page 1-36 |                                |

| Reserved (denotes connections that are always reserved) |                                 | 5                              | <b>Table 1-12</b> on page 1-36 |

Note: Refer to the System Interface Unit (SIU) chapter in the MSC8101 Reference Manual for details on how to configure these pins.

Figure 1-1. MSC8101 External Signals

1-2 Freescale Semiconductor

Figure 1-2. CPM Port A-D Pin Multiplexed Functionality

# 1.1 Power Signals

Table 1-2. Power and Ground Signal Inputs

| Power Name          | Description                                                                                                                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>     | Internal Logic Power  V <sub>DD</sub> dedicated for use with the device core. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>DD</sub> power rail.                                     |

| $V_{DDH}$           | Input/Output Power This source supplies power for the I/O buffers. The user must provide adequate external decoupling capacitors.                                                                                                                               |

| V <sub>CCSYN</sub>  | System PLL Power  V <sub>CC</sub> dedicated for use with the system Phase Lock Loop (PLL). The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>CC</sub> power rail.                        |

| V <sub>CCSYN1</sub> | SC140 PLL Power  V <sub>CC</sub> dedicated for use with the SC140 core PLL. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the V <sub>CC</sub> power rail.                                       |

| GND                 | System Ground  An isolated ground for the internal processing logic. This connection must be tied externally to all chip ground connections, except GND <sub>SYN</sub> and GND <sub>SYN1</sub> . The user must provide adequate external decoupling capacitors. |

| GND <sub>SYN</sub>  | System PLL Ground Ground dedicated for system PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                        |

| GND <sub>SYN1</sub> | SC140 PLL Ground 1 Ground dedicated for SC140 core PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                   |

# 1.2 Clock Signals

Table 1-3.Clock Signals

| Signal Name | Туре   | Signal Description                                                                                               |

|-------------|--------|------------------------------------------------------------------------------------------------------------------|

| CLKIN       | Input  | Clock In Primary clock input to the MSC8101 PLL.                                                                 |

| MODCK1      | Input  | Clock Mode Input 1 Defines the operating mode of internal clock circuits.                                        |

| TC0         | Output | Transfer Code 0 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL0     | Output | Bank Select 0 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

| MODCK2      | Input  | Clock Mode Input 2 Defines the operating mode of internal clock circuits.                                        |

| TC1         | Output | Transfer Code 1 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL1     | Output | Bank Select 1 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

| MODCK3      | Input  | Clock Mode Input 3 Defines the operating mode of internal clock circuits.                                        |

| TC2         | Output | Transfer Code 2 Supplies information that can be useful for debugging bus transactions initiated by the MSC8101. |

| BNKSEL2     | Output | Bank Select 2 Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.                             |

1-4 Freescale Semiconductor

Table 1-3. Clock Signals (Continued)

| Signal Name | Туре   | Signal Description                                                                                      |

|-------------|--------|---------------------------------------------------------------------------------------------------------|

| CLKOUT      | Output | Clock Out The system bus clock.                                                                         |

| DLLIN       | Input  | DLLIN Synchronizes with an external device. Note: When the DLL is disabled, connect this signal to GND. |

## 1.3 Reset, Configuration, and EOnCE Event Signals

Table 1-4. Reset, Configuration, and EOnCE Event Signals

| Signal Name      | Туре   | Signal Description                                                                                                                                                                                                 |

|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBREQ            | Input  | Debug Request Determines whether to go into SC140 Debug mode when PORESET is deasserted.                                                                                                                           |

| EE0 <sup>1</sup> |        | Enhanced OnCE (EOnCE) Event 0 After PORESET is deasserted, you can configure EE0 as an input (default) or an output.                                                                                               |

|                  | Input  | Debug request, enable Address Event Detection Channel 0, or generate an EOnCE event.                                                                                                                               |

|                  | Output | Detection by Address Event Detection Channel 0. Used to trigger external debugging equipment.                                                                                                                      |

| HPE              | Input  | Host Port Enable When this pin is asserted during PORESET, the Host port is enabled, the system data bus is 32 bits wide, and the Host <i>must</i> program the reset configuration word.                           |

| EE1 <sup>1</sup> |        | EOnCE Event 1 After PORESET is deasserted, you can configure EE1 as an input (default) or an output.                                                                                                               |

|                  | Input  | Enable Address Event Detection Channel 1 or generate an EOnCE event.                                                                                                                                               |

|                  | Output | Debug Acknowledge or detection by Address Event Detection Channel 1. Used to trigger external debugging equipment.                                                                                                 |

| EE2 <sup>1</sup> |        | EOnCE Event 2 After PORESET is deasserted, you can configure EE2 as an input (default) or an output.                                                                                                               |

|                  | Input  | Enable Address Event Detection Channel 2 or generate an EOnCE event or enable the Event Counter.                                                                                                                   |

|                  | Output | Detection by Address Event Detection Channel 2. Used to trigger external debugging equipment.                                                                                                                      |

| EE3 <sup>1</sup> |        | EOnCE Event 3  After PORESET is deasserted, you can configure EE3 as an input (default) or an output. See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on the ERCV Register. |

|                  | Input  | Enable Address Event Detection Channel 3 or generate one of the EOnCE events.                                                                                                                                      |

|                  | Output | The DSP has read the EOnCE Receive Register (ERCV). Triggers external debugging equipment.                                                                                                                         |

Reset, Configuration, and EOnCE Event Signals (Continued) **Table 1-4.**

| Signal Name                                                                                                                  | Туре   | Signal Description                                                                                                                                                                                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BTM[0-1]                                                                                                                     | Input  | Boot Mode 0–1  Determines the MSC8101 boot mode when PORESET is deasserted. See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on how to set these pins.                                           |  |

| EE4 <sup>1</sup>                                                                                                             |        | <b>EOnCE Event 4</b> After PORESET is deasserted, you can configure EE4 as an input (default) or an output. See the emulation and debug chapter in the <i>SC140 DSP Core Reference Manual</i> for details on the ETRSMT Register.      |  |

|                                                                                                                              | Input  | Enable Address Event Detection Channel 4 or generate an EOnCE event.                                                                                                                                                                   |  |

|                                                                                                                              | Output | The DSP wrote the EOnCE Transmit Register (ETRSMT). Triggers external debugging equipment.                                                                                                                                             |  |

| EE5 <sup>1</sup>                                                                                                             |        | EOnCE Event 5 After PORESET is deasserted, you can configure EE5 as an input (default) or an output.                                                                                                                                   |  |

|                                                                                                                              | Input  | Enable Address Event Detection Channel 5.                                                                                                                                                                                              |  |

|                                                                                                                              | Output | Detection by Address Event Detection Channel 5. Triggers external debugging equipment.                                                                                                                                                 |  |

| EED <sup>1</sup>                                                                                                             |        | Enhanced OnCE (EOnCE) Event Detection After PORESET is deasserted, you can configure EED as an input (default) or output:                                                                                                              |  |

|                                                                                                                              | Input  | Enable the Data Event Detection Channel.                                                                                                                                                                                               |  |

|                                                                                                                              | Output | Detection by the Data Event Detection Channel. Triggers external debugging equipment.                                                                                                                                                  |  |

| PORESET                                                                                                                      | Input  | Power-On Reset When asserted, this line causes the MSC8101 to enter power-on reset state.                                                                                                                                              |  |

| RSTCONF                                                                                                                      | Input  | Reset Configuration Used during reset configuration sequence of the chip. A detailed explanation of its function is provided in the "Power-On Reset Flow" and "Hardware Reset Configuration" sections of the MSC8101 Reference Manual. |  |

| HRESET                                                                                                                       | Input  | Hard Reset When asserted, this open-drain line causes the MSC8101 to enter the hard reset state.                                                                                                                                       |  |

| SRESET                                                                                                                       | Input  | Soft Reset When asserted, this open-drain line causes the MSC8101 to enter the soft reset state.                                                                                                                                       |  |

| Note: See the emulation and debug chapter in the SC140 DSP Core Reference Manual for details on how to configure these pins. |        |                                                                                                                                                                                                                                        |  |

### 1.4 System Bus, HDI16, and Interrupt Signals

The system bus, HDI16, and interrupt signals are grouped together because they use a common set of signal lines. Individual assignment of a signal to a specific signal line is configured through registers in the System Interface Unit (SIU) and the Host Interface (HDI16). 1-5 describes the signals in this group.

To boot from the host interface, the HDI16 must be enabled by pulling up the HPE signal line during PORESET. The configuration word must then be loaded from the host. The configuration word must set the Internal Space Port Size bit in the Bus Control Register (BCR[ISPS]) to change the system data bus width from 64 bits to 32 bits and reassign the upper 32 bits to their HDI16 functions. Never set the Host Port Enable (HEN) bit in the Host Port Control Register (HPCR) to enable the HDI16, unless the bus size is first changed from 64 bits to 32 bits. Otherwise, unpredictable operation may occur.

Although there are eight interrupt request  $(\overline{IRQ})$  connections to the core processor, there are multiple external lines that can connect to these internal signal lines. After reset, the default configuration includes two  $\overline{IRQ1}$  and two  $\overline{IRQ7}$  input lines. The designer must select one line for each required interrupt and reconfigure the other external signal line or lines for alternate functions.

Table 1-5. System Bus, HDI16, and Interrupt Signals

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0-31]   | Input/Output | Address Bus  When the MSC8101 is in external master bus mode, these pins function as the address bus. The MSC8101 drives the address of its internal bus masters and responds to addresses generated by external bus masters. When the MSC8101 is in Internal Master Bus mode, these pins are used as address lines connected to memory devices and are controlled by the MSC8101 memory controller |

| TT[0-4]   | Input/Output | Bus Transfer Type The bus master drives these pins during the address tenure to specify the type of transaction.                                                                                                                                                                                                                                                                                    |

| TSIZ[0-3] | Input/Output | Transfer Size  The bus master drives these pins with a value indicating the number of bytes transferred in the current transaction.                                                                                                                                                                                                                                                                 |

| TBST      | Input/Output | Bus Transfer Burst The bus master asserts this pin to indicate that the current transaction is a burst transaction (transfers four quad words).                                                                                                                                                                                                                                                     |

| IRQ1      | Input        | Interrupt Request 1 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| GBL       | Input/Output | Global <sup>1</sup> When a master within the chip initiates a bus transaction, it drives this pin. When an external master initiates a bus transaction, it should drive this pin. Assertion of this pin indicates that the transfer is global and it should be snooped by caches in the system.                                                                                                     |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR29   | Output       | Burst Address 29 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ2      | Input        | Interrupt Request 2 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR30   | Output       | Burst Address 30 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ3      | Input        | Interrupt Request 3 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                              |

| BADDR31   | Output       | Burst Address 31 <sup>1</sup> One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8101 memory controller.                                                                                                                                                                                                                              |

| ĪRQ5      | Input        | Interrupt Request 5 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                        |

#### MSC8101 Technical Data, Rev. 19

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal  | Data Flow              | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR      | Input/Output<br>Output | Bus Request <sup>2</sup> An output when an external arbiter is used. The MSC8101 asserts this pin to request ownership of the bus.                                                                                                                                                                                                                                                                                 |

|         | Input                  | An input when an internal arbiter is used. An external master should assert this pin to request bus ownership from the internal arbiter.                                                                                                                                                                                                                                                                           |

| BG      | Input/Output<br>Output | Bus Grant <sup>2</sup> An output when an internal arbiter is used. The MSC8101 asserts this pin to grant bus ownership to an external bus master.                                                                                                                                                                                                                                                                  |

|         | Input                  | An input when an external arbiter is used. The external arbiter should assert this pin to grant bus ownership to the MSC8101.                                                                                                                                                                                                                                                                                      |

| ABB     | Input/Output<br>Output | Address Bus Busy <sup>1</sup> The MSC8101 asserts this pin for the duration of the address bus tenure. Following an address acknowledge (AACK) signal, which terminates the address bus tenure, the MSC8101 deasserts ABB for a fraction of a bus cycle and then stops driving this pin.                                                                                                                           |

|         | Input                  | The MSC8101 does not assume bus ownership while it this pin is asserted by an external bus master.                                                                                                                                                                                                                                                                                                                 |

| ĪRQ2    | Input                  | Interrupt Request 2 <sup>1</sup> One of the eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                   |

| TS      | Input/Output           | Bus Transfer Start Signals the beginning of a new address bus tenure. The MSC8101 asserts this signal when one of its internal bus masters (SC140 core or DMA controller) begins an address tenure. When the MSC8101 senses this pin being asserted by an external bus master, it responds to the address bus tenure as required (snoop if enabled, access internal MSC8101 resources, memory controller support). |

| AACK    | Input/Output           | Address Acknowledge A bus slave asserts this signal to indicate that it identified the address tenure. Assertion of this signal terminates the address tenure.                                                                                                                                                                                                                                                     |

| ARTRY   | Input                  | Address Retry Assertion of this signal indicates that the bus transaction should be retried by the bus master. The MSC8101 asserts this signal to enforce data coherency with its internal cache and to prevent deadlock situations.                                                                                                                                                                               |

| DBG     | Input/Output<br>Output | Data Bus Grant <sup>2</sup> An output when an internal arbiter is used. The MSC8101 asserts this pin as an output to grant data bus ownership to an external bus master.                                                                                                                                                                                                                                           |

|         | Input                  | An input when an external arbiter is used. The external arbiter should assert this pin as an input to grant data bus ownership to the MSC8101.                                                                                                                                                                                                                                                                     |

| DBB     | Input/Output<br>Output | Data Bus Busy <sup>1</sup> The MSC8101 asserts this pin as an output for the duration of the data bus tenure. Following a TA, which terminates the data bus tenure, the MSC8101 deasserts DBB for a fraction of a bus cycle and then stops driving this pin.                                                                                                                                                       |

|         | Input                  | The MSC8101 does not assume data bus ownership while DBB is asserted by an external bus master.                                                                                                                                                                                                                                                                                                                    |

| ĪRQ3    | Input                  | Interrupt Request 3 <sup>1</sup> One of the eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                   |

| D[0-31] | Input/Output           | Data Bus Most Significant Word In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus. In Host Port Disabled mode, these 32 bits are part of the 64-bit data bus. In Host Port Enabled mode, these bits are used as the bus in 32-bit mode.                                                                                      |

#### MSC8101 Technical Data, Rev. 19

1-8 Freescale Semiconductor

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                         |

|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[32–47]  | Input/Output | Data Bus Bits 32–47 In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus.                                                                                                                       |

| HD[0-15]  | Input/Output | Host Data <sup>2</sup> When the HDI16 interface is enabled, these signals are lines 0-15 of the bidirectional tri-state data bus.                                                                                                                                                   |

| D[48–51]  | Input/Output | Data Bus Bits 48–51 In write transactions the bus master drives the valid data on these pins. In read transactions the slave drives the valid data on these pins.                                                                                                                   |

| HA[0-3]   | Input        | Host Address Line 0–3 <sup>3</sup> When the HDI16 interface bus is enabled, these lines address internal host registers.                                                                                                                                                            |

| D52       | Input/Output | Data Bus Bit 52 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |

| HCS1      | Input        | Host Chip Select <sup>3</sup> When the HDI16 interface is enabled, this is one of the two chip-select pins. The HDI16 chip select is a logical OR of HCS1 and HCS2.                                                                                                                 |

| D53       | Input/Output | Data Bus Bit 53 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |

| HRW       | Input        | Host Read Write Select <sup>3</sup> When the HDI16 interface is enabled in Single Strobe mode, this is the read/write input (HRW).                                                                                                                                                  |

| HRD/HRD   | Input        | Host Read Strobe <sup>3</sup> When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the read data strobe Schmitt trigger input (HRD/HRD). The polarity of the data strobe is programmable.                                                      |

| D54       | Input/Output | Data Bus Bit 54 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |

| HDS/HDS   | Input        | Host Data Strobe <sup>3</sup> When the HDI16 is programmed to interface with a single data strobe host bus, this pin is the data strobe Schmitt trigger input (HDS/HDS). The polarity of the data strobe is programmable.                                                           |

| HWR/HWR   | Input        | Host Write Data Strobe <sup>3</sup> When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the write data strobe Schmitt trigger input (HWR/HWR). The polarity of the data strobe is programmable.                                               |

| D55       | Input/Output | Data Bus Bit 55 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                           |

| HREQ/HREQ | Output       | Host Request <sup>3</sup> When the HDI16 is programmed to interface with a single host request host bus, this pin is the host request output (HREQ/HREQ). The polarity of the host request is programmable. The host request may be programmed as a driven or open-drain output.    |

| HTRQ/HTRQ | Output       | Transmit Host Request <sup>3</sup> When the HDI16 is programmed to interface with a double host request host bus, this pin is the transmit host request output (HTRQ/HTRQ). The signal can be programmed as driven or open drain. The polarity of the host request is programmable. |

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                       |  |  |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D56       | Input/Output | Data Bus Bit 56 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |

| HACK/HACK | Output       | Host Acknowledge <sup>3</sup> When the HDI16 is programmed to interface with a single host request host bus, this pin is the host acknowledge Schmitt trigger input (HACK). The polarity of the host acknowledge is programmable.                                                 |  |  |

| HRRQ/HRRQ | Output       | Receive Host Request <sup>3</sup> When the HDI16 is programmed to interface with a double host request host bus, this pin is the receive host request output (HRRQ/HRRQ). The signal can be programmed as driven or open drain. The polarity of the host request is programmable. |  |  |

| D57       | Input/Output | Data Bus Bit 57 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |

| HDSP      | Input        | Host Data Strobe Polarity <sup>3</sup> When the HDI16 interface is enabled, this pin is the host data strobe polarity (HDSP).                                                                                                                                                     |  |  |

| D58       | Input/Output | Data Bus Bit 58 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |

| HDDS      | Input        | Host Dual Data Strobe <sup>3</sup> When the HDI16 interface is enabled, this pin is the host dual data strobe (HDDS).                                                                                                                                                             |  |  |

| D59       | Input/Output | Data Bus Bit 59 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |

| H8BIT     | Input        | H8BIT <sup>3</sup> When the HDI16 interface is enabled, this bit determines if the interface is in 8-bit or 16-bit mode.                                                                                                                                                          |  |  |

| D60       | Input/Output | Data Bus Bit 60 In write transactions the bus master drives the valid data on this pin. In read transactions the slave drives the valid data on this pin.                                                                                                                         |  |  |

| HCS2      | Input        | Host Chip Select <sup>3</sup> When the HDI16 interface is enabled, this is one of the two chip-select pins. The HDI16 chip select is a logical OR of HCS1 and HCS2.                                                                                                               |  |  |

| D[61-63]  | Input/Output | Data Bus Bits 61–63 Used only in 60x-mode-only mode. In write transactions the bus master drives the valid data on this bus. In read transactions the slave drives the valid data on this bus.                                                                                    |  |  |

| Reserved  |              | These dedicated signals are reserved when the HDI16 is enabled. <sup>3</sup>                                                                                                                                                                                                      |  |  |

| Reserved  | Input        | The primary configuration is reserved.                                                                                                                                                                                                                                            |  |  |

| DP0       | Input/Output | Data Parity 0 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity zero pin should give odd parity (odd number of ones) on the group of signals that includes data parity 0 and D[0–7].                       |  |  |

| EXT_BR2   | Input        | External Bus Request 2 <sup>1,2</sup> An external master asserts this pin to request bus ownership from the internal arbiter.                                                                                                                                                     |  |  |

1-10 Freescale Semiconductor

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal   | Data Flow    | Description                                                                                                                                                                                                                                                    |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĪRQ1     | Input        | Interrupt Request 1 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                   |

| DP1      | Input/Output | Data Parity 1 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity one pin should give odd parity (odd number of ones) on the group of signals that includes data parity 1 and D[8–15].    |

| EXT_BG2  | Output       | External Bus Grant 2 <sup>1,2</sup> The MSC8101 asserts this pin to grant bus ownership to an external bus master.                                                                                                                                             |

| ĪRQ2     | Input        | Interrupt Request 2 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                   |

| DP2      | Input/Output | Data Parity 2 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity two pin should give odd parity (odd number of ones) on the group of signals that includes data parity 2 and D[16–23].   |

| EXT_DBG2 | Output       | External Data Bus Grant 2 <sup>1,2</sup> The MSC8101 asserts this pin to grant data bus ownership to an external bus master.                                                                                                                                   |

| ĪRQ3     | Input        | Interrupt Request 3 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                   |

| DP3      | Input/Output | Data Parity 3 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity three pin should give odd parity (odd number of ones) on the group of signals that includes data parity 3 and D[24–31]. |

| EXT_BR3  | Input        | External Bus Request 3 <sup>1,2</sup> An external master asserts this pin to request bus ownership from the internal arbiter.                                                                                                                                  |

| ĪRQ4     | Input        | Interrupt Request 4 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                   |

| DP4      | Input/Output | Data Parity 4 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity four pin should give odd parity (odd number of ones) on the group of signals that includes data parity 4 and D[32–39].  |

| DREQ3    | Input        | DMA Request 3 <sup>1</sup> An external peripheral uses this pin to request DMA service.                                                                                                                                                                        |

| EXT_BG3  | Output       | External Bus Grant 3 <sup>1,2</sup> The MSC8101 asserts this pin to grant bus ownership to an external bus master.                                                                                                                                             |

Table 1-5.

System Bus, HDI16, and Interrupt Signals (Continued)

| Signal   | Data Flow    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ĪRQ5     | Input        | Interrupt Request 5 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| DP5      | Input/Output | Data Parity 5 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity five pin should give odd parity (odd number of ones) on the group of signals that includes data parity 5 and D[40–47].                                                                                                                                                                                                                                                                                                                                                                  |  |

| DREQ4    | Input        | DMA Request 4 <sup>1</sup> An external peripheral uses this pin to request DMA service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| EXT_DBG3 | Output       | External Data Bus Grant 3 <sup>1,2</sup> The MSC8101 asserts this pin to grant data bus ownership to an external bus master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| ĪRQ6     | Input        | Interrupt Request 6 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| DP6      | Input/Output | Data Parity 6 <sup>1</sup> The agent that drives the data bus also drives the data parity signals. The value driven on the data parity six pin should give odd parity (odd number of ones) on the group of signals that includes data parity 6 and D[48–55].                                                                                                                                                                                                                                                                                                                                                                   |  |

| DACK3    | Output       | DMA Acknowledge 3 <sup>1</sup> The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| ĪRQ7     | Input        | Interrupt Request 7 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| DP7      | Input/Output | Data Parity 7 <sup>1</sup> The master or slave that drives the data bus also drives the data parity signals. The value driven on the data parity seven pin should give odd parity (odd number of ones) on the group of signals that includes data parity 7 and D[56–63].                                                                                                                                                                                                                                                                                                                                                       |  |

| DACK4    | Output       | DMA Acknowledge <sup>1</sup> The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| TA       | Input/Output | Transfer Acknowledge Indicates that a data beat is valid on the data bus. For single beat transfers, assertion of TA indicates the termination of the transfer. For burst transfers, TA is asserted four times to indicate the transfer of four data beats with the last assertion indicating the termination of the burst transfer.                                                                                                                                                                                                                                                                                           |  |

| TEA      | Input/Output | Transfer Error Acknowledge Indicates a bus error. masters within the MSC8101 monitor the state of this pin. The MSC8101 internal bus monitor can assert this pin if it identifies a bus transfer that is hung.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| NMI      | Input        | Non-Maskable Interrupt When an external device asserts this line, the MSC8101 NMI input is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| NMI_OUT  | Output       | Non-Maskable Interrupt Driven from the MSC8101 internal interrupt controller. Assertion of this output indicates that a non-maskable interrupt, pending in the MSC8101 internal interrupt controller, is waiting to be handled by an external host.                                                                                                                                                                                                                                                                                                                                                                            |  |

| PSDVAL   | Input/Output | handled by an external host.  Data Valid Indicates that a data beat is valid on the data bus. The difference between the TA pin and PSDVAL is that the TA pin is asserted to indicate data transfer terminations while the PSDVAL signal is asserted with each data beat movement. Thus, when TA is asserted, PSDVAL is asserted, but when PSDVAL is asserted, TA is not necessarily asserted. For example when the SDMA initiates a double word (2x64 bits) transfer to a memory device that has a 32-bit port size, PSDVAL is asserted three times without TA, and finally both pins are asserted to terminate the transfer. |  |

#### MSC8101 Technical Data, Rev. 19

1-12 Freescale Semiconductor

| Table 1-5. | System Bus, | HDI16, and | Interrupt | Signals ( | (Continued) |

|------------|-------------|------------|-----------|-----------|-------------|

|            |             |            |           |           |             |

| Signal                                       | Data Flow                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IRQ7 Input                                   |                                                                                                                                                                            | Interrupt Request 7 <sup>1</sup> One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |