Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: [info@chipsmall.com](mailto:info@chipsmall.com) Web: [www.chipsmall.com](http://www.chipsmall.com)

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MSC8126

## Quad Digital Signal Processor

- Four StarCore™ SC140 DSP extended cores, each with an SC140 DSP core, 224 Kbyte of internal SRAM M1 memory (1436 Kbyte total), 16 way 16 Kbyte instruction cache (ICache), four-entry write buffer, external cache support, programmable interrupt controller (PIC), local interrupt controller (LIC), and low-power Wait and Stop processing modes.

- 475 Kbyte M2 memory for critical data/temporary data buffering.

- 4 Kbyte boot ROM.

- M2-accessible multi-core MQBus connecting the M2 memory with all four cores, operating at the core frequency, with data bus access of up to 128-bit reads and up to 64-bit writes, central efficient round-robin arbiter for core access to the bus, and atomic control of M2 memory access by the cores and local bus.

- Internal PLL configured are reset by configuration signal values.

- 60x-compatible system bus with 64 or 32 bit data and 32-bit address bus, support for multi-master designs, four-beat burst transfers (eight-beat in 32-bit data mode), port size of 64/32/16/8 bits controlled by the internal memory controller, access to external memory or peripherals, access by an external host to internal resources, slave support with direct access to internal resources including M1 and M2 memories, and on-device arbitration for up to four master devices.

- Direct slave interface (DSI) using a 32/64-bit slave interface with 21–25 bit addressing and 32/64-bit data transfers, direct access by an external host to internal/external resources, synchronous or asynchronous accesses with burst capability in synchronous mode, dual or single strobe mode, write and read buffers to improve host bandwidth, byte enable signals for 1/2/4/8-byte write granularity, sliding window mode for access using a reduced number of address pins, chip ID decoding to allow one CS signal to control multiple DSPs, broadcast mode to write to multiple DSPs, and big-endian/little-endian/munged support.

- Three mode signal multiplexing: 64-bit DSI/32-bit system bus, 32-bit DSI/64-bit system bus, or 32-bit DSI/32-bit system bus.

- Flexible memory controller with three UPMs, a GPCM, a page-mode SDRAM machine, glueless interface to a variety of memories and devices, byte enables for 64-/32-bit bus widths, 8 memory banks for external memories, and 2 memory banks for IPBus peripherals and internal memories.

- Multi-channel DMA controller with 16 time-multiplexed single channels, up to four external peripherals, DONE or DRACK protocol for two external peripherals, service for up to 16 internal requests from up to 8 internal FIFOs per channel, FIFO generated watermarks and hungry requests, priority-based time-multiplexing between channels using 16 internal priority

- levels or round-robin time-multiplexing between channels, flexible channel configuration with connection to local bus or system bus, and flyby transfer support that bypasses the FIFO.

- Up to four independent TDM modules with programmable word size (2, 4, 8, or 16-bit), hardware-base A-law/μ-law conversion, up to 128 Mbps data rate for all channels, with glueless interface to E1 or T1 framers, and can interface with H-MVIP/H.110 devices, TSI, and codecs such as AC-97.

- Ethernet controller: support for 10/100 Mbps MII/RMII/SMII including full- and half-duplex operation, full-duplex flow controls, out-of-sequence transmit queues, programmable maximum frame length including jumbo frames and VLAN tags and priority, retransmission after collision, CRC generation and verification of inbound/outbound packets, address recognition (including exact match, broadcast address, individual hash check, group hash check, and promiscuous mode), pattern matching, insertion with expansion or replacement for transmit frames, VLAN tag insertion, RMON statistics, local bus master DMA for descriptor fetching and buffer access, and optional multiplexing with GPIO (MII/RMII/SMII) or DSI/system bus signals lines (MII/RMII).

- UART with full-duplex operation up to 6.25 Mbps.

- Up to 32 general-purpose input/output (GPIO) ports.

- I<sup>2</sup>C interface that allows booting from EEPROM devices.

- Two timer modules, each with sixteen configurable 16-bit timers.

- Eight programmable hardware semaphores.

- Global interrupt controller (GIC) with interrupt consolidation and routing to INT\_OUT, NMI\_OUT, and the cores; thirty-two virtual maskable interrupts (8 per core) and four virtual NMI (one per core) that can be generated by a simple write access.

- Boot options: external memory, external host, UART, TDM, or I<sup>2</sup>C.

- VCOP with fully programmable feed-forward channel decoding, feed-forward channel equalization and traceback sessions. Up to 400 3GPP 12.2 kbps AMR channels (channel decoding, number of channels linear to frequency). Up to 200 blind transport format detect (BTFD) channels according to the 3GPP standard. Number of channels linear to frequency.

- TCOP with full support for 3GPP and CDMA2000 standards in Turbo decode; up to 20 turbo-coding 384 kbps channels; 8 state PCCC with polynomial as supported by the 3G standards; iterative decoding structure based on Maximum A-Posteriori probability (MAP), with calculations performed in the LOG domain.

# Table of Contents

|                        |                                                                                             |    |

|------------------------|---------------------------------------------------------------------------------------------|----|

| 1                      | Pin Assignments.....                                                                        | 4  |

| 1.1                    | FC-PBGA Ball Layout Diagrams.....                                                           | 4  |

| 1.2                    | Signal List By Ball Location.....                                                           | 7  |

| 2                      | Electrical Characteristics .....                                                            | 13 |

| 2.1                    | Maximum Ratings .....                                                                       | 13 |

| 2.2                    | Recommended Operating Conditions.....                                                       | 14 |

| 2.3                    | Thermal Characteristics .....                                                               | 14 |

| 2.4                    | DC Electrical Characteristics .....                                                         | 15 |

| 2.5                    | AC Timings .....                                                                            | 16 |

| 3                      | Hardware Design Considerations.....                                                         | 40 |

| 3.1                    | Start-up Sequencing Recommendations .....                                                   | 40 |

| 3.2                    | Power Supply Design Considerations.....                                                     | 40 |

| 3.3                    | Connectivity Guidelines .....                                                               | 42 |

| 3.4                    | External SDRAM Selection.....                                                               | 43 |

| 3.5                    | Thermal Considerations .....                                                                | 44 |

| 4                      | Ordering Information.....                                                                   | 44 |

| 5                      | Package Information.....                                                                    | 45 |

| 6                      | Product Documentation .....                                                                 | 45 |

| 7                      | Revision History .....                                                                      | 46 |

| <b>List of Figures</b> |                                                                                             |    |

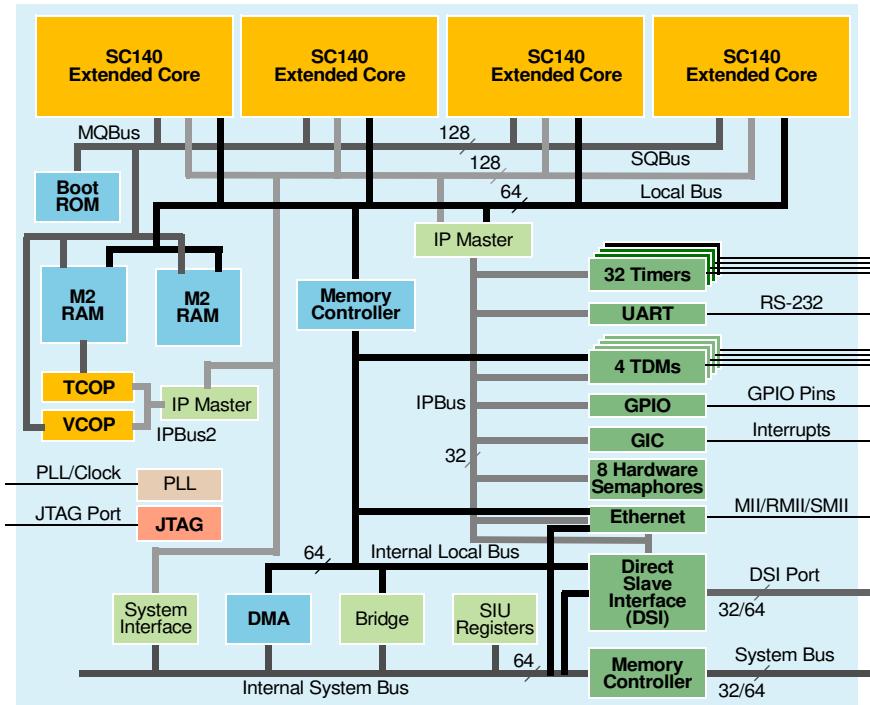

| Figure 1.              | MSC8126 Block Diagram .....                                                                 | 3  |

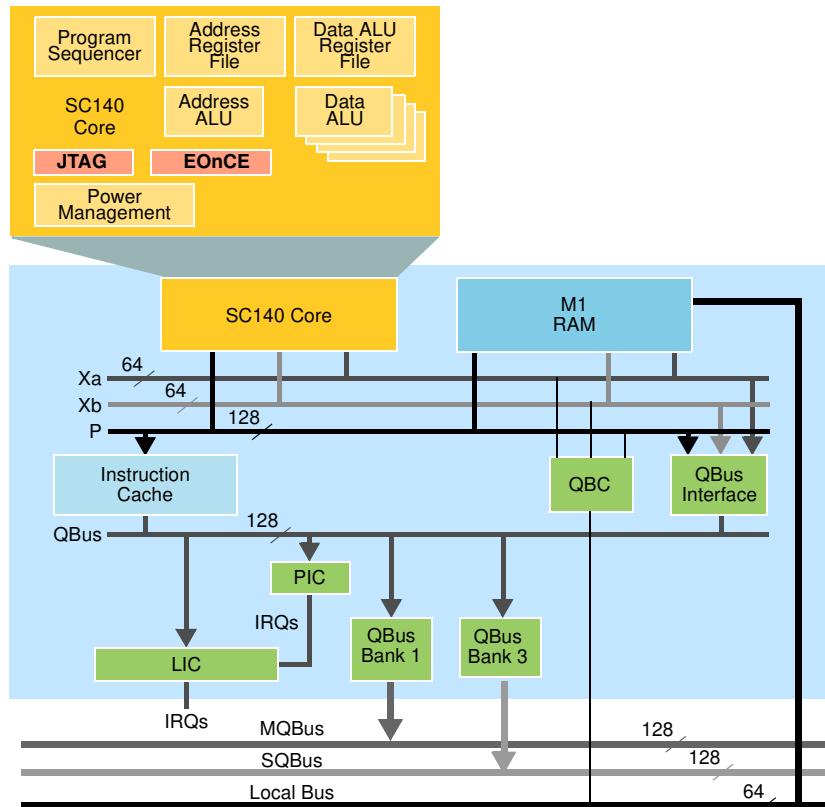

| Figure 2.              | StarCore SC140 DSP Extended Core Block Diagram ..                                           | 3  |

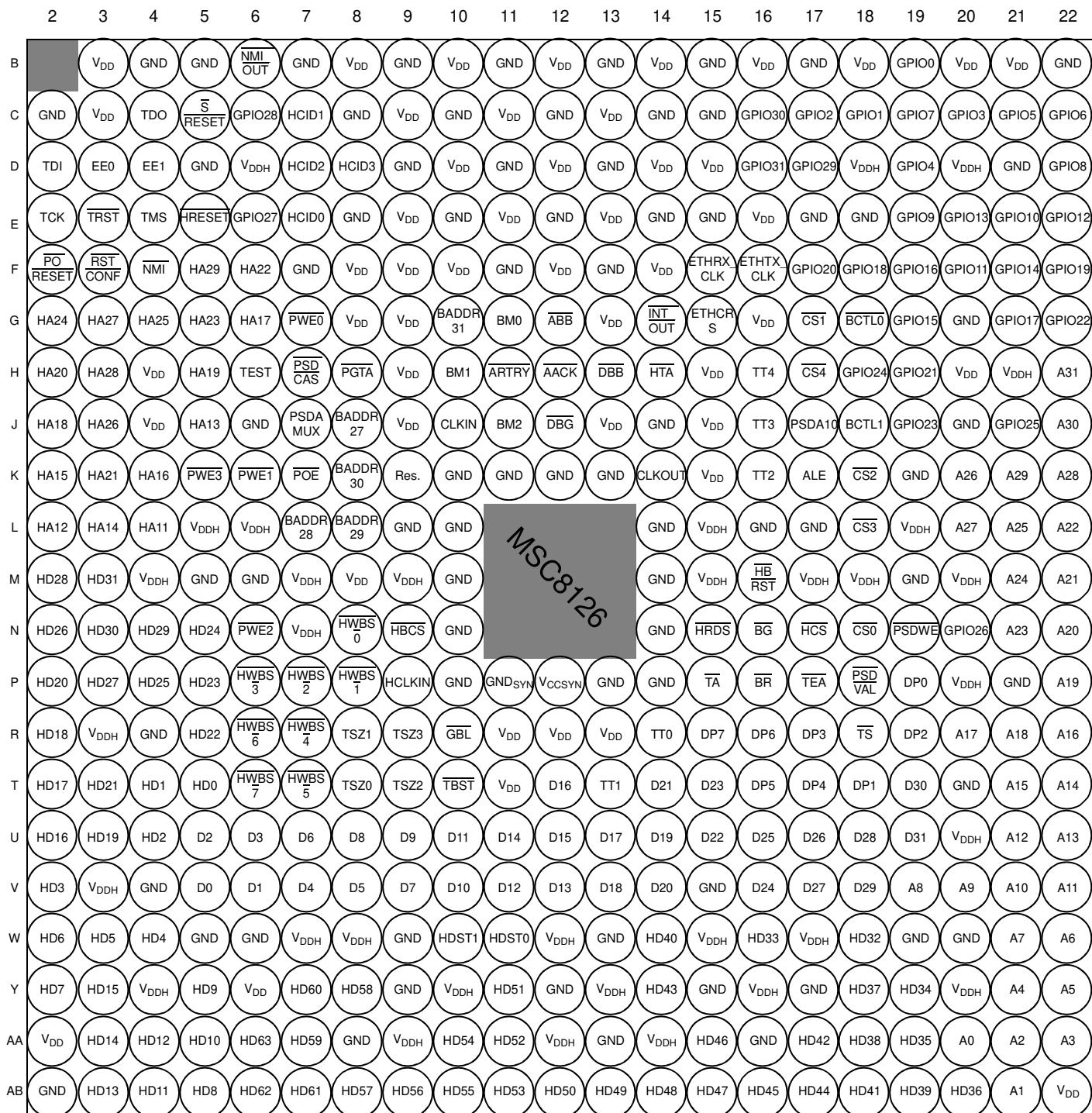

| Figure 3.              | MSC8126 Package, Top View .....                                                             | 5  |

| Figure 4.              | MSC8126 Package, Bottom View.....                                                           | 6  |

| Figure 5.              | Overshoot/Undershoot Voltage for $V_{IH}$ and $V_{IL}$ .....                                | 16 |

| Figure 6.              | Start-Up Sequence: $V_{DD}$ and $V_{DDH}$ Raised Together..                                 | 17 |

| Figure 7.              | Start-Up Sequence: $V_{DD}$ Raised Before $V_{DDH}$ with CLKIN Started with $V_{DDH}$ ..... | 17 |

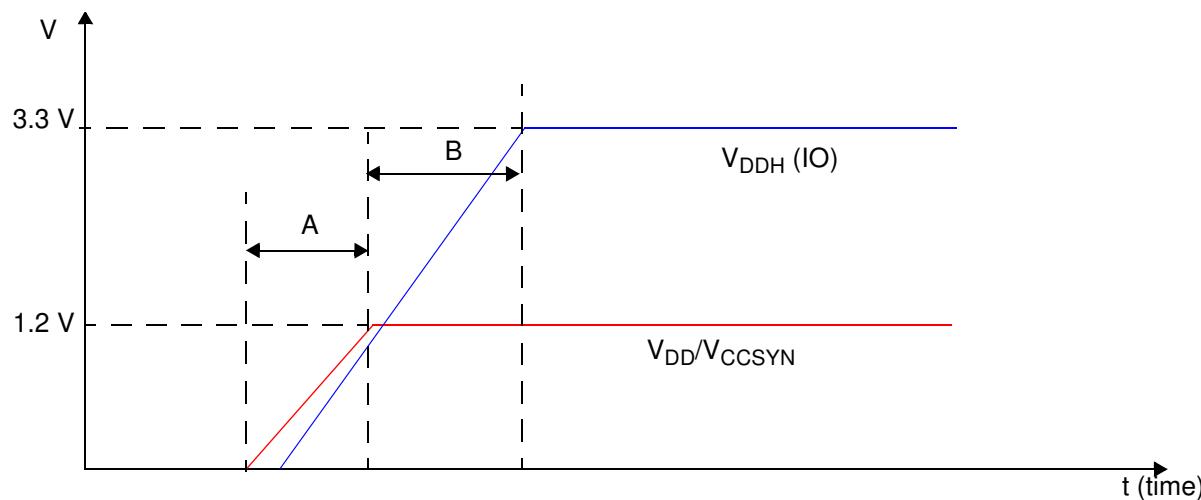

| Figure 8.              | Power-Up Sequence for $V_{DDH}$ and $V_{DD}/V_{CCSYN}$ .....                                | 18 |

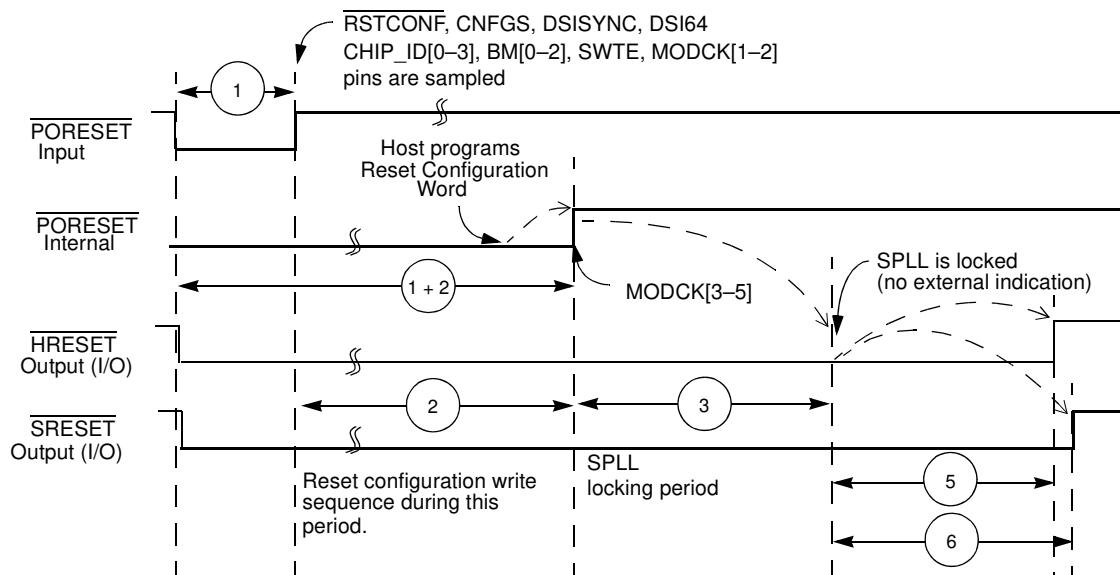

| Figure 9.              | Timing Diagram for a Reset Configuration Write.....                                         | 21 |

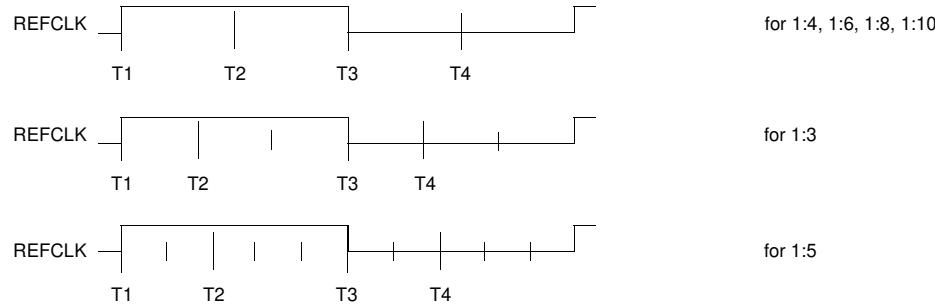

| Figure 10.             | Internal Tick Spacing for Memory Controller Signals.....                                    | 22 |

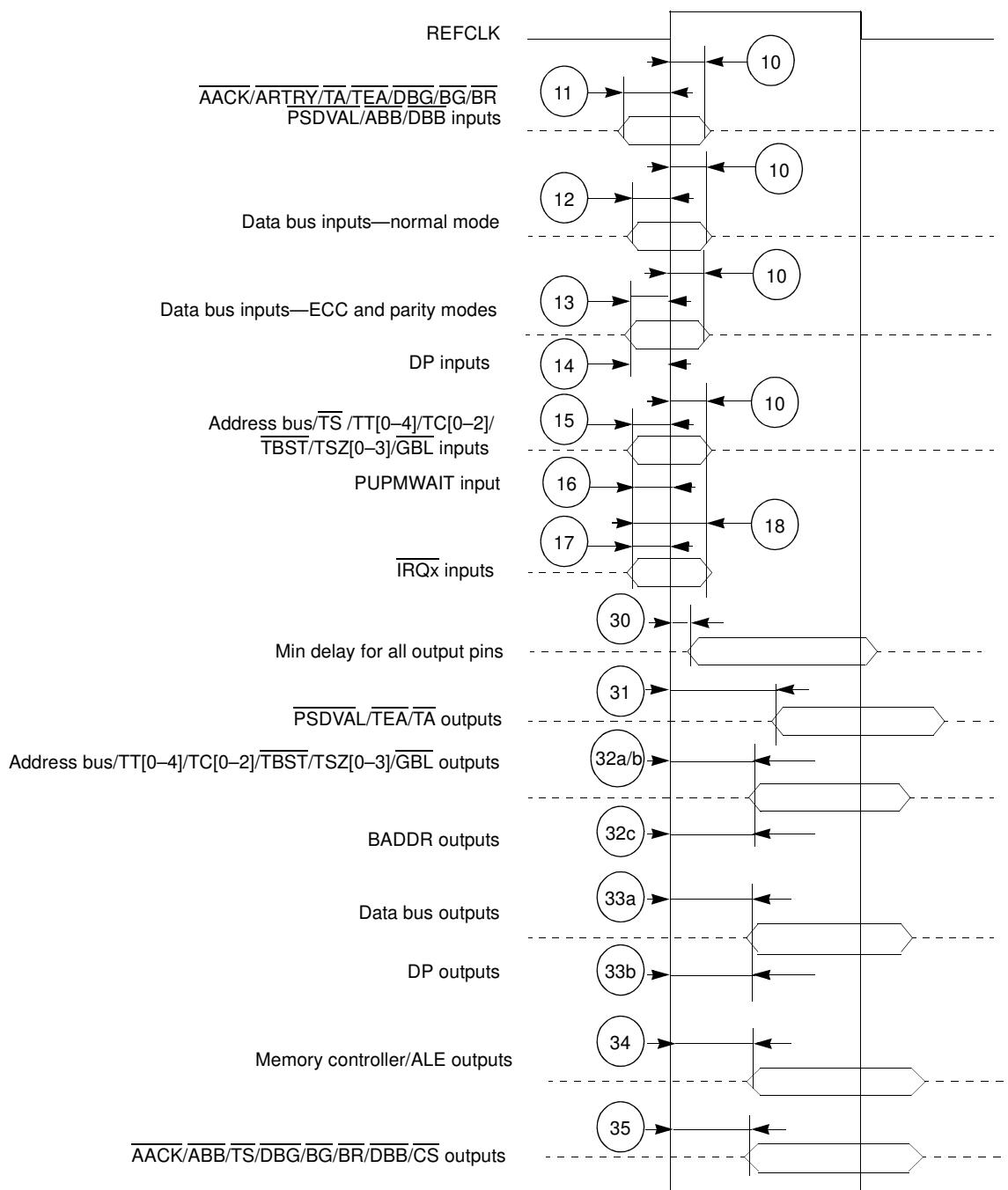

| Figure 11.             | SIU Timing Diagram .....                                                                    | 25 |

| Figure 12.             | CLKOUT and CLKIN Signals .....                                                              | 26 |

| Figure 13.             | DMA Signals .....                                                                           | 27 |

| Figure 14.             | Asynchronous Single- and Dual-Strobe Modes Read Timing Diagram .....                        | 29 |

| Figure 15.             | Asynchronous Single- and Dual-Strobe Modes Write Timing Diagram .....                       | 30 |

| Figure 16.             | Asynchronous Broadcast Write Timing Diagram.....                                            | 30 |

| Figure 17.             | DSI Synchronous Mode Signals Timing Diagram .....                                           | 31 |

| Figure 18.             | TDM Inputs Signals .....                                                                    | 32 |

| Figure 19.             | TDM Output Signals .....                                                                    | 32 |

| Figure 20.             | UART Input Timing .....                                                                     | 33 |

| Figure 21.             | UART Output Timing .....                                                                    | 33 |

| Figure 22.             | Timer Timing .....                                                                          | 34 |

| Figure 23.             | MDIO Timing Relationship to MDC .....                                                       | 34 |

| Figure 24.             | MII Mode Signal Timing .....                                                                | 35 |

| Figure 26.             | SMII Mode Signal Timing .....                                                               | 36 |

| Figure 27.             | GPIO Timing .....                                                                           | 37 |

| Figure 28.             | EE Pin Timing .....                                                                         | 37 |

| Figure 29.             | Test Clock Input Timing Diagram.....                                                        | 38 |

| Figure 30.             | Boundary Scan (JTAG) Timing Diagram .....                                                   | 38 |

| Figure 31.             | Test Access Port Timing Diagram .....                                                       | 39 |

| Figure 32.             | TRST Timing Diagram .....                                                                   | 39 |

| Figure 33.             | Core Power Supply Decoupling.....                                                           | 41 |

| Figure 34.             | $V_{CCSYN}$ Bypass .....                                                                    | 41 |

| Figure 35.             | MSC8126 Mechanical Information, 431-pin FC-PBGA Package.....                                | 45 |

Figure 1. MSC8126 Block Diagram

**Notes:**

1. The arrows show the data transfer direction.

2. The QBus interface includes a bus switch, write buffer, fetch unit, and a control unit that defines four QBus banks. In addition, the QBC handles internal memory contentions.

Figure 2. StarCore SC140 DSP Extended Core Block Diagram

# 1 Pin Assignments

This section includes diagrams of the MSC8126 package ball grid array layouts and pinout allocation tables.

## 1.1 FC-PBGA Ball Layout Diagrams

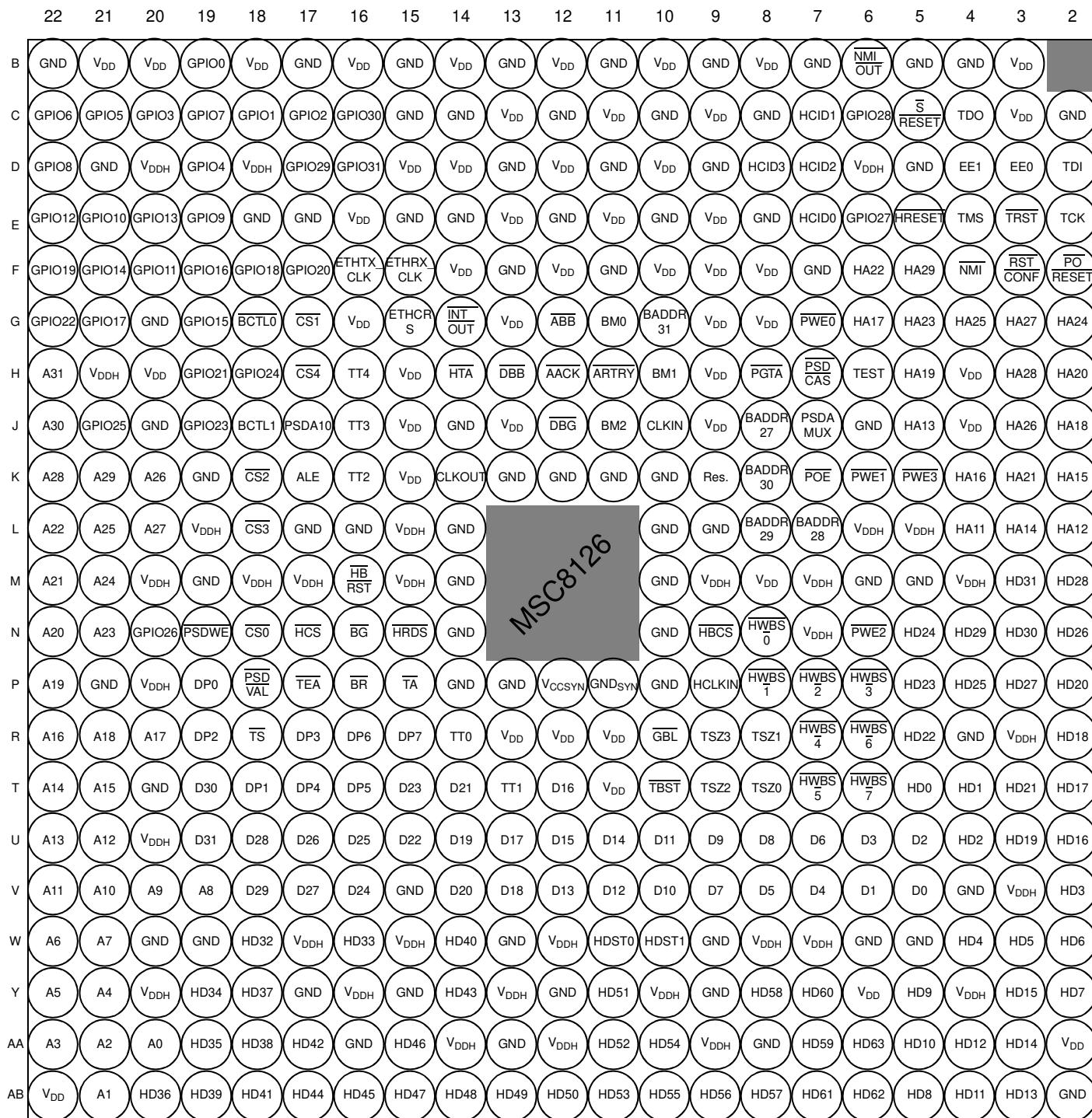

Top and bottom views of the FC-PBGA package are shown in **Figure 3** and **Figure 4** with their ball location index numbers.

### Top View

**Figure 3. MSC8126 Package, Top View**

### Bottom View

**Figure 4. MSC8126 Package, Bottom View**

## 1.2 Signal List By Ball Location

Table 1 presents signal list sorted by ball number. -

Table 1. MSC8126 Signal Listing by Ball Designator

| Des. | Signal Name                 | Des. | Signal Name                        |

|------|-----------------------------|------|------------------------------------|

| B3   | V <sub>DD</sub>             | C18  | GPIO1/TIMER0/CHIP_ID1/IRQ5/ETHTXD1 |

| B4   | GND                         | C19  | GPIO7/TDM3RCLK/IRQ5/ETHTXD3        |

| B5   | GND                         | C20  | GPIO3/TDM3TSYN/IRQ1/ETHTXD2        |

| B6   | NMI_OUT                     | C21  | GPIO5/TDM3TDAT/IRQ3/ETHRXD3        |

| B7   | GND                         | C22  | GPIO6/TDM3RSYN/IRQ4/ETHRXD2        |

| B8   | V <sub>DD</sub>             | D2   | TDI                                |

| B9   | GND                         | D3   | EE0                                |

| B10  | V <sub>DD</sub>             | D4   | EE1                                |

| B11  | GND                         | D5   | GND                                |

| B12  | V <sub>DD</sub>             | D6   | V <sub>DDH</sub>                   |

| B13  | GND                         | D7   | HCID2                              |

| B14  | V <sub>DD</sub>             | D8   | HCID3/HA8                          |

| B15  | GND                         | D9   | GND                                |

| B16  | V <sub>DD</sub>             | D10  | V <sub>DD</sub>                    |

| B17  | GND                         | D11  | GND                                |

| B18  | V <sub>DD</sub>             | D12  | V <sub>DD</sub>                    |

| B19  | GPIO0/CHIP_ID0/IRQ4/ETHTXD0 | D13  | GND                                |

| B20  | V <sub>DD</sub>             | D14  | V <sub>DD</sub>                    |

| B21  | V <sub>DD</sub>             | D15  | V <sub>DD</sub>                    |

| B22  | GND                         | D16  | GPIO31/TIMER3/SCL                  |

| C2   | GND                         | D17  | GPIO29/CHIP_ID3/ETHTX_EN           |

| C3   | V <sub>DD</sub>             | D18  | V <sub>DDH</sub>                   |

| C4   | TDO                         | D19  | GPIO4/TDM3TCLK/IRQ2/ETHTX_ER       |

| C5   | SRESET                      | D20  | V <sub>DDH</sub>                   |

| C6   | GPIO28/DREQ2/UTXD           | D21  | GND                                |

| C7   | HCID1                       | D22  | GPIO8/TDM3RDAT/IRQ6/ETHCOL         |

| C8   | GND                         | E2   | TCK                                |

| C9   | V <sub>DD</sub>             | E3   | TRST                               |

| C10  | GND                         | E4   | TMS                                |

| C11  | V <sub>DD</sub>             | E5   | HRESET                             |

| C12  | GND                         | E6   | GPIO27/DREQ1/URXD                  |

| C13  | V <sub>DD</sub>             | E7   | HCID0                              |

| C14  | GND                         | E8   | GND                                |

| C15  | GND                         | E9   | V <sub>DD</sub>                    |

| C16  | GPIO30/TIMER2/TMCLK/SDA     | E10  | GND                                |

| C17  | GPIO2/TIMER1/CHIP_ID2/IRQ6  | E11  | V <sub>DD</sub>                    |

Table 1. MSC8126 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                                | Des. | Signal Name                     |

|------|--------------------------------------------|------|---------------------------------|

| E12  | GND                                        | G6   | HA17                            |

| E13  | V <sub>DD</sub>                            | G7   | <u>PWE0/PSDDQM0/PBS0</u>        |

| E14  | GND                                        | G8   | V <sub>DD</sub>                 |

| E15  | GND                                        | G9   | V <sub>DD</sub>                 |

| E16  | V <sub>DD</sub>                            | G10  | <u>IRQ3/BADDR31</u>             |

| E17  | GND                                        | G11  | BM0/TC0/BNKSEL0                 |

| E18  | GND                                        | G12  | <u>ABB/IRQ4</u>                 |

| E19  | GPIO9/TDM2TSYN/IRQ7/ETHMDIO                | G13  | V <sub>DD</sub>                 |

| E20  | GPIO13/TDM2RCLK/IRQ11/ETHMDC               | G14  | <u>IRQ7/INT_OUT</u>             |

| E21  | GPIO10/TDM2TCLK/IRQ8/ETHRX_DV/ETHCRS_DV/NC | G15  | ETHCRS/ETHRXD                   |

| E22  | GPIO12/TDM2RSYN/IRQ10/ETHRXD1/ETHSYNC      | G16  | V <sub>DD</sub>                 |

| F2   | <u>PORESET</u>                             | G17  | <u>CS1</u>                      |

| F3   | <u>RSTCONF</u>                             | G18  | <u>BCTL0</u>                    |

| F4   | <u>NMI</u>                                 | G19  | GPIO15/TDM1TSYN/DREQ1           |

| F5   | HA29                                       | G20  | GND                             |

| F6   | HA22                                       | G21  | GPIO17/TDM1TDAT/DACK1           |

| F7   | GND                                        | G22  | GPIO22/TDM0TCLK/DONE2/DRACK2    |

| F8   | V <sub>DD</sub>                            | H2   | HA20                            |

| F9   | V <sub>DD</sub>                            | H3   | HA28                            |

| F10  | V <sub>DD</sub>                            | H4   | V <sub>DD</sub>                 |

| F11  | GND                                        | H5   | HA19                            |

| F12  | V <sub>DD</sub>                            | H6   | TEST                            |

| F13  | GND                                        | H7   | <u>PSDCAS/PGPL3</u>             |

| F14  | V <sub>DD</sub>                            | H8   | <u>PGTA/PUPMWAIT/PGPL4/PPBS</u> |

| F15  | ETHRX_CLK/ETHSYNC_IN                       | H9   | V <sub>DD</sub>                 |

| F16  | ETHTX_CLK/ETHREF_CLK/ETHCLOCK              | H10  | BM1/TC1/BNKSEL1                 |

| F17  | GPIO20/TDM1RDATA                           | H11  | <u>ARTRY</u>                    |

| F18  | GPIO18/TDM1RSYN/DREQ2                      | H12  | <u>AACK</u>                     |

| F19  | GPIO16/TDM1TCLK/DONE1/DRACK1               | H13  | <u>DBB/IRQ5</u>                 |

| F20  | GPIO11/TDM2TDAT/IRQ9/ETHRX_ER/ETHTXD       | H14  | <u>HTA</u>                      |

| F21  | GPIO14/TDM2RDATA/IRQ12/ETHRXD0/NC          | H15  | V <sub>DD</sub>                 |

| F22  | GPIO19/TDM1RCLK/DACK2                      | H16  | TT4/CS7                         |

| G2   | HA24                                       | H17  | <u>CS4</u>                      |

| G3   | HA27                                       | H18  | GPIO24/TDM0RSYN/IRQ14           |

| G4   | HA25                                       | H19  | GPIO21/TDM0TSYN                 |

| G5   | HA23                                       | H20  | V <sub>DD</sub>                 |

| H21  | V <sub>DDH</sub>                           | K15  | V <sub>DD</sub>                 |

| H22  | A31                                        | K16  | TT2/CS5                         |

| J2   | HA18                                       | K17  | ALE                             |

Table 1. MSC8126 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                                                               | Des. | Signal Name                             |

|------|---------------------------------------------------------------------------|------|-----------------------------------------|

| J3   | HA26                                                                      | K18  | $\overline{\text{CS2}}$                 |

| J4   | $V_{DD}$                                                                  | K19  | GND                                     |

| J5   | HA13                                                                      | K20  | A26                                     |

| J6   | GND                                                                       | K21  | A29                                     |

| J7   | PSDAMUX/PGPL5                                                             | K22  | A28                                     |

| J8   | BADDR27                                                                   | L2   | HA12                                    |

| J9   | $V_{DD}$                                                                  | L3   | HA14                                    |

| J10  | CLKIN                                                                     | L4   | HA11                                    |

| J11  | BM2/TC2/BNKSEL2                                                           | L5   | $V_{DDH}$                               |

| J12  | $\overline{\text{DBG}}$                                                   | L6   | $V_{DDH}$                               |

| J13  | $V_{DD}$                                                                  | L7   | BADDR28                                 |

| J14  | GND                                                                       | L8   | $\overline{\text{IRQ5}}/\text{BADDR29}$ |

| J15  | $V_{DD}$                                                                  | L9   | GND                                     |

| J16  | TT3/ $\overline{\text{CS6}}$                                              | L10  | GND                                     |

| J17  | PSDA10/PGPL0                                                              | L14  | GND                                     |

| J18  | $\overline{\text{BCTL1}}/\overline{\text{CS5}}$                           | L15  | $V_{DDH}$                               |

| J19  | GPIO23/TDM0TDAT/ $\overline{\text{IRQ13}}$                                | L16  | GND                                     |

| J20  | GND                                                                       | L17  | GND                                     |

| J21  | GPIO25/TDM0RCLK/ $\overline{\text{IRQ15}}$                                | L18  | $\overline{\text{CS3}}$                 |

| J22  | A30                                                                       | L19  | $V_{DDH}$                               |

| K2   | HA15                                                                      | L20  | A27                                     |

| K3   | HA21                                                                      | L21  | A25                                     |

| K4   | HA16                                                                      | L22  | A22                                     |

| K5   | $\overline{\text{PWE3}}/\overline{\text{PSDDQM3}}/\overline{\text{PBS3}}$ | M2   | HD28                                    |

| K6   | $\overline{\text{PWE1}}/\overline{\text{PSDDQM1}}/\overline{\text{PBS1}}$ | M3   | HD31                                    |

| K7   | $\overline{\text{POE}}/\overline{\text{PSDRAS}}/\overline{\text{GPL2}}$   | M4   | $V_{DDH}$                               |

| K8   | $\overline{\text{IRQ2}}/\text{BADDR30}$                                   | M5   | GND                                     |

| K9   | Reserved                                                                  | M6   | GND                                     |

| K10  | GND                                                                       | M7   | $V_{DDH}$                               |

| K11  | GND                                                                       | M8   | $V_{DD}$                                |

| K12  | GND                                                                       | M9   | $V_{DDH}$                               |

| K13  | GND                                                                       | M10  | GND                                     |

| K14  | CLKOUT                                                                    | M14  | GND                                     |

| M15  | $V_{DDH}$                                                                 | P12  | $V_{CCSYN}$                             |

| M16  | $\overline{\text{HBRST}}$                                                 | P13  | GND                                     |

| M17  | $V_{DDH}$                                                                 | P14  | GND                                     |

| M18  | $V_{DDH}$                                                                 | P15  | $\overline{\text{T}}$                   |

| M19  | GND                                                                       | P16  | $\overline{\text{BR}}$                  |

| M20  | $V_{DDH}$                                                                 | P17  | $\overline{\text{TEA}}$                 |

Table 1. MSC8126 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                                      | Des. | Signal Name                                      |

|------|--------------------------------------------------|------|--------------------------------------------------|

| M21  | A24                                              | P18  | <u>PSDVAL</u>                                    |

| M22  | A21                                              | P19  | DP0/DREQ1/ <u>EXT_BR2</u>                        |

| N2   | HD26                                             | P20  | <u>V<sub>DDH</sub></u>                           |

| N3   | HD30                                             | P21  | GND                                              |

| N4   | HD29                                             | P22  | A19                                              |

| N5   | HD24                                             | R2   | HD18                                             |

| N6   | <u>PWE2/PSDDQM2/PBS2</u>                         | R3   | <u>V<sub>DDH</sub></u>                           |

| N7   | <u>V<sub>DDH</sub></u>                           | R4   | GND                                              |

| N8   | <u>HWBS0/HDBS0/HWBE0/HDBE0</u>                   | R5   | HD22                                             |

| N9   | <u>HBCS</u>                                      | R6   | <u>HWBS6/HDBS6/HWBE6/HDBE6/PWE6/PSDDQM6/PBS6</u> |

| N10  | GND                                              | R7   | <u>HWBS4/HDBS4/HWBE4/HDBE4/PWE4/PSDDQM4/PBS4</u> |

| N14  | GND                                              | R8   | TSZ1                                             |

| N15  | <u>HRDS/HRW/HRDE</u>                             | R9   | TSZ3                                             |

| N16  | <u>BG</u>                                        | R10  | <u>IRQ1/GBL</u>                                  |

| N17  | <u>HCS</u>                                       | R11  | <u>V<sub>DD</sub></u>                            |

| N18  | <u>CS0</u>                                       | R12  | <u>V<sub>DD</sub></u>                            |

| N19  | <u>PSDW<sub>E</sub>/PGPL1</u>                    | R13  | <u>V<sub>DD</sub></u>                            |

| N20  | GPIO26/TDM0RDAT                                  | R14  | TT0/HA7                                          |

| N21  | A23                                              | R15  | <u>IRQ7/DP7/DREQ4</u>                            |

| N22  | A20                                              | R16  | <u>IRQ6/DP6/DREQ3</u>                            |

| P2   | HD20                                             | R17  | <u>IRQ3/DP3/DREQ2/EXT_BR3</u>                    |

| P3   | HD27                                             | R18  | <u>TS</u>                                        |

| P4   | HD25                                             | R19  | <u>IRQ2/DP2/DACK2/EXT_DBG2</u>                   |

| P5   | HD23                                             | R20  | A17                                              |

| P6   | <u>HWBS3/HDBS3/HWBE3/HDBE3</u>                   | R21  | A18                                              |

| P7   | <u>HWBS2/HDBS2/HWBE2/HDBE2</u>                   | R22  | A16                                              |

| P8   | <u>HWBS1/HDBS1/HWBE1/HDBE1</u>                   | T2   | HD17                                             |

| P9   | HCLKIN                                           | T3   | HD21                                             |

| P10  | GND                                              | T4   | HD1/DSISYNC                                      |

| P11  | GND <sub>SYN</sub>                               | T5   | HD0/SWTE                                         |

| T6   | <u>HWBS7/HDBS7/HWBE7/HDBE7/PWE7/PSDDQM7/PBS7</u> | U21  | A12                                              |

| T7   | <u>HWBS5/HDBS5/HWBE5/HDBE5/PWE5/PSDDQM5/PBS5</u> | U22  | A13                                              |

| T8   | TSZ0                                             | V2   | HD3/MODCK1                                       |

| T9   | TSZ2                                             | V3   | <u>V<sub>DDH</sub></u>                           |

| T10  | <u>TBST</u>                                      | V4   | GND                                              |

| T11  | <u>V<sub>DD</sub></u>                            | V5   | D0                                               |

| T12  | D16                                              | V6   | D1                                               |

| T13  | TT1                                              | V7   | D4                                               |

| T14  | D21                                              | V8   | D5                                               |

Table 1. MSC8126 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                    | Des. | Signal Name               |

|------|--------------------------------|------|---------------------------|

| T15  | D23                            | V9   | D7                        |

| T16  | <u>IRQ5/DP5/DACK4/EXT_BG3</u>  | V10  | D10                       |

| T17  | <u>IRQ4/DP4/DACK3/EXT_DBG3</u> | V11  | D12                       |

| T18  | <u>IRQ1/DP1/DACK1/EXT_BG2</u>  | V12  | D13                       |

| T19  | D30                            | V13  | D18                       |

| T20  | GND                            | V14  | D20                       |

| T21  | A15                            | V15  | GND                       |

| T22  | A14                            | V16  | D24                       |

| U2   | HD16                           | V17  | D27                       |

| U3   | HD19                           | V18  | D29                       |

| U4   | HD2/DSI64                      | V19  | A8                        |

| U5   | D2                             | V20  | A9                        |

| U6   | D3                             | V21  | A10                       |

| U7   | D6                             | V22  | A11                       |

| U8   | D8                             | W2   | HD6                       |

| U9   | D9                             | W3   | HD5/CNFGS                 |

| U10  | D11                            | W4   | HD4/MODCK2                |

| U11  | D14                            | W5   | GND                       |

| U12  | D15                            | W6   | GND                       |

| U13  | D17                            | W7   | $V_{DDH}$                 |

| U14  | D19                            | W8   | $V_{DDH}$                 |

| U15  | D22                            | W9   | GND                       |

| U16  | D25                            | W10  | HDST1/HA10                |

| U17  | D26                            | W11  | HDST0/HA9                 |

| U18  | D28                            | W12  | $V_{DDH}$                 |

| U19  | D31                            | W13  | GND                       |

| U20  | $V_{DDH}$                      | W14  | HD40/D40/ETHRXD0          |

| W15  | $V_{DDH}$                      | AA9  | $V_{DDH}$                 |

| W16  | HD33/D33/reserved              | AA10 | HD54/D54/ETHTX_EN         |

| W17  | $V_{DDH}$                      | AA11 | HD52/D52                  |

| W18  | HD32/D32/reserved              | AA12 | $V_{DDH}$                 |

| W19  | GND                            | AA13 | GND                       |

| W20  | GND                            | AA14 | $V_{DDH}$                 |

| W21  | A7                             | AA15 | HD46/D46/ETHXT0           |

| W22  | A6                             | AA16 | GND                       |

| Y2   | HD7                            | AA17 | HD42/D42/ETHRXD2/reserved |

| Y3   | HD15                           | AA18 | HD38/D38/reserved         |

| Y4   | $V_{DDH}$                      | AA19 | HD35/D35/reserved         |

| Y5   | HD9                            | AA20 | A0                        |

Table 1. MSC8126 Signal Listing by Ball Designator (continued)

| Des. | Signal Name               | Des. | Signal Name                 |

|------|---------------------------|------|-----------------------------|

| Y6   | V <sub>DD</sub>           | AA21 | A2                          |

| Y7   | HD60/D60/ETHCOL/reserved  | AA22 | A3                          |

| Y8   | HD58/D58/ETHMDC           | AB2  | GND                         |

| Y9   | GND                       | AB3  | HD13                        |

| Y10  | V <sub>DDH</sub>          | AB4  | HD11                        |

| Y11  | HD51/D51                  | AB5  | HD8                         |

| Y12  | GND                       | AB6  | HD62/D62                    |

| Y13  | V <sub>DDH</sub>          | AB7  | HD61/D61                    |

| Y14  | HD43/D43/ETHRXD3/reserved | AB8  | HD57/D57/ETHRX_ER           |

| Y15  | GND                       | AB9  | HD56/D56/ETHRX_DV/ETHCRS_DV |

| Y16  | V <sub>DDH</sub>          | AB10 | HD55/D55/ETHTX_ER/reserved  |

| Y17  | GND                       | AB11 | HD53/D53                    |

| Y18  | HD37/D37/reserved         | AB12 | HD50/D50                    |

| Y19  | HD34/D34/reserved         | AB13 | HD49/D49/ETHTXD3/reserved   |

| Y20  | V <sub>DDH</sub>          | AB14 | HD48/D48/ETHTXD2/reserved   |

| Y21  | A4                        | AB15 | HD47/D47/ETHTXD1            |

| Y22  | A5                        | AB16 | HD45/D45                    |

| AA2  | V <sub>DD</sub>           | AB17 | HD44/D44                    |

| AA3  | HD14                      | AB18 | HD41/D41/ETHRXD1            |

| AA4  | HD12                      | AB19 | HD39/D39/reserved           |

| AA5  | HD10                      | AB20 | HD36/D36/reserved           |

| AA6  | HD63/D63                  | AB21 | A1                          |

| AA7  | HD59/D59/ETHMDIO          | AB22 | V <sub>DD</sub>             |

| AA8  | GND                       |      |                             |

## 2 Electrical Characteristics

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the *MSC8126 Reference Manual*.

### 2.1 Maximum Ratings

#### CAUTION

**This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).**

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a “maximum” value for a specification never occurs in the same device with a “minimum” value for another specification; adding a maximum to a minimum represents a condition that can never exist.

**Table 2** describes the maximum electrical ratings for the MSC8126.

**Table 2. Absolute Maximum Ratings**

| Rating                                                   | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Value       | Unit |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Core and PLL supply voltage                              | $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -0.2 to 1.6 | V    |

| I/O supply voltage                                       | $V_{DDH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.2 to 4.0 | V    |

| Input voltage                                            | $V_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -0.2 to 4.0 | V    |

| Maximum operating temperature:<br>• 400 MHz<br>• 500 MHz | $T_J$                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105<br>90   | °C   |

| Minimum operating temperature<br>• 400 MHz<br>• 500 MHz  | $T_J$                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -40<br>0    | °C   |

| Storage temperature range                                | $T_{STG}$                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -55 to +150 | °C   |

| <b>Notes:</b>                                            | <ol style="list-style-type: none"><li>Functional operating conditions are given in <b>Table 3</b>.</li><li>Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.</li><li><b>Section 3.5, Thermal Considerations</b> includes a formula for computing the chip junction temperature (<math>T_J</math>).</li></ol> |             |      |

## 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

**Table 3. Recommended Operating Conditions**

| Rating                                                                                              | Symbol                  | Value                                        | Unit |

|-----------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|------|

| Core and PLL supply voltage:<br>• Standard<br>— 400 MHz<br>— 500 MHz<br>• Reduced (300 and 400 MHz) | $V_{DD}$<br>$V_{CCSYN}$ | 1.14 to 1.26<br>1.16 to 1.24<br>1.07 to 1.13 | V    |

| I/O supply voltage                                                                                  | $V_{DDH}$               | 3.135 to 3.465                               | V    |

| Input voltage                                                                                       | $V_{IN}$                | -0.2 to $V_{DDH}+0.2$                        | V    |

| Operating temperature range:<br>• Standard<br>• Extended                                            | $T_J$<br>$T_J$          | 0 to 90<br>-40 to 105                        | °C   |

## 2.3 Thermal Characteristics

Table 4 describes thermal characteristics of the MSC8126 for the FC-PBGA packages.

**Table 4. Thermal Characteristics for the MSC8126**

| Characteristic                                        | Symbol          | FC-PBGA<br>20 × 20 mm <sup>5</sup> |                               | Unit |

|-------------------------------------------------------|-----------------|------------------------------------|-------------------------------|------|

|                                                       |                 | Natural<br>Convection              | 200 ft/min<br>(1 m/s) airflow |      |

| Junction-to-ambient <sup>1, 2</sup>                   | $R_{\theta JA}$ | 26                                 | 21                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup> | $R_{\theta JA}$ | 19                                 | 15                            | °C/W |

| Junction-to-board (bottom) <sup>4</sup>               | $R_{\theta JB}$ | 9                                  |                               | °C/W |

| Junction-to-case <sup>5</sup>                         | $R_{\theta JC}$ | 0.9                                |                               | °C/W |

| Junction-to-package-top <sup>6</sup>                  | $\Psi_{JT}$     | 1                                  |                               | °C/W |

**Notes:**

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

3. Per JEDEC JESD51-6 with the board horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

Section 3.5, *Thermal Considerations* provides a detailed explanation of these characteristics.

## 2.4 DC Electrical Characteristics

This section describes the DC electrical characteristics for the MSC8126. The measurements in **Table 5** assume the following system conditions:

- $T_A = 25^\circ\text{C}$

- $V_{DD} =$

- 400 MHz = 1.14–1.26 V<sub>DC</sub>

- 500 MHz = 1.16–1.24 V<sub>DC</sub>

- $V_{DDH} = 3.3 \text{ V} \pm 5\% \text{ V}_{DC}$

- $\text{GND} = 0 \text{ V}_{DC}$

**Note:** The leakage current is measured for nominal  $V_{DDH}$  and  $V_{DD}$ .

**Table 5. DC Electrical Characteristics**

| Characteristic                                                            | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Min    | Typical                              | Max    | Unit          |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------|--------|---------------|

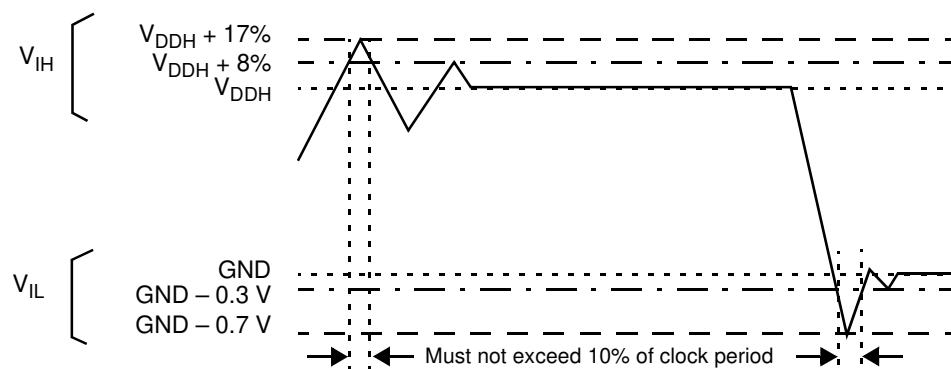

| Input high voltage <sup>1</sup> , all inputs except CLKIN                 | $V_{IH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.0    | —                                    | 3.465  | V             |

| Input low voltage <sup>1</sup>                                            | $V_{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND    | 0                                    | 0.8    | V             |

| CLKIN input high voltage                                                  | $V_{IHC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.4    | 3.0                                  | 3.465  | V             |

| CLKIN input low voltage                                                   | $V_{ILC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND    | 0                                    | 0.8    | V             |

| Input leakage current, $V_{IN} = V_{DDH}$                                 | $I_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | –1.0   | 0.09                                 | 1      | $\mu\text{A}$ |

| Tri-state (high impedance off state) leakage current, $V_{IN} = V_{DDH}$  | $I_{OZ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | –1.0   | 0.09                                 | 1      | $\mu\text{A}$ |

| Signal low input current, $V_{IL} = 0.8 \text{ V}^2$                      | $I_L$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | –1.0   | 0.09                                 | 1      | $\mu\text{A}$ |

| Signal high input current, $V_{IH} = 2.0 \text{ V}^2$                     | $I_H$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | –1.0   | 0.09                                 | 1      | $\mu\text{A}$ |

| Output high voltage, $I_{OH} = –2 \text{ mA}$ ,<br>except open drain pins | $V_{OH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.0    | 3.0                                  | —      | V             |

| Output low voltage, $I_{OL} = 3.2 \text{ mA}$                             | $V_{OL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —      | 0                                    | 0.4    | V             |

| $V_{CCSYN}$ PLL supply current                                            | $I_{VCCSYN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —      | 2                                    | 4      | mA            |

| Internal supply current:<br>• Wait mode<br>• Stop mode                    | $I_{DDW}$<br>$I_{DDS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —<br>— | 375 <sup>3</sup><br>290 <sup>3</sup> | —<br>— | mA<br>mA      |

| Typical power 400 MHz at 1.2 V <sup>4</sup>                               | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —      | 1.15                                 | —      | W             |

| <b>Notes:</b>                                                             | <ol style="list-style-type: none"> <li>1. See <b>Figure 5</b> for undershoot and overshoot voltages.</li> <li>2. Not tested. Guaranteed by design.</li> <li>3. Measured for 1.2 V core at 25°C junction temperature.</li> <li>4. The typical power values were measured using an EFR code with the device running at a junction temperature of 25°C. No peripherals were enabled and the ICache was not enabled. The source code was optimized to use all the ALUs and AGUs and all four cores. It was created using CodeWarrior® 2.5. These values are provided as examples only. Power consumption is application dependent and varies widely. To assure proper board design with regard to thermal dissipation and maintaining proper operating temperatures, evaluate power consumption for your application and use the design guidelines in <b>Chapter 4</b> of this document and in <i>MSC8102, MSC8122, and MSC8126 Thermal Management Design Guidelines</i> (AN2601).</li> </ol> |        |                                      |        |               |

Figure 5. Overshoot/Uncertain Voltage for  $V_{IH}$  and  $V_{IL}$

## 2.5 AC Timings

The following sections include illustrations and tables of clock diagrams, signals, and parallel I/O outputs and inputs. When systems such as DSP farms are developed using the DSI, use a device loading of 4 pF per pin. AC timings are based on a 20 pF load, except where noted otherwise, and a 50  $\Omega$  transmission line. For loads smaller than 20 pF, subtract 0.06 ns per pF down to 10 pF load. For loads larger than 20 pF, add 0.06 ns for SIU/Ethernet/DSI delay and 0.07 ns for GPIO/TDM/timer delay. When calculating overall loading, also consider additional RC delay.

### 2.5.1 Output Buffer Impedances

Table 6. Output Buffer Impedances

| Output Buffers    | Typical Impedance ( $\Omega$ ) |

|-------------------|--------------------------------|

| System bus        | 50                             |

| Memory controller | 50                             |

| Parallel I/O      | 50                             |

**Note:** These are typical values at 65°C. The impedance may vary by  $\pm 25\%$  depending on device process and operating temperature.

### 2.5.2 Start-Up Timing

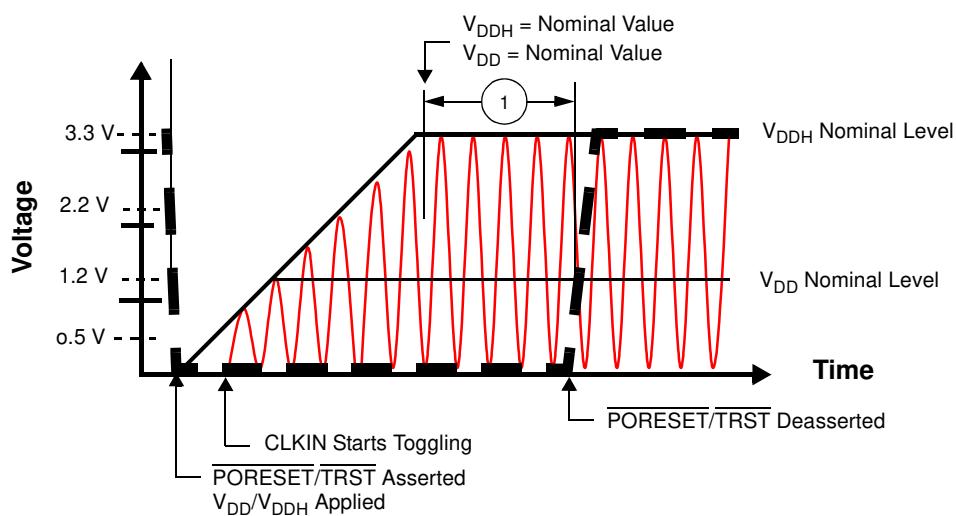

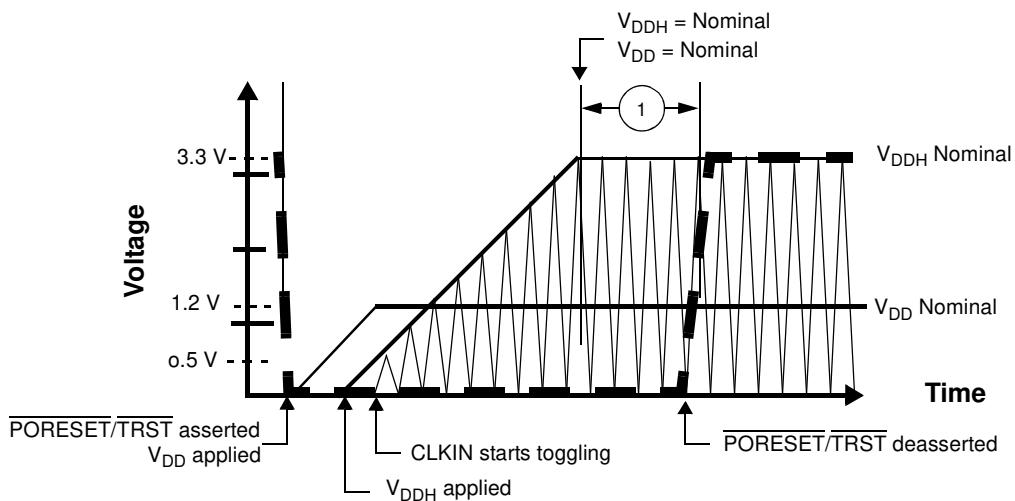

Starting the device requires coordination among several input sequences including clocking, reset, and power. **Section 2.5.3** describes the clocking characteristics. **Section 2.5.4** describes the reset and power-up characteristics. You must use the following guidelines when starting up an MSC8126 device:

- $\overline{PORESET}$  and  $\overline{TRST}$  must be asserted externally for the duration of the power-up sequence. See **Table 11** for timing.

- If possible, bring up the  $V_{DD}$  and  $V_{DDH}$  levels together. For designs with separate power supplies, bring up the  $V_{DD}$  levels and then the  $V_{DDH}$  levels (see **Figure 7**).

- $CLKIN$  should start toggling at least 16 cycles (starting after  $V_{DDH}$  reaches its nominal level) before  $\overline{PORESET}$  deassertion to guarantee correct device operation (see **Figure 6** and **Figure 7**).

- $CLKIN$  must not be pulled high during  $V_{DDH}$  power-up.  $CLKIN$  can toggle during this period.

**Note:** See **Section 3.1** for start-up sequencing recommendations and **Section 3.2** for power supply design recommendations.

The following figures show acceptable start-up sequence examples. **Figure 6** shows a sequence in which  $V_{DD}$  and  $V_{DDH}$  are raised together. **Figure 7** shows a sequence in which  $V_{DDH}$  is raised after  $V_{DD}$  and  $CLKIN$  begins to toggle as  $V_{DDH}$  rises.

Figure 6. Start-Up Sequence:  $V_{DD}$  and  $V_{DDH}$  Raised Together

Figure 7. Start-Up Sequence:  $V_{DD}$  Raised Before  $V_{DDH}$  with CLKIN Started with  $V_{DDH}$

In all cases, the power-up sequence must follow the guidelines shown in **Figure 8**.

**Figure 8. Power-Up Sequence for  $V_{DDH}$  and  $V_{DD}/V_{CCSYN}$**

The following rules apply:

1. During time interval A,  $V_{DDH}$  should always be equal to or less than the  $V_{DD}/V_{CCSYN}$  voltage level. The duration of interval A should be kept below 10 ms.

2. The duration of timing interval B should be kept as small as possible and less than 10 ms.

### 2.5.3 Clock and Timing Signals

The following sections include a description of clock signal characteristics. **Table 7** shows the maximum frequency values for internal (Core, Reference, Bus, and DSI) and external (CLKIN and CLKOUT) clocks. The user must ensure that maximum frequency values are not exceeded.

**Table 7. Maximum Frequencies**

| Characteristic                             | Maximum in MHz                                  |

|--------------------------------------------|-------------------------------------------------|

| Core frequency                             | 400/500                                         |

| Reference frequency (REFCLK)               | 133/166                                         |

| Internal bus frequency (BLCK)              | 133/166                                         |

| DSI clock frequency (HCLKIN)               | $HCLKIN \leq (\min\{100 \text{ MHz}, CLKOUT\})$ |

| External clock frequency (CLKIN or CLKOUT) | 133/166                                         |

**Table 8. Clock Frequencies**

| Characteristics                    | Symbol       | 400 MHz Device |       | 500 MHz Device |       |

|------------------------------------|--------------|----------------|-------|----------------|-------|

|                                    |              | Min            | Max   | Min            | Max   |

| CLKIN frequency                    | $F_{CLKIN}$  | 20             | 133.3 | 20             | 166.7 |

| BCLK frequency                     | $F_{BCLK}$   | 40             | 133.3 | 40             | 166.7 |

| Reference clock (REFCLK) frequency | $F_{REFCLK}$ | 40             | 133.3 | 40             | 166.7 |

| Output clock (CLKOUT) frequency    | $F_{CLKOUT}$ | 40             | 133.3 | 40             | 166.7 |

| SC140 core clock frequency         | $F_{CORE}$   | 200            | 400   | 200            | 500   |

**Note:** The rise and fall time of external clocks should be 5 ns maximum

Table 9. System Clock Parameters

| Characteristic                                                           | Min                                                                                                              | Max         | Unit |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------|------|

| Phase jitter between BCLK and CLKIN                                      | —                                                                                                                | 0.3         | ns   |

| CLKIN frequency                                                          | 20                                                                                                               | see Table 8 | MHz  |

| CLKIN slope                                                              | —                                                                                                                | 3           | ns   |

| PLL input clock (after predivider)                                       | 20                                                                                                               | 100         | MHz  |

| PLL output frequency (VCO output)                                        | 800                                                                                                              |             | MHz  |

| • 400 MHz core                                                           |                                                                                                                  | 1600        | MHz  |

| • 500 MHz core                                                           |                                                                                                                  | 2000        | MHz  |

| CLKOUT frequency jitter <sup>1</sup>                                     | —                                                                                                                | 200         | ps   |

| CLKOUT phase jitter <sup>1</sup> with CLKIN phase jitter of $\pm 100$ ps | —                                                                                                                | 500         | ps   |

| <b>Notes:</b>                                                            | <ol style="list-style-type: none"> <li>1. Peak-to-peak.</li> <li>2. Not tested. Guaranteed by design.</li> </ol> |             |      |

## 2.5.4 Reset Timing

The MSC8126 has several inputs to the reset logic:

- Power-on reset (PORESET)

- External hard reset (HRESET)

- External soft reset (SRESET)

- Software watchdog reset

- Bus monitor reset

- Host reset command through JTAG

All MSC8126 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. **Table 10** describes the reset sources.

Table 10. Reset Sources

| Name                               | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)        | Input         | Initiates the power-on reset flow that resets the MSC8126 and configures various attributes of the MSC8126. On PORESET, the entire MSC8126 device is reset. SPLL states is reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The clock mode (MODCK bits), reset configuration mode, boot mode, Chip ID, and use of either a DSI 64 bits port or a System Bus 64 bits port are configured only when PORESET is asserted.                                                             |

| External hard reset (HRESET)       | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC8126. While HRESET is asserted, SRESET is also asserted. HRESET is an open-drain pin. Upon hard reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The most configurable features are reconfigured. These features are defined in the 32-bit hard reset configuration word described in <i>Hard Reset Configuration Word</i> section of the <i>Reset</i> chapter in the <i>MSC8126 Reference Manual</i> . |

| External soft reset (SRESET)       | Input/ Output | Initiates the soft reset flow. The MSC8126 detects an external assertion of SRESET only if it occurs while the MSC8126 is not asserting reset. SRESET is an open-drain pin. Upon soft reset, SRESET is driven, the SC140 extended cores are reset, and system configuration is maintained.                                                                                                                                                                                                                                                      |

| Software watchdog reset            | Internal      | When the MSC8126 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                                       |