# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **MSM51V17400F**

#### 4,194,304-Word × 4-Bit DYNAMIC RAM : FAST PAGE MODE TYPE

#### DESCRIPTION

The MSM51V17400F is a 4,194,304-word  $\times$  4-bit dynamic RAM fabricated in LAPIS Semiconductor's silicon-gate CMOS technology. The MSM51V17400F achieves high integration, high-speed operation, and low-power consumption because LAPIS Semiconductor manufactures the device in a quadruple-layer polysilicon/double-layer metal CMOS process. The MSM51V17400F is available in a 26/24-pin plastic TSOP.

#### FEATURES

- $\cdot$  4,194,304-word  $\times$  4-bit configuration

- $\cdot$  Single 3.3V power supply,  $\pm 0.3$ V tolerance

- Input : LVTTL compatible, low input capacitance

- · Output : LVTTL compatible, 3-state

- · Refresh : 2048 cycles/32ms

- · Fast page mode, read modify write capability

- · CAS before RAS refresh, hidden refresh, RAS-only refresh capability

- · Packages:

26/24-pin 300mil plastic TSOP (P-TSOP(2)26/24-300-1.27-Z3K)

#### **PRODUCT FAMILY**

|                 | ŀ                | Access Ti       | me (Max.         | )                | Cycle Time | Power Dissipation   |                   |  |

|-----------------|------------------|-----------------|------------------|------------------|------------|---------------------|-------------------|--|

| Family          | t <sub>RAC</sub> | t <sub>AA</sub> | t <sub>CAC</sub> | t <sub>OEA</sub> | (Min.)     | Operating<br>(Max.) | Standby<br>(Max.) |  |

| MSM51V17400F-60 | 60ns             | 30ns            | 15ns             | 15ns             | 110ns      | 324mW               | 1.8mW             |  |

#### MSM51V17400F

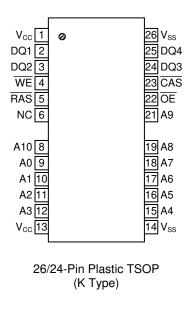

#### PIN CONFIGURATION (TOP VIEW)

| Function               |  |  |  |

|------------------------|--|--|--|

| Address Input          |  |  |  |

| Row Address Strobe     |  |  |  |

| Column Address Strobe  |  |  |  |

| Data Input/Data Output |  |  |  |

| Output Enable          |  |  |  |

| Write Enable           |  |  |  |

| Power Supply (3.3V)    |  |  |  |

| Ground (0V)            |  |  |  |

| No Connection          |  |  |  |

|                        |  |  |  |

Note : The same power supply voltage must be provided to every  $V_{CC}$  pin, and the same GND voltage level must be provided to every  $V_{SS}$  pin.

#### **ELECTRICAL CHARACTERISTICS**

#### ABSOLUTE MAXIMUM RATINGS

| Parameter                                    | Symbol                             | Value                         | Unit |

|----------------------------------------------|------------------------------------|-------------------------------|------|

| Voltage on Any Pin Relative to $V_{SS}$      | V <sub>IN</sub> , V <sub>OUT</sub> | –0.5 to V <sub>CC</sub> + 0.5 | V    |

| Voltage $V_{CC}$ Supply relative to $V_{SS}$ | V <sub>CC</sub>                    | -0.5 to 4.6                   | V    |

| Short Circuit Output Current                 | I <sub>OS</sub>                    | 50                            | mA   |

| Power Dissipation                            | ₽ <sub>D*</sub>                    | 1                             | W    |

| Operating Temperature                        | T <sub>opr</sub>                   | 0 to 70                       | °C   |

| Storage Temperature                          | T <sub>stg</sub>                   | –55 to 150                    | °C   |

\*: Ta = 25°C

#### **RECOMMENDED OPERATING CONDITIONS**

|                      |                 |                     |      | (Ta                | $a = 0$ to $70^{\circ}C$ ) |

|----------------------|-----------------|---------------------|------|--------------------|----------------------------|

| Parameter            | Symbol          | Min.                | Тур. | Max.               | Unit                       |

| Power Supply Voltage | V <sub>CC</sub> | 3.0                 | 3.3  | 3.6                | V                          |

| Fower Suppry Voltage | V <sub>SS</sub> | 0                   | 0    | 0                  | V                          |

| Input High Voltage   | V <sub>IH</sub> | 2.0                 | _    | $V_{CC} + 0.3^{1}$ | V                          |

| Input Low Voltage    | V <sub>IL</sub> | - 0.3 <sup>*2</sup> | _    | 0.8                | V                          |

Notes: \*1. The input voltage is  $V_{CC}$  + 1.0V when the pulse width is less than 20ns (the pulse width is with respect to the point at which  $V_{CC}$  is applied).

\*2. The input voltage is  $V_{SS} - 1.0V$  when the pulse width is less than 20ns (the pulse width respect to the point at which  $V_{SS}$  is applied).

#### PIN CAPACITANCE

| 1 | Nec - | 3 31/ | +0.3      | V To -  | = 25°C, | f _ 1 |        |

|---|-------|-------|-----------|---------|---------|-------|--------|

|   | VCC = | 3.3V  | $\pm 0.3$ | v, ia = | = 25°0, | I = I | IVIHZ) |

| Parameter                               | Symbol           | Min. | Min. | Unit |

|-----------------------------------------|------------------|------|------|------|

| Input Capacitance (A0 – A10)            | C <sub>IN1</sub> | _    | 5    | pF   |

| Input Capacitance<br>(RAS, CAS, WE, OE) | C <sub>IN2</sub> |      | 7    | pF   |

| Output Capacitance (DQ1 - DQ4)          | C <sub>I/O</sub> | _    | 7    | pF   |

#### FEDD51V17400F-03

#### MSM51V17400F

#### DC CHARACTERISTICS

|                                                                |                  |                                                                                                                                                                             |      | $(V_{CC} = 3.3V)$ | ± 0.3V, Ta = | 0 to 70°C) |

|----------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|--------------|------------|

| Parameter                                                      | Symbol Condition |                                                                                                                                                                             |      | V17400<br>60      | Unit         | Note       |

|                                                                |                  |                                                                                                                                                                             | Min. | Max.              |              |            |

| Output High Voltage                                            | V <sub>OH</sub>  | I <sub>OH</sub> = -2.0mA                                                                                                                                                    | 2.4  | V <sub>CC</sub>   | V            |            |

| Output Low Voltage                                             | V <sub>OL</sub>  | I <sub>OL</sub> = 2.0mA                                                                                                                                                     | 0    | 0.4               | V            |            |

| Input Leakage<br>Current                                       | ILI              | $\label{eq:VCC} \begin{split} &0V \leq V_I \leq V_{CC} + 0.3V; \\ & \text{All other pins not} \\ & \text{under test} = 0V \end{split}$                                      | - 10 | 10                | μA           |            |

| Output Leakage<br>Current                                      | ILO              | DQ disable $0V \le V_O \le V_{CC}$                                                                                                                                          | - 10 | 10                | μΑ           |            |

| Average Power<br>Supply Current<br>(Operating)                 | I <sub>CC1</sub> | RAS, CAS cycling,<br>t <sub>RC</sub> = Min.                                                                                                                                 | _    | 90                | mA           | 1,2        |

| Power Supply                                                   |                  | $\overline{\text{RAS}}, \overline{\text{CAS}} = V_{IH}$                                                                                                                     | _    | 2                 |              |            |

| Current<br>(Standby)                                           | 1002             |                                                                                                                                                                             |      | 0.5               | mA           | 1          |

| Average Power<br>Supply Current<br>(RAS-only Refresh)          | I <sub>CC3</sub> | $\label{eq:RAS} \begin{array}{l} \overline{\text{RAS}} \text{ cycling}, \\ \overline{\text{CAS}} = \text{V}_{\text{IH}}, \\ \text{t}_{\text{RC}} = \text{Min}. \end{array}$ | _    | 90                | mA           | 1,2        |

| Power Supply<br>Current<br>(Standby)                           | I <sub>CC5</sub> | $\label{eq:RAS} \begin{split} \overline{RAS} &= V_{IH}, \\ \overline{CAS} &= V_{IL}, \\ DQ &= enable \end{split}$                                                           |      | 5                 | mA           | 1          |

| Average Power<br>Supply Current<br>(CAS before RAS<br>Refresh) | I <sub>CC6</sub> | $\overline{RAS}$ = cycling,<br>$\overline{CAS}$ before $\overline{RAS}$                                                                                                     | _    | 90                | mA           | 1,2        |

| Average Power<br>Supply Current<br>(Fast Page Mode)            | I <sub>CC7</sub> | $\label{eq:RAS} \begin{split} \overline{\text{RAS}} &= \text{V}_{\text{IL}},\\ \overline{\text{CAS}} \text{ cycling},\\ \text{t}_{\text{PC}} &= \text{Min}. \end{split}$    | _    | 70                | mA           | 1,3        |

$(V_{CC} = 3.3V \pm 0.3V, Ta = 0 \text{ to } 70^{\circ}\text{C})$

Notes: 1.  $I_{CC}$  Max. is specified as  $I_{CC}$  for output open condition.

2. The address can be changed once or less while  $\overline{RAS} = V_{IL}$ .

3. The address can be changed once or less while  $\overline{CAS} = V_{IH}$ .

#### FEDD51V17400F-03

MSM51V17400F

#### AC CHARACTERISTICS (1/2)

| Parameter                                                | Symbol            |      | 51V17400<br>F-60 | Unit | Note    |

|----------------------------------------------------------|-------------------|------|------------------|------|---------|

|                                                          |                   | Min. | Max.             |      |         |

| Random Read or Write Cycle Time                          | t <sub>RC</sub>   | 110  | _                | ns   |         |

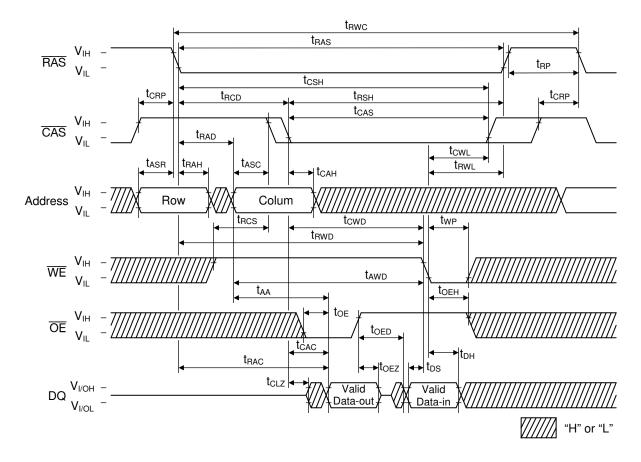

| Read Modify Write Cycle Time                             | t <sub>RWC</sub>  | 155  | _                | ns   |         |

| Fast Page Mode Cycle Time                                | t <sub>PC</sub>   | 40   | _                | ns   |         |

| Fast Page Mode Read Modify Write<br>Cycle Time           | t <sub>PRWC</sub> | 85   | _                | ns   |         |

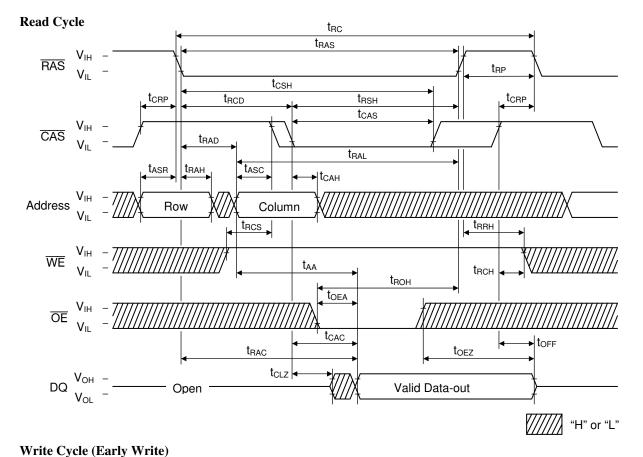

| Access Time from RAS                                     | t <sub>RAC</sub>  | —    | 60               | ns   | 4, 5, 6 |

| Access Time from CAS                                     | tCAC              | —    | 15               | ns   | 4, 5    |

| Access Time from Column Address                          | t <sub>AA</sub>   | —    | 30               | ns   | 4, 6    |

| Access Time from CAS Precharge                           | t <sub>CPA</sub>  | _    | 35               | ns   | 4       |

| Access Time from OE                                      | t <sub>OEA</sub>  | _    | 15               | ns   | 4       |

| Output Low Impedance Time from CAS                       | t <sub>CLZ</sub>  | 0    |                  | ns   | 4       |

| CAS to Data Output Buffer Turn-<br>off Delay Time        | tOFF              | 0    | 15               | ns   | 7       |

| OE to Data Output Buffer Turn-off<br>Delay Time          | <sup>t</sup> OEZ  | 0    | 15               | ns   | 7       |

| Transition Time                                          | tT                | 3    | 50               | ns   | 3       |

| Refresh Period                                           | t <sub>REF</sub>  | —    | 32               | ms   |         |

| RAS Precharge Time                                       | t <sub>RP</sub>   | 40   | —                | ns   |         |

| RAS Pulse Width                                          | t <sub>RAS</sub>  | 60   | 10,000           | ns   |         |

| RAS Pulse Width (Fast Page Mode)                         | t <sub>RASP</sub> | 60   | 100,000          | ns   |         |

| RAS Hold Time                                            | t <sub>RSH</sub>  | 15   | _                | ns   |         |

| $\overline{RAS}$ Hold Time referenced to $\overline{OE}$ | t <sub>ROH</sub>  | 15   |                  | ns   |         |

| CAS Precharge Time<br>(Fast Page Mode)                   | t <sub>CP</sub>   | 10   | _                | ns   |         |

| CAS Pulse Width                                          | tCAS              | 15   | 10,000           | ns   |         |

| CAS Hold Time                                            | t <sub>CSH</sub>  | 60   |                  | ns   |         |

| CAS to RAS Precharge Time                                | t <sub>CRP</sub>  | 5    |                  | ns   |         |

| RAS Hold Time from CAS Precharge                         | t <sub>RHCP</sub> | 35   |                  | ns   |         |

| RAS to CAS Delay Time                                    | t <sub>RCD</sub>  | 20   | 45               | ns   | 5       |

| RAS to Column Address Delay Time                         | t <sub>RAD</sub>  | 15   | 30               | ns   | 6       |

| Row Address Set-up Time                                  | tASR              | 0    | _                | ns   |         |

#### FEDD51V17400F-03

MSM51V17400F

#### AC CHARACTERISTICS (2/2)

| Parameter                                   | Symbol           |      | IV17400<br>-60 | Unit | Note |

|---------------------------------------------|------------------|------|----------------|------|------|

|                                             |                  | Min. | Max.           |      |      |

| Row Address Hold Time                       | t <sub>RAH</sub> | 10   | _              | ns   |      |

| Column Address Set-up Time                  | tASC             | 0    | _              | ns   |      |

| Column Address Hold Time                    | tCAH             | 10   |                | ns   |      |

| Column Address to RAS Lead Time             | t <sub>RAL</sub> | 30   | _              | ns   |      |

| Read Command Set-up Time                    | t <sub>RCS</sub> | 0    | _              | ns   |      |

| Read Command Hold Time                      | t <sub>RCH</sub> | 0    | _              | ns   | 8    |

| Read Command Hold Time referenced to RAS    | t <sub>RRH</sub> | 0    | _              | ns   | 8    |

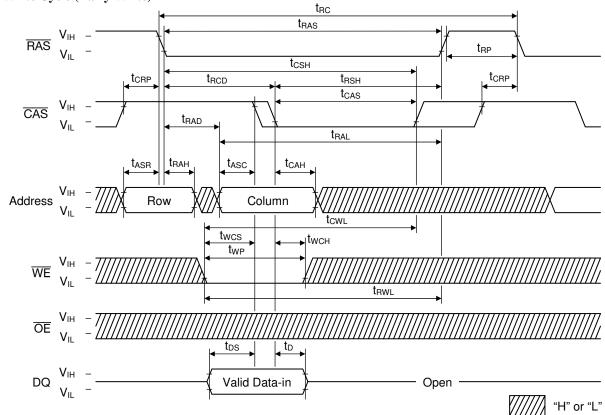

| Write Command Set-up Time                   | twcs             | 0    | _              | ns   | 9    |

| Write Command Hold Time                     | twcн             | 10   | _              | ns   |      |

| Write Command Pulse Width                   | t <sub>WP</sub>  | 10   | —              | ns   |      |

| OE Command Hold Time                        | t <sub>OEH</sub> | 15   | —              | ns   |      |

| Write Command to RAS Lead Time              | t <sub>RWL</sub> | 15   | —              | ns   |      |

| Write Command to CAS Lead Time              | tCWL             | 15   | _              | ns   |      |

| Data-in Set-up Time                         | t <sub>DS</sub>  | 0    | _              | ns   | 10   |

| Data-in Hold Time                           | t <sub>DH</sub>  | 10   | _              | ns   | 10   |

| OE to Data-in Delay Time                    | tOED             | 15   | _              | ns   |      |

| CAS to WE Delay Time                        | tCWD             | 40   | _              | ns   | 9    |

| Column Address to WE Delay Time             | t <sub>AWD</sub> | 55   | _              | ns   | 9    |

| RAS to WE Delay Time                        | t <sub>RWD</sub> | 85   | _              | ns   | 9    |

| CAS Precharge WE Delay Time                 | tCPWD            | 60   | _              | ns   | 9    |

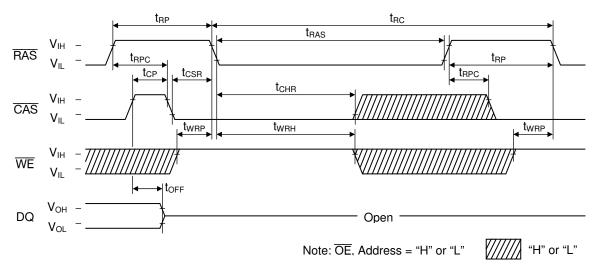

| CAS Active Delay Time from RAS Precharge    | t <sub>RPC</sub> | 5    | _              | ns   |      |

| RAS to CAS Set-up Time<br>(CAS before RAS)  | <sup>t</sup> CSR | 10   | _              | ns   |      |

| RAS to CAS Hold Time<br>CAS before RAS)     | <sup>t</sup> CHR | 10   |                | ns   |      |

| WE to RAS Precharge Time<br>CAS before RAS) | twrp             | 10   | _              | ns   |      |

| WE Hold Time from RAS<br>(CAS before RAS)   | twrh             | 10   |                | ns   |      |

| RAS to WE Set-up Time (Test Mode)           | twrs             | 10   |                | ns   |      |

| RAS to WE Hold Time (Test Mode)             | twтн             | 10   |                | ns   |      |

- Notes: 1. A start-up delay of 200 $\mu$ s is required after power-up, followed by a minimum of eight initialization cycles (RAS-only refresh or CAS before RAS refresh) before proper device operation is achieved.

- 2. The AC characteristics assume  $t_T = 5ns$ .

- 3.  $V_{IH}$  (Min.) and  $V_{IL}$  (Max.) are reference levels for measuring input timing signals. Transition times (t<sub>T</sub>) are measured between  $V_{IH}$  and  $V_{IL}$ .

- 4. This parameter is measured with a load circuit equivalent to 1TTL load and 100pF.

- 5. Operation within the  $t_{RCD}$  (Max.) limit ensures that  $t_{RAC}$  (Max.) can be met.  $t_{RCD}$  (Max.) is specified as a reference point only. If  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (Max.) limit, then the access time is controlled by  $t_{CAC}$ .

- 6. Operation within the  $t_{RAD}$  (Max.) limit ensures that  $t_{RAC}$  (Max.) can be met.  $t_{RAD}$  (Max.) is specified as a reference point only. If  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (Max.) limit, then the access time is controlled by  $t_{AA}$ .

- 7. t<sub>OFF</sub> (Max.) and t<sub>OEZ</sub> (Max.) define the time at which the output achieved the open circuit condition and are not referenced to output voltage levels.

- 8.  $t_{RCH}$  or  $t_{RRH}$  must be satisfied for a read cycle.

- 9.  $t_{WCS}$ ,  $t_{CWD}$ ,  $t_{RWD}$ ,  $t_{AWD}$  and  $t_{CPWD}$  are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If  $t_{WCS} \ge t_{WCS}$  (Min.), then the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If  $t_{CWD} \ge t_{CWD}$  (Min.),  $t_{RWD} \ge t_{RWD}$ (Min.),  $t_{AWD} \ge t_{AWD}$  (Min.) and  $t_{CPWD} \ge t_{CPWD}$  (Min.), then the cycle is a read modify write cycle and data out will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, then the condition of the data out (at access time) is indeterminate.

- 10. These parameters are referenced to the  $\overline{CAS}$ , leading edges in an early write cycle, and to the  $\overline{WE}$  leading edge in an  $\overline{OE}$  control write cycle, or a read modify write cycle.

- 11. The test mode is initiated by performing a  $\overline{WE}$  and  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle. This mode is latched and remains in effect until the exit cycle is generated. In a test CA9 and CA10 are not used and each DQ pin now access 4-bit locations. Since all 4 DQ pins are used, a total 16 data bits can be written in parallel into the memory array. In a read cycle, if 4 data bits are equal, the DQ pin will indicate a high level. If the 4 data bits are not equal, the DQ pin will indicate a low level. The test mode is cleared and the memory device returned to its normal operating state by performing a  $\overline{RAS}$ -only refresh cycle or a  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle.

- 12. In a test mode read cycle, the value of access time parameter is delayed for 5ns for the specified value. These parameters should be specified in test mode cycle by adding the above value to the specified value in this data sheet.

#### MSM51V17400F

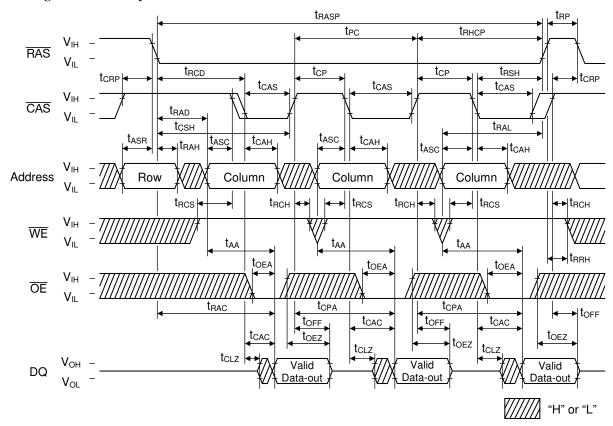

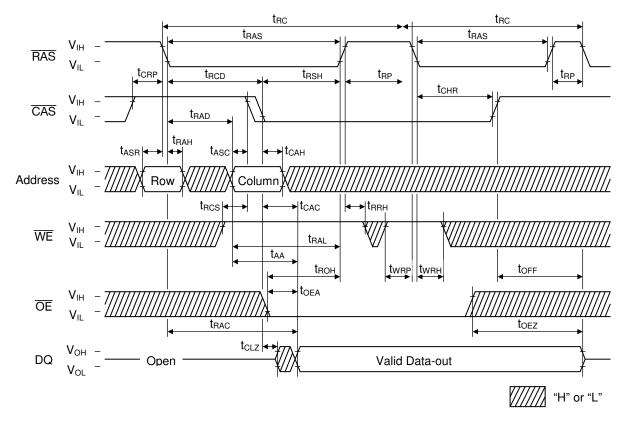

#### TIMING CHART

MSM51V17400F

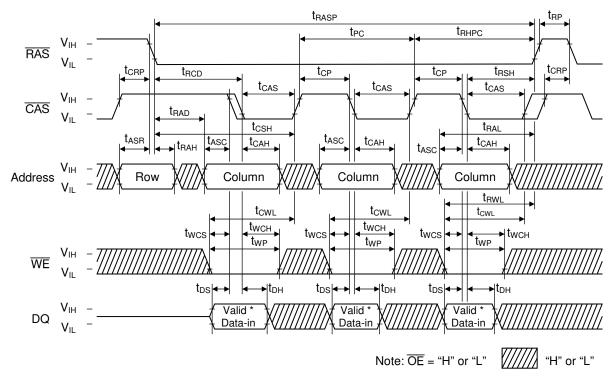

#### **Read Modify Write Cycle**

MSM51V17400F

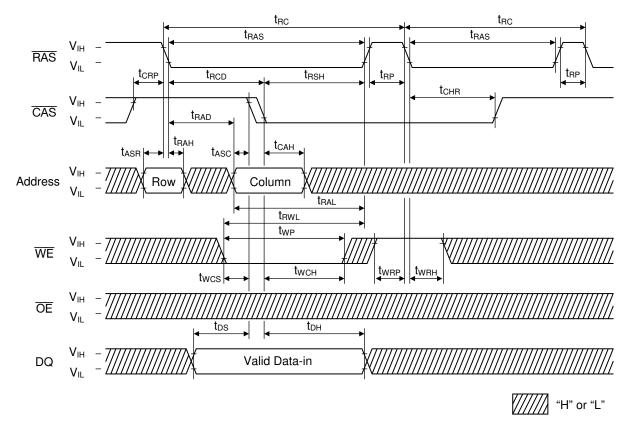

Fast Page Mode Read Cycle

Fast Page Mode Write Cycle (Early Write)

MSM51V17400F

Fast Page Mode Read Modify Write Cycle

MSM51V17400F

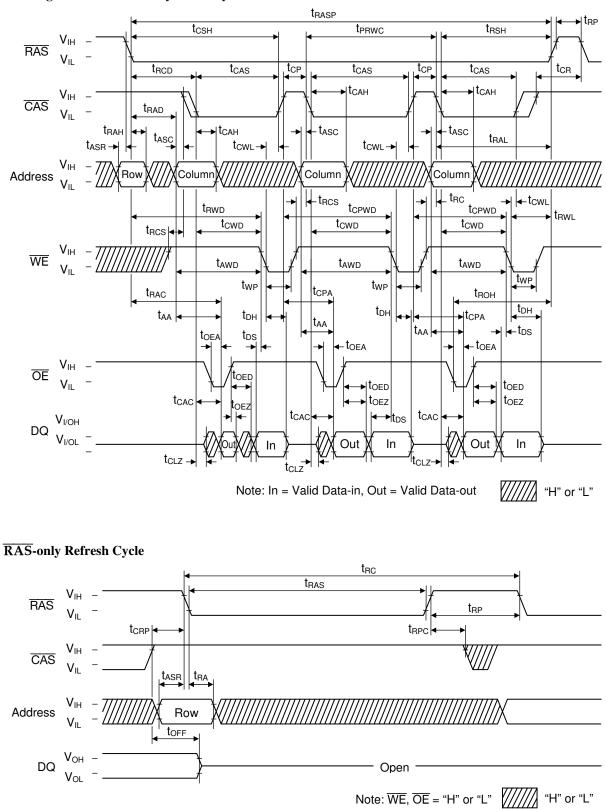

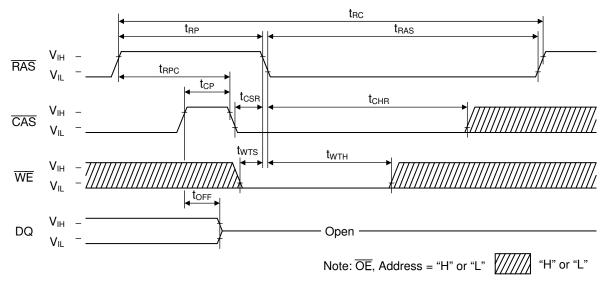

#### **CAS** before **RAS** Refresh Cycle

#### Hidden Refresh Read Cycle

FEDD51V17400F-03

MSM51V17400F

#### Hidden Refresh Write Cycle

#### **Test Mode-in Cycle**

#### MSM51V17400F

#### **REVISION HISTORY**

| Document         | Document .    |                     | ge                 |                                                                                |

|------------------|---------------|---------------------|--------------------|--------------------------------------------------------------------------------|

| No.              | Date          | Previous<br>Edition | Current<br>Edition | Description                                                                    |

| FEDD51V17400F-01 | Mar.23, 2004  | _                   | _                  | Final edition 1 from FEDD5117400F-04                                           |

| FEDD51V17400F-02 | Feb.01, 2012  | 1,2<br>1<br>3       | 1,2<br>1<br>-      | Deleted SOJ26/24<br>Changed pb-free device name<br>Deleted Block diagram       |

| FEDD51V17400F-03 | Nov. 27, 2014 | 1                   | 1                  | Changed package code(Cu frame)<br>Added ROHM logo mark<br>Changed company Logo |

#### **NOTES**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2004 – 2014 LAPIS Semiconductor Co., Ltd.

### LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/