Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Addendum Automotive DDR3L SDRAM**

# MT41K128M8 - 16 Meg x 8 x 8 banks MT41K64M16 - 8 Meg x 16 x 8 banks

# **Description**

This addendum provides information to add Automotive Ultra-high Temperature (AUT) option for the data sheet. This addendum does not provide detailed information about the device. Refer to the data sheet (1Gb: x8, x16 Automotive DDR3L SDRAM, Rev. B 2/15 EN) for a complete description of device functionality, operating modes, and specifications for the same Micron part number products. The 1.35V DDR3L SDRAM device is a low-voltage version of the 1.5V DDR3 SDRAM device. Refer to the DDR3 (1.5V) SDRAM data sheet specifications when running in 1.5V compatible mode.

#### **Features**

- $V_{DD} = V_{DDO} = 1.35V (1.283V \text{ to } 1.45V)$

- Backward compatible to  $V_{DD} = V_{DDO} = 1.5V \pm 0.075V$

- · Differential bidirectional data strobe

- 8*n*-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- · 8 internal banks

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS (READ) latency (CL)

- Programmable CAS additive latency (AL)

- Programmable CAS (WRITE) latency (CWL)

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- · Self refresh mode

- T<sub>C</sub> of -40°C to 125°C

- 64ms, 8192-cycle refresh at –40°C to 85°C

- 32ms at 85°C to 105°C

- 16ms at 105°C to 115°C

- 8ms at 115°C to 125°C

- Self refresh temperature (SRT)

- Automatic self refresh (ASR)

- · Write leveling

- Multipurpose register

- · Output driver calibration

- AEC-Q100

- PPAP submission

- 8D response time

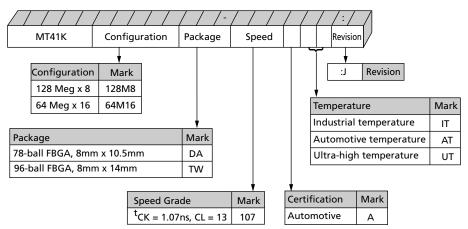

| Options <sup>1</sup>                                                                    | Marking |

|-----------------------------------------------------------------------------------------|---------|

| • Configuration                                                                         | _       |

| - 128 Meg x 8                                                                           | 128M8   |

| - 64 Meg x 16                                                                           | 64M16   |

| • FBGA package (Pb-free) – x8                                                           |         |

| <ul> <li>78-ball FBGA (8mm x 10.5mm)</li> </ul>                                         | DA      |

| • FBGA package (Pb-free) – x16                                                          |         |

| <ul> <li>96-ball FBGA (8mm x 14mm)</li> </ul>                                           | TW      |

| • Timing – cycle time                                                                   |         |

| - 1.07ns @ CL = 13 (DDR3-1866)                                                          | -107    |

| <ul> <li>Product certification</li> </ul>                                               |         |

| <ul><li>Automotive</li></ul>                                                            | A       |

| <ul> <li>Operating temperature</li> </ul>                                               |         |

| - Industrial ( $-40^{\circ}$ C $\leq$ T <sub>C</sub> $\leq$ +95 $^{\circ}$ C)           | IT      |

| - Automotive ( $-40^{\circ}\text{C} \le \text{T}_{\text{C}} \le +105^{\circ}\text{C}$ ) | AT      |

| - Ultra-high $(-40^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C})^3$ | UT      |

| • Revision                                                                              | :J      |

Notes

- 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

- 2. The datasheet does not support ×4 mode even though ×4 mode description exists in the following sections.

- 3. The UT option use based on automotive usage model. Contact Micron sales representative for further information.

#### **Table 1: Key Timing Parameters**

| Speed Grade | Data Rate (MT/s) | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns) |

|-------------|------------------|---------------------------------------------|-----------------------|----------------------|---------|

| -107        | 1866             | 13-13-13                                    | 13.91                 | 13.91                | 13.91   |

**Table 2: Addressing**

| Parameter      | 128 Meg x 8          | 64 Meg x 16          |

|----------------|----------------------|----------------------|

| Configuration  | 16 Meg x 8 x 8 banks | 8 Meg x 16 x 8 banks |

| Refresh count  | 8K                   | 8K                   |

| Row address    | 16K A[13:0]          | 8K A[12:0]           |

| Bank address   | 8 BA[2:0]            | 8 BA[2:0]            |

| Column address | 1K A[9:0]            | 1K A[9:0]            |

| Page Size      | 1KB                  | 2KB                  |

**Figure 1: DDR3L Part Numbers**

Example Part Number: MT41K64M16DA-107AAT:J

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

# 1Gb: x8, x16 Automotive DDR3L SDRAM Addendum Functional Description

# **Functional Description**

DDR3 SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is an 8*n*-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR3 SDRAM effectively consists of a single 8*n*-bit-wide, four-clock-cycle data transfer at the internal DRAM core and eight corresponding *n*-bit-wide, one-half-clock-cycle data transfers at the I/O pins.

The differential data strobe (DQS, DQS#) is transmitted externally, along with data, for use in data capture at the DDR3 SDRAM input receiver. DQS is center-aligned with data for WRITEs. The read data is transmitted by the DDR3 SDRAM and edge-aligned to the data strobes.

The DDR3 SDRAM operates from a differential clock (CK and CK#). The crossing of CK going HIGH and CK# going LOW is referred to as the positive edge of CK. Control, command, and address signals are registered at every positive edge of CK. Input data is registered on the first rising edge of DQS after the WRITE preamble, and output data is referenced on the first rising edge of DQS after the READ preamble.

Read and write accesses to the DDR3 SDRAM are burst-oriented. Accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE commands are used to select the bank and the starting column location for the burst access.

The device uses a READ and WRITE BL8 and BC4. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard DDR SDRAM, the pipelined, multibank architecture of DDR3 SDRAM allows for concurrent operation, thereby providing high bandwidth by hiding row precharge and activation time.

A self refresh mode is provided, along with a power-saving, power-down mode.

#### **Industrial Temperature**

The industrial temperature (IT) device requires that the case temperature not exceed  $-40^{\circ}\text{C}$  or 95°C. JEDEC specifications require the refresh rate to double when  $T_{C}$  exceeds 85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance and the input/output impedance must be derated when  $T_{C}$  is <0°C or >85°C.

# **Automotive Temperature**

The automotive temperature (AT) device requires that the case temperature not exceed  $-40^{\circ}\text{C}$  or  $105^{\circ}\text{C}$ . JEDEC specifications require the refresh rate to double when  $T_{\text{C}}$  exceeds 85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance and the input/output impedance must be derated when  $T_{\text{C}}$  is <0°C or >85°C.

# 1Gb: x8, x16 Automotive DDR3L SDRAM Addendum Functional Description

#### **Utra-high Temperature**

The Utra-high temperature (UT) device requires that the case temperature not exceed  $-40^{\circ}\text{C}$  or  $125^{\circ}\text{C}$ . JEDEC specifications require the refresh rate to double when  $T_{C}$  exceeds  $85^{\circ}\text{C}$ ; this also requires use of the high-temperature auto refresh option. When  $T_{C}>+85^{\circ}\text{C}$ , the refresh rate must be increased to 2X, when  $T_{C}>+105^{\circ}\text{C}$ , the refresh rate must be increased to 4X and when  $T_{C}>+115^{\circ}\text{C}$ , the refresh rate must be increased to 8X. Self-refresh mode is not available for  $T_{C}>+105^{\circ}\text{C}$ . Additionally, ODT resistance and the input/output impedance must be derated when  $T_{C}$  is <0°C or >85°C.

#### **General Notes**

- The functionality and the timing specifications discussed in this data sheet are for the DLL enable mode of operation (normal operation).

- Throughout this data sheet, various figures and text refer to DQs as "DQ." DQ is to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

- The terms "DQS" and "CK" found throughout this data sheet are to be interpreted as DQS, DQS# and CK, CK# respectively, unless specifically stated otherwise.

- Complete functionality may be described throughout the document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- Any specific requirement takes precedence over a general statement.

- Any functionality not specifically stated is considered undefined, illegal, and not supported, and can result in unknown operation.

- Row addressing is denoted as A[*n*:0]. *For example,* 1Gb: *n* = 12 (x16); 1Gb: *n* = 13 (x4, x8); 2Gb: *n* = 13 (x16) and 2Gb: *n* = 14 (x4, x8); 4Gb: *n* = 14 (x16); and 4Gb: *n* = 15 (x4, x8).

- Dynamic ODT has a special use case: when DDR3 devices are architected for use in a single rank memory array, the ODT ball can be wired HIGH rather than routed. Refer to the Dynamic ODT Special Use Case section.

- A x16 device's DQ bus is comprised of two bytes. If only one of the bytes needs to be used, use the lower byte for data transfers and terminate the upper byte as noted:

- Connect UDQS to ground via  $1k\Omega^*$  resistor.

- Connect UDQS# to  $V_{DD}$  via  $1k\Omega^*$  resistor.

- Connect UDM to  $V_{DD}$  via  $1k\Omega^*$  resistor.

- Connect DQ[15:8] individually to either  $V_{SS}$ ,  $V_{DD}$ , or  $V_{REF}$  via  $1k\Omega$  resistors,\* or float DQ[15:8].

\*If ODT is used,  $1k\Omega$  resistor should be changed to 4x that of the selected ODT.

#### 1Gb: x8, x16 Automotive DDR3L SDRAM Addendum Electrical Specifications

# **Electrical Specifications**

#### **Absolute Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 3: Absolute Maximum Ratings**

| Symbol                             | Parameter                                                   | Min  | Мах   | Unit | Notes |

|------------------------------------|-------------------------------------------------------------|------|-------|------|-------|

| $V_{DD}$                           | V <sub>DD</sub> supply voltage relative to V <sub>SS</sub>  | -0.4 | 1.975 | V    | 1     |

| $V_{\rm DDQ}$                      | V <sub>DD</sub> supply voltage relative to V <sub>SSQ</sub> | -0.4 | 1.975 | V    |       |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub>              | -0.4 | 1.975 | V    |       |

| T <sub>C</sub>                     | Operating case temperature – Commercial                     | 0    | 95    | °C   | 2, 3  |

|                                    | Operating case temperature – Industrial                     | -40  | 95    | °C   | 2, 3  |

|                                    | Operating case temperature – Automotive                     | -40  | 105   | °C   | 2, 3  |

|                                    | Operating case temperature – Ultra-high                     | -40  | 125   | °C   | 2, 3  |

| T <sub>STG</sub>                   | Storage temperature                                         | -55  | 150   | °C   |       |

Notes

- 1.  $V_{DD}$  and  $V_{DDQ}$  must be within 300mV of each other at all times, and  $V_{REF}$  must not be greater than  $0.6 \times V_{DDQ}$ . When  $V_{DD}$  and  $V_{DDQ}$  are <500mV,  $V_{REF}$  can be ≤300mV.

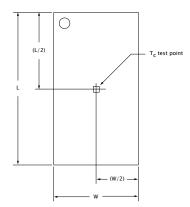

- 2. MAX operating case temperature. T<sub>C</sub> is measured in the center of the package.

- 3. Device functionality is not guaranteed if the DRAM device exceeds the maximum T<sub>C</sub> during operation.

- 4. Ultra-high temperature use based on automotive usage model. Please contact Micron sales representative if you have questions.

#### **Input/Output Capacitance**

#### **Table 4: DDR3L Input/Output Capacitance**

Note 1 applies to the entire table;

| Capacitance                              |                          | DDR3L-1866 |      |      |       |

|------------------------------------------|--------------------------|------------|------|------|-------|

| Parameters                               | Symbol                   | Min        | Max  | Unit | Notes |

| CK and CK#                               | C <sub>CK</sub>          | 0.8        | 1.3  | pF   |       |

| ΔC: CK to CK#                            | C <sub>DCK</sub>         | 0.0        | 0.15 | pF   |       |

| Single-end I/O: DQ, DM                   | C <sub>IO</sub>          | 1.4        | 2.1  | pF   | 2     |

| Differential I/O: DQS, DQS#, TDQS, TDQS# | C <sub>IO</sub>          | 1.4        | 2.1  | pF   | 3     |

| ΔC: DQS to DQS#, TDQS, TDQS#             | C <sub>DDQS</sub>        | 0.0        | 0.15 | pF   | 3     |

| ΔC: DQ to DQS                            | C <sub>DIO</sub>         | -0.5       | 0.3  | pF   | 4     |

| Inputs (CTRL, CMD, ADDR)                 | C <sub>I</sub>           | 0.75       | 1.2  | pF   | 5     |

| ΔC: CTRL to CK                           | C <sub>DI_CTRL</sub>     | -0.4       | 0.2  | pF   | 6     |

| ΔC: CMD_ADDR to CK                       | C <sub>DI_CMD_ADDR</sub> | -0.4       | 0.4  | pF   | 7     |

#### **Table 4: DDR3L Input/Output Capacitance (Continued)**

Note 1 applies to the entire table;

| Capacitance           |                 | DDR3L-1866 |     |      |       |

|-----------------------|-----------------|------------|-----|------|-------|

| Parameters            | Symbol          | Min        | Max | Unit | Notes |

| ZQ pin capacitance    | C <sub>ZQ</sub> | _          | 3.0 | pF   |       |

| Reset pin capacitance | C <sub>RE</sub> | -          | 3.0 | pF   |       |

- Notes: 1.  $V_{DD} = 1.35V$  (1.283–1.45V),  $V_{DDQ} = V_{DD}$ ,  $V_{REF} = V_{SS}$ , f = 100 MHz,  $T_C = 25$ °C.  $V_{OUT(DC)} = 0.5$  $\times$  V<sub>DDO</sub>, V<sub>OUT</sub> = 0.1V (peak-to-peak).

- 2. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 3. Includes TDQS, TDQS#. CDDQS is for DQS vs. DQS# and TDQS vs. TDQS# separately.

- 4.  $C_{DIO} = C_{IO(DQ)} 0.5 \times (C_{IO(DQS)} + C_{IO(DQS\#)}).$

- 5. Excludes CK, CK#; CTRL = ODT, CS#, and CKE; CMD = RAS#, CAS#, and WE#; ADDR = A[n:0], BA[2:0].

- 6.  $C_{DI CTRL} = C_{I(CTRL)} 0.5 \times (C_{CK(CK)} + C_{CK(CK\#)}).$

- 7.  $C_{DI\_CMD\_ADDR} = C_{I(CMD\_ADDR)} 0.5 \times (C_{CK(CK)} + C_{CK(CK\#)})$ .

#### **Thermal Characteristics**

#### **Table 5: Thermal Characteristics**

| Parameter/Condition                        |              | Value       | Units | Symbol         | Notes         |

|--------------------------------------------|--------------|-------------|-------|----------------|---------------|

| Operating case temperature –<br>Commercial |              | 0 to +85    | °C    | T <sub>C</sub> | 1, 2, 3       |

| Operating case temperature –<br>Industrial |              | -40 to +95  | °C    | T <sub>C</sub> | 1, 2, 3, 4    |

| Operating case temperature –<br>Automotive |              | -40 to +105 | °C    | T <sub>C</sub> | 1, 2, 3, 4    |

| Operating case temperature –<br>Ultra-high |              | -40 to +125 | °C    | T <sub>C</sub> | 1, 2, 3, 4, 6 |

| Junction-to-case (TOP)                     | 78-ball "DA" | 10.1        | °C/W  | ΘJC            | 5             |

|                                            | 96-ball "TW" | 9.4         |       |                |               |

- Notes: 1. MAX operating case temperature.  $T_C$  is measured in the center of the package.

- 2. A thermal solution must be designed to ensure the DRAM device does not exceed the maximum T<sub>C</sub> during operation.

- 3. Device functionality is not guaranteed if the DRAM device exceeds the maximum T<sub>C</sub> during operation.

- 4. If T<sub>C</sub> exceeds 85°C, the DRAM must be refreshed externally at 2x refresh, which is a 3.9µs interval refresh rate. The use of SRT or ASR must be enabled.

- 5. The thermal resistance data is based off of a number of samples from multiple lots and should be viewed as a typical number.

- 6. Ultra-high temperature use based on automotive usage model. Please contact Micron sales representative if you have questions.

**Figure 2: Thermal Measurement Point**

7

# **Electrical Characteristics – IDD Specifications**

**Table 6: IDD Maximum Limits**

|                                                |                           |       | DDR3L |       |            |

|------------------------------------------------|---------------------------|-------|-------|-------|------------|

| Parameter                                      | Symbol                    | Width | -1866 | Units | Notes      |

| Operating current 0: One bank ACTIVATE-to-PRE- | I <sub>DD0</sub>          | x8    | 36    | mA    | 1, 2       |

| CHARGE                                         |                           | x16   | 46    | mA    | 1, 2       |

| Operating current 1: One bank ACTIVATE-to-     | I <sub>DD1</sub>          | х8    | 47    | mA    | 1, 2       |

| READ-to-PRECHARGE                              |                           | x16   | 63    | mA    | 1, 2       |

| Precharge power-down current: Slow exit        | I <sub>DD2P0</sub> (slow) | All   | 12    | mA    | 1, 2, 6    |

| Precharge power-down current: Fast exit        | I <sub>DD2P1</sub> (fast) | All   | 12    | mA    | 1, 2, 6    |

| Precharge quiet standby                        | I <sub>DD2Q</sub>         | All   | 15    | mA    | 1, 2, 6    |

| Precharge standby current                      | I <sub>DD2N</sub>         | All   | 17    | mA    | 1, 2, 6    |

| Precharge standby ODT current                  | I <sub>DD2NT</sub>        | х8    | 27    | mA    | 1, 2, 6    |

|                                                |                           | x16   | 28    | mA    | 1, 2, 6    |

| Active power-down current                      | I <sub>DD3P</sub>         | All   | 14    | mA    | 1, 2, 6    |

| Active standby current                         | I <sub>DD3N</sub>         | х8    | 26    | mA    | 1, 2, 6    |

|                                                |                           | x16   | 28    | mA    | 1, 2, 6    |

| Burst read operating current                   | I <sub>DD4R</sub>         | х8    | 95    | mA    | 1, 2       |

|                                                |                           | x16   | 135   | mA    | 1, 2       |

| Burst write operating current                  | I <sub>DD4W</sub>         | х8    | 99    | mA    | 1, 2       |

|                                                |                           | x16   | 149   | mA    | 1, 2       |

| Burst refresh current                          | I <sub>DD5B</sub>         | All   | 165   | mA    | 1, 2       |

| Room temperature self refresh                  | I <sub>DD6</sub>          | All   | 12    | mA    | 1, 2, 3, 7 |

| Extended temperature self refresh              | I <sub>DD6ET</sub>        | All   | 14    | mA    | 1, 4, 7    |

| All banks interleaved read current             | I <sub>DD7</sub>          | х8    | 162   | mA    | 1, 2       |

|                                                |                           | x16   | 219   | mA    | 1, 2       |

| Reset current                                  | I <sub>DD8</sub>          | All   | 14    | mA    | 1, 2       |

- Notes: 1.  $T_C = 85$ °C; SRT and ASR are disabled.

- 2. Enabling ASR could increase  $I_{DD}x$  by up to an additional 2mA.

- 3. Restricted to  $T_C$  (MAX) = 85°C.

- 4.  $T_C = 85$ °C; ASR and ODT are disabled; SRT is enabled.

- 5. The I<sub>DD</sub> values must be derated (increased) on IT-option and AT-option devices when operated outside of the range  $0^{\circ}C \le T_C \le +85^{\circ}C$ :

- 5a. When  $T_C < 0^{\circ}C$ :  $I_{DD2P0}$ ,  $I_{DD2P1}$  and  $I_{DD3P}$  must be derated by 4%;  $I_{DD4R}$  and  $I_{DD4W}$  must be derated by 2%; and I<sub>DD6</sub> and I<sub>DD7</sub> must be derated by 7%.

- 5b. When  $T_C > 85^{\circ}C$ :  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5B}$ must be derated by 2%; I<sub>DD2Px</sub> must be derated by 30%.

- 6. The  $I_{DD}$  values must be derated (increased) on UT-option. When  $T_C > +105$ °C:  $I_{DD2p0}$ ,  $I_{DD2p1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3P}$ , and  $I_{DD3N}$  must be derated by 60% from the 85°C specs.

- 7. When  $T_C > 105$ °C, self refresh mode is not available.

# **Electrical Characteristics and AC Operating Conditions**

#### **Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions**

|                             |                                |                               | DDR3L-1866                                                                                                                    |                            |                       |        |

|-----------------------------|--------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|--------|

| Parameter                   | arameter                       |                               | Min                                                                                                                           | Max                        | Unit                  | Notes  |

| Clock Timing                |                                |                               |                                                                                                                               |                            |                       |        |

| Clock period average: DLL   | –40°C ≤ T <sub>C</sub> ≤ 85°C  | tCK (DLL_DIS)                 | 8                                                                                                                             | 7800                       | ns                    | 9, 42  |

| disable mode                | 85°C < T <sub>C</sub> ≤ 95°C   |                               | 8                                                                                                                             | 3900                       | ns                    | 42     |

|                             | 95°C < T <sub>C</sub> ≤ 105°C  |                               | 8                                                                                                                             | 3900                       | ns                    | 42     |

|                             | 105°C < T <sub>C</sub> ≤ 125°C |                               | 8                                                                                                                             | 3900                       | ns                    | 42     |

| Clock period average: DLL   | enable mode                    | <sup>t</sup> CK (AVG)         | •                                                                                                                             | in Tables for<br>e allowed | ns                    | 10, 11 |

| High pulse width average    |                                | tCH (AVG)                     | 0.47                                                                                                                          | 0.53                       | CK                    | 12     |

| Low pulse width average     |                                | <sup>t</sup> CL (AVG)         | 0.47                                                                                                                          | 0.53                       | СК                    | 12     |

| Clock period jitter         | DLL locked                     | <sup>t</sup> JITper           | -60                                                                                                                           | 60                         | ps                    | 13     |

|                             | DLL locking                    | <sup>t</sup> JITper,lck       | -50                                                                                                                           | 50                         | ps                    | 13     |

| Clock absolute period       |                                | <sup>t</sup> CK (ABS)         | MIN = <sup>t</sup> CK (AVG) MIN<br>+ <sup>t</sup> JITper MIN;<br>MAX = <sup>t</sup> CK (AVG) MAX +<br><sup>t</sup> JITper MAX |                            | ps                    |        |

| Clock absolute high pulse v | width                          | tCH (ABS)                     | 0.43                                                                                                                          | _                          | <sup>t</sup> CK (AVG) | 14     |

| Clock absolute low pulse w  | vidth                          | <sup>t</sup> CL (ABS)         | 0.43                                                                                                                          | -                          | <sup>t</sup> CK (AVG) | 15     |

| Cycle-to-cycle jitter       | DLL locked                     | <sup>t</sup> JITcc            | 120                                                                                                                           |                            | ps                    | 16     |

|                             | DLL locking                    | <sup>t</sup> JITcc,lck        | 100                                                                                                                           |                            | ps                    | 16     |

| Cumulative error across     | 2 cycles                       | <sup>t</sup> ERR2per          | -88                                                                                                                           | 88                         | ps                    | 17     |

|                             | 3 cycles                       | <sup>t</sup> ERR3per          | -105                                                                                                                          | 105                        | ps                    | 17     |

|                             | 4 cycles                       | <sup>t</sup> ERR4per          | -117                                                                                                                          | 117                        | ps                    | 17     |

|                             | 5 cycles                       | <sup>t</sup> ERR5per          | -126                                                                                                                          | 126                        | ps                    | 17     |

|                             | 6 cycles                       | <sup>t</sup> ERR6per          | -133                                                                                                                          | 133                        | ps                    | 17     |

|                             | 7 cycles                       | <sup>t</sup> ERR7per          | -139                                                                                                                          | 139                        | ps                    | 17     |

|                             | 8 cycles                       | <sup>t</sup> ERR8per          | -145                                                                                                                          | 145                        | ps                    | 17     |

|                             | 9 cycles                       | <sup>t</sup> ERR9per          | -150                                                                                                                          | 150                        | ps                    | 17     |

|                             | 10 cycles                      | <sup>t</sup> ERR10per         | -154                                                                                                                          | 154                        | ps                    | 17     |

|                             | 11 cycles                      | <sup>t</sup> ERR11per         | -158                                                                                                                          | 158                        | ps                    | 17     |

|                             | 12 cycles                      | <sup>t</sup> ERR12per         | -161                                                                                                                          | 161                        | ps                    | 17     |

|                             | n = 13, 14 49, 50 cycles       | <sup>t</sup> ERR <i>n</i> per | tERRnper MIN = (1 + 0.68In[n]) × tJITper MIN tERRnper MAX = (1 + 0.68In[n]) × tJITper MAX                                     |                            | ps                    | 17     |

**Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                          |                               |                                 | DDR3L-1866 |         |           |            |

|------------------------------------------|-------------------------------|---------------------------------|------------|---------|-----------|------------|

| Parameter                                | arameter                      |                                 | Min        | Max     | Unit      | Notes      |

| Data setup time to DQS,<br>DQS#          | Base (specification) @ 2 V/ns | <sup>t</sup> DS<br>(AC130)      | 70         | -       | ps        | 18, 19     |

|                                          | V <sub>REF</sub> @ 2 V/ns     |                                 | 135        | _       | ps        | 19, 20     |

| Data hold time from DQS,<br>DQS#         | Base (specification) @ 2 V/ns | <sup>t</sup> DH<br>(DC90)       | 75         | -       | ps        | 18, 19     |

|                                          | V <sub>REF</sub> @ 2 V/ns     |                                 | 110        | _       | ps        | 19, 20     |

| Minimum data pulse widtl                 | า                             | <sup>t</sup> DIPW               | 320        | _       | ps        | 41         |

| DQ Output Timing                         | ,                             |                                 |            |         | '         | ļ.         |

| DQS, DQS# to DQ skew, pe                 | er access                     | <sup>t</sup> DQSQ               | _          | 85      | ps        |            |

| DQ output hold time from                 | DQS, DQS#                     | <sup>t</sup> QH                 | 0.38       | _       | tCK (AVG) | 21         |

| DQ Low-Z time from CK, C                 | K#                            | <sup>t</sup> LZDQ               | -390       | 195     | ps        | 22, 23     |

| DQ High-Z time from CK, (                | CK#                           | tHZDQ                           | _          | 195     | ps        | 22, 23     |

| DQ Strobe Input Timing                   | <u>'</u>                      |                                 |            | 1       | 1         |            |

| DQS, DQS# rising to CK, CI               | C# rising                     | <sup>t</sup> DQSS               | -0.27      | 0.27    | CK        | 25         |

| DQS, DQS# differential inp               | out low pulse width           | <sup>t</sup> DQSL               | 0.45       | 0.55    | CK        |            |

| DQS, DQS# differential inp               | out high pulse width          | <sup>t</sup> DQSH               | 0.45       | 0.55    | CK        |            |

| DQS, DQS# falling setup to               | CK, CK# rising                | <sup>t</sup> DSS                | 0.18       | _       | CK        | 25         |

| DQS, DQS# falling hold fro               | om CK, CK# rising             | <sup>t</sup> DSH                | 0.18       | _       | CK        | 25         |

| DQS, DQS# differential Wi                | RITE preamble                 | tWPRE                           | 0.9        | _       | CK        |            |

| DQS, DQS# differential WF                | RITE postamble                | tWPST                           | 0.3        | _       | CK        |            |

| DQ Strobe Output Timir                   | ıg                            |                                 |            |         |           |            |

| DQS, DQS# rising to/from                 | rising CK, CK#                | <sup>t</sup> DQSCK              | -195       | 195     | ps        | 23         |

| DQS, DQS# rising to/from DLL is disabled | rising CK, CK# when           | <sup>t</sup> DQSCK<br>(DLL_DIS) | 1          | 10      | ns        | 26         |

| DQS, DQS# differential ou                | tput high time                | <sup>t</sup> QSH                | 0.40       | _       | CK        | 21         |

| DQS, DQS# differential ou                | tput low time                 | <sup>t</sup> QSL                | 0.40       | _       | CK        | 21         |

| DQS, DQS# Low-Z time (RL                 | 1)                            | <sup>t</sup> LZDQS              | -390       | 195     | ps        | 22, 23     |

| DQS, DQS# High-Z time (R                 | L + BL/2)                     | <sup>t</sup> HZDQS              | _          | 195     | ps        | 22, 23     |

| DQS, DQS# differential RE                | AD preamble                   | <sup>t</sup> RPRE               | 0.9        | Note 24 | CK        | 23, 24     |

| DQS, DQS# differential RE.               | AD postamble                  | <sup>t</sup> RPST               | 0.3        | Note 27 | CK        | 23, 27     |

| Command and Address                      | Timing                        |                                 |            | •       | •         |            |

| DLL locking time                         |                               | <sup>t</sup> DLLK               | 512        | _       | CK        | 28         |

| CTRL, CMD, ADDR                          | Base (specification)          | <sup>t</sup> IS                 | 65         | _       | ps        | 29, 30, 44 |

| setup to CK,CK#                          | V <sub>REF</sub> @ 1 V/ns     | (AC135)                         | 200        | -       | ps        | 20, 30     |

| CTRL, CMD, ADDR                          | Base (specification)          | <sup>t</sup> IS                 | 150        | _       | ps        | 29, 30, 44 |

| setup to CK,CK#                          | V <sub>REF</sub> @ 1 V/ns     | (AC125)                         | 275        | _       | ps        | 20, 30     |

#### **Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                                                         |                                   |                     | DDR3I                                             | L-1866                    |    |            |

|-------------------------------------------------------------------------|-----------------------------------|---------------------|---------------------------------------------------|---------------------------|----|------------|

| Parameter                                                               |                                   |                     | Min                                               | Min Max                   |    | Notes      |

| CTRL, CMD, ADDR hold                                                    |                                   |                     | 110                                               | _                         | ps | 29, 30     |

| from CK,CK#                                                             | V <sub>REF</sub> @ 1 V/ns         | (DC90)              | 200                                               | _                         | ps | 20, 30     |

| Minimum CTRL, CMD, ADD                                                  | R pulse width                     | <sup>t</sup> IPW    | 535                                               | _                         | ps | 41         |

| ACTIVATE to internal READ                                               | or WRITE delay                    | <sup>t</sup> RCD    | See Speed B                                       |                           | ns | 31         |

| PRECHARGE command peri                                                  | od                                | <sup>t</sup> RP     | See Speed B                                       |                           | ns | 31         |

| ACTIVATE-to-PRECHARGE c                                                 | ommand period                     | <sup>t</sup> RAS    | See Speed B                                       | in Tables for<br>AS       | ns | 31, 32     |

| ACTIVATE-to-ACTIVATE con                                                | nmand period                      | <sup>t</sup> RC     | See Speed B                                       |                           | ns | 31, 43     |

| ACTIVATE-to-ACTIVATE minimum command period                             | 1KB page size                     | <sup>t</sup> RRD    | MIN = great<br>5r                                 | er of 4CK or<br>ns        | CK | 31         |

|                                                                         | 2KB page size                     |                     | MIN = great<br>6r                                 |                           | CK | 31         |

| Four ACTIVATE                                                           | 1KB page size                     | <sup>t</sup> FAW    | 27                                                | _                         | ns | 31         |

| windows                                                                 | 2KB page size                     |                     | 35                                                | _                         | ns | 31         |

| Write recovery time                                                     |                                   | <sup>t</sup> WR     | MIN = 15ns; MAX = N/A                             |                           | ns | 31, 32, 33 |

| Delay from start of internal WRITE transaction to internal READ command |                                   | <sup>t</sup> WTR    | MIN = greater of 4CK or<br>7.5ns; MAX = N/A       |                           | CK | 31, 34     |

| READ-to-PRECHARGE time                                                  |                                   | <sup>t</sup> RTP    | MIN = greater of 4CK or<br>7.5ns; MAX = N/A       |                           | CK | 31, 32     |

| CAS#-to-CAS# command de                                                 | lay                               | <sup>t</sup> CCD    | MIN = 4CK; MAX = N/A                              |                           | CK |            |

| Auto precharge write recov                                              | very + precharge time             | <sup>t</sup> DAL    | $MIN = WR + {}^{t}RP/{}^{t}CK (AVG);$ $MAX = N/A$ |                           | CK |            |

| MODE REGISTER SET comm                                                  | and cycle time                    | <sup>t</sup> MRD    | MIN = 4CK;                                        | MAX = N/A                 | CK |            |

| MODE REGISTER SET comm                                                  | and update delay                  | <sup>t</sup> MOD    | MIN = greate<br>15ns; MA                          | er of 12CK or<br>AX = N/A | CK |            |

| MULTIPURPOSE REGISTER R<br>mode register set for multi                  |                                   | <sup>t</sup> MPRR   | MIN = 1CK;                                        | MAX = N/A                 | CK |            |

| Calibration Timing                                                      |                                   |                     |                                                   |                           |    |            |

| ZQCL command: Long cali-<br>bration time                                | POWER-UP and RE-<br>SET operation | <sup>t</sup> ZQinit | MAX<br>MIN = MA<br>640                            | X(512nCK,                 | CK |            |

|                                                                         | Normal operation                  | <sup>t</sup> ZQoper | MAX<br>MIN = MA<br>320                            | X(256nCK,                 | CK |            |

| ZQCS command: Short calibration time                                    |                                   | MIN – M             | MAX = N/A<br>1AX(64nCK, 80n                       | s) <sup>t</sup> 7OCS      | CK |            |

#### **Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                                       |                           |                        | DDR3L-1866                                                    |                              |      |       |

|-------------------------------------------------------|---------------------------|------------------------|---------------------------------------------------------------|------------------------------|------|-------|

| Parameter                                             | rameter                   |                        | Min                                                           | Max                          | Unit | Notes |

| Exit reset from CKE HIG                               | H to a valid command      | <sup>t</sup> XPR       | _                                                             | ter of 5CK or<br>; MAX = N/A | CK   |       |

| Begin power supply ram<br>ble                         | np to power supplies sta- | <sup>t</sup> VDDPR     | MIN = N/A;                                                    | MAX = 200                    | ms   |       |

| RESET# LOW to power s                                 | supplies stable           | <sup>t</sup> RPS       | MIN = 0; I                                                    | MAX = 200                    | ms   |       |

| RESET# LOW to I/O and                                 | R <sub>TT</sub> High-Z    | <sup>t</sup> IOZ       | MIN = N/A                                                     | ; MAX = 20                   | ns   | 35    |

| Refresh Timing                                        |                           |                        |                                                               |                              |      |       |

| REFRESH-to-ACTIVATE o                                 | or REFRESH                | <sup>t</sup> RFC – 1Gb | MIN = 110; N                                                  | ЛАX = 70,200                 | ns   |       |

| command period                                        |                           | <sup>t</sup> RFC – 2Gb | MIN = 160; N                                                  | MAX = 70,200                 | ns   |       |

|                                                       |                           | <sup>t</sup> RFC – 4Gb | MIN = 260; N                                                  | ЛАX = 70,200                 | ns   |       |

|                                                       |                           | <sup>t</sup> RFC – 8Gb | MIN = 350; N                                                  | MAX = 70,200                 | ns   |       |

| Maximum refresh                                       | T <sub>C</sub> ≤ 85°C     | -                      | 64                                                            | (1X)                         | ms   | 36    |

| period                                                | T <sub>C</sub> > 85°C     |                        | 32                                                            | (2X)                         | ms   | 36    |

|                                                       | T <sub>C</sub> > 105°C    |                        | 16 (4X)                                                       |                              | ms   | 36    |

|                                                       | T <sub>C</sub> > 115°C    |                        | 8 (                                                           | 8X)                          | ms   | 36    |

| Maximum average                                       | T <sub>C</sub> ≤ 85°C     | <sup>t</sup> REFI      | 7.8 (64ms/8192)                                               |                              | μs   | 36    |

| periodic refresh                                      | T <sub>C</sub> > 85°C     |                        | 3.9 (32r                                                      | ms/8192)                     | μs   | 36    |

|                                                       | T <sub>C</sub> >105°C     |                        | 1.95 (16ms/8192)                                              |                              | μs   | 36    |

|                                                       | T <sub>C</sub> >115°C     |                        | 0.977 (8                                                      | ms/8192)                     | μs   | 36    |

| Self Refresh Timing <sup>45</sup>                     |                           | <del>'</del>           | 1                                                             | ,                            |      |       |

| Exit self refresh to comm<br>locked DLL               | nands not requiring a     | <sup>t</sup> XS        | MIN = greater of 5CK or<br><sup>†</sup> RFC + 10ns; MAX = N/A |                              | CK   |       |

| Exit self refresh to comn<br>locked DLL               | nands requiring a         | <sup>t</sup> XSDLL     | MIN = <sup>t</sup> DLLK (MIN);<br>MAX = N/A                   |                              | CK   | 28    |

| Minimum CKE low pulse<br>entry to self refresh exit   |                           | <sup>t</sup> CKESR     | $MIN = {}^{t}CKE (MIN) + CK;$ $MAX = N/A$                     |                              | CK   |       |

| Valid clocks after self re<br>down entry              | fresh entry or power-     | <sup>t</sup> CKSRE     | MIN = greater of 5CK or<br>10ns; MAX = N/A                    |                              | CK   |       |

| Valid clocks before self i<br>power-down exit, or res |                           | <sup>t</sup> CKSRX     | MIN = greater of 5CK or<br>10ns; MAX = N/A                    |                              | CK   |       |

| Power-Down Timing                                     |                           |                        |                                                               |                              |      |       |

| CKE MIN pulse width                                   |                           | tCKE (MIN)             | Greater of                                                    | 3CK or 5ns                   | CK   |       |

| Command pass disable of                               | delay                     | <sup>t</sup> CPDED     | MIN = 2;<br>MAX = N/A                                         |                              | CK   |       |

| Power-down entry to po                                | ower-down exit timing     | <sup>t</sup> PD        | $MIN = {}^{t}CKE (MIN);$ $MAX = 9 \times {}^{t}REFI$          |                              | CK   |       |

| Begin power-down peri<br>registered HIGH              | od prior to CKE           | <sup>t</sup> ANPD      | WL -                                                          | - 1CK                        | CK   |       |

#### **Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                                                            |                          |                      | DDR3L-1866                                                                               |          |      |        |

|----------------------------------------------------------------------------|--------------------------|----------------------|------------------------------------------------------------------------------------------|----------|------|--------|

| Parameter                                                                  |                          | Symbol               | Min                                                                                      | Max      | Unit | Notes  |

| Power-down entry period: ODT either synchronous or asynchronous            |                          | PDE                  | Greater of <sup>t</sup> ANPD or <sup>t</sup> RFC -<br>REFRESH command to CKE<br>LOW time |          | CK   |        |

| Power-down exit period: ODT either                                         |                          | PDX                  | <sup>t</sup> ANPD + <sup>t</sup> XPDLL                                                   |          | CK   |        |

| synchronous or asynchrono                                                  |                          |                      |                                                                                          |          |      |        |

| Power-Down Entry Minir                                                     |                          |                      |                                                                                          |          |      |        |

| ACTIVATE command to power-down entry                                       |                          | <sup>t</sup> ACTPDEN | MIN = 2                                                                                  |          | CK   |        |

| PRECHARGE/PRECHARGE ALL command to power-down entry                        |                          | <sup>†</sup> PRPDEN  | MIN = 2                                                                                  |          | CK   |        |

| REFRESH command to power-down entry                                        |                          | <sup>t</sup> REFPDEN | MIN = 2                                                                                  |          | CK   | 37     |

| MRS command to power-do                                                    | own entry                | <sup>t</sup> MRSPDEN | MIN = <sup>t</sup> MOD (MIN)                                                             |          | CK   |        |

| READ/READ with auto precharge command to power-down entry                  |                          | <sup>t</sup> RDPDEN  | MIN = RL + 4 + 1                                                                         |          | CK   |        |

| WRITE command to pow-<br>er-down entry                                     | BL8 (OTF, MRS)<br>BC4OTF | <sup>t</sup> WRPDEN  | MIN = WL + 4 +<br><sup>t</sup> WR/ <sup>t</sup> CK (AVG)                                 |          | CK   |        |

|                                                                            | BC4MRS                   | <sup>t</sup> WRPDEN  | MIN = WL + 2 +<br>tWR/tCK (AVG)                                                          |          | CK   |        |

| WRITE with auto pre-<br>charge command to pow-                             | BL8 (OTF, MRS)<br>BC4OTF | <sup>t</sup> WRAPDEN | MIN = WL + 4 + WR + 1                                                                    |          | CK   |        |

| er-down entry                                                              | BC4MRS                   | tWRAPDEN             | MIN = WL + 2 + WR + 1                                                                    |          | CK   |        |

| Power-Down Exit Timing                                                     |                          |                      | 1                                                                                        |          |      |        |

| DLL on, any valid command, or DLL off to commands not requiring locked DLL |                          | <sup>t</sup> XP      | MIN = greater of 3CK or<br>6ns;<br>MAX = N/A                                             |          | CK   |        |

| Precharge power-down with DLL off to commands requiring a locked DLL       |                          | <sup>t</sup> XPDLL   | MIN = greater of 10CK or<br>24ns; MAX = N/A                                              |          | CK   | 28     |

| ODT Timing                                                                 |                          |                      |                                                                                          |          |      |        |

| $R_{TT}$ synchronous turn-on de                                            | lay                      | ODTL on              | CWL +                                                                                    | AL - 2CK | CK   | 38     |

| R <sub>TT</sub> synchronous turn-off de                                    | elay                     | ODTL off             | CWL + AL - 2CK                                                                           |          | CK   | 40     |

| R <sub>TT</sub> turn-on from ODTL on reference                             |                          | <sup>t</sup> AON     | -195                                                                                     | 195      | ps   | 23, 38 |

| R <sub>TT</sub> turn-off from ODTL off reference                           |                          | <sup>t</sup> AOF     | 0.3                                                                                      | 0.7      | CK   | 39, 40 |

| Asynchronous R <sub>TT</sub> turn-on delay (power-down with DLL off)       |                          | <sup>t</sup> AONPD   | MIN = 2; MAX = 8.5                                                                       |          | ns   | 38     |

| Asynchronous R <sub>TT</sub> turn-off delay (power-down with DLL off)      |                          | <sup>t</sup> AOFPD   | MIN = 2; MAX = 8.5                                                                       |          | ns   | 40     |

| ODT HIGH time with WRITE command and BL8                                   |                          | ODTH8                | MIN = 6; MAX = N/A                                                                       |          | CK   |        |

| ODT HIGH time without WRITE command or with WRITE command and BC4          |                          | ODTH4                | MIN = 4; MAX = N/A                                                                       |          | CK   |        |

| Dynamic ODT Timing                                                         |                          |                      |                                                                                          |          |      | 1      |

#### **Table 7: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

Notes 1-8 apply to the entire table

|                                                                                |                      | DDR3L-1866    |     |      |       |

|--------------------------------------------------------------------------------|----------------------|---------------|-----|------|-------|

| Parameter                                                                      | Symbol               | Min           | Max | Unit | Notes |

| R <sub>TT,nom</sub> -to-R <sub>TT(WR)</sub> change skew                        | ODTLcnw              | WL - 2CK      |     | CK   |       |

| R <sub>TT(WR)</sub> -to-R <sub>TT,nom</sub> change skew - BC4                  | ODTLcwn4             | 4CK + ODTLoff |     | CK   |       |

| R <sub>TT(WR)</sub> -to-R <sub>TT,nom</sub> change skew - BL8                  | ODTLcwn8             | 6CK + ODTLoff |     | CK   |       |

| R <sub>TT</sub> dynamic change skew                                            | <sup>t</sup> ADC     | 0.3           | 0.7 | CK   | 39    |

| Write Leveling Timing                                                          |                      |               |     | •    | •     |

| First DQS, DQS# rising edge                                                    | tWLMRD               | 40            | _   | CK   |       |

| DQS, DQS# delay                                                                | <sup>t</sup> WLDQSEN | 25            | -   | CK   |       |

| Write leveling setup from rising CK, CK# crossing to rising DQS, DQS# crossing | tWLS                 | 140           | -   | ps   |       |

| Write leveling hold from rising DQS, DQS# crossing to rising CK, CK# crossing  | <sup>t</sup> WLH     | 140           | -   | ps   |       |

| Write leveling output delay                                                    | <sup>t</sup> WLO     | 0             | 7.5 | ns   |       |

| Write leveling output error                                                    | <sup>t</sup> WLOE    | 0             | 2   | ns   |       |

Notes:

- 1. AC timing parameters are valid from specified T<sub>C</sub> MIN to T<sub>C</sub> MAX values.

- 2. All voltages are referenced to V<sub>SS</sub>.

- 3. Output timings are only valid for R<sub>ON34</sub> output buffer selection.

- 4. The unit <sup>t</sup>CK (AVG) represents the actual <sup>t</sup>CK (AVG) of the input clock under operation. The unit CK represents one clock cycle of the input clock, counting the actual clock edges.

- 5. AC timing and I<sub>DD</sub> tests may use a V<sub>IL</sub>-to-V<sub>IH</sub> swing of up to 900mV in the test environment, but input timing is still referenced to V<sub>REF</sub> (except <sup>t</sup>IS, <sup>t</sup>IH, <sup>t</sup>DS, and <sup>t</sup>DH use the AC/DC trip points and CK, CK# and DQS, DQS# use their crossing points). The minimum slew rate for the input signals used to test the device is 1 V/ns for single-ended inputs (DQs are at 2V/ns for DDR3-1866 and DDR3-2133) and 2 V/ns for differential inputs in the range between V<sub>II (AC)</sub> and V<sub>IH(AC)</sub>.

- 6. All timings that use time-based values (ns, μs, ms) should use <sup>t</sup>CK (AVG) to determine the correct number of clocks (Table 7 (page 9) uses CK or <sup>t</sup>CK [AVG] interchangeably). In the case of noninteger results, all minimum limits are to be rounded up to the nearest whole integer, and all maximum limits are to be rounded down to the nearest whole integer.

- 7. Strobe or DQSdiff refers to the DQS and DQS# differential crossing point when DQS is the rising edge. Clock or CK refers to the CK and CK# differential crossing point when CK is the rising edge.

- 8. This output load is used for all AC timing (except ODT reference timing) and slew rates. The actual test load may be different. The output signal voltage reference point is V<sub>DDQ</sub>/2 for single-ended signals and the crossing point for differential signals (see Figure 25: Differential Output Signal in the data sheet).

- 9. When operating in DLL disable mode, Micron does not warrant compliance with normal mode timings or functionality.

- 10. The clock's <sup>t</sup>CK (AVG) is the average clock over any 200 consecutive clocks and <sup>t</sup>CK (AVG) MIN is the smallest clock rate allowed, with the exception of a deviation due to clock jitter. Input clock jitter is allowed provided it does not exceed values specified and must be of a random Gaussian distribution in nature.

- 11. Spread spectrum is not included in the jitter specification values. However, the input clock can accommodate spread-spectrum at a sweep rate in the range of 20–60 kHz with an additional 1% of <sup>t</sup>CK (AVG) as a long-term jitter component; however, the spread spectrum may not use a clock rate below <sup>t</sup>CK (AVG) MIN.

- 12. The clock's <sup>t</sup>CH (AVG) and <sup>t</sup>CL (AVG) are the average half clock period over any 200 consecutive clocks and is the smallest clock half period allowed, with the exception of a deviation due to clock jitter. Input clock jitter is allowed provided it does not exceed values specified and must be of a random Gaussian distribution in nature.

- 13. The period jitter (<sup>†</sup>JITper) is the maximum deviation in the clock period from the average or nominal clock. It is allowed in either the positive or negative direction.

- 14. <sup>t</sup>CH (ABS) is the absolute instantaneous clock high pulse width as measured from one rising edge to the following falling edge.

- 15. <sup>t</sup>CL (ABS) is the absolute instantaneous clock low pulse width as measured from one falling edge to the following rising edge.

- 16. The cycle-to-cycle jitter <sup>t</sup>JITcc is the amount the clock period can deviate from one cycle to the next. It is important to keep cycle-to-cycle jitter at a minimum during the DLL locking time.

- 17. The cumulative jitter error  ${}^{t}$ ERRnper, where n is the number of clocks between 2 and 50, is the amount of clock time allowed to accumulate consecutively away from the average clock over n number of clock cycles.

- 18. <sup>t</sup>DS (base) and <sup>t</sup>DH (base) values are for a single-ended 1 V/ns slew rate DQs (DQs are at 2V/ns for DDR3-1866 and DDR3-2133) and 2 V/ns slew rate differential DQS, DQS#; when DQ single-ended slew rate is 2V/ns, the DQS differential slew rate is 4V/ns.

- 19. These parameters are measured from a data signal (DM, DQ0, DQ1, and so forth) transition edge to its respective data strobe signal (DQS, DQS#) crossing.

- 20. The setup and hold times are listed converting the base specification values (to which derating tables apply) to V<sub>REF</sub> when the slew rate is 1 V/ns (DQs are at 2V/ns for DDR3-1866 and DDR3-2133). These values, with a slew rate of 1 V/ns (DQs are at 2V/ns for DDR3-1866 and DDR3-2133), are for reference only.

- 21. When the device is operated with input clock jitter, this parameter needs to be derated by the actual <sup>t</sup>JITper (larger of <sup>t</sup>JITper (MIN) or <sup>t</sup>JITper (MAX) of the input clock (output deratings are relative to the SDRAM input clock).

- 22. Single-ended signal parameter.

- 23. The DRAM output timing is aligned to the nominal or average clock. Most output parameters must be derated by the actual jitter error when input clock jitter is present, even when within specification. This results in each parameter becoming larger. The following parameters are required to be derated by subtracting <sup>†</sup>ERR10per (MAX): <sup>†</sup>DQSCK (MIN), <sup>†</sup>LZDQS (MIN), <sup>†</sup>LZDQ (MIN), and <sup>†</sup>AON (MIN). The following parameters are required to be derated by subtracting <sup>†</sup>ERR10per (MIN): <sup>†</sup>DQSCK (MAX), <sup>†</sup>HZ (MAX), <sup>†</sup>LZDQS (MAX), and <sup>†</sup>AON (MAX). The parameter <sup>†</sup>RPRE (MIN) is derated by subtracting <sup>†</sup>JITper (MAX), while <sup>†</sup>RPRE (MAX) is derated by subtracting <sup>†</sup>JITper (MIN).

- 24. The maximum preamble is bound by <sup>t</sup>LZDQS (MAX).

- 25. These parameters are measured from a data strobe signal (DQS, DQS#) crossing to its respective clock signal (CK, CK#) crossing. The specification values are not affected by the amount of clock jitter applied, as these are relative to the clock signal crossing. These parameters should be met whether clock jitter is present.

- 26. The <sup>t</sup>DQSCK (DLL\_DIS) parameter begins CL + AL 1 cycles after the READ command.

- 27. The maximum postamble is bound by <sup>t</sup>HZDQS (MAX).

- 28. Commands requiring a locked DLL are: READ (and RDAP) and synchronous ODT commands. In addition, after any change of latency <sup>t</sup>XPDLL, timing must be met.

- 29. <sup>t</sup>IS (base) and <sup>t</sup>IH (base) values are for a single-ended 1 V/ns control/command/address slew rate and 2 V/ns CK, CK# differential slew rate.

- 30. These parameters are measured from a command/address signal transition edge to its respective clock (CK, CK#) signal crossing. The specification values are not affected by the amount of clock jitter applied as the setup and hold times are relative to the clock signal crossing that latches the command/address. These parameters should be met whether clock jitter is present.

- 31. For these parameters, the DDR3 SDRAM device supports <sup>t</sup>nPARAM (nCK) = RU(<sup>t</sup>PARAM [ns]/<sup>t</sup>CK[AVG] [ns]), assuming all input clock jitter specifications are satisfied. For example, the device will support <sup>t</sup>nRP (nCK) = RU(<sup>t</sup>RP/<sup>t</sup>CK[AVG]) if all input clock jitter specifications are met. This means that for DDR3-800 6-6-6, of which <sup>t</sup>RP = 5ns, the device will support <sup>t</sup>nRP = RU(<sup>t</sup>RP/<sup>t</sup>CK[AVG]) = 6 as long as the input clock jitter specifications are met. That is, the PRECHARGE command at T0 and the ACTIVATE command at T0 + 6 are valid even if six clocks are less than 15ns due to input clock jitter.

- 32. During READs and WRITEs with auto precharge, the DDR3 SDRAM will hold off the internal PRECHARGE command until <sup>t</sup>RAS (MIN) has been satisfied.

- 33. When operating in DLL disable mode, the greater of 4CK or 15ns is satisfied for <sup>t</sup>WR.

- 34. The start of the write recovery time is defined as follows:

- For BL8 (fixed by MRS or OTF): Rising clock edge four clock cycles after WL

- For BC4 (OTF): Rising clock edge four clock cycles after WL

- For BC4 (fixed by MRS): Rising clock edge two clock cycles after WL

- 35. RESET# should be LOW as soon as power starts to ramp to ensure the outputs are in High-Z. Until RESET# is LOW, the outputs are at risk of driving and could result in excessive current, depending on bus activity.

- 36. The refresh period is 64ms when  $T_C$  is less than or equal to 85°C. This equates to an average refresh rate of 7.8125 $\mu$ s. However, nine REFRESH commands should be asserted at least once every 70.3 $\mu$ s. When  $T_C$  is greater than 85°C, the refresh period is 32ms. When  $T_C$  is greater than 105°C, the refresh period is 16ms. When  $T_C$  is greater than 115°C, the refresh period is 8ms.

- 37. Although CKE is allowed to be registered LOW after a REFRESH command when <sup>t</sup>REFPDEN (MIN) is satisfied, there are cases where additional time such as <sup>t</sup>XPDLL (MIN) is required.

- 38. ODT turn-on time MIN is when the device leaves High-Z and ODT resistance begins to turn on. ODT turn-on time maximum is when the ODT resistance is fully on. The ODT reference load is shown in Figure 19: ODT Timing Reference Load in the data sheet. Designs that were created prior to JEDEC tightening the maximum limit from 9ns to 8.5ns will be allowed to have a 9ns maximum.

- 39. Half-clock output parameters must be derated by the actual <sup>t</sup>ERR10per and <sup>t</sup>JITdty when input clock jitter is present. This results in each parameter becoming larger. The parameters <sup>t</sup>ADC (MIN) and <sup>t</sup>AOF (MIN) are each required to be derated by subtracting both <sup>t</sup>ERR10per (MAX) and <sup>t</sup>JITdty (MAX). The parameters <sup>t</sup>ADC (MAX) and <sup>t</sup>AOF (MAX) are required to be derated by subtracting both <sup>t</sup>ERR10per (MAX) and <sup>t</sup>JITdty (MAX).

- 40. ODT turn-off time minimum is when the device starts to turn off ODT resistance. ODT turn-off time maximum is when the DRAM buffer is in High-Z. The ODT reference load is shown in Figure 19: ODT Timing Reference Load in the data sheet. This output load is used for ODT timings (Figure 26: Reference Output Load for AC Timing and Output Slew Rate in the data sheet).

- 41. Pulse width of a input signal is defined as the width between the first crossing of  $V_{REF(DC)}$  and the consecutive crossing of  $V_{REF(DC)}$ .

- 42. Should the clock rate be larger than <sup>t</sup>RFC (MIN), an AUTO REFRESH command should have at least one NOP command between it and another AUTO REFRESH command. Additionally, if the clock rate is slower than 40ns (25 MHz), all REFRESH commands should be followed by a PRECHARGE ALL command.

#### 1Gb: x8, x16 Automotive DDR3L SDRAM Addendum Extended Temperature Usage

- 43. DRAM devices should be evenly addressed when being accessed. Disproportionate accesses to a particular row address may result in a reduction of REFRESH characteristics or product lifetime.

- 44. When two  $V_{IH(AC)}$  values (and two corresponding  $V_{IL(AC)}$  values) are listed for a specific speed bin, the user may choose either value for the input AC level. Whichever value is used, the associated setup time for that AC level must also be used. Additionally, one  $V_{IH(AC)}$  value may be used for address/command inputs and the other  $V_{IH(AC)}$  value may be used for data inputs.

For example, for DDR3-800, two input AC levels are defined:  $V_{IH(AC175),min}$  and  $V_{IH(AC150),min}$  (corresponding  $V_{IL(AC175),min}$  and  $V_{IL(AC150),min}$ ). For DDR3-800, the address/command inputs must use either  $V_{IH(AC175),min}$  with  $^tIS(AC175)$  of 200ps or  $V_{IH(AC150),min}$  with  $^tIS(AC150)$  of 350ps; independently, the data inputs must use either  $V_{IH(AC175),min}$  with  $^tDS(AC175)$  of 75ps or  $V_{IH(AC150),min}$  with  $^tDS(AC150)$  of 125ps.

45. Self refresh is not available when  $T_C > 105$ °C.

# **Extended Temperature Usage**

Micron's DDR3 SDRAM support the optional extended case temperature ( $T_C$ ) range of 0°C to 125°C. Thus, the SRT and ASR options must be used at a minimum.

The extended temperature range DRAM must be refreshed externally at 2x (double refresh) anytime the case temperature is above 85°C (and does not exceed 105°C), 4x anytime the case temperature is above 105°C (and does not exceed 115°C) and 8x anytime the case temperature is above 115°C (and does not exceed 125°C). However, self refresh mode requires either ASR or SRT to support the extended temperatures between 85°C and 105°C and is not supported for temperatures above 105°C.

**Table 8: Self Refresh Temperature and Auto Self Refresh Description**

| Field   | MR2 Bits                       | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Self Re | Self Refresh Temperature (SRT) |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| SRT     | 7                              | If ASR is disabled (MR2[6] = 0), SRT must be programmed to indicate $T_{OPER}$ during self refresh:<br>*MR2[7] = 0: Normal operating temperature range ( $-40^{\circ}$ C to 85°C)<br>*MR2[7] = 1: Extended operating temperature range ( $-40^{\circ}$ C to 105°C)<br>If ASR is enabled (MR2[7] = 1), SRT must be set to 0, even if the extended temperature range is<br>supported<br>*MR2[7] = 0: SRT is disabled |  |  |  |  |

| Auto S  | Auto Self Refresh (ASR)        |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| ASR     | 6                              | When ASR is enabled, the DRAM automatically provides SELF REFRESH power management functions, (refresh rate for all supported operating temperature values)  * MR2[6] = 1: ASR is enabled (M7 must = 0)  When ASR is not enabled, the SRT bit must be programmed to indicate $T_{OPER}$ during SELF REFRESH operation  * MR2[6] = 0: ASR is disabled; must use manual self refresh temperature (SRT)               |  |  |  |  |

# 1Gb: x8, x16 Automotive DDR3L SDRAM Addendum Extended Temperature Usage

#### **Table 9: Self Refresh Mode Summary**

| MR2[6]<br>(ASR) |   | SELF REFRESH Operation                                                                                                                             | Permitted Operating Temperature<br>Range for Self Refresh Mode |

|-----------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 0               | 0 | Self refresh mode is supported in the normal temperature range                                                                                     | Normal (–40°C to 85°C)                                         |

| 0               | 1 | Self refresh mode is supported in normal and extended temper-<br>ature ranges; When SRT is enabled, it increases self refresh<br>power consumption | Normal and extended (–40°C to 105°C)                           |

| 1               | 0 | Self refresh mode is supported in normal and extended temperature ranges; Self refresh power consumption may be temperature-dependent              | Normal and extended (–40°C to 105°C)                           |