Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# MT90869 Flexible 16 K Digital Switch (F16kDX)

**Data Sheet**

December 2010

**Features**

- 16,384-channel x 16,384-channel non-blocking unidirectional switching. The Backplane and Local inputs and outputs can be combined to form a non-blocking switching matrix with 64 stream inputs and 64 stream outputs

- 8,192-channel x 8,192-channel non-blocking Backplane to Local stream switch

- 8.192-channel x 8.192-channel non-blocking Local to Backplane stream switch

- 8,192-channel x 8,192-channel non-blocking Backplane input to Backplane output switch

- 8,192-channel x 8,192-channel non-blocking Local input to Local output stream switch

- Rate conversion on all data paths, Backplane to Local, Local to Backplane, Backplane to Backplane and Local to Local streams

- Backplane port accepts 32 ST-BUS streams with data rates of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or 16.384 Mb/s in any combination. or a fixed allocation of 16 streams at 32.768 Mb/s

**Ordering Information**

MT90869AG 272 Ball PBGA Trays 272 Ball PBGA\* MT90869AG2 Travs

> \*Pb Free Tin/Silver/Copper -40 to +85°C

\*Note: the package thickness is different than the MT90869AG (see drawing at the end of the data

- Local port accepts 32 ST-BUS streams with data rates of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or 16.384 Mb/s, in any combination

- Per-stream channel and bit delay for Local input streams

- Per-stream channel and bit delay for Backplane input streams

- Per-stream advancement for Local output

- Per-stream advancement for Backplane output streams

- Constant throughput delay for frame integrity

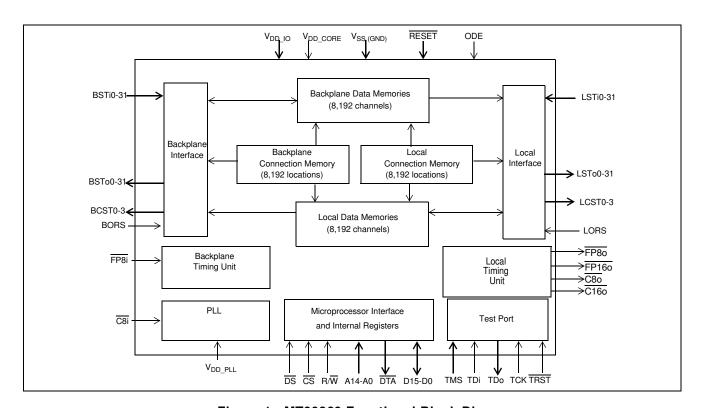

Figure 1 - MT90869 Functional Block Diagram

- Per-channel high impedance output control for Local and Backplane streams

- · Per-channel driven-high output control for local and backplane streams

- · High impedance-control outputs for external drivers on backplane and local port

- · Per-channel message mode for local and backplane output streams

- Connection memory block programming for fast device initialization

- BER testing for local and backplane ports.

- Automatic selection between ST-BUS and GCI-BUS operation

- · Non-multiplexed Motorola microprocessor interface

- Conforms to the mandatory requirements of the IEEE-1149.1 (JTAG) standard

- Memory Built-In-Self-Test (BIST), controlled via microprocessor registers

- 1.8 V core supply voltage

- 3.3 V I/O supply voltage

- 5 V tolerant inputs, outputs and I/Os

- Per stream subrate switching at 4 bit, 2 bit and 1 bit depending on stream data rate

## **Applications**

- Central Office Switches (Class 5)

- Mediation Switches

- Class-independent switches

- · Access Concentrators

- Scalable TDM-Based Architectures

- Digital Loop Carriers

### **Device Overview**

The MT90869 has two data ports, the Backplane and the Local port. The Backplane port has two modes of operation, either 32 input and 32 output streams operated at 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or 16.384 Mb/s, in any combination, or 16 input and 16 output streams operated at 32.768 Mb/s. The Local port has 32 input and 32 output streams operated at 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or 16.384 Mb/s, in any combination.

The MT90869 contains two data memory blocks (Backplane and Local) to provide the following switching path configurations:

- Backplane-to-Local, supporting 8 K x 8 K data switching,

- Local-to-Backplane, supporting 8 K x 8 K data switching,

- Backplane-to-Backplane, supporting 8 K x 8 K data switching.

- Local-to-Local, supporting 8 K x 8 K data switching.

The device contains two connection memory blocks, one for the Backplane output and one for the Local output. Data to be output on the serial streams may come from either of the data memories (Connection Mode) or directly from the connection memory contents (Message Mode).

In Connection Mode the contents of the connection memory defines, for each output stream and channel, the source stream and channel (stored in data memory) to be switched.

In Message Mode, microprocessor data can be written to the connection memory for broadcast on the output streams on a per channel basis. This feature is useful for transferring control and status information to external circuits or other ST-BUS devices.

The device uses a master frame pulse (FP8i) and master clock (C8i) to define the frame boundary and timing for both the backplane port and the local port. The device will automatically detect whether an ST-BUS or a GCI-BUS style frame pulse is being used. There is a two frame delay from the time RESET is de-asserted to the establishment of full switch functionality. During this period the frame format is determined before switching begins.

The device provides FP80, FP160, C80 and C160 outputs to support external devices connected to the local port.

Subrate switching is accomplished by oversampling (i.e., 1 bit switching can be accomplished by sampling a 2 Mb/s stream at 16 Mbps). Refer to MSAN 175.

A non-multiplexed Motorola microprocessor port allows programming of the various device operation modes and switching configurations. The microprocessor port provides access for Register read/write, Connection Memory read/write and Data Memory read-only operations. The port has a 15-bit address bus, 16-bit data bus and 4 control signals. The microprocessor may monitor channel data in the backplane and local data memories.

The mandatory requirements of the IEEE-1149.1 (JTAG) standard are fully supported via a dedicated test port.

The MT90869 is manufactured in a 27 mm x 27 mm body, 1.27 mm ball-pitch, 272-PBGA to JEDEC standard MS-034 BAL-2 Iss. A.

## **Table of Contents**

| 1.0 Bidirectional and Unidirectional Switching Applications             | 17 |

|-------------------------------------------------------------------------|----|

| 1.1 Flexible Configuration                                              |    |

| 2.0 Functional Description                                              | 19 |

| 2.1 Switching Configuration                                             |    |

| 2.1.1 Backplane-to-Local Path                                           |    |

| 2.1.2 Local-to-Backplane Path                                           |    |

| 2.1.3 Backplane-to-Backplane Path                                       |    |

| 2.1.4 Local-to-Local Path                                               |    |

| 2.1.5 Uni-directional Switch.                                           |    |

| 2.2 Port Data Rate Modes and Selection                                  |    |

| 2.2.1 Local Port Rate Selection.                                        |    |

| 2.2.1.1 Local Input Port                                                |    |

| 2.2.1.2 Local Output Port                                               |    |

| 2.2.2 Backplane Port Rate Selection                                     | 21 |

| 2.2.2.1 Backplane Input Port                                            |    |

| 2.2.2.2 Backplane Output Port                                           | 21 |

| 2.3 Backplane Frame Pulse Input and Master Input Clock Timing           | 22 |

| 2.4 Backplane Frame Pulse Input and Local Frame Pulse Output Alignment  | 23 |

| 3.0 Input and Output Offset Programming                                 | 23 |

| 3.1 Input Channel Delay Programming (Backplane and Local Input Streams) |    |

| 3.2 Input Bit Delay Programming (Backplane and Local Input Streams)     |    |

| 3.3 Output Advancement Programming (Backplane and Local Output Streams) |    |

| 3.3.1 Local Output Advancement Programming                              | 26 |

| 3.3.2 Backplane Output Advancement Programming                          | 26 |

| 4.0 Port High Impedance Control                                         | 27 |

| 4.1 Local Port High Impedance Control                                   |    |

| 4.1.1 LORS Šet LOW                                                      |    |

| 4.1.2 LORS Set HIGH                                                     | 28 |

| 4.2 Backplane High Impedance Control                                    | 31 |

| 4.2.2 BORS Set LOW, 32 Mb/s Mode                                        |    |

| 4.2.3 BORS Set HIGH                                                     | 39 |

| 5.0 Data Delay Through the Switching Paths                              | 40 |

| 6.0 Connection Memory Description                                       | 41 |

| 6.1 Local Connection Memory                                             |    |

| 6.2 Backplane Connection Memory                                         |    |

| 6.3 Connection Memory Block Programming                                 |    |

| 6.3.1 Memory Block Programming Procedure                                |    |

| 7.0 Microprocessor Port                                                 | 42 |

| 8.0 Device Power-up, Initialization and Reset                           |    |

| 8.1 Power-Up Sequence                                                   |    |

| 8.2 Initialization                                                      |    |

| 8.3 Reset                                                               |    |

| 9.0 Bit Error Rate Test                                                 |    |

| 10.0 Memory Built-In-Self-Test (BIST) Mode                              |    |

|                                                                         |    |

| 11.0 JTAG Port                                                          |    |

| 11.1 Test Access Port (TAP)                                             |    |

| 11.2 TAP Registers                                                      |    |

| 11.2.1 Test Instruction Register                                        |    |

| 11.2.2.1 The Boundary-Scan Register                                     |    |

| 11.2.2.2 The Boundary-Scarr negister                                    |    |

| 11.2.2.2 The bypass register                                            | 40 |

## MT90869

# **Table of Contents**

|     | 11.2.2.3 The Device Identification Register                    | 46 |

|-----|----------------------------------------------------------------|----|

|     | 11.3 Boundary Scan Description Language (BSDL) File            | 46 |

| 12. | 0 Memory Address Mappings                                      | 46 |

|     | 12.1 Backplane Data Memory Bit Definition                      |    |

|     | 12.2 Local Data Memory Bit Definition                          |    |

|     | 12.3 Local Connection Memory Bit Definition                    |    |

|     | 12.4 Backplane Connection Memory Bit Definition                |    |

|     | 12.5 Internal Register Mappings                                |    |

| 13. | 0 Detailed Register Description                                |    |

|     | 13.1 Control Register (CR)                                     |    |

|     | 13.2 Block Programming Register (BPR)                          | 53 |

|     | 13.3 Bit Error Rate Test Control Register (BERCR)              |    |

|     | 13.4 Local Input Channel Delay Registers (LCDR0 to LCDR31)     | 55 |

|     | 13.4.1 Local Channel Delay Bits 7-0 (LCD7 - LCD0)              |    |

|     | 13.5 Local Input Bit Delay Registers (LIDR0 to LIDR31)         |    |

|     | 13.5.1 Local Input Delay Bits 4-0 (LID4 - LID0)                | 5/ |

|     | 13.6 Backplane Input Channel Delay Registers (BCDR0 to BCDR31) |    |

|     | 13.6.1 Backplane Channel Delay Bits 8-0 (BCDn8 - BCDn0)        |    |

|     | 13.7 Backplane Input Bit Delay Registers (BIDR0 to BIDR31)     |    |

|     | 13.8 Local Output Advancement Registers (LOAR0 to LOAR31)      | 59 |

|     | 13.8.1 Local Output Advancement Bits 1-0 (LOA1-LOA0)           | 61 |

|     | 13.9 Backplane Output Advancement Registers (BOAR0 - 31)       | 61 |

|     | 13.9.1 Backplane Output Advancement Bits 1-0 (BOA1-BOA0).      |    |

|     | 13.10 Local Bit Error Rate (BER) Registers                     |    |

|     | 13.10.1 Local BER Start Send Register (LBSSR)                  |    |

|     | 13.10.2 Local Receive BER Length Register (LRXBLR)             |    |

|     | 13.10.3 Local BER Start Receive Register (LBSRR)               |    |

|     | 13.10.4 Local BER Count Register (LBCR)                        |    |

|     | 13.11 Backplane Bit Error Rate (BER) Registers                 | 64 |

|     | 13.11.1 Backplane BER Start Send Register (BBSSR)              |    |

|     | 13.11.2 Backplane Transmit BER Length Register (BTXBLR)        |    |

|     | 13.11.3 Backplane Receive BER Length Register (BRXBLR)         |    |

|     | 13.11.4 Backplane BER Start Receive Register (BBSRR)           | 65 |

|     | 13.11.5 Backplane BER Count Register (BBCR)                    |    |

|     | 13.12 Local Bit Rate Registers                                 | 65 |

|     | 13.12.1 Local Input Bit Rate Registers (LIBRR0-31)             | 65 |

|     | 13.12.2 Local Output Bit Rate Resisters (LOBRR0-31)            |    |

|     | 13.13 Backplane Bit Rate Registers                             |    |

|     | 13.13.1 Backplane Input Bit Rate Registers (BIBRR0-31)         |    |

|     | 13.13.2 Backplane Output Bit Rate Registers (BOBRR0-31)        |    |

|     | 13.14 Memory BIST Register                                     |    |

|     | 13.15 Revision Control Register                                | 69 |

## MT90869

Data Sheet

# **List of Figures**

| Figure 1 - MT90869 Functional Block Diagram                                                             | 1      |

|---------------------------------------------------------------------------------------------------------|--------|

| Figure 2 - MT90869 PBGA Connections (272 PBGA) Pin Diagram                                              |        |

| (as viewed through top of package)                                                                      |        |

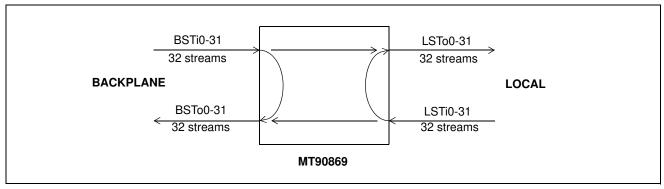

| Figure 3 - 8,192 x 8,192 Channels (16 Mb/s), Bidirectional Switching                                    | 17     |

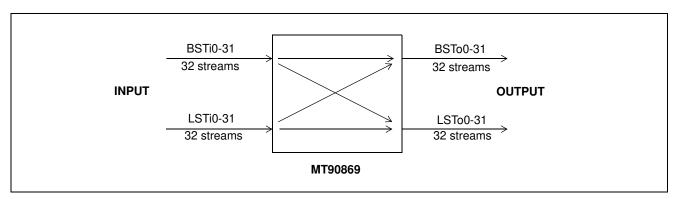

| Figure 4 - 16,384 x 16,384 Channels (16 Mb/s), Unidirectional Switching                                 | 17     |

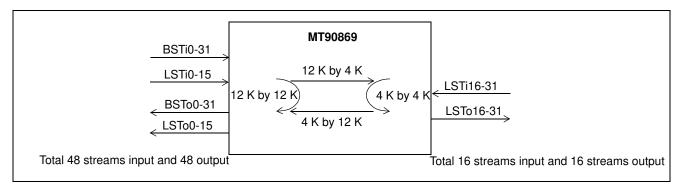

| Figure 5 - 12 K by 4 K Blocking Configuration                                                           | 18     |

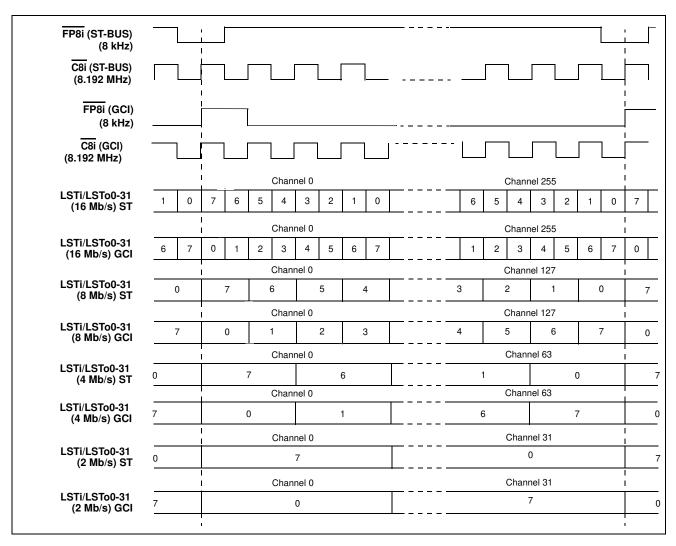

| Figure 6 - Local Port Timing Diagram for 2,4,8 and 16 Mb/s stream rates                                 | 20     |

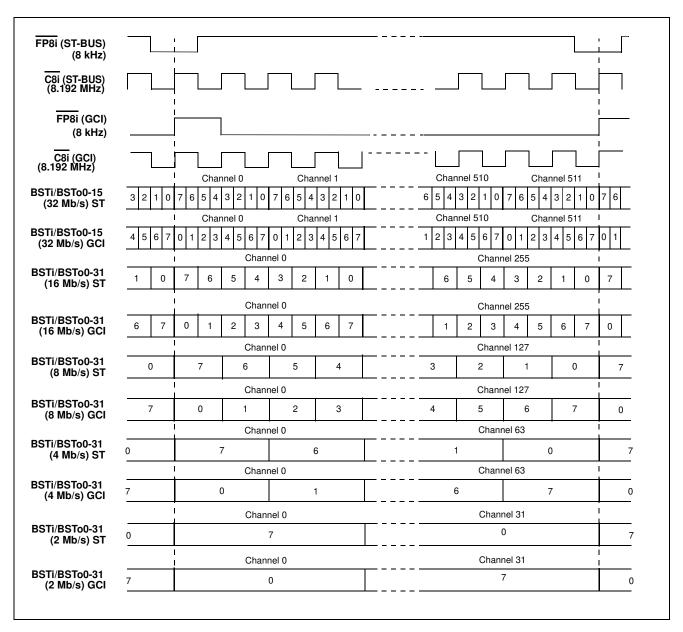

| Figure 7 - Backplane Port Timing Diagram for 2, 4, 8, 16 and 32 Mb/s stream rates                       | 22     |

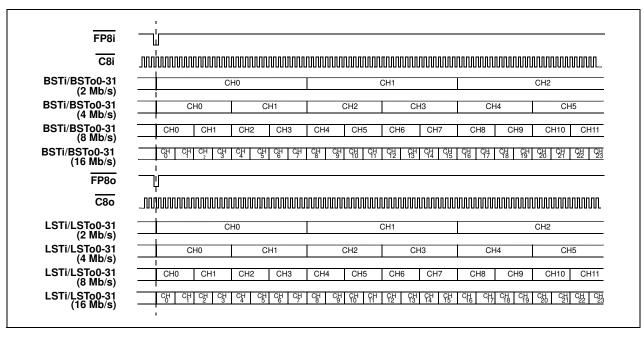

| Figure 8 - Backplane and Local Frame Pulse Alignment for Data Rates of 2 Mb/s, 4 Mb/s, 8 Mb/s and 16 Mb | /s. 23 |

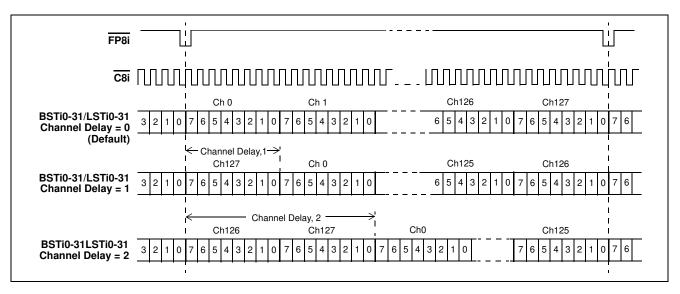

| Figure 9 - Backplane and Local Input Channel Delay Timing Diagram                                       | 24     |

| Figure 10 - Backplane and Local Input Bit Delay Timing Diagram for Data Rate of 16 Mb/s                 | 25     |

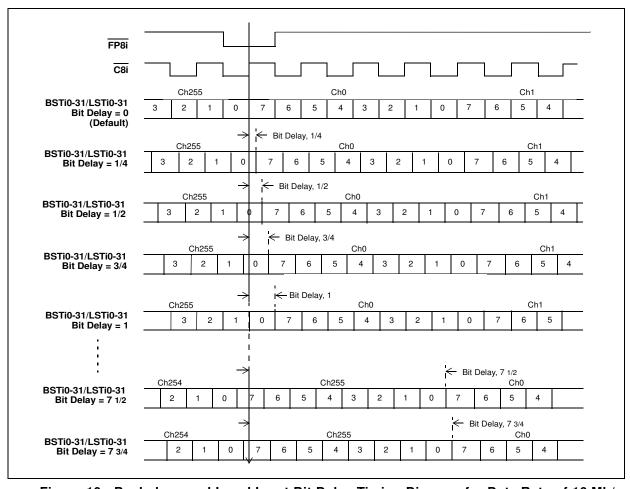

| Figure 11 - Backplane and Local Input Bit Delay Timing Diagram for Data Rate of 8 Mb/s                  | 26     |

| Figure 12 - Backplane and Local Output Advancement Timing diagram for Data Rate of 16 Mb/s              | 27     |

| Figure 13 - Local Port External High Impedance Control Bit Timing (ST-Bus Mode)                         | 31     |

| Figure 14 - Backplane Port External High Impedance Control Bit Timing (Non-32 Mb/s mode)                | 35     |

| Figure 15 - Backplane Port External High Impedance Control Timing (32 Mb/s Mode)                        | 39     |

| Figure 16 - Constant Switch Delay: Examples of different stream rates and routing                       | 40     |

| Figure 17 - Examples of BER transmission channels                                                       | 44     |

| Figure 18 - Frame Boundary Conditions, ST- BUS Operation                                                | 52     |

| Figure 19 - Frame Boundary Conditions, GCI - BUS Operation                                              | 53     |

| Figure 20 - Backplane and Local Clock Timing Diagram for ST-BUS                                         | 73     |

| Figure 21 - Backplane and Local Clock Timing for GCI-BUS                                                | 74     |

| Figure 22 - ST-BUS Backplane Data Timing Diagram (8 Mb/s, 4 Mb/s, 2 Mb/s)                               | 75     |

| Figure 23 - ST-BUS Backplane Data Timing Diagram (32 Mb/s, 16 Mb/s)                                     | 76     |

| Figure 24 - GCI BUS Backplane Data Timing Diagram (8 Mb/s, 4 Mb/s, 2 Mb/s)                              | 77     |

| Figure 25 - GCI BUS Backplane Data Timing Diagram (32 Mb/s, 16 Mb/s)                                    | 78     |

| Figure 26 - ST-BUS Local Timing Diagram (16 Mb/s)                                                       | 79     |

| Figure 27 - ST-BUS Local Data Timing Diagram (8 Mb/s, 4 Mb/s, 2 Mb/s)                                   | 80     |

| Figure 28 - Serial Output and External Control                                                          |        |

| Figure 29 - Output Driver Enable (ODE)                                                                  | 81     |

| Figure 30 - Motorola Non-Multiplexed Bus Timing                                                         | 82     |

## **List of Tables**

| Table 1 - Per-stream Data-Rate Selection: Backplane and Local, Non-32 Mb/s Mode and 32 Mb/s Mode   |    |

|----------------------------------------------------------------------------------------------------|----|

| Table 2 - LCSTo Allocation of Channel Control Bits to the Output Streams                           |    |

| Table 3 - BCSTo Allocation of Channel Control Bits to the Output Streams (Non-32 Mb/s Mode)        |    |

| Table 4 - BCSTo Allocation of Channel Control Bits to the Output Streams (32 Mb/s Mode)            |    |

| Table 5 - Local and Backplane Connection Memory Configuration                                      |    |

| Table 6 - Local Connection Memory in Block Programming Mode                                        |    |

| Table 7 - Backplane Connection Memory in Block Programming Mode                                    |    |

| Table 8 - Address Map for Data and Connection Memory Locations (A14=1)                             | 46 |

| Table 9 - Backplane Data Memory (BDM) Bits                                                         | 47 |

| Table 10 - Local Data Memory (LDM) Bits                                                            |    |

| Table 11 - LCM Bits for Local-to-Local and Backplane (Non-32 Mb/s Mode)-to-Local Switching         | 48 |

| Table 12 - LCM Bits for Backplane(32 Mb/s Mode)-to-Local Switching                                 | 48 |

| Table 13 - BCM Bits for Local-to-Backplane and Backplane-to-Backplane Switching (Non-32 Mb/s Mode) | 49 |

| Table 14 - BCM Bits for Backplane-to-Backplane Switching (32Mb/s mode)                             | 49 |

| Table 15 - Address Map for Register (A14 = 0)                                                      | 50 |

| Table 16 - Control Register Bits                                                                   | 51 |

| Table 17 - Block Programming Register Bits                                                         | 54 |

| Table 18 - Bit Error Rate Test Control Register (BERCR) Bits                                       |    |

| Table 19 - Local Channel Delay Register (LCDRn) Bits                                               |    |

| Table 20 - Local Input Channel Delay Programming Table                                             |    |

| Table 21 - Local Channel Delay Register (LIDRn) Bits                                               |    |

| Table 22 - Local Input Bit Delay Programming Table                                                 | 57 |

| Table 23 - Backplane Channel Delay Register (BCDRn) Bits                                           |    |

| Table 24 - Backplane Input Channel Delay (BCD) Programming Table                                   |    |

| Table 25 - Backplane Input Bit Delay Register (BIDRn) Bits                                         |    |

| Table 26 - Backplane Input Bit Delay Programming Table                                             |    |

| Table 27 - Local Output Advancement Register (LOARn) Bits                                          |    |

| Table 28 - Local Output Advancement (LOAR) Programming Table                                       | 61 |

| Table 29 - Backplane Output Advancement Register (BOAR) Bits                                       | 61 |

| Table 30 - Backplane Output Advancement (BOAR) Programming Table                                   |    |

| Table 31 - Local BER Start Send Register (LBSSR) Bits                                              |    |

| Table 32 - Local BER Length Register (LTXBLR) Bits                                                 | 62 |

| Table 33 - Local Receive BER Length Register (LRXBLR) Bits                                         | 63 |

| Table 34 - Local BER Start Receive Register (LBSRR) Bits                                           | 63 |

| Table 35 - Local BER Count Register (LBCR) Bits                                                    | 63 |

| Table 36 - Backplane BER Start Send Register (BBSSR) Bits                                          | 64 |

| Table 37 - Backplane Transmit BER Length (BTXBLR) Bits                                             | 64 |

| Table 38 - Backplane Receive BER Length (BRXBLR) Bits                                              | 64 |

| Table 39 - Backplane BER Start Receive Register (BBSRR) Bits                                       | 65 |

| Table 40 - Backplane BER Count Register (BBCR) Bits                                                | 65 |

| Table 41 - Local Input Bit Rate Register (LIBRRn) Bits                                             | 65 |

| Table 42 - Local Input Bit Rate (LIBR) Programming Table                                           | 66 |

| Table 43 - Local Output Bit Rate Register (LOBRRn) Bits                                            |    |

| Table 44 - Output Bit Rate (LOBR) Programming Register                                             |    |

| Table 45 - Backplane Input Bit Rate Register (BIBRRn) Bits                                         |    |

| Table 46 - Backplane Input Bit Rate (BIBR) Programming Table                                       |    |

| Table 47 - Backplane Output Bit Rate Register (BOBRRn) Bits                                        |    |

| Table 48 - Backplane Output Bit Rate (BOBRR) Programming Table                                     |    |

|                                                                                                    |    |

MT90869

## **List of Tables**

| Table 49   | lemory BIST Register (MBISTR) Bits   | <br>. 68 |

|------------|--------------------------------------|----------|

| Table 50 - | Revision Control Register (RCR) Bits | <br>. 69 |

## **Changes Summary**

The following table captures the changes from the November 2005 issue.

| Page | ltem            | Change                                                               |

|------|-----------------|----------------------------------------------------------------------|

| 83   | Package Drawing | Changed package Bill of Material with a thinner substrate thickness. |

The following table captures the changes from the December 2002 issue.

| Page | Item                                                                                                           | Change                                                                                                                                                                                                                                                     |

|------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | Pin Description, C8i                                                                                           | The internal frame boundary alignment description is changed from the clock rising or falling edge to rising edge only. Also added description to specify setting the C8IPOL bit in the Control Register to one for clock rising edge alignment operation. |

| 20   | Figure 6, Local Port Timing Diagram for 2,4,8 and 16 Mb/s stream rates                                         | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                        |

| 22   | Figure 7, Backplane Port Timing Diagram for 2, 4, 8, 16 and 32 Mb/s stream rates                               | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                        |

| 22   | Section 2.3. Backplane Frame Pulse Input and Master Input Clock Timing                                         | Removed the falling clock edge frame boundary alignment option.                                                                                                                                                                                            |

| 23   | Figure 8, Backplane and Local Frame<br>Pulse Alignment for Data Rates of 2 Mb/s,<br>4 Mb/s, 8 Mb/s and 16 Mb/s | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                        |

| 24   | Figure 9, Backplane and Local Input<br>Channel Delay Timing Diagram                                            | Changed FPo and C8o to FPi and C8i respectively and showing rising C8i frame boundary active edge.                                                                                                                                                         |

| 25   | Figure 10, Backplane and Local Input Bit<br>Delay Timing Diagram for Data Rate of<br>16 Mb/s                   | Changed FPo and C8o to FPi and C8i respectively and showing rising C8i frame boundary active edge.                                                                                                                                                         |

| 26   | Figure 11, Backplane and Local Input Bit<br>Delay Timing Diagram for Data Rate of<br>8 Mb/s                    | Changed FPo and C8o to FPi and C8i respectively.                                                                                                                                                                                                           |

| 51   | Section 13.1. Control Register (CR) Bit 6, C8IPOL                                                              | Changed description to specify Bit 6, C8IPOL must be set high for rising clock edge frame boundary alignment operation.                                                                                                                                    |

| 52   | Figure 18, Frame Boundary Conditions,<br>ST- BUS Operation                                                     | Removed waveforms showing C8i falling edge frame boundary option.                                                                                                                                                                                          |

| 53   | Figure 19, Frame Boundary Conditions,<br>GCI - BUS Operation                                                   | Removed waveforms showing $\overline{\text{C8i}}$ falling edge frame boundary option.                                                                                                                                                                      |

| Page | Item                                                                                                                                                                                 | Change                                                                                                                                                                                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72   | Backplane and Local Clock Timing: Item 2, Back <u>plane</u> Frame Pulse Setup Time before C8i clock falling edge Item 3, Backplane Frame Pulse Hold Time from C8i clock falling edge | Item 2, <u>Ba</u> ckplane Frame Pulse Setup Time before C8i clock falling edge changed to Backplane Frame Pulse Setup Time before C8i clock rising edge.  Item 3, Backplane Frame Pulse Hold Time from C8i clock falling edge changed to Backplane Frame Pulse Hold Time from C8i clock rising edge. |

| 73   | Figure 20, Backplane and Local Clock<br>Timing Diagram for ST-BUS                                                                                                                    | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                                                                  |

| 75   | Figure 22, ST-BUS Backplane Data<br>Timing Diagram (8 Mb/s, 4 Mb/s, 2 Mb/s)                                                                                                          | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                                                                  |

| 76   | Figure 23, ST-BUS Backplane Data<br>Timing Diagram (32 Mb/s, 16 Mb/s)                                                                                                                | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                                                                  |

| 79   | Figure 26, ST-BUS Local Timing Diagram (16 Mb/s)                                                                                                                                     | Changed C8i frame boundary active edge from falling to rising edge.                                                                                                                                                                                                                                  |

| 80   | Figure 27, ST-BUS Local Data Timing<br>Diagram (8 Mb/s, 4 Mb/s, 2 Mb/s)                                                                                                              | Changed FPo and C8o to FPi and C8i respectively and showing rising C8i frame boundary active edge.                                                                                                                                                                                                   |

| 1        | 1       | 2          | 3            | 4            | 5            | 6          | 7            | 8   | 9   | 10         | 11           | 12           | 13   | 14           | 15         | 16           | 17           | 18           | 19         | 20           |

|----------|---------|------------|--------------|--------------|--------------|------------|--------------|-----|-----|------------|--------------|--------------|------|--------------|------------|--------------|--------------|--------------|------------|--------------|

| G۱       | ND      | IC         | BST<br>o5    | BST<br>o4    | BST<br>o2    | A2         | VDD_<br>CORE | A8  | A11 | A14        | DS           | ODE          | DTA  | TCK          | BCST<br>o1 | LCST<br>o3   | LST<br>o0    | LST<br>o1    | LST<br>o2  | IC           |

| B5       |         | BST<br>o7  | BST<br>o8    | VDD_<br>CORE | BST<br>o1    | IC         | A5           | A7  | A10 | IC         | CS           | VDD_<br>CORE | TDi  | TRST         | BCST<br>o2 | LCST<br>o2   | IC           | LST<br>o3    | LST<br>o4  | LST<br>o5    |

| BS       |         | BST<br>o10 | IC           | BST<br>o3    | BST<br>o0    | A1         | A4           | A6  | IC  | A13        | RW           | RESET        | TDo  | BCST<br>o0   | BCST<br>o3 | LCST<br>o1   | LCST<br>o0   | LST<br>o6    | LST<br>o7  | LST<br>o8    |

| BS<br>01 |         | BST<br>o12 | BST<br>o13   | GND          | A0           | VDD<br>_IO | A3           | GND | A9  | A12        | VDD<br>_IO   | TMS          | GND  | VDD_<br>CORE | VDD<br>_IO | IC           | GND          | LST<br>o9    | LST<br>o10 | LST<br>o11   |

| BS<br>01 |         | BST<br>o15 | BST<br>o16   | BST<br>o17   |              |            |              |     |     |            |              |              |      |              |            |              | LST<br>o12   | LST<br>o13   | LST<br>o14 | LST<br>o15   |

| BS<br>01 |         | BST<br>o19 | BST<br>o20   | VDD<br>_IO   |              |            |              |     |     |            |              |              |      |              |            |              | VDD<br>_IO   | LST<br>o16   | LST<br>o17 | LST<br>o18   |

| BS<br>02 |         | BST<br>o22 | BST<br>o23   | BST<br>o24   |              |            |              |     |     |            |              |              |      |              |            |              | LST<br>o19   | LST<br>o20   | LST<br>o21 | LST<br>o22   |

| BS<br>02 |         | BST<br>o26 | BST<br>o27   | GND          | ·            |            |              |     |     |            |              |              |      |              |            |              | GND          | LST<br>o23   | LST<br>o24 | LST<br>o25   |

| BS<br>02 |         | BST<br>o29 | BST<br>o30   | BST<br>o31   |              |            |              |     | GND | GND        | GND          | GND          |      |              |            |              | LST<br>o26   | LST<br>o27   | LST<br>o28 | LST<br>o29   |

| VD<br>CO |         | BORS       | BST<br>i0    | VDD<br>_IO   |              |            |              |     | GND | GND        | GND          | GND          |      |              |            |              | LST<br>o30   | LST<br>o31   | LORS       | VDD_<br>CORE |

| BS<br>i  |         | BST<br>i2  | BST<br>i3    | BST<br>i4    |              |            |              |     | GND | GND        | GND          | GND          |      |              |            |              | VDD<br>_IO   | LST<br>i0    | LST<br>i1  | LST<br>i2    |

| BS<br>i  | ST<br>5 | BST<br>i6  | BST<br>i7    | BST<br>i8    |              |            |              |     | GND | GND        | GND          | GND          |      |              |            |              | LST<br>i3    | LST<br>i4    | LST<br>i5  | LST<br>i6    |

| BS<br>is |         | BST<br>i10 | VDD_<br>CORE | GND          |              |            |              |     |     |            |              |              | J    |              |            |              | GND          | LST<br>i7    | LST<br>i8  | LST<br>i9    |

| BS<br>i1 |         | BST<br>i12 | BST<br>i13   | BST<br>i14   | •            |            |              |     |     |            |              |              |      |              |            |              | LST<br>i10   | VDD<br>_CORE | LST<br>i11 | LST<br>i12   |

| BS<br>i1 | -       | BST<br>i16 | BST<br>i17   | VDD<br>_IO   |              |            |              |     |     |            |              |              |      |              |            |              | VDD<br>_IO   | LST<br>i13   | LST<br>i14 | LST<br>i15   |

| BS<br>i1 |         | BST<br>i19 | BST<br>i20   | BST<br>i21   |              |            |              |     |     |            |              |              |      |              |            |              | VDD_<br>CORE | LST<br>i16   | LST<br>i17 | LST<br>i18   |

| BS<br>i2 |         | IC         | IC           | GND          | BST<br>i28   | VDD<br>_IO | D10          | GND | D4  | VDD<br>_IO | GND          | VDD<br>_PLL  | GND  | FP8i         | VDD<br>_IO | VDD_<br>CORE | GND          | LST<br>i19   | LST<br>i20 | LST<br>i21   |

| VD<br>CO |         | IC         | IC           | BST<br>i29   | VDD_<br>CORE | D13        | D9           | D7  | D3  | D0         | IC           | IC           | C8o  | FP8o         | IC         | IC           | LST<br>i22   | LST<br>i23   | LST<br>i24 | LST<br>i25   |

| BS<br>i2 |         | BST<br>i24 | BST<br>i25   | BST<br>i30   | D15          | D12        | D8           | D6  | D2  | IC         | IC           | C8i          | C160 | FP16o        | IC         | IC           | IC           | LST<br>i26   | LST<br>i27 | IC           |

| BS<br>i2 |         | BST<br>i27 | IC           | BST<br>i31   | D14          | D11        | VDD_<br>CORE | D5  | D1  | IC         | VDD_<br>CORE | NC           | NC   | VDD_<br>CORE | IC         | IC           | LST<br>i29   | LST<br>i30   | LST<br>i31 | LST<br>i28   |

Figure 2 - MT90869 PBGA Connections (272 PBGA) Pin Diagram (as viewed through top of package)

| Name                  | Package<br>Coordinates                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD_IO</sub>    | D6, D11, D15, F4,<br>F17, K4, L17, R4,<br>R17, U6, U10, U15                                                                                                    | Power Supply for Periphery Circuits: +3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD_CORE</sub>  | A7, B4, B12, D14,<br>K1, K20, N3, P18,<br>T17, U16, V1, V5,<br>Y7, Y11, Y14                                                                                    | Power Supply for Core Logic Circuits: +1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DD_PLL</sub>   | U12                                                                                                                                                            | Power Supply for Analog PLL: +1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS (GND)</sub> | A1, D4, D8, D13,<br>D17, H4, H17, J9,<br>J10, J11, J12, K9,<br>K10, K11, K12, L9,<br>L10, L11, L12, M9,<br>M10, M11, M12, N4,<br>N17, U4, U8, U11,<br>U13, U17 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BSTi0 - 15            | K3, L1, L2, L3, L4,<br>M1, M2, M3, M4, N1,<br>N2, P1, P2, P3, P4,<br>R1                                                                                        | Backplane Serial Input Streams 0 to 15 (5 V Tolerant, Internal pull-down).  In Non-32 Mb/s Mode, these pins accept serial TDM data streams at a data-rate of:- 16.384 Mb/s (with 256 channels per stream), 8.192 Mb/s (with 128 channels per stream), 4.096 Mb/s (with 64 channels per stream), or 2.048 Mb/s (with 32 channels per stream).  The data-rate is independently programmable for each input stream.  In 32 Mb/s Mode, these pins accept serial TDM data streams at a fixed data-rate of 32.768 Mb/s (with 512 channels per stream). |

| BSTi16 - 31           | R2, R3, T1, T2, T3,<br>T4, U1,W1, W2, W3,<br>Y1, Y2, U5, V4, W4,<br>Y4                                                                                         | Backplane Serial Input Streams 16 to 31 (5 V Tolerant, Internal pull-down).  In Non-32 Mb/s Mode, these pins accept serial TDM data streams at a data-rate of:- 16.384 Mb/s (with 256 channels per stream), 8.192 Mb/s (with 128 channels per stream), 4.096 Mb/s (with 64 channels per stream), or 2.048 Mb/s (with 32 channels per stream).  The data-rate is independently programmable for each input stream.  In 32 Mb/s Mode, these pins are unused and should be externally connected to a defined logic level.                           |

| Name        | Package<br>Coordinates                           | Description                                                                                                                                                                                                                              |

|-------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSTo0 - 15  | C5, B5, A5 C4, A4,                               | Backplane Serial Output Streams 0 to 15 (5 V Tolerant, Three-state Outputs).                                                                                                                                                             |

|             | A3, B1, B2, B3, C1,<br>C2, D1, D2, D3, E1,<br>E2 | In Non-32 Mb/s Mode, these pins output serial TDM data streams at a data-rate of:-                                                                                                                                                       |

|             |                                                  | 16.384 Mb/s (with 256 channels per stream),                                                                                                                                                                                              |

|             |                                                  | 8.192 Mb/s (with 128 channels per stream),                                                                                                                                                                                               |

|             |                                                  | 4.096 Mb/s (with 64 channels per stream), or                                                                                                                                                                                             |

|             |                                                  | 2.048 Mb/s (with 32 channels per stream).                                                                                                                                                                                                |

|             |                                                  | The data-rate is independently programmable for each output stream.                                                                                                                                                                      |

|             |                                                  | In 32 Mb/s Mode, these pins output serial TDM data streams at a fixed data-rate of 32.768 Mb/s (with 512 channels per stream).                                                                                                           |

|             |                                                  | Refer to descriptions of the <b>BORS</b> and <b>ODE</b> pins for control of the output High or High-Impedance state.                                                                                                                     |

| BSTo16 - 31 | E3, E4, F1, F2, F3,                              | Backplane Serial Output Streams 16 to 31 (5 V Tolerant Three-state Outputs).                                                                                                                                                             |

|             | G1, G2, G3, G4, H1,<br>H2, H3, J1, J2, J3,<br>J4 | In Non-32 Mb/s Mode, these pins output serial TDM data streams at a data-rate of:-                                                                                                                                                       |

|             | 04                                               | 16.384 Mb/s (with 256 channels per stream),                                                                                                                                                                                              |

|             |                                                  | 8.192 Mb/s (with 128 channels per stream),                                                                                                                                                                                               |

|             |                                                  | 4.096 Mb/s (with 64 channels per stream), or                                                                                                                                                                                             |

|             |                                                  | 2.048 Mb/s (with 32 channels per stream).                                                                                                                                                                                                |

|             |                                                  | The data-rate is independently programmable for each output stream.                                                                                                                                                                      |

|             |                                                  | These pins are unused when the 32 Mb/s Mode is selected.                                                                                                                                                                                 |

|             |                                                  | Refer to descriptions of the <b>BORS</b> and <b>ODE</b> pins for control of the output High or High-Impedance state.                                                                                                                     |

| BCSTo0-3    | C14, A15, B15, C15                               | Backplane Output Channel High Impedance Control (5 V Tolerant Three-state Outputs). Active high output enable which may be used to control external buffering individually for a set of backplane output streams on a per channel basis. |

|             |                                                  | In non-32 Mb/s mode (stream rates 2 Mb/s to 16 Mb/s):                                                                                                                                                                                    |

|             |                                                  | BCSTo0 is the output enable for BSTo[0,4,8,12,16,20,24,28],                                                                                                                                                                              |

|             |                                                  | BCSTo1 is the output enable for BSTo[1,5,9,13,17,21,25,29],                                                                                                                                                                              |

|             |                                                  | BCSTo2 is the output enable for BSTo[2,6,10,14,18,22,26,30],                                                                                                                                                                             |

|             |                                                  | BCSTo3 is the output enable for BSTo[3,7,11,15,19,23,27,31].                                                                                                                                                                             |

|             |                                                  | In 32 Mb/s mode (stream rate 32 Mb/s):                                                                                                                                                                                                   |

|             |                                                  | BCSTo0 is the output enable for BSTo[0,4,8,12],                                                                                                                                                                                          |

|             |                                                  | BCSTo1 is the output enable for BSTo[1,5,9,13],                                                                                                                                                                                          |

|             |                                                  | BCSTo2 is the output enable for BSTo[2,6,10,14],                                                                                                                                                                                         |

|             |                                                  | BCSTo3 is the output enable for BSTo[3,7,11,15].                                                                                                                                                                                         |

|             |                                                  | Refer to descriptions of the <b>BORS</b> and <b>ODE</b> pins for control of the output High or High-Impedance state.                                                                                                                     |

| Name     | Package<br>Coordinates                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP8i     | U14                                                                     | Frame Pulse Input (5 V Tolerant). This pin accepts the Frame Pulse signal. The pulse width may be active for 122 ns or 244 ns at the frame boundary and the Frame Pulse Width bit (FPW) of the Control Register must be set Low (default) for a 122 ns and set High for a the 244 ns pulse condition. The device will automatically detect whether an ST-BUS or GCI-BUS style frame pulse is applied.                                                                                      |

| C8i      | W12                                                                     | Master Clock Input (5 V Tolerant). This pin accepts a 8.192 MHz clock. The internal Frame Boundary is aligned with the rising edge of this clock. This rising edge frame boundary alignment is controlled by the C8IPOL bit in the Control Register as shown in Table 16 on page 51. The C8IPOL bit MUST be set to ONE for the rising edge frame boundary to be detected correctly. Falling C8i edge frame boundary alignment is not supported and should not be used.                     |

| CS       | B11                                                                     | Chip Select (5 V Tolerant). Active low input used by the microprocessor to enable the microprocessor port access. This input is internally set low during a device RESET.                                                                                                                                                                                                                                                                                                                  |

| DS       | A11                                                                     | <b>Data Strobe (5 V Tolerant).</b> This active low input works in conjunction with $\overline{\text{CS}}$ to enable the microprocessor port read and write operations.                                                                                                                                                                                                                                                                                                                     |

| R/W      | C11                                                                     | <b>Read/Write (5 V Tolerant).</b> This input controls the direction of the data bus lines (D0-D15) during a microprocessor access.                                                                                                                                                                                                                                                                                                                                                         |

| A0 - A14 | D5, C6, A6, D7, C7,<br>B7, C8, B8, A8, D9,<br>B9, A9, D10, C10,<br>A10  | Address 0 - 14 (5 V Tolerant). These pins form the 15-bit address bus to the internal memories and registers.  A0 = LSB                                                                                                                                                                                                                                                                                                                                                                    |

| D0 - D15 | V10, Y9, W9, V9,U9,<br>Y8, W8, V8, W7, V7,<br>U7, Y6, W6, V6, Y5,<br>W5 | Data Bus 0 - 15 (5 V Tolerant). These pins form the 16-bit data bus of the microprocessor port.  D0 = LSB                                                                                                                                                                                                                                                                                                                                                                                  |

| DTA      | A13                                                                     | <b>Data Transfer Acknowledgment (5 V Tolerant).</b> This active low output indicates that a data bus transfer is complete. A pull-up resistor is required to hold a HIGH level. (Max. $I_{OL} = 10 \text{ mA}$ ).                                                                                                                                                                                                                                                                          |

| TMS      | D12                                                                     | Test Mode Select (5 V Tolerant with internal pull-up). JTAG signal that controls the state transitions of the TAP controller.                                                                                                                                                                                                                                                                                                                                                              |

| TCK      | A14                                                                     | Test Clock (5 V Tolerant). Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDi      | B13                                                                     | Test Serial Data In (5 V Tolerant with internal pull-up). JTAG serial test instructions and data are shifted in on this pin.                                                                                                                                                                                                                                                                                                                                                               |

| TDo      | C13                                                                     | <b>Test Serial Data Out (5 V Tolerant Three-state Output).</b> JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG is not enabled.                                                                                                                                                                                                                                                                                       |

| TRST     | B14                                                                     | <b>Test Reset (5 V Tolerant with internal pull-up)</b> Asynchronously initializes the JTAG TAP controller to the Test-Logic-Reset state. To be pulsed low during power-up for JTAG testing. This pin must be held LOW for normal functional operation of the device.                                                                                                                                                                                                                       |

| RESET    | C12                                                                     | Device Reset (5 V Tolerant with internal pull-up). This input (active LOW) asynchronously applies reset and synchronously releases reset to the device. In the reset state, the outputs LSTo0 - 31 and BSTo0 - 31 are set to a high or high impedance depending on the state of the LORS and BORS external control pins, respectively. It clears the device registers and internal counters. This pin must stay low for more than 2 cycles of input clock C8i for the reset to be invoked. |

| Name       | Package<br>Coordinates                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSTi0-31   | L18, L19, L20, M17,<br>M18,<br>M19, M20, N18,<br>N19, N20, P17, P19,<br>P20, R18, R19, R20,<br>T18, T19, T20, U18,<br>U19, U20, V17, V18,<br>V19, V20, W18,<br>W19, Y20, Y17, Y18,<br>Y19 | Local Serial Input Streams 0 to 31 (5 V Tolerant with internal pull-down). These pins accept serial TDM data streams at a data-rate of:- 16.384 Mb/s (with 256 channels per stream), 8.192 Mb/s (with 128 channels per stream), 4.096 Mb/s (with 64 channels per stream), or 2.048 Mb/s (with 32 channels per stream). The data-rate is independently programmable for each input stream.                                                                                                                                                                                                    |

| C160       | W13                                                                                                                                                                                       | C16o Output Clock (Three-state Output). A 16.384 MHz clock output. The clock falling edge or rising edge is aligned with the local frame boundary, this is controlled by the COPOL bit of the Control Register.                                                                                                                                                                                                                                                                                                                                                                              |

| C80        | V13                                                                                                                                                                                       | C8o Output Clock (Three-state Output). A 8.192 MHz clock output. The clock falling edge or rising edge is aligned with the local frame boundary, this is controlled by the COPOL bit of the Control Register.                                                                                                                                                                                                                                                                                                                                                                                |

| FP160      | W14                                                                                                                                                                                       | <b>Frame Pulse Output (Three-state Output).</b> Frame pulse output is active for 61ns at the frame boundary. The frame pulse, running at a 8 <u>KHz rate</u> , will be the same format (ST-BUS or GCI-BUS) as the input frame pulse (FP8i).                                                                                                                                                                                                                                                                                                                                                  |

| FP8o       | V14                                                                                                                                                                                       | Frame Pulse Output (Three-state Output). Frame pulse output is active for 122 ns at the frame boundary. The frame pulse, running at <u>8 KHz</u> rate, will be the same style (ST-BUS or GCI-BUS) as the input frame pulse (FP8i).                                                                                                                                                                                                                                                                                                                                                           |

| LSTo0 - 31 | A17, A18, A19, B18,<br>B19, B20, C18, C19,<br>C20, D18, D19, D20,<br>E17, E18, E19, E20,<br>F18, F19, F20, G17,<br>G18, G19, G20,<br>H18, H19, H20, J17,<br>J18, J19, J20, K17,<br>K18    | Local Serial Output Streams 0 to 31 (5 V Tolerant Three-state Outputs). These pins output serial TDM data streams at a data-rate of:- 16.384 Mb/s (with 256 channels per stream), 8.192 Mb/s (with 128 channels per stream), 4.096 Mb/s (with 64 channels per stream), or 2.048 Mb/s (with 32 channels per stream).  The data-rate is independently programmable for each output stream.  Refer to descriptions of the LORS and ODE pins for control of the output High or High-Impedance state.                                                                                             |

| LCSTo0-3   | C17, C16, B16, A16                                                                                                                                                                        | Local Output Channel High Impedance Control (5 V Tolerant Three-state Outputs).  Active high output enable which may be used to control external buffering individually for a set of local output streams on a per channel basis.  LCSTo0 is the output enable for LSTo[0,4,8,12,16,20,24,28], LCSTo1 is the output enable for LSTo[1,5,9,13,17,21,25,29], LCSTo2 is the output enable for LSTo[2,6,10,14,18,22,26,30], LCSTo3 is the output enable for LSTo[3,7,11,15,19,23,27,31].  Refer to descriptions of the LORS and ODE pins for control of the output High or High-Impedance state. |

| Name | Package<br>Coordinates                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ODE  | A12                                                                                                                                       | Output Drive Enable (5 V Tolerant, Internal pull-up).                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                                                           | An asynchronous input providing Output Enable control to the BSTo0- 31, LSTo0- 31, BCSTo0-3 and LCSTo0-3 outputs.                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                           | When LOW, the BSTo0-31 and LSTo0-31 outputs are driven high or high impedance (dependent on the <b>BORS</b> and <b>LORS</b> pin settings respectively) and the outputs BCSTo0-3 and LCSTo0-3 are driven low.                                                                                                                                                                                         |

|      |                                                                                                                                           | When HIGH, the outputs BSTo0- 31, LSTo0-31, BCSTo0-3 and LCSTo0-3 are enabled.                                                                                                                                                                                                                                                                                                                       |

| BORS | K2                                                                                                                                        | Backplane Output Reset State (5 V Tolerant, Internal pull-down).                                                                                                                                                                                                                                                                                                                                     |

|      |                                                                                                                                           | When this input is LOW the device will initialize with the BSTo0-31 outputs driven high, and the BCSTo0-3 outputs driven low. Following initialization, the Backplane stream outputs are always active and a high impedance state, if required on a perchannel basis, may be implemented with external buffers controlled by outputs BCSTo0-3.                                                       |

|      |                                                                                                                                           | When this input is HIGH, the device will initialize with the BSTo0-31 outputs at high impedance and the BCSTo0-3 outputs driven low. Following initialization, the Backplane stream outputs may be set active or high impedance using the <b>ODE</b> pin or on a per-channel basis with the <b>BE</b> bit in Backplane Connection Memory.                                                            |

| LORS | K19                                                                                                                                       | Local Output Reset State (5 V Tolerant, Internal pull-down).  When this input is LOW, the device will initialize with the LSTo0-31 outputs driven high and the LCSTo0-3 outputs driven low. Following initialization, the Local stream outputs are always active and a high impedance state, if required on a perchannel basis, may be implemented with external buffers controlled by the LCSTo0-3. |

|      |                                                                                                                                           | When this input is HIGH, the device will initialize with the LST00-31 outputs at high impedance and the LCST00-3 driven low. Following initialization, the Local stream outputs may be set active or high impedance using the <b>ODE</b> pin or on a perchannel basis with the <b>LE</b> bit in Local Connection Memory.                                                                             |

| NC   | Y12, Y13                                                                                                                                  | No Connect No connection to be made.                                                                                                                                                                                                                                                                                                                                                                 |

| IC0  | A2, A20, B6, B10,<br>B17, C3, C9, D16,<br>U2, U3, V2, V3, V11,<br>V12, V15, V16, W10,<br>W11, W15, W16,<br>W17, W20, Y3, Y10,<br>Y15, Y16 | Internal Connects These inputs MUST be held LOW.                                                                                                                                                                                                                                                                                                                                                     |

## 1.0 Bidirectional and Unidirectional Switching Applications