# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

ISO<sup>2</sup>-CMOS MT9162 5 Volt Single Rail Codec

Data Sheet

## Features

- Single 5 volt supply

- Programmable  $\mu$ -law/A-law Codec and filters

- Fully differential output driver

- SSI digital interface

- SSI speed control via external pins CSLO-CSL2

- · Individual transmit and receive mute controls

- 0 dB gain in receive path

- 6 dB gain in transmit path

- · Low power operation

- ITU-T G.714 compliant

## Applications

- Cellular radio sets

- Local area communications stations

- Line cards

May 2006

#### **Ordering Information**

MT9162AE 20 Pin PDIP Tubes MT9162AS 20 Pin SOIC Tubes MT9162AN 20 Pin SSOP Tubes MT9162AN1 20 Pin SSOP\* Tubes \*Pb Free Matte Tin

-40°C to +85°C

## Description

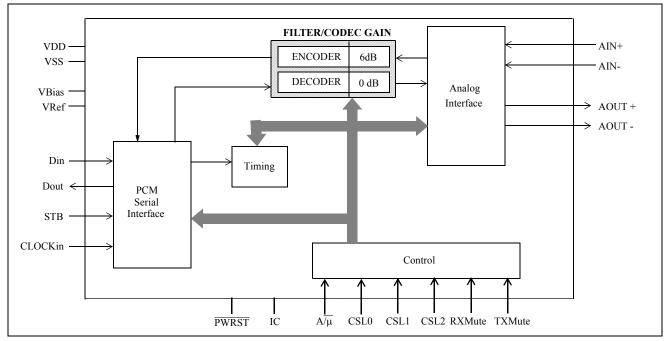

The MT9162 5 V single rail Codec incorporates a builtin Filter/Codec, transmit anti-alias filter, a reference voltage and bias source. The device supports both Alaw and  $\mu$ -law requirements.

The analog interface is capable of driving a 20 k ohm load.

The MT9162 is fabricated in Zarlink's ISO<sup>2</sup>-CMOS technology ensuring low power consumption and high reliability.

#### Figure 1 - Functional Block Diagram

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 1999-2006, Zarlink Semiconductor Inc. All Rights Reserved.

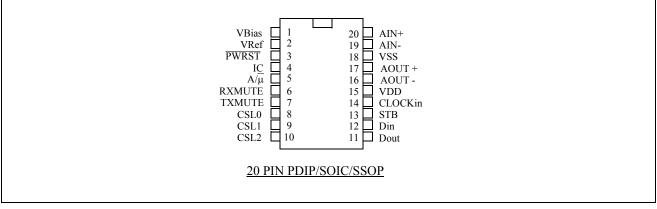

#### **Pin Description**

| Pin #        | Name                 | Description                                                                                                                                                                                                                                                             |

|--------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | V <sub>Bias</sub>    | <b>Bias Voltage (Output).</b> $(V_{DD}/2)$ volts is available at this pin for biasing external amplifiers. Connect 0.1 $\mu$ F capacitor to V <sub>SS</sub> . Connect 1 $\mu$ F capacitor to Vref.                                                                      |

| 2            | V <sub>Ref</sub>     | <b>Reference Voltage for Codec (Output).</b> Nominally $[(V_{DD}/2)-1.9]$ volts. Used internally. Connect 0.1 $\mu$ F capacitor to V <sub>SS</sub> . Connect 1 $\mu$ F capacitor to VBias                                                                               |

| 3            | PWRST                | Power-up Reset. Resets internal state of device via Schmitt Trigger input (active low).                                                                                                                                                                                 |

| 4            | IC                   | Internal Connection. Tie externally to $V_{SS}$ for normal operation.                                                                                                                                                                                                   |

| 5            | $A/\overline{\mu}$   | $A/\overline{\mu}$ Law Selection. CMOS level compatible input pin governs the companding law used by the device. A-law selected when pin tied to $V_{DD}$ or $\mu$ -law selected when pin tied to $V_{SS}$ .                                                            |

| 6            | RXMute               | <b>Receive Mute.</b> When 1, the transmit PCM is forced to negative zero code. When 0, normal operation. CMOS level compatible.                                                                                                                                         |

| 7            | TXMute               | <b>Transmit Mute.</b> When 1, the transmit PCM is forced to negative zero code. When 0, normal operation. CMOS level compatible.                                                                                                                                        |

| 8<br>9<br>10 | CSL0<br>CSL1<br>CSL2 | <b>Clock Speed Select.</b> These pins are used to program the speed of the SSI mode as well as the conversion rate between the externally supplied MCL clock and the 512 kHz clock required by the filter/codec. Refer to Table 2 for details. CMOS level compatible.   |

| 11           | D <sub>out</sub>     | <b>Data Output.</b> A tri-state digital output for 8-bit wide channel data being sent to the Layer 1 device.<br>Data is shifted out via the pin concurrent with the rising edge of BCL during the timeslot defined by STB.                                              |

| 12           | D <sub>in</sub>      | <b>Data Input.</b> A digital input for 8-bit wide data from the layer 1 device. Data is sampled on the falling edge of BCL during the timeslot defined by STB. CMOS level compatible.                                                                                   |

| 13           | STB                  | <b>Data Strobe.</b> This input determines the 8-bit timeslot used by the device for both transmit and receive data. This active high signal has a repetition rate of 8 kHz. CMOS level compatible.                                                                      |

| 14           | CLOCKin              | <b>Clock (Input).</b> The clock provided to this input pin is used by the internal device functions. Connect bit clock to this pin when it is 512 kHz or greater. Connect a 4096 kHz clock to this pin when the bit clock is 128 kHz or 256 kHz. CMOS level compatible. |

| 15           | V <sub>DD</sub>      | Positive Power Supply. Nominally 5 volts.                                                                                                                                                                                                                               |

#### Pin Description (continued)

| Pin # | Name            | Description                                                                             |  |  |  |  |  |  |

|-------|-----------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 16    | AOUT-           | Inverting Analog Output. (balanced).                                                    |  |  |  |  |  |  |

| 17    | AOUT+           | Inverting Analog Output. (balanced).                                                    |  |  |  |  |  |  |

| 18    | V <sub>SS</sub> | Ground. Nominally 0 volts.                                                              |  |  |  |  |  |  |

| 19    | Ain-            | Inverting Analog Input. No external anti-aliasing is required.                          |  |  |  |  |  |  |

| 20    | Ain+            | Non-Inverting Analog Input. Non-inverting input. No external anti-aliasing is required. |  |  |  |  |  |  |

## Overview

The 5 V single rail Codec features complete Analog/Digital and Digital/Analog conversion of audio signals (Filter/Codec) and an analog interface to a standard analog transmitter and receiver (Analog Interface). The receiver amplifier is capable of driving a 20 k ohm load.

## **Functional Description**

#### Filter/Codec

The Filter/Codec block implements conversion of the analog 0-3.3 kHz speech signals to/from the digital domain compatible with 64 kb/s PCM B-Channels. Selection of companding curves and digital code assignment are programmable. These are ITU-T G.711 A-law or  $\mu$ -Law, with true-sign/Alternate Digit Inversion.

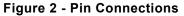

The Filter/Codec block also implements a transmit audio path gain in the analog domain. Figure 3 depicts the nominal half-channel for the MT9162.

The internal architecture is fully differential to provide the best possible noise rejection as well as to allow a wide dynamic range from a single 5 volt supply design. This fully differential architecture is continued into the analog interface section to provide full chip realization of these capabilities for the external functions.

A reference voltage (V<sub>Ref</sub>), for the conversion requirements of the Codec section, and a bias voltage (V<sub>Bias</sub>), for biasing the internal analog sections, are both generated on-chip. V<sub>Bias</sub> is also brought to an external pin so that it may be used for biasing external gain setting amplifiers. A  $0.1\mu$ F capacitor must be connected from V<sub>Bias</sub> to analog ground at all times. Likewise, although V<sub>Ref</sub> may only be used internally, a  $0.1\mu$ F capacitor from the V<sub>Ref</sub> pin to ground is required at all times. The analog ground reference point for these two capacitors must be physically the same point. To facilitate this the V<sub>Ref</sub> and V<sub>Bias</sub> pins are situated on adjacent pins.

The transmit filter is designed to meet ITU-T G.714 specifications. An anti-aliasing filter is included. This is a second order lowpass implementation with a corner frequency at 25 kHz.

The receive filter is designed to meet ITU-T G.714 specifications. Filter response is peaked to compensate for the sinx/x attenuation caused by the 8 kHz sampling rate.

Companding law selection for the Filter/Codec is provided by the A/  $\mu$  companding control pin. Table 1 illustrates these choices.

| Code                  | ITU-T (G.711) |           |  |  |  |  |  |

|-----------------------|---------------|-----------|--|--|--|--|--|

| Coue                  | μ -Law        | A-Law     |  |  |  |  |  |

| + Full Scale          | 1000 0000     | 1010 1010 |  |  |  |  |  |

| + Zero                | 1111 1111     | 1101 0101 |  |  |  |  |  |

| -Zero<br>(quiet code) | 0111 1111     | 0101 0101 |  |  |  |  |  |

| - Full Scale          | 0000 0000     | 0010 1010 |  |  |  |  |  |

Table 1 - Law Selection

#### Analog Interfaces

Standard interfaces are provided by the MT9162. These are:

- The analog inputs (transmitter), pins AIN+/AIN-. The maximum peak to peak input is 3.667Vpp  $\mu$ -law and across AIN+/AIN- 3.8Vpp A-law.

- The analog outputs (receiver), pins AOUT+/AOUT-. This internally compensated fully differential output driver is capable of driving a load of 20k ohms.

#### **PCM Serial Interface**

A serial link is required to transport data between the MT9162 and an external digital transmission device. The MT9162 utilizes the strobed data interface found on many standard Codec devices. This interface is commonly referred to as Simple Serial Interface (SSI).

The required mode of operation is selected via the CSL2-0 control pins. See Table 2 for selections based in CSL2-0 pin settings.

#### **Quiet Code**

The PCM serial port can be made to send quiet code to the decoder and receive filter path by setting the RxMute pin high. Likewise, the PCM serial port will send quiet code in the transmit path when the

| CSL <sub>2</sub> | CSL <sub>1</sub> | CSL <sub>0</sub> | External<br>Clock Bit<br>Rate (kHz) | CLOCKin<br>(kHz) |

|------------------|------------------|------------------|-------------------------------------|------------------|

| 1                | 0                | 0                | 128                                 | 4096             |

| 1                | 0                | 1                | 256                                 | 4096             |

| 0                | 0                | 0                | 512                                 | 512              |

| 0                | 0                | 1                | 1536                                | 1536             |

| 0                | 1                | 0                | 2048                                | 2048             |

| 0                | 1                | 1                | 4096                                | 4096             |

Figure 2 - Table 2: Bit Clock Rate Selection

TxMute pin is high. When either of these pins are low their respective paths function normally. The -Zero entry of Table 1 is used for the quiet code definition.

#### SSI Mode

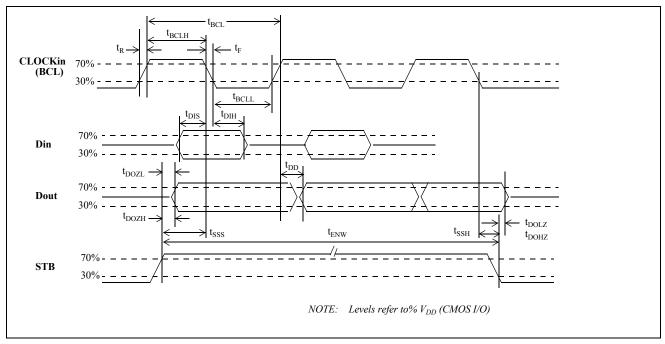

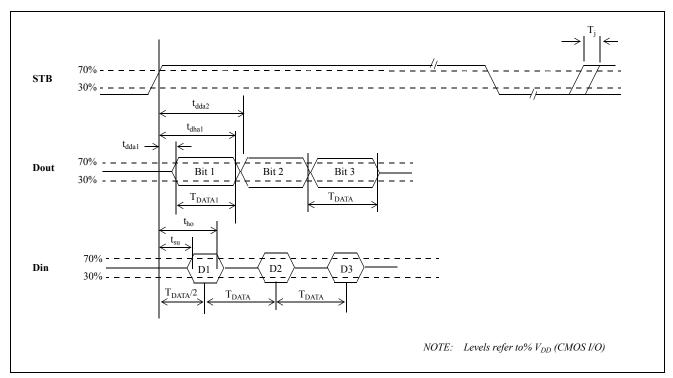

The SSI BUS consists of input and output serial data streams named Din and Dout respectively, a Clock input signal (CLOCKin), and a framing strobe input (STB). A 4.096 MHz master clock is also required for SSI operation if the bit clock is less than 512 kHz. The timing requirements for SSI are shown in Figures 5 & 6.

In SSI mode the MT9162 supports only B-Channel operation. Hence, in SSI mode transmit and receive B-Channel data are always in the channel defined by the STB input.

The data strobe input STB determines the 8-bit timeslot used by the device for both transmit and receive data. This is an active high signal with an 8 kHz repetition rate.

SSI operation is separated into two categories based upon the data rate of the available bit clock. If the bit clock is 512 kHz or greater then it is used directly by the internal MT9162 functions allowing synchronous operation. If the available bit clock is 128 kHz or 256 kHz, then a 4096 kHz master clock is required to derive clocks for the internal MT9162 functions.

Applications where Bit Clock (BCL) is below 512 kHz are designated as asynchronous. The MT9162 will re-align its internal clocks to allow operation when the external master and bit clocks are asynchronous. Control pins CSL2, CSL1 and CSL0 are used to program the bit rates.

Figure 3 - Audio Gain Partitioning

For synchronous operation, data is sampled from Din, on the falling edge of BCL during the time slot defined by the STB input. Data is made available, on Dout, on the rising edge of BCL during the time slot defined by the STB input. Dout is tri-stated at all times when STB is not true. If STB is valid, then quiet code will be transmitted on Dout during the valid strobe period. There is no frame delay through the PCM serial circuit for synchronous operation.

For asynchronous operation Dout and Din are as defined for synchronous operation except that the allowed output jitter on Dout is larger. This is due to the resynchronization circuitry activity and will not affect operation since the bit cell period at 128 kb/s and 256 kb/s is relatively large. There is a one frame delay through the PCM serial circuit for asynchronous operation. Refer to the specifications of Figures 5 & 6 for both synchronous and asynchronous SSI timing.

## **PWRST**

While the MT9162 is held in PWRST no device control or functionality is possible.

## Applications

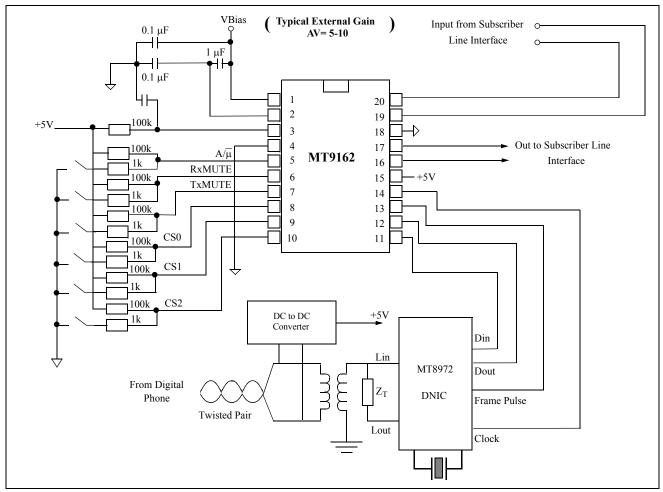

Figure 4 shows the MT9162 in a line card application.

Figure 4 - Line Card Application

## Absolute Maximum Ratings<sup>†</sup>

|   | Parameter                                     | Symbol                            | Min.                  | Max.           | Units |

|---|-----------------------------------------------|-----------------------------------|-----------------------|----------------|-------|

| 1 | Supply Voltage                                | V <sub>DD</sub> - V <sub>SS</sub> | - 0.3                 | 7              | V     |

| 2 | Voltage on any I/O pin                        | $V_I/V_O$                         | V <sub>SS</sub> - 0.3 | $V_{DD} + 0.3$ | V     |

| 3 | Current on any I/O pin (transducers excluded) | I <sub>I</sub> /I <sub>O</sub>    |                       | ± 20           | mA    |

| 4 | Storage Temperature                           | Τ <sub>S</sub>                    | - 65                  | + 150          | °C    |

| 5 | Power Dissipation (package)                   | P <sub>D</sub>                    |                       | 750            | mW    |

<sup>†</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

Recommended Operating Conditions - Voltages are with respect to  $V_{SS}$  unless otherwise stated

|   | Characteristics           | Sym.             | Min.            | Тур. | Max.            | Units | Test Conditions |

|---|---------------------------|------------------|-----------------|------|-----------------|-------|-----------------|

| 1 | Supply Voltage            | V <sub>DD</sub>  | 4.75            | 5    | 5.25            | V     |                 |

| 2 | CMOS Input Voltage (high) | V <sub>IHC</sub> | 4.5             |      | V <sub>DD</sub> | V     |                 |

| 3 | CMOS Input Voltage (low)  | V <sub>ILC</sub> | V <sub>SS</sub> |      | 0.5             | V     |                 |

| 4 | Operating Temperature     | T <sub>A</sub>   | - 40            |      | + 85            | °C    |                 |

#### **Power Characteristics**

|   | Characteristics                                        | Sym.              | Min. | Тур. | Max. | Units | Test Conditions                                    |

|---|--------------------------------------------------------|-------------------|------|------|------|-------|----------------------------------------------------|

| 1 | Static Supply Current (clock disabled)                 | I <sub>DDC1</sub> |      | 4    | 20   | μΑ    | Outputs unloaded, Input signals static, not loaded |

| 2 | Dynamic Supply Current:<br>Total all functions enabled | I <sub>DDFT</sub> |      | 7.0  | 10   | mA    | See Note 1                                         |

Note 1: Power delivered to the load is in addition to the bias current requirements.

|    | Characteristics                                                                                      | Sym.                               | Min. | Typ.‡                      | Max. | Units  | <b>Test Conditions</b>                |

|----|------------------------------------------------------------------------------------------------------|------------------------------------|------|----------------------------|------|--------|---------------------------------------|

| 1  | Input HIGH Voltage CMOS inputs                                                                       | V <sub>IHC</sub>                   | 3.5  |                            |      | V      |                                       |

| 2  | Input LOW Voltage CMOS inputs                                                                        | V <sub>ILC</sub>                   |      |                            | 1.5  | V      |                                       |

| 3  | VBias Voltage Output                                                                                 | V <sub>Bias</sub>                  |      | $V_{DD}/2$                 |      | V      | Max. Load = $10k\Omega$               |

| 4  | V <sub>Ref</sub> Output Voltage                                                                      | V <sub>Ref</sub>                   |      | V <sub>DD</sub> /2-<br>1.9 |      | V      | No load                               |

| 5  | Input Leakage Current                                                                                | I <sub>IZ</sub>                    |      | 0.1                        | 10   | μΑ     | $V_{IN}=V_{DD}$ to $V_{SS}$           |

| 6  | Positive Going Threshold<br>Voltage (PWRST only)<br>Negative Going Threshold<br>Voltage (PWRST only) | V <sub>T+</sub><br>V <sub>T-</sub> | 3.7  |                            | 1.3  | V<br>V |                                       |

| 7  | Output HIGH Current                                                                                  | I <sub>OH</sub>                    | 3    | 7                          |      | mA     | $V_{OH} = 0.9*V_{DD}$<br>See Note 1   |

| 8  | Output LOW Current                                                                                   | I <sub>OL</sub>                    | 5    | 10                         |      | mA     | $V_{OL} = 0.1 * V_{DD}$<br>See Note 1 |

| 9  | Output Leakage Current                                                                               | I <sub>OZ</sub>                    |      | 0.01                       | 10   | μΑ     | $V_{OUT} = V_{DD}$ and $V_{SS}$       |

| 10 | Output Capacitance                                                                                   | Co                                 |      | 15                         |      | pF     |                                       |

| 11 | Input Capacitance                                                                                    | Ci                                 |      | 10                         |      | pF     |                                       |

## **DC Electrical Characteristics**<sup>†</sup> - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

† DC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

\* Note 1 - Magnitude measurement, ignore signs.

## **Clockin Tolerance Characteristics<sup>†</sup>**

|   | Characteristics                          | Min.   | Тур.‡ | Max.   | Units | Test Conditions |

|---|------------------------------------------|--------|-------|--------|-------|-----------------|

| 1 | CLOCKin Frequency (Asynchronous<br>Mode) | 4095.6 | 4096  | 4096.4 | kHz   | (i.e., 100 ppm) |

† AC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

|   | Characteristics                                                                                              | Sym.                                       | Min.                 | Typ.‡                    | Max.                                              | Units                            | <b>Test Conditions</b>                                                                                  |

|---|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|--------------------------|---------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|

| 1 | Analog input equivalent to overload decision                                                                 | A <sub>Li3.17</sub><br>A <sub>Li3.14</sub> |                      | 7.334<br>7.6             |                                                   | Vp-p<br>Vp-p                     | μ-Law<br>A-Law<br>Both at Codec                                                                         |

| 2 | Absolute half-channel gain<br>AIN ± to Dout                                                                  | G <sub>AX1</sub>                           | 5.2                  | 6.0                      | 6.8                                               | dB                               | Transmit filter gain=0dB<br>setting.<br>@1020Hz                                                         |

| 3 | Gain tracking vs. input level<br>ITU-T G.714 Method 2                                                        | G <sub>TX</sub>                            | -0.3<br>-0.6<br>-1.6 |                          | 0.3<br>0.6<br>1.6                                 | dB<br>dB<br>dB                   | 3 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0                                                     |

| 4 | Signal to total Distortion vs. input<br>level.<br>ITU-T G.714 Method 2                                       | D <sub>QX</sub>                            | 35<br>29<br>24       |                          |                                                   | dB<br>dB<br>dB                   | 0 to -30 dBm0<br>-40 dBm0<br>-45 dBm0                                                                   |

| 5 | Transmit Idle Channel Noise                                                                                  | N <sub>CX</sub><br>N <sub>PX</sub>         |                      | 8.5<br>-71               | 12<br>-69                                         | dBrnC0<br>dBm0p                  | μ-Law<br>A-Law                                                                                          |

| 6 | Gain relative to gain at<br><50Hz<br>60Hz<br>200Hz<br>300 - 3000 Hz<br>3000 - 3400 Hz<br>4000 Hz<br>>4600 Hz | G <sub>RX</sub>                            | -0.25<br>-0.9        | -45<br>-23<br>-40        | -25<br>-30<br>0.0<br>0.25<br>0.25<br>-12.5<br>-25 | dB<br>dB<br>dB<br>dB<br>dB<br>dB |                                                                                                         |

| 7 | Absolute Delay                                                                                               | D <sub>AX</sub>                            |                      | 360                      |                                                   | μs                               | at frequency of minimum delay                                                                           |

| 8 | Group Delay relative to $D_{AX}$                                                                             | D <sub>DX</sub>                            |                      | 750<br>380<br>130<br>750 |                                                   | μs<br>μs<br>μs<br>μs             | 500-600 Hz<br>600 - 1000 Hz<br>1000 - 2600 Hz<br>2600 - 2800 Hz                                         |

| 9 | Power Supply Rejection<br>f=1020 Hz<br>f=0.3 to 3 kHz<br>f=3 to 4 kHz<br>f=4 to 50 kHz                       | PSSR<br>PSSR1<br>PSSR2<br>PSSR3            | 37                   | 37<br>40<br>35<br>40     |                                                   | dB<br>dB<br>dB<br>dB             | $\pm 100 \text{mV}$ peak signal on<br>V <sub>DD</sub><br>$\mu$ -law<br>PSSR1-3 not production<br>tested |

## **AC Characteristics**<sup>†</sup> **for A/D (Transmit) Path** - 0dBm0 = $A_{Lo3.17}$ - 3.17dB = 1.773V<sub>rms</sub> for $\mu$ -Law and - 3.14dB = 1.843V<sub>rms</sub> for A-Law, at the Codec. (V<sub>Ref</sub>=0.6 volts and V<sub>Bias</sub>=2.5 volts.)

0dBm0 =  $A_{Lo3.14}$

† AC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

|   | Characteristics                                                                                    | Sym.                                       | Min.                 | Typ.‡                    | Max.                                 | Units                      | <b>Test Conditions</b>                                          |

|---|----------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|--------------------------|--------------------------------------|----------------------------|-----------------------------------------------------------------|

| 1 | Analog output at the Codec full scale                                                              | A <sub>Lo3.17</sub><br>A <sub>Lo3.14</sub> |                      | 7.225<br>7.481           |                                      | Vp-p<br>Vp-p               | μ-Law<br>A-Law                                                  |

| 2 | Absolute half-channel gain.<br>Din to AOUT±                                                        | G <sub>AR1</sub>                           | -0.8                 | 0                        | 0.8                                  | dB                         | @1020Hz                                                         |

| 3 | Gain tracking vs. input level<br>ITU-T G.714 Method 2                                              | G <sub>TR</sub>                            | -0.3<br>-0.6<br>-1.6 |                          | 0.3<br>0.6<br>1.6                    | dB<br>dB<br>dB             | 3 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0             |

| 4 | Signal to total distortion vs. input<br>level.<br>ITU-T G.714 Method 2                             | G <sub>QR</sub>                            | 35<br>29<br>24       |                          |                                      | dB<br>dB<br>dB             | 0 to -30 dBm0<br>-40 dBm0<br>-45 dBm0                           |

| 5 | Receive Idle Channel Noise                                                                         | N <sub>CR</sub><br>N <sub>PR</sub>         |                      | 7<br>-84                 | 10<br>-80                            | dBrnC0<br>dBm0p            | μ-Law<br>A-Law                                                  |

| 6 | Gain relative to gain at 1020Hz<br>200Hz<br>300 - 3000 Hz<br>3000 - 3400 Hz<br>4000 Hz<br>>4600 Hz | G <sub>RR</sub>                            | -0.25<br>-0.90       |                          | 0.25<br>0.25<br>0.25<br>-12.5<br>-25 | dB<br>dB<br>dB<br>dB<br>dB |                                                                 |

| 7 | Absolute Delay                                                                                     | D <sub>AR</sub>                            |                      | 240                      |                                      | μs                         | at frequency of min. delay                                      |

| 8 | Group Delay relative to D <sub>AR</sub>                                                            | D <sub>DR</sub>                            |                      | 750<br>380<br>130<br>750 |                                      | μs<br>μs<br>μs<br>μs       | 500-600 Hz<br>600 - 1000 Hz<br>1000 - 2600 Hz<br>2600 - 2800 Hz |

| 9 | CrosstalkD/A to A/D<br>A/D to D/A                                                                  | CT <sub>RT</sub><br>CT <sub>TR</sub>       |                      |                          | -74<br>-80                           | dB<br>dB                   | G.714.16<br>ITU-T                                               |

## **AC Characteristics**<sup>†</sup> **for D/A (Receive) Path** - 0dBm0 = $A_{Lo3.17}$ - 3.17dB = 1.773V<sub>rms</sub> for $\mu$ -Law and - 3.14dB = 1.843V<sub>rms</sub> for A-Law, at the Codec. (V<sub>Ref</sub>=0.6 volts and V<sub>Bias</sub>=2.5 volts.)

0dBm0 =  $A_{Lo3.14}$

+ AC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

## Electrical Characteristics<sup>†</sup> for Analog Outputs

|   | Characteristics                   | Sym.            | Min. | Typ.‡ | Max<br>· | Units | Test Conditions                                          |

|---|-----------------------------------|-----------------|------|-------|----------|-------|----------------------------------------------------------|

| 1 | Load impedance at Output          | E <sub>ZL</sub> | 20k  |       |          | ohms  | across AOUT±                                             |

| 2 | Allowable output capacitive load  | E <sub>CL</sub> |      | 20    |          | pF    | each pin:AOUT+, AOUT-                                    |

| 3 | Analog output harmonic distortion | E <sub>D</sub>  |      |       | 0.5      | %     | 20k ohms load across<br>AOUT±<br>VO≤693mV <sub>RMS</sub> |

† Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

## Electrical Characteristics<sup>†</sup> for Analog Inputs

|   | Characteristics                                                        | Sym.              | Min. | Typ.‡        | Max. | Units | Test Conditions                                  |

|---|------------------------------------------------------------------------|-------------------|------|--------------|------|-------|--------------------------------------------------|

| 1 | Maximum input voltage without<br>overloading Codec<br>across AIN+/AIN- | V <sub>IOLH</sub> |      | 2.90<br>3.00 |      | Vp-p  | $\begin{array}{l} A/\mu=0\\ A/\mu=1 \end{array}$ |

| 2 | Input Impedance                                                        | ZI                | 50   |              |      | kΩ    | AIN+/AIN- to V <sub>SS</sub>                     |

† Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25 °C and are for design aid only: not guaranteed and not subject to production testing.

|    | Characteristics                                           | Sym.              | Min. | Typ.‡                | Max.                 | Units | Test Conditions                          |

|----|-----------------------------------------------------------|-------------------|------|----------------------|----------------------|-------|------------------------------------------|

| 1  | BCL Clock Period                                          | t <sub>BCL</sub>  | 244  |                      | 1953                 | ns    | BCL=4096 kHz to 512 kHz                  |

| 2  | BCL Pulse Width High                                      | t <sub>BCLH</sub> |      | 122                  |                      | ns    | BCL=4096 kHz                             |

| 3  | BCL Pulse Width Low                                       | t <sub>BCLL</sub> |      | 122                  |                      | ns    | BCL=4096 kHz                             |

| 4  | BCL Rise/Fall Time                                        | $t_R/t_F$         |      | 20                   |                      | ns    | Note 1                                   |

| 5  | Strobe Pulse Width                                        | t <sub>ENW</sub>  |      | 8 x t <sub>BCL</sub> |                      | ns    | Note 1                                   |

| 6  | Strobe setup time before BCL falling                      | t <sub>SSS</sub>  | 70   |                      | t <sub>BCL-80</sub>  | ns    |                                          |

| 7  | Strobe hold time after BCL falling                        | t <sub>SSH</sub>  | 80   |                      | t <sub>BCL</sub> -80 | ns    |                                          |

| 8  | Dout High Impedance to Active Low from Strobe rising      | t <sub>DOZL</sub> |      |                      | 50                   | ns    | $C_{L}$ =150 pF, $R_{L}$ =1K             |

| 9  | Dout High Impedance to Active High from Strobe rising     | t <sub>DOZH</sub> |      |                      | 50                   | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

| 10 | Dout Active Low to High Impedance<br>from Strobe falling  | t <sub>DOLZ</sub> |      |                      | 50                   | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

| 11 | Dout Active High to High Impedance<br>from Strobe falling | t <sub>DOHZ</sub> |      |                      | 50                   | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

| 12 | Dout Delay (high and low) from BCL rising                 | t <sub>DD</sub>   |      |                      | 50                   | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

| 13 | Din Setup time before BCL falling                         | t <sub>DIS</sub>  | 20   |                      |                      | ns    |                                          |

| 14 | Din Hold Time from BCL falling                            | t <sub>DIH</sub>  | 50   |                      |                      | ns    |                                          |

## AC Electrical Characteristics<sup>†</sup> - SSI BUS Synchronous Timing (see Figure 5)

† Timing is over recommended temperature range & recommended power supply voltages.

**‡** Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing. NOTE 1:Not production tested, guaranteed by design.

Figure 5 - SSI Synchronous Timing Diagram

| <b>AC Electrical Characteristic</b> | <sup>†</sup> - SSI BUS Asynchronous Timing (note 1) (see Figure 6) |

|-------------------------------------|--------------------------------------------------------------------|

|-------------------------------------|--------------------------------------------------------------------|

|   |                                      |                    |                                   | +                 |                                   |       |                                          |

|---|--------------------------------------|--------------------|-----------------------------------|-------------------|-----------------------------------|-------|------------------------------------------|

|   | Characteristics                      | Sym.               | Min.                              | Тур.‡             | Max.                              | Units | Test Conditions                          |

| 1 | Bit Cell Period                      | T <sub>DATA</sub>  |                                   | 7812              |                                   | ns    | BCL=128 kHz                              |

|   |                                      |                    |                                   | 3906              |                                   | ns    | BCL=256 kHz                              |

| 2 | Frame Jitter                         | Tj                 |                                   |                   | 600                               | ns    |                                          |

| 3 | Bit 1 Dout Delay from STB going high | t <sub>dda1</sub>  |                                   |                   | T <sub>j</sub> +600               | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

| 4 | Bit 2 Dout Delay from STB going      | t <sub>dda2</sub>  | 600+                              | 600+              | 600 +                             | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

|   | high                                 |                    | T <sub>DATA</sub> -T <sub>j</sub> | T <sub>DATA</sub> | T <sub>DATA</sub> +T <sub>j</sub> |       |                                          |

| 5 | Bit n Dout Delay from STB going      | t <sub>ddan</sub>  | 600 +                             | 600 +             | 600 +                             | ns    | $C_L = 150 \text{ pF}, R_L = 1 \text{K}$ |

|   | high                                 |                    | (n-1) x                           | (n-1) x           | (n-1) x                           |       | n=3 to 8                                 |

|   |                                      |                    | T <sub>DATA</sub> -T <sub>j</sub> | T <sub>DATA</sub> | T <sub>DATA</sub> +T <sub>j</sub> |       |                                          |

|   |                                      |                    |                                   |                   |                                   |       |                                          |

| 6 | Bit 1 Data Boundary                  | T <sub>DATA1</sub> | T <sub>DATA</sub> -T <sub>j</sub> |                   | T <sub>DATA</sub> +T <sub>j</sub> | ns    |                                          |

| 7 | Din Bit n Data Setup time from       | $t_{\mathrm{SU}}$  | $T_{DATA} \ge 2$                  |                   |                                   | ns    | n=1-8                                    |

|   | STB rising                           |                    | +500ns-T <sub>j</sub>             |                   |                                   |       |                                          |

|   |                                      |                    | +(n-1)x                           |                   |                                   |       |                                          |

|   |                                      |                    | T <sub>DATA</sub>                 |                   |                                   |       |                                          |

| 8 | Din Data Hold time from STB          | t <sub>ho</sub>    | $T_{DATA} \ge 2$                  |                   |                                   | ns    |                                          |

|   | rising                               |                    | +500ns+T <sub>j</sub>             |                   |                                   |       |                                          |

| 1 |                                      |                    | +(n-1) x                          |                   |                                   |       |                                          |

|   |                                      |                    | T <sub>DATA</sub>                 |                   |                                   |       |                                          |

† Timing is over recommended temperature range & recommended power supply voltages.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Figure 6 - SSI Asynchronous Timing Diagram

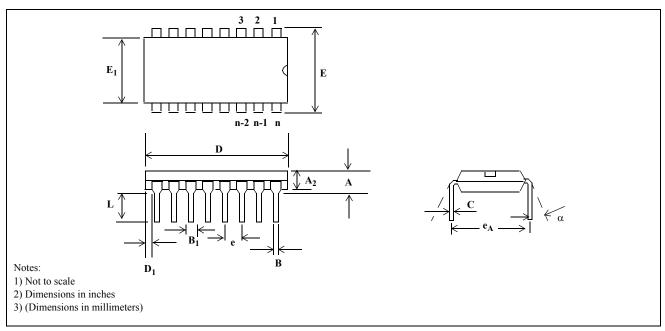

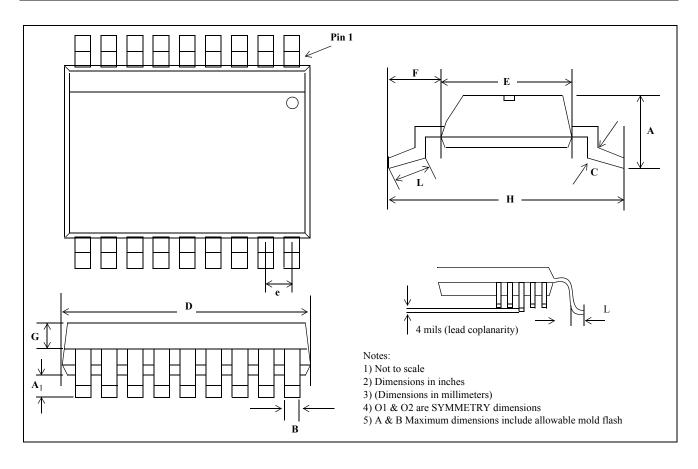

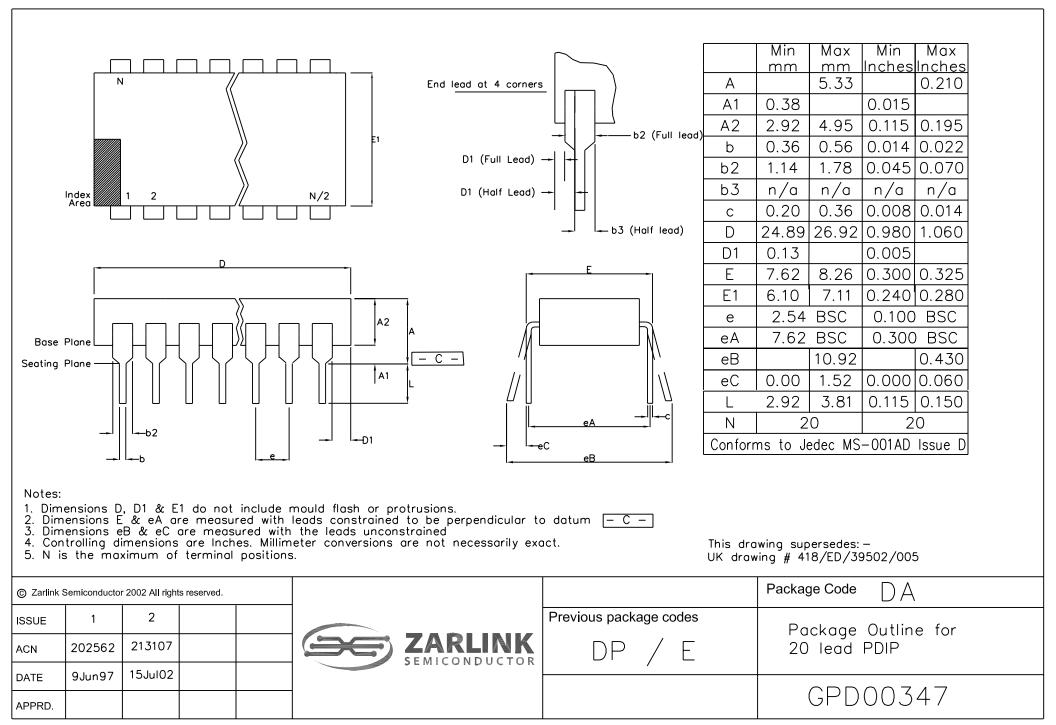

## Plastic Dual-In-Line Packages (PDIP) - E Suffix

|                | 8-1              | Pin              | 16-              | Pin              | 18-              | Pin              | 20-              | Pin              |

|----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| DIM            | Pla              | stic             | Pla              | Plastic          |                  | stic             | Pla              | stic             |

|                | Min              | Max              | Min              | Max              | Min              | Max              | Min              | Max              |

| А              |                  | 0.210 (5.33)     |                  | 0.210 (5.33)     |                  | 0.210 (5.33)     |                  | 0.210 (5.33)     |

| A <sub>2</sub> | 0.115 (2.93)     | 0.195 (4.95)     | 0.115 (2.93)     | 0.195 (4.95)     | 0.115 (2.93)     | 0.195 (4.95)     | 0.115 (2.93)     | 0.195 (4.95)     |

| В              | 0.014<br>(0.356) | 0.022<br>(0.558) | 0.014<br>(0.356) | 0.022<br>(0.558) | 0.014<br>(0.356) | 0.022<br>(0.558) | 0.014<br>(0.356) | 0.022<br>(0.558) |

| B <sub>1</sub> | 0.045 (1.15)     | 0.070 (1.77)     | 0.045 (1.15)     | 0.070 (1.77)     | 0.045 (1.15)     | 0.070 (1.77)     | 0.045 (1.15)     | 0.070 (1.77)     |

| С              | 0.008<br>(0.204) | 0.015<br>(0.381) | 0.008<br>(0.204) | 0.015<br>(0.381) | 0.008<br>(0.204) | 0.015<br>(0.381) | 0.008<br>(0.204) | 0.015<br>(0.381) |

| D              | 0.348 (8.84)     | 0.430<br>(10.92) | 0.745<br>(18.93) | 0.840<br>(21.33) | 0.845<br>(21.47) | 0.925<br>(23.49) | 0.925<br>(23.49) | 1.060 (26.9)     |

| D <sub>1</sub> | 0.005 (0.13)     |                  | 0.005 (0.13)     |                  | 0.005 (0.13)     |                  | 0.005 (0.13)     |                  |

| Е              | 0.290 (7.37)     | 0.330 (8.38)     | 0.290 (7.37)     | 0.330 (8.38)     | 0.290 (7.37)     | 0.330 (8.38)     | 0.290 (7.37)     | 0.330 (8.38)     |

| E <sub>1</sub> | 0.240 (6.10)     | 0.280 (7.11)     | 0.240 (6.10)     | 0.280 (7.11)     | 0.240 (6.10)     | 0.280 (7.11)     | 0.240 (6.10)     | 0.280 (7.11)     |

| e              | 0.100 BSC (2.54) |                  |

| e <sub>1</sub> |                  |                  |                  |                  |                  |                  |                  |                  |

| e <sub>A</sub> | 0.300 BSC (7.62) |                  |

| L              | 0.115 (2.93)     | 0.160 (4.06)     | 0.115 (2.93)     | 0.160 (4.06)     | 0.115 (2.93)     | 0.160 (4.06)     | 0.115 (2.93)     | 0.160 (4.06)     |

|     | 8-1 | Pin  | 16-Pin<br>Plastic |     | 18-     | Pin | 20-Pin  |     |

|-----|-----|------|-------------------|-----|---------|-----|---------|-----|

| DIM | Pla | stic |                   |     | Plastic |     | Plastic |     |

|     | Min | Max  | Min               | Max | Min     | Max | Min     | Max |

| S   |     |      |                   |     |         |     |         |     |

| a   |     | 15°  |                   | 15° |         | 15° |         | 15° |

NOTE: ( ) Millimeters

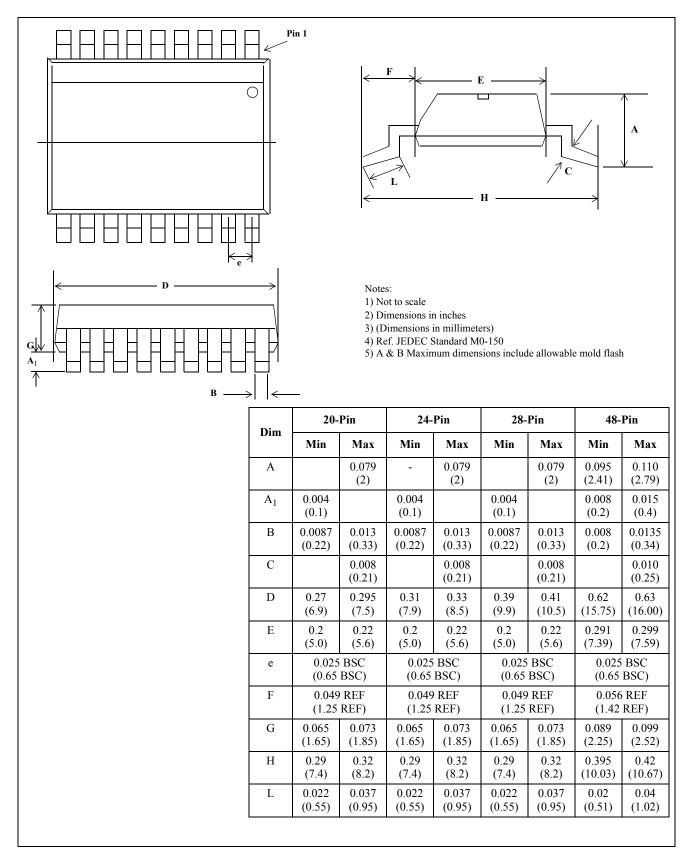

| DIM            | 16-Pin     |         | 18-        | 18-Pin  |            | Pin     | 24-        | Pin     | 28-        | Pin     |

|----------------|------------|---------|------------|---------|------------|---------|------------|---------|------------|---------|

| DIN            | Min        | Max     |

| А              | 0.093      | 0.104   | 0.093      | 0.104   | 0.093      | 0.104   | 0.093      | 0.104   | 0.093      | 0.104   |

|                | (2.35)     | (2.65)  | (2.35)     | (2.65)  | (2.35)     | (2.65)  | (2.35)     | (2.65)  | (2.35)     | (2.65)  |

| A <sub>1</sub> | 0.004      | 0.012   | 0.004      | 0.012   | 0.004      | 0.012   | 0.004      | 0.012   | 0.004      | 0.012   |

|                | (0.10)     | (0.30)  | (0.10)     | (0.30)  | (0.10)     | (0.30)  | (0.10)     | (0.30)  | (0.10)     | (0.30)  |

| В              | 0.014      | 0.019   | 0.014      | 0.019   | 0.014      | 0.019   | 0.014      | 0.019   | 0.014      | 0.019   |

|                | (0.351)    | (0.488) | (0.351)    | (0.488) | (0.351)    | (0.488) | (0.351)    | (0.488) | (0.351)    | (0.488) |

| С              | 0.009      | 0.013   | 0.009      | 0.013   | 0.009      | 0.013   | 0.009      | 0.013   | 0.009      | 0.013   |

|                | (0.231)    | (0.318) | (0.231)    | (0.318) | (0.231)    | (0.318) | (0.231)    | (0.318) | (0.231)    | (0.318) |

| D              | 0.398      | 0.413   | 0.447      | 0.469   | 0.496      | 0.518   | 0.598      | 0.614   | 0.697      | 0.712   |

|                | (10.1)     | (10.5)  | (11.35)    | (11.90) | (12.60)    | (13.00) | (15.2)     | (15.6)  | (17.7)     | (18.1)  |

| Е              | 0.291      | 0.305   | 0.291      | 0.305   | 0.291      | 0.305   | 0.291      | 0.305   | 0.291      | 0.305   |

|                | (7.40)     | (7.75)  | (7.40)     | (7.75)  | (7.40)     | (7.75)  | (7.40)     | (7.75)  | (7.40)     | (7.75)  |

| e              | 0.050 BSC  |         |

|                | (1.27 BSC) |         | (1.27 BSC) |         | (1.27 BSC) |         | (1.27 BSC) |         | (1.27 BSC) |         |

| F              | 0.044      | 0.064   | 0.044      | 0.064   | 0.044      | 0.064   | 0.044      | 0.064   | 0.044      | 0.064   |

|                | (1.125)    | (1.625) | (1.125)    | (1.625) | (1.125)    | (1.625) | (1.125)    | (1.625) | (1.125)    | (1.625) |

| DIM | 16-Pin  |         | 18-Pin  |         | 20-Pin  |         | 24-Pin  |         | 28-Pin  |         |

|-----|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| DIM | Min     | Max     |

| G   | 0.040   | 0.050   | 0.040   | 0.050   | 0.040   | 0.050   | 0.040   | 0.050   | 0.040   | 0.050   |

|     | (1.016) | (1.270) | (1.016) | (1.270) | (1.016) | (1.270) | (1.016) | (1.270) | (1.016) | (1.270) |

| Н   | 0.394   | 0.419   | 0.394   | 0.419   | 0.394   | 0.419   | 0.394   | 0.419   | 0.394   | 0.419   |

|     | (10.00) | (10.65) | (10.00) | (10.65) | (10.00) | (10.65) | (10.00) | (10.65) | (10.00) | (10.65) |

| L   | 0.016   | 0.050   | 0.016   | 0.050   | 0.016   | 0.050   | 0.016   | 0.050   | 0.016   | 0.050   |

|     | (0.40)  | (1.27)  | (0.40)  | (1.27)  | (0.40)  | (1.27)  | (0.40)  | (1.27)  | (0.40)  | (1.27)  |

Lead SOIC Package - S Suffix

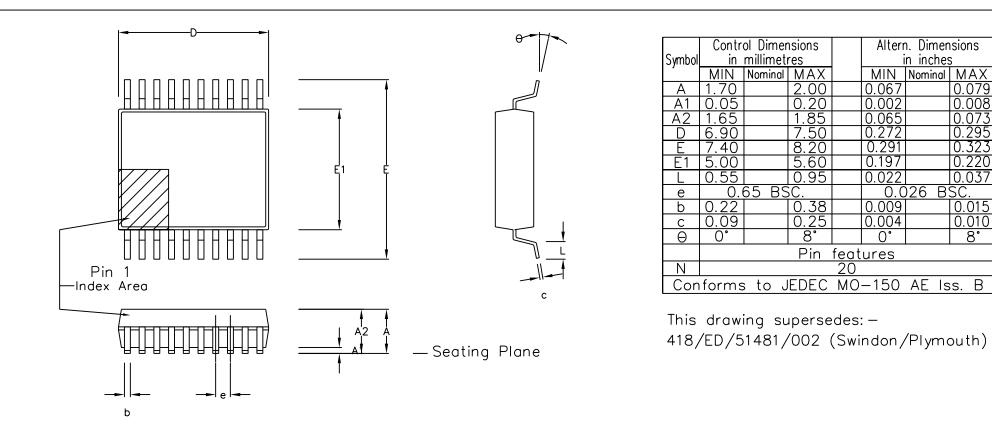

#### Small Shrink Outline Package (SSOP) - N Suffix

## Notes:

- 1. A visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- 3. Dimensions D and E1 do not include mould flash or protusion. Mould flash or protusion shall not exceed

- 0.20 mm per side. D and E1 are maximum plastic body size dimensions including mould mismatch.

4. Dimension b does not include dambar protusion/intrusion. Allowable dambar protusion shall be 0.13 mm total in excess of b dimension. Dambar intrusion shall not reduce dimension b by more than 0.07 mm.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |        |  |               |                        | Package Code                |

|---------------------------------------------------|---------|---------|--------|--|---------------|------------------------|-----------------------------|

| ISSUE                                             | 1       | 2       | 3      |  |               | Previous package codes | Package Outline for 20 lead |

| ACN                                               | 201933  | 205234  | 212477 |  | SEMICONDUCTOR |                        | SSOP (5.3mm Body Width)     |

| DATE                                              | 27Feb97 | 25Sep98 | 3Apr02 |  |               |                        |                             |

| APPRD.                                            |         |         |        |  |               |                        | GPD00294                    |

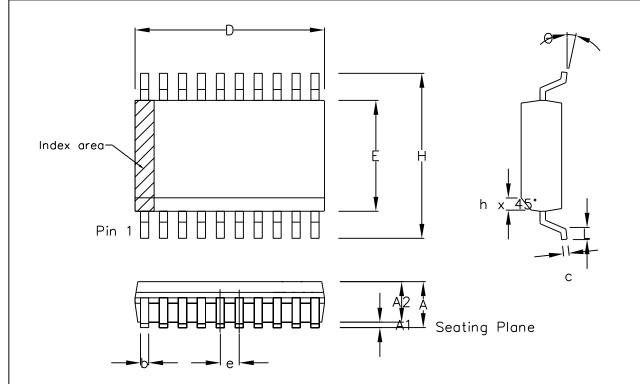

|        | <u> </u>     |          |       |    | • • •      |                | <u> </u> |  |  |  |

|--------|--------------|----------|-------|----|------------|----------------|----------|--|--|--|

|        |              | ol Dime  |       |    | Altern     | . Dimer        |          |  |  |  |

| Symbol | in ı         | millimet | res   |    | i          | <u>n inche</u> | S        |  |  |  |

|        | MIN          | Nominal  | MAX   |    | MIN        | Nominal        | MAX      |  |  |  |

| Α      | 2.35         |          | 2.65  |    | 0.093      |                | 0.104    |  |  |  |

| A1     | 0.10         |          | 0.30  |    | 0.004      |                | 0.012    |  |  |  |

| A2     | 2.25         |          | 2.35  |    | 0.089      |                | 0.092    |  |  |  |

| D      | 12.60        |          | 13.00 |    | 0.496      |                | 0.512    |  |  |  |

| Н      | 10.00        |          | 10.65 |    | 0.394      |                | 0.419    |  |  |  |

| Ε      | 7.40         |          | 7.60  |    | 0.291      |                | 0.299    |  |  |  |

| L      | 0.40         |          | 1.27  |    | 0.016      |                | 0.050    |  |  |  |

| е      | 1.1          | 27 BS    | C.    |    | 0.050 BSC. |                |          |  |  |  |

| b      | 0.33         |          | 0.51  |    | 0.013      |                | 0.020    |  |  |  |

| С      | 0.23         |          | 0.32  |    | 0.009      |                | 0.013    |  |  |  |

| θ      | 0°           |          | 8°    |    | 0°         |                | 8°       |  |  |  |

| h      | 0.25         |          | 0.75  |    | 0.010      |                | 0.029    |  |  |  |

|        | Pin features |          |       |    |            |                |          |  |  |  |

| Ν      | 20           |          |       |    |            |                |          |  |  |  |

| Cor    | form         | s to .   | JEDEC | MS | -013       | AC Iss         | s. C     |  |  |  |

## Notes:

- 1. The chamfer on the body is optional. If it not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- Dimension D do not include mould flash, protrusion or gate burrs. These shall not exceed 0.006" per side.

Dimension E1 do not include inter-lead flash or protrusion. These shall not exceed 0.010" per side.

Dimension b does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be 0.004"

- total in excess of b dimension.

| © Zarlink Semiconductor 2002 All rights reserved. |        |         |         |  |               |                        | Package Code                        |  |  |  |  |

|---------------------------------------------------|--------|---------|---------|--|---------------|------------------------|-------------------------------------|--|--|--|--|

| ISSUE                                             | 1      | 2       | 3       |  |               | Previous package codes | Package Outline for                 |  |  |  |  |

| ACN                                               | 6746   | 201941  | 213098  |  | SEMICONDUCTOR | MP/S                   | 20 lead SOIC<br>(0.300" Body Width) |  |  |  |  |

| DATE                                              | 7Apr95 | 27Feb97 | 15Jul02 |  |               |                        |                                     |  |  |  |  |

| APPRD.                                            |        |         |         |  |               |                        | GPD00015                            |  |  |  |  |

## For more information about all Zarlink products visit our Web Site at

## www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE