# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## MT9P401 1/2.5-Inch 5 Mp CMOS Digital Image Sensor

#### Table 1. KEY PERFORMANCE PARAMETERS

| Para                            | ameter            | Value                                                                            |  |  |

|---------------------------------|-------------------|----------------------------------------------------------------------------------|--|--|

| Optical Format                  |                   | 1/2.5-inch (4:3)                                                                 |  |  |

| Active Imager Size              |                   | 5.70 mm (H) x 4.28 mm (V)<br>7.13 mm Diagonal                                    |  |  |

| Active Pixels                   |                   | 2592 (H) x 1944 (V)                                                              |  |  |

| Pixel Size                      |                   | 2.2 x 2.2 μm                                                                     |  |  |

| Color Filter Array              |                   | RGB Bayer Pattern                                                                |  |  |

| Shutter Type                    |                   | Global Reset Release (GRR),<br>Snapshot Only<br>Electronic Rolling Shutter (ERS) |  |  |

| Maximum Data Ra<br>Master Clock | te/               | 96 Mp/s at 96 MHz (2.8 V I/O)<br>48 Mp/s at 48 MHz (1.8 V I/O)                   |  |  |

| Frame Rate                      | Full Resolution   | Programmable up to fps                                                           |  |  |

|                                 | HDTV (1280 x 720) | Programmable up to 60 fps                                                        |  |  |

| ADC Resolution                  |                   | 12–bit, On–chip                                                                  |  |  |

| Responsivity                    |                   | 1.4 V/lux-sec (550 nm)                                                           |  |  |

| Pixel Dynamic Ran               | ge                | 70.1 dB                                                                          |  |  |

| SNR <sub>MAX</sub>              |                   | 38.1 dB                                                                          |  |  |

| Supply Voltage                  | I/O               | 1.7–3.1 V                                                                        |  |  |

|                                 | Digital           | 1.7-1.9 V (1.8 V Nominal)                                                        |  |  |

|                                 | Analog            | 2.6-3.1 V (2.8 V Nominal)                                                        |  |  |

| Power Consumption               | n                 | 381 mW at 15 fps Full Resolution                                                 |  |  |

| Operating Tempera               | ature             | –30°C to +70°C                                                                   |  |  |

| Packaging                       |                   | 48-pin iLCC, Die                                                                 |  |  |

#### Features

- High Frame Rate

- Superior Low-light Performance

- Low Dark Current

- Global Reset Release, which Starts the Exposure of all Rows Simultaneously

- Bulb Exposure Mode, for Arbitrary Exposure Times

- Snapshot Mode to Take Frames on Demand

- Horizontal and Vertical Mirror Image

- Column and Row Skip Modes to Reduce Image Size without Reducing Field-of-view (FOV)

- Column and Row Binning Modes to Improve Image Quality when Resizing

#### **ON Semiconductor®**

www.onsemi.com

ILCC48 10x10 CASE 847AA

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

#### Features (continued)

- Simple Two-wire Serial Interface

- Programmable Controls: Gain, Frame Rate, Frame Size, Exposure

- Automatic Black Level Calibration

- On-chip Phase-locked Loop (PLL)

- 720p HDTV Video at 60 fps

#### Applications

- Digital Still Cameras

- Digital Video Cameras

- PC Cameras

- Converged DSCs/camcorders

- Cellular Phones

- PDAs

#### ORDERING INFORMATION

| Part Number              | Product Description | Orderable Product Attribute Description |

|--------------------------|---------------------|-----------------------------------------|

| MT9P401D00C18B-N3001-200 | VGA 1/3" GS CIS     | Die Sales, 200 μm Thickness             |

| MT9P401I12STC-DP         | 5 MP 1/2.5" CIS     | Dry Pack with Protective Film           |

| MT9P401I12STC-DR         | 5 MP 1/2.5" CIS     | Dry Pack without Protective Film        |

#### Table 2. AVAILABLE PART NUMBERS

#### **GENERAL DESCRIPTION**

The ON Semiconductor MT9P401 is a 1/2.5–inch CMOS active–pixel digital image sensor with an active imaging pixel array of 2592 (H)  $\times$  1944 (V). It incorporates sophisticated camera functions on–chip such as windowing, column and row skip mode, and snapshot mode. It is programmable through a simple two–wire serial interface.

The 5 Mp CMOS image sensor features ON Semiconductor's breakthrough low-noise CMOS imaging technology that achieves CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

The MT9P401 sensor can be operated in its default mode or programmed by the user for frame size, exposure, gain setting, and other parameters. The default mode outputs a full resolution image at 15 frames per second (fps). An on-chip analog-to-digital converter (ADC) provides 12 bits per pixel. FRAME\_VALID (FV) and LINE\_VALID (LV) signals are output on dedicated pins, along with a pixel clock that is synchronous with valid data.

TheMT9P401 produces extraordinarily clear, sharp digital pictures, and its ability to capture both continuous HDTV video and single frames makes it the perfect choice for a wide range of consumer and

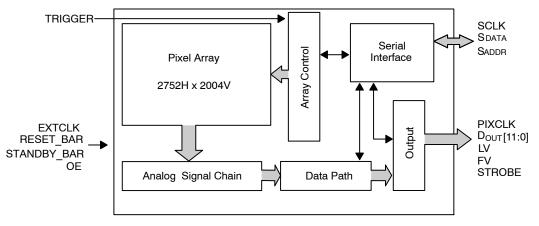

#### FUNCTIONAL OVERVIEW

The MT9P401 is a progressive–scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on–chip, phase–locked loop (PLL) to generate all internal clocks from a single master input clock running between 6 and 27 MHz. The maximum pixel rate is 96 Mp/s, corresponding to a clock rate of 96 MHz. Figure 1 illustrates a block diagram of the sensor.

Figure 1. Block Diagram

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 5 Mp active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain). The pixel data are output at a rate of up to 96 Mp/s, in addition to frame and line synchronization signals.

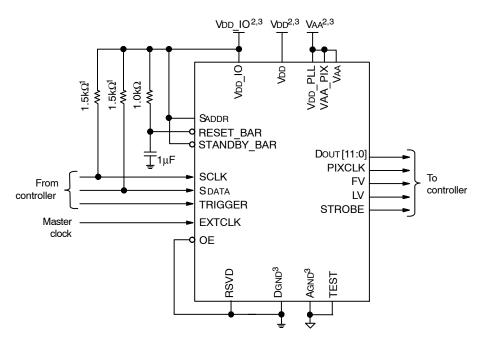

Figure 2. Typical Configuration (Connection)

NOTE:

1. A resistor value of 1.5 k $\Omega$  is recommended, but may be greater for slower two-wire speed.

2. All power supplies should be adequately decoupled.

3. All DGND pins must be tied together, as must all AGND pins, all VDD\_IO pins, and all VDD pins.

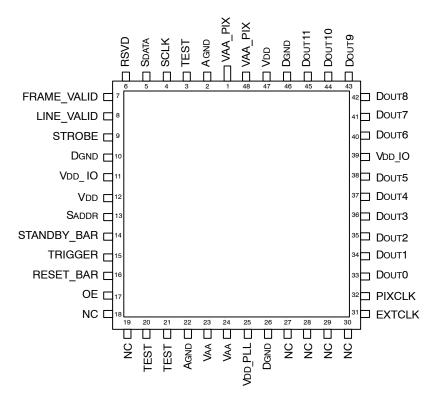

Figure 3. 48-Pin iLCC 10 x 10 Package Pinout Diagram (Top View)

#### Table 3. PIN DESCRIPTION

| Name        | Туре   | Description                                                                                                                                              |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_BAR   | Input  | When LOW, the MT9P401 asynchronously resets. When driven HIGH, it re-<br>sumes normal operation with all configuration registers set to factory defaults |

| EXTCLK      | Input  | External input clock                                                                                                                                     |

| SCLK        | Input  | Serial clock. Pull to VDD_IO with a 1.5 k $\Omega$ resistor                                                                                              |

| OE          | Input  | When HIGH, the PIXCLK, DOUT, FV, LV, and STROBE outputs enter a High–Z. When driven LOW, normal operation resumes                                        |

| STANDBY_BAR | Input  | Standby. When LOW, the chip enters a low-power standby mode. It resumes normal operation when the pin is driven HIGH                                     |

| TRIGGER     | Input  | Snapshot trigger. Used to trigger one frame of output in snapshot modes, and to indicate the end of exposure in bulb exposure modes                      |

| Saddr       | Input  | Serial address. When HIGH, the MT9P401 responds to device ID (BA)_H. When LOW, it responds to serial device ID (90)_H                                    |

| Sdata       | I/O    | Serial data. Pull to VDD_IO with a 1.5 k $\Omega$ resistor                                                                                               |

| PIXCLK      | Output | Pixel clock. The Dout, FV, LV, and STROBE outputs should be captured on the falling edge of this signal                                                  |

| Dout[11:0]  | Output | Pixel data. Pixel data is 12-bit. MSB (DOUT11) through LSB (DOUT0) of each pixel, to be captured on the falling edge of PIXCLK                           |

| FRAME_VALID | Output | Frame valid. Driven HIGH during active pixels and horizontal blanking of each frame and LOW during vertical blanking                                     |

| LINE_VALID  | Output | Line valid. Driven HIGH with active pixels of each line and LOW during blank-<br>ing periods                                                             |

| STROBE      | Output | Snapshot strobe. Driven HIGH when all pixels are exposing in snapshot modes                                                                              |

| Vdd         | Supply | Digital supply voltage. Nominally 1.8 V                                                                                                                  |

| VDD_IO      | Supply | IO supply voltage. Nominally 1.8 or 2.8 V                                                                                                                |

| Dgnd        | Supply | Digital ground                                                                                                                                           |

| VAA         | Supply | Analog supply voltage. Nominally 2.8 V                                                                                                                   |

| VAA_PIX     | Supply | Pixel supply voltage. Nominally 2.8 V, connected externally to VAA                                                                                       |

| Agnd        | Supply | Analog ground                                                                                                                                            |

| VDD_PLL     | Supply | PLL supply voltage. Nominally 2.8 V, connected externally to VAA                                                                                         |

| TEST        |        | Tie to AGND for normal device operation (factory use only)                                                                                               |

| RSVD        |        | Tie to DGND for normal device operation (factory use only)                                                                                               |

| NC          |        | No connect                                                                                                                                               |

#### **PIXEL DATA FORMAT**

#### **Pixel Array Structure**

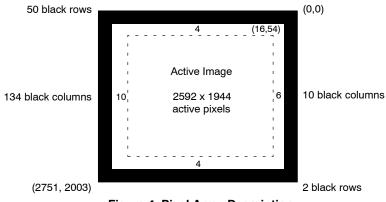

The MT9P401 pixel array consists of a 2752–column by 2004–row matrix of pixels addressed by column and row. The address (column 0, row 0) represents the upper–right corner of the entire array, looking at the sensor, as shown in Figure 4.

The array consists of a 2592–column by 1944–row active region in the center representing the default output image, surrounded by a boundary region (also active), surrounded by a border of dark pixels (see Table 4 and Table 5). The boundary region can be used to avoid edge effects when doing color processing to achieve a  $2592 \times 1944$  result image, while the optically black column and rows can be used to monitor the black level.

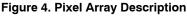

Pixels are output in a Bayer pattern format consisting of four "colors"–GreenR, GreenB, Red, and Blue (Gr, Gb, R, B)–representing three filter colors. When no mirror modes are enabled, the first row output alternates between Gr and R pixels, and the second row output alternates between B and Gb pixels. The Gr and Gb pixels have the same color filter, but they are treated as separate colors by the data path and analog signal chain.

#### Table 4. PIXEL TYPE BY COLUMN

| Column    | Pixel Type           |  |  |

|-----------|----------------------|--|--|

| 0–9       | Dark (10)            |  |  |

| 10–15     | Active boundary (6)  |  |  |

| 16–2607   | Active image (2592)  |  |  |

| 2608–2617 | Active boundary (10) |  |  |

| 2618–2751 | Dark (134)           |  |  |

#### Table 5. PIXEL TYPE BY ROW

| Column    | Pixel Type          |  |  |

|-----------|---------------------|--|--|

| 0–49      | Dark (50)           |  |  |

| 50–53     | Active boundary (4) |  |  |

| 54–1997   | Active image (1944) |  |  |

| 1998–2001 | Active boundary (3) |  |  |

| 2002–2003 | Dark (2)            |  |  |

Figure 5. Pixel Color Pattern Detail (Top Right Corner)

#### **Default Readout Order**

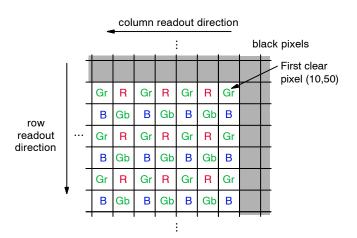

By convention, the sensor core pixel array is shown with pixel (0,0) in the top right corner (see Figure 4). This reflects the actual layout of the array on the die. Also, the first pixel data read out of the sensor in default condition is that of pixel (16, 54).

When the sensor is imaging, the active surface of the sensor faces the scene as shown in Figure 5. When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced as shown in Figure 6.

#### Figure 6. Imaging a Scene

#### **Output Data Format (Default Mode)**

The MT9P401 image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking

and vertical blanking, as shown in Figure 7. LV is HIGH during the shaded region of the figure. FV timing is described in "Output Data Timing".

| P <sub>0,0</sub> P <sub>0,1</sub> P <sub>0,2</sub> P <sub>0,n-1</sub> P <sub>0,n</sub>                                             | 00 00 00 00 00 00                      |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| P <sub>1,0</sub> P <sub>1,1</sub> P <sub>1,2</sub> P <sub>1,n-1</sub> P <sub>1,n</sub>                                             | 00 00 00 00 00 00                      |

| VALID IMAGE                                                                                                                        | HORIZONTAL<br>BLANKING                 |

| $\begin{array}{c} P_{m-1,0} \; P_{m-1,1} \; P_{m-1,n-1} \; \; P_{m-1,n} \\ P_{m,0} \; P_{m,1} \; P_{m,n-1} \; P_{m,n} \end{array}$ | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

| 00 00 00 00 00 00                                                                                                                  | 00 00 00 00 00 00                      |

| 00 00 00 00 00 00                                                                                                                  | 00 00 00 00 00 00                      |

| VERTICAL BLANKING                                                                                                                  | VERTICAL/HORIZONTAL<br>BLANKING        |

| 00 00 00 00 00 00                                                                                                                  | 00 00 00 00 00 00                      |

| 00 00 00 00 00 00                                                                                                                  | 00 00 00 00 00 00 00                   |

#### Figure 7. Spatial Illustration of Image Readout

#### **Readout Sequence**

Typically, the readout window is set to a region including only active pixels. The user has the option of reading out dark regions of the array, but if this is done, consideration must be given to how the sensor reads the dark regions for its own purposes.

1. Dark rows:

If Show\_Dark\_Rows is set, or if Manual\_BLC is clear, dark rows on the top of the array are read out. The set of rows sampled are adjusted based on the Row\_Bin setting such that there are 8 rows after binning, as shown in the Table 6. The Row Skip setting is ignored for the dark row

region.

If Show\_Dark\_Rows is clear and Manual\_BLC is set, no dark rows are read from the array as part of this step, allowing all rows to be part of the active image. This does not change the frame time, as H<sub>DR</sub> is included in the vertical blank period.

2. Active image:

The rows defined by the row start, row size, bin, skip, and row mirror settings are read out. If this set of rows includes rows read out above, those rows are resampled, meaning that the data is invalid.

Table 6. DARK ROWS SAMPLED AS A FUNCTION OF ROW\_BIN

| Row_Bin | H <sub>DR</sub> (Dark Rows After Binning) |

|---------|-------------------------------------------|

| 0       | 8                                         |

| 1       | 8                                         |

| 3       | 8                                         |

Columns are read out in the following order:

1. Dark columns:

If either Show\_Dark\_Columns or Row\_BLC is set, dark columns on the left side of the image are read out followed by those on the right side. The set of columns read is shown in Table 7. The Column\_Skip setting is ignored for the dark columns.

If neither Show\_Dark\_Columns nor Row\_BLC is set, no dark columns are read, allowing all columns to be part of the active image. This does not change the row time, as  $W_{DC}$  is included in the vertical blank period.

2. Active image:

The columns defined by column start, column size, bin, skip, and column mirror settings are read out. If this set of columns includes the columns read out above, these columns are resampled, meaning the data is invalid.

#### Table 7. DARK COLUMNS SAMPLED AS A FUNCTION OF COLUMN\_BIN

| Column_Bin | W <sub>DC</sub> (Dark Columns After Binning) |

|------------|----------------------------------------------|

| 0          | 80                                           |

| 1          | 40                                           |

| 3          | 20                                           |

#### **OUTPUT DATA TIMING**

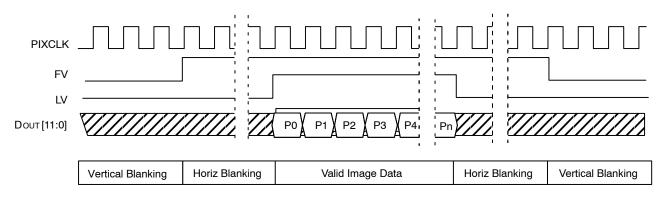

The output images are divided into frames, which are further divided into lines. By default, the sensor produces 1944 rows of 2592 columns each. The FV and LV signals indicate the boundaries between frames and lines, respectively. PIXCLK can be used as a clock to latch the data. For each PIXCLK cycle, one 12-bit pixel datum outputs on the DOUT pins. When both FV and LV are asserted, the pixel is valid. PIXCLK cycles that occur when FV is negated are called vertical blanking. PIXCLK cycles that occur when only LV is negated are called horizontal blanking.

Figure 8. Default Pixel Output Timing

#### LV and FV

The timing of the FV and LV outputs is closely related to the row time and the frame time.

FV will be asserted for an integral number of row times, which will normally be equal to the height of the output image. If Show\_Dark\_Rows is set, the dark sample rows will be output before the active image, and FV will be extended to include them. In this case, FV's leading edge happens at time 0.

LV will be asserted during the valid pixels of each row. The leading edge of LV will be offset from the leading edge of FV by 609 PIXCLKs. If Show\_Dark\_Columns is set, the dark columns will be output before the image pixels, and LV will be extended back to include them; in this case, the first pixel of the active image still occurs at the same position relative to the leading edge of FV. Normally, LV will only be asserted if FV is asserted; this is configurable as described below.

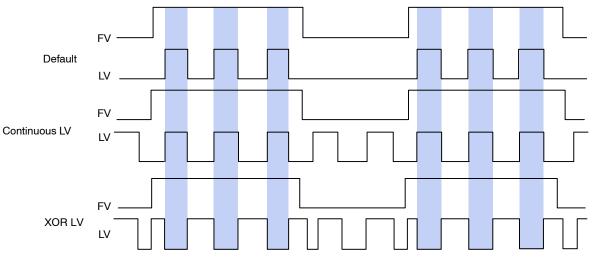

#### LV Format Options

The default situation is for LV to be negated when FV is negated. The other option available is shown in Figure 9. If Continuous\_LV is set, LV is asserted even when FV is not, with the same period and duty cycle. If XOR\_Line\_Valid is set, but not Continuous\_Line\_Valid, the resulting LV will be the XOR of FV and the continuous LV.

Figure 9. LV Format Options

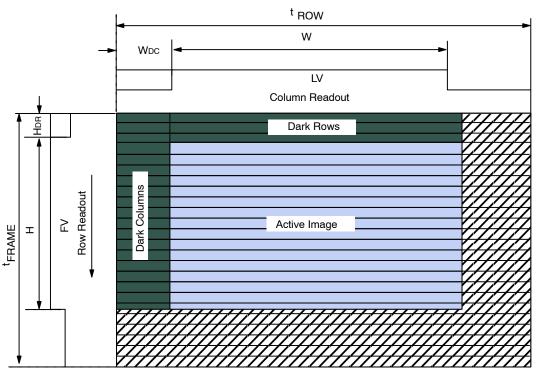

The timing of an entire frame is shown in Figure 10.

Figure 10. Frame Timing

#### Frame Time

The pixel clock (PIXCLK) represents the time needed to sample 1 pixel from the array, and is typically equal to 1 EXTCLK period. The sensor outputs data at the maximum rate of 1 pixel per PIXCLK. One row time (<sup>t</sup>ROW) is the period from the first pixel output in a row to the first pixel output in the next row. The row time and frame time are defined by equations in Table 8.

#### Table 8. FRAME TIME

| Parameters               | Name                        | Equation                                                                                               | Default Timing at<br>EXTCLK = 96 MHz |  |  |

|--------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| fps                      | Frame Rate                  | 1/ <sup>t</sup> FRAME                                                                                  | 14                                   |  |  |

| <sup>t</sup> FRAME       | Frame Time                  | (H + max(VB, VBMIN)) $\times$ tROW                                                                     | 71.66 ms                             |  |  |

| <sup>t</sup> ROW         | Row Time                    | 2 × <sup>t</sup> PIXCLK × max(((W/2) + max(HB, HB <sub>MIN</sub> )),<br>(41 + 346 × (Row_Bin+1) + 99)) | 36.38 μs                             |  |  |

| <sup>t</sup> ROW_Default | Row Time                    |                                                                                                        |                                      |  |  |

| <sup>t</sup> ROW_HDTV    | Row Time                    | 2 × <sup>t</sup> PIXCLK × max(((W/2) + max(HB, HBMIN)),<br>(41 + 186 × (Row_Bin+1) + 99))              | 24.4 μs                              |  |  |

| W                        | Output Image Width          | $2 \times \text{ceil}((\text{Column}_\text{Size} + 1) / (2 \times (\text{Column}_\text{Skip} + 1)))$   | 2592 PIXCLK                          |  |  |

| Н                        | Output Image Height         | 2 × ceil((Row_Size + 1) / (2 × (Row_Skip + 1)))                                                        | 1944 rows                            |  |  |

| SW                       | Shutter Width               | max (1, (2 16 × Shutter_Width_Upper)<br>+ Shutter_Width_Lower)                                         | 1943 rows                            |  |  |

| HB                       | Horizontal Blanking         | Horizontal_Blank + 1                                                                                   | 1 PIXCLK                             |  |  |

| VB                       | Vertical Blanking           | Vertical_Blank + 1                                                                                     | 26 rows                              |  |  |

| НВмім                    | Minimum Horizontal Blanking | 346 × (Row_Bin + 1) + 64 + (WDC / 2)                                                                   | 450 PIXCLK                           |  |  |

| VBMIN                    | Minimum Vertical Blanking   | max (8, SW – H) + 1                                                                                    | 9 rows                               |  |  |

| <sup>t</sup> PIXCLK      | Pixclk Period               | 1/ <sup>f</sup> PIXCLK                                                                                 | 10.42 ns                             |  |  |

#### CONFIDENTIAL AND PROPRIETARY NOT FOR PUBLIC RELEASE

The minimum horizontal blanking (HBMIN) values for various Row\_Bin and Column\_Bin settings are shown in Table 9.

#### Table 9. HB<sub>MIN</sub> VALUES FOR ROW\_BIN VS. COLUMN\_BIN SETTINGS

|         | Column_bin (W <sub>DC</sub> ) |      |      |      |  |  |  |  |

|---------|-------------------------------|------|------|------|--|--|--|--|

| Row_bin |                               | 0    | 1    | 3    |  |  |  |  |

|         | 0                             | 450  | 430  | 420  |  |  |  |  |

|         | 1                             | 796  | 776  | 766  |  |  |  |  |

|         | 3                             | 1488 | 1468 | 1458 |  |  |  |  |

#### Frame Rates at Common Resolutions

Table 10 and Table 11 show examples of register settings to achieve common resolutions and their frame rates. Frame

rates are shown both with subsampling enabled and disabled.

#### Table 10. STANDARD RESOLUTIONS

| Resolution                       | Frame<br>Rate | Sub–<br>sampling<br>Mode | Column_<br>Size<br>(R0x04) | Row_<br>Size<br>(R0x03) | Shutter_<br>Width_<br>Lower<br>(R0x09) | Row_<br>Bin<br>(R0x22<br>[5:4]) | Row_<br>Skip<br>(R0x22<br>[2:0]) | Column_<br>Bin<br>(R0x23<br>[5:4]) | Column_<br>Skip<br>(R0x23<br>[2:0]) |

|----------------------------------|---------------|--------------------------|----------------------------|-------------------------|----------------------------------------|---------------------------------|----------------------------------|------------------------------------|-------------------------------------|

| 2592 x 1944<br>(Full Resolution) | 14            | N/A                      | 2591                       | 1943                    | <1943                                  | 0                               | 0                                | 0                                  | 0                                   |

| 2048 x 1536 QXGA                 | 21            | N/A                      | 2047                       | 1535                    | <1535                                  | 0                               | 0                                | 0                                  | 0                                   |

| 1600 x 1200 UXGA                 | 31            | N/A                      | 1599                       | 1199                    | <1199                                  | 0                               | 0                                | 0                                  | 0                                   |

| 1280 x 1024 SXGA                 | 42            | N/A                      | 1279                       | 1023                    | <1023                                  | 0                               | 0                                | 0                                  | 0                                   |

| 1024 x 768 XGA                   | 63            | N/A                      | 1023                       | 767                     | <767                                   | 0                               | 0                                | 0                                  | 0                                   |

|                                  | 63            | Skipping                 | 2047                       | 1535                    |                                        | 0                               | 1                                | 0                                  | 1                                   |

|                                  | 47            | Binning                  | 2047                       | 1535                    |                                        | 1                               | 1                                | 1                                  | 1                                   |

| 800 x 600 SVGA                   | 90            | N/A                      | 799                        | 599                     | <599                                   | 0                               | 0                                | 0                                  | 0                                   |

|                                  | 90            | Skipping                 | 1599                       | 1199                    |                                        | 0                               | 1                                | 0                                  | 1                                   |

|                                  | 65            | Binning                  | 1599                       | 1199                    |                                        | 1                               | 1                                | 1                                  | 1                                   |

| 640 x 480 VGA                    | 123           | N/A                      | 639                        | 479                     | <479                                   | 0                               | 0                                | 0                                  | 0                                   |

|                                  | 123           | Skipping                 | 2559                       | 1919                    |                                        | 0                               | 3                                | 0                                  | 3                                   |

|                                  | 53            | Binning                  | 2559                       | 1919                    |                                        | 3                               | 3                                | 3                                  | 3                                   |

#### Table 11. WIDE SCREEN (16:9) RESOLUTIONS

| Resolution       | Frame<br>Rate | Sub–<br>sampling<br>Mode | Column_<br>Size<br>(R0x04) | Row_<br>Size<br>(R0x03) | Shutter_<br>Width_<br>Lower<br>(R0x09) | Row_<br>Bin<br>(R0x22<br>[5:4]) | Row_<br>Skip<br>(R0x22<br>[2:0]) | Column_<br>Bin<br>(R0x23<br>[5:4]) | Column_<br>Skip<br>(R0x23<br>[2:0]) |

|------------------|---------------|--------------------------|----------------------------|-------------------------|----------------------------------------|---------------------------------|----------------------------------|------------------------------------|-------------------------------------|

| 1920 x 1080 HDTV | 31            | N/A                      | 1919                       | 1079                    | <1079                                  | 0                               | 0                                | 0                                  | 0                                   |

| 1280 x 720 HDTV  | 60            | Binning                  | 2559                       | 1439                    | <719                                   | 1                               | 1                                | 1                                  | 1                                   |

1. It is assumed that the minimum horizontal blanking and the minimum vertical blanking conditions are met, and that all other registers are set to default values. Please refer to TN09111 for instructions on how to configure 720p HDTV.

#### SERIAL BUS DESCRIPTION

Registers are written to and read from the MT9P401 through the two-wire serial interface bus. The MT9P401 is a serial interface slave and is controlled by the serial clock (SCLK), which is driven by the serial interface master. Data is transferred into and out of the MT9P401 through the serial data (SDATA) line. The SDATA line is pulled up to VDD\_IO off-chip by a 1.5 k $\Omega$  resistor. Either the slave or master device can pull the SDATA line LOW—the serial interface protocol determines which device is allowed to pull the SDATA line down at any given time.

#### Protocol

The two-wire serial defines several different transmission codes, as follows:

- 1. a start bit

- 2. the slave device 8-bit address

- 3. an (a no) acknowledge bit

- 4. an 8-bit message

- 5. a stop bit

#### Sequence

A typical READ or WRITE sequence begins by the master sending a start bit. After the start bit, the master sends the slave device's 8-bit address. The last bit of the address determines if the request is a READ or a WRITE, where a "0" indicates a WRITE and a "1" indicates a READ. The slave device acknowledges its address by sending an acknowledge bit back to the master.

If the request is a WRITE, the master then transfers the 8-bit register address to which a WRITE should take place. The slave sends an acknowledge bit to indicate that the register address has been received. The master then transfers the data 8 bits at a time, with the slave sending an acknowledge bit after each 8 bits. The MT9P401 uses 16-bit data for its internal registers, thus requiring two 8-bit transfers to write to one register. After 16 bits are transferred, the register address is automatically incremented, so that the next 16 bits are written to the next register address. The master stops writing by sending a start or stop bit.

A typical READ sequence is executed as follows. First the master sends the write-mode slave address and 8-bit register address, just as in the WRITE request. The master then sends a start bit and the read-mode slave address. The master then clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The register address is automatically-incremented after every 16 bits is transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

#### **Bus Idle State**

The bus is idle when both the data and clock lines are HIGH. Control of the bus is initiated with a start bit, and the bus is released with a stop bit. Only the master can generate the start and stop bits.

#### Start Bit

The start bit is defined as a HIGH-to-LOW transition of the data line while the clock line is HIGH.

#### Stop Bit

The stop bit is defined as a LOW-to-HIGH transition of the data line while the clock line is HIGH.

#### Slave Address

The 8-bit address of a two-wire serial interface device consists of 7 bits of address and 1 bit of direction. A "0" in the LSB (least significant bit) of the address indicates write mode (0xBA), and a "1" indicates read mode (0xBB).

#### Data Bit Transfer

One data bit is transferred during each clock pulse. The serial interface clock pulse is provided by the master. The data must be stable during the HIGH period of the two-wire serial interface clock-it can only change when the serial clock is LOW. Data is transferred 8 bits at a time, followed by an acknowledge bit.

#### Acknowledge Bit

The master generates the acknowledge clock pulse. The transmitter (which is the master when writing, or the slave when reading) releases the data line, and the receiver indicates an acknowledge bit by pulling the data line LOW during the acknowledge clock pulse.

#### No-Acknowledge Bit

The no-acknowledge bit is generated when the data line is not pulled down by the receiver during the acknowledge clock pulse. A no-acknowledge bit is used to terminate a read sequence.

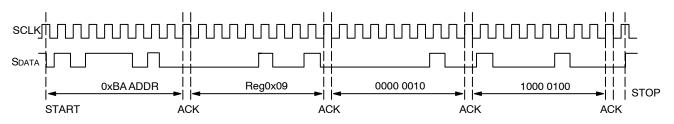

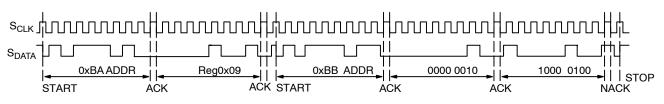

#### TWO-WIRE SERIAL INTERFACE SAMPLE WRITE AND READ SEQUENCES

#### **16-Bit WRITE Sequence**

A typical WRITE sequence for writing 16 bits to a register is shown in Figure 11. A start bit given by the master, followed by the write address, starts the sequence. The image sensor then gives an acknowledge bit and expects the register address to come first, followed by the 16-bit data. After each 8-bit transfer, the image sensor gives an acknowledge bit. All 16 bits must be written before the register is updated. After 16 bits are transferred, the register address is automatically incremented so that the next 16 bits are written to the next register. The master stops writing by sending a start or stop bit.

Figure 11. Timing Diagram Showing a WRITE to Reg0x09 with the Value 0x0284

#### **16-Bit READ Sequence**

A typical READ sequence is shown in Figure 12. First the master has to write the register address, as in a WRITE sequence. Then a start bit and the read address specify that a READ is about to happen from the register. The master

then clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The register address should be incremented after every 16 bits is transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

Figure 12. Timing Diagram Showing a READ to Reg0x09 with the Value 0x0284

#### REGISTERS

#### **Register List**

Table 12 lists sensor registers and their default values.

#### Table 12. REGISTER LIST AND DEFAULT VALUES

| Register # Dec (Hex) | Register Description | Data Format (Binary)       | Default Value Dec (Hex) |  |

|----------------------|----------------------|----------------------------|-------------------------|--|

| R0:0(R0x000)         | Chip Version         | ???? ???? ???? ????        | 6145 (0x1801)           |  |

| R1:0(R0x001)         | Row Start            | 0000 0ddd dddd dddd        | 54 (0x0036)             |  |

| R2:0(R0x002)         | Column Start         | 0000 dddd dddd dddd        | 16 (0x0010)             |  |

| R3:0(R0x003)         | Row Size             | 0000 0ddd dddd dddd        | 1943 (0x0797)           |  |

| R4:0(R0x004)         | Column Size          | 0000 dddd dddd dddd        | 2591 (0x0A1F)           |  |

| R5:0(R0x005)         | Horizontal Blank     | 0000 dddd dddd dddd        | 0 (0x0000)              |  |

| R6:0(R0x006)         | Vertical Blank       | 0000 0ddd dddd dddd        | 25 (0x0019)             |  |

| R7:0(R0x007)         | Output Control       | 0d0d dddd dddd dddd        | 8066 (0x1F82)           |  |

| R8:0(R0x008)         | Shutter Width Upper  | 0000 0000 0000 dddd        | 0 (0x0000)              |  |

| R9:0(R0x009)         | Shutter Width Lower  | dddd dddd dddd dddd        | 1943 (0x0797)           |  |

| R10:0(R0x00A)        | Pixel Clock Control  | d000 0ddd 0ddd dddd        | 0 (0x0000)              |  |

| R11:0(R0x00B)        | Restart              | 0000 0000 0000 0ddd        | 0 (0x0000)              |  |

| R12:0(R0x00C)        | Shutter Delay        | 000d dddd dddd dddd        | 0 (0x0000)              |  |

| R13:0(R0x00D)        | Reset                | 0000 0000 0000 000d        | 0 (0x0000)              |  |

| R15:0(R0x00F)        | Reserved             | -                          | 0 (0x0000)              |  |

| R16:0(R0x010)        | PLL Control          | ddd0 000d dddd 00dd        | 80 (0x0050)             |  |

| R17:0(R0x011)        | PLL Config 1         | dddd dddd 00dd dddd        | 25604 (0x6404)          |  |

| R18:0(R0x012)        | PLL Config 2         | 000d dddd 000d dddd        | 0 (0x0000)              |  |

| R20:0(R0x014)        | Reserved             | -                          | 54 (0x0036)             |  |

| R21:0(R0x015)        | Reserved             | -                          | 16 (0x0010)             |  |

| R30:0(R0x01E)        | Read Mode 1          | Oddd dddd dddd dddd        | 16390 (0x4006)          |  |

| R32:0(R0x020)        | Read Mode 2          | dddd d000 0ddd 00d0        | 64 (0x0040)             |  |

| R34:0(R0x022)        | Row Address Mode     | 0ddd 0ddd 00dd 0ddd        | 0 (0x0000)              |  |

| R35:0(R0x023)        | Column Address Mode  | 0000 0ddd 00dd 0ddd        | 0 (0x0000)              |  |

| R36:0(R0x024)        | Reserved             | -                          | 2 (0x0002)              |  |

| R39:0(R0x027)        | Reserved             | -                          | 11 (0x000B)             |  |

| R41:0(R0x029)        | Reserved             | -                          | 1153 (0x0481)           |  |

| R42:0(R0x02A)        | Reserved             | -                          | 4230 (0x1086)           |  |

| R43:0(R0x02B)        | Green1 Gain          | Oddd dddd dddd dddd        | 8 (0x0008)              |  |

| R44:0(R0x02C)        | Blue Gain            | 0ddd dddd dddd dddd        | 8 (0x0008)              |  |

| R45:0(R0x02D)        | Red Gain             | 0ddd dddd dddd dddd        | 8 (0x0008)              |  |

| R46:0(R0x02E)        | Green2 Gain          | Green2 Gain 0ddd dddd dddd |                         |  |

| R48:0(R0x030)        | Reserved             | Reserved –                 |                         |  |

| R50:0(R0x032)        | Reserved             | -                          | 0 (0x0000)              |  |

| R53:0(R0x035)        | Global Gain          | dddd dddd dddd 8 (0x0008)  |                         |  |

| R60:0(R0x03C)        | Reserved             | -                          | 4112 (0x1010)           |  |

| R61:0(R0x03D)        | Reserved             | -                          | 5 (0x0005)              |  |

#### Table 12. REGISTER LIST AND DEFAULT VALUES (continued)

| Register # Dec (Hex)   | Register Description | Data Format (Binary) | Default Value Dec (Hex) |  |

|------------------------|----------------------|----------------------|-------------------------|--|

| R62:0(R0x03E) Reserved |                      | -                    | 64 (0x80C7)             |  |

| R63:0(R0x03F)          | Reserved             | -                    | 4 (0x0004)              |  |

| R64:0(R0x040)          | Reserved             | _                    | 7 (0x0007)              |  |

| R65:0(R0x041)          | Reserved             | _                    | 3 (0x0000)              |  |

| R66:0(R0x042)          | Reserved             | _                    | 5 (0x0003)              |  |

| R67:0(R0x043)          | Reserved             | -                    | 1 (0x0003)              |  |

| R68:0(R0x044)          | Reserved             | _                    | 515 (0x0203)            |  |

| R69:0(R0x045)          | Reserved             | -                    | 4112 (0x1010)           |  |

| R70:0(R0x046)          | Reserved             | -                    | 4112 (0x1010)           |  |

| R71:0(R0x047)          | Reserved             | -                    | 4112 (0x1010)           |  |

| R72:0(R0x048)          | Reserved             | -                    | 16 (0x0010)             |  |

| R73:0(R0x049)          | Reserved             | _                    | 168 (0x00A8)            |  |

| R74:0(R0x04A)          | Reserved             | _                    | 16 (0x0010)             |  |

| R75:0(R0x04B)          | Reserved             | _                    | 40 (0x0028)             |  |

| R76:0(R0x04C)          | Reserved             | -                    | 16 (0x0010)             |  |

| R77:0(R0x04D)          | Reserved             | -                    | 8224 (0x2020)           |  |

| R78:0(R0x04E)          | Reserved             | -                    | 4112 (0x1010)           |  |

| R79:0(R0x04F)          | Reserved             | -                    | 23 (0x0014)             |  |

| R80:0(R0x050)          | Reserved             | _                    | 32768 (0x8000)          |  |

| R81:0(R0x051)          | Reserved             | _                    | 7 (0x0007)              |  |

| R82:0(R0x052)          | Reserved             | -                    | 32768 (0x8000)          |  |

| R83:0(R0x053)          | Reserved             | -                    | 7 (0x0007)              |  |

| R84:0(R0x054)          | Reserved             | -                    | 8 (0x0008)              |  |

| R86:0(R0x056)          | Reserved             | Reserved –           |                         |  |

| R87:0(R0x057)          | Reserved             | -                    | 4 (0x0004)              |  |

| R88:0(R0x058)          | Reserved             | -                    | 32768 (0x8000)          |  |

| R89:0(R0x059)          | Reserved             | -                    | 7 (0x0007)              |  |

| R90:0(R0x05A)          | Reserved             | -                    | 4 (0x0004)              |  |

| R91:0(R0x05B)          | Reserved             | _                    | 1 (0x0001)              |  |

| R92:0(R0x05C)          | Reserved             | -                    | 90 (0x005A)             |  |

| R93:0(R0x05D)          | Reserved             | -                    | 11539 (0x2D13)          |  |

| R94:0(R0x05E)          | Reserved             | _                    | 16895 (0x41FF)          |  |

| R95:0(R0x05F)          | Reserved             | _                    | 8989 (0x231D)           |  |

| R96:0(R0x060)          | Reserved             | _                    | 32 (0x0020)             |  |

| R97:0(R0x061)          | Reserved             | Reserved –           |                         |  |

| R98:0(R0x062)          | Reserved             | Reserved –           |                         |  |

| R99:0(R0x063)          | Reserved             | _                    | 32 (0x0020)             |  |

| R100:0(R0x064)         | Reserved             | -                    | 32 (0x0020)             |  |

| R101:0(R0x065)         | Reserved             | _                    | 0 (0x0000)              |  |

| R104:0(R0x068)         | Reserved             | _                    | 0 (0x0000)              |  |

| R105:0(R0x069)         | Reserved             | _                    | 0 (0x0000)              |  |

#### Table 12. REGISTER LIST AND DEFAULT VALUES (continued)

| Register # Dec (Hex) | Register Description | Data Format (Binary) | Default Value Dec (Hex) |  |

|----------------------|----------------------|----------------------|-------------------------|--|

| R106:0(R0x06A)       | Reserved             | _                    | 0 (0x0000)              |  |

| R107:0(R0x06B)       | Reserved             | -                    | 0 (0x0000)              |  |

| R108:0(R0x06C)       | Reserved             | -                    | 0 (0x0000)              |  |

| R109:0(R0x06D)       | Reserved             | -                    | 0 (0x0000)              |  |

| R112:0(R0x070)       | Reserved             | -                    | 103 (0x00AC)            |  |

| R113:0(R0x071)       | Reserved             | -                    | 25604 (0xA700)          |  |

| R114:0(R0x072)       | Reserved             | _                    | 25094 (0xA700)          |  |

| R115:0(R0x073)       | Reserved             | _                    | 5128 (0x0C00)           |  |

| R116:0(R0x074)       | Reserved             | -                    | 5642 (0x0600)           |  |

| R117:0(R0x075)       | Reserved             | -                    | 13068 (0x5 617)         |  |

| R118:0(R0x076)       | Reserved             | -                    | 18229 (0x6B57)          |  |

| R119:0(R0x077)       | Reserved             | _                    | 18743 (0x6B57)          |  |

| R120:0(R0x078)       | Reserved             | _                    | 24633 (0xA500)          |  |

| R121:0(R0x079)       | Reserved             | _                    | 26114 (0xAB00)          |  |

| R122:0(R0x07A)       | Reserved             | _                    | 25604 (0xA904)          |  |

| R123:0(R0x07B)       | Reserved             | -                    | 25094 (0xA700)          |  |

| R124:0(R0x07C)       | Reserved             | -                    | 25094 (0xA700)          |  |

| R125:0(R0x07D)       | Reserved             | _                    | 65280 (0xFF00)          |  |

| R126:0(R0x07E)       | Reserved             | -                    | 25608 (0xA900)          |  |

| R127:0(R0x07F)       | Reserved             | -                    | 25604 (0x6404)          |  |

| R128:0(R0x080)       | Reserved             | =                    | 34 (0x0022)             |  |

| R129:0(R0x081)       | Reserved             | -                    | 7940 (0x1F04)           |  |

| R130:0(R0x082)       | Reserved             | -                    | 0 (0x0000)              |  |

| R131:0(R0x083)       | Reserved             | -                    | 6918 (0x1B06)           |  |

| R132:0(R0x084)       | Reserved             | _                    | 7432 (0x1D08)           |  |

| R134:0(R0x086)       | Reserved             | _                    | 6150 (0x1806)           |  |

| R135:0(R0x087)       | Reserved             | _                    | 6664 (0x1A08)           |  |

| R144:0(R0x090)       | Reserved             | _                    | 2000 (0x07D0)           |  |

| R145:0(R0x091)       | Reserved             | _                    | 0 (0x0000)              |  |

| R146:0(R0x092)       | Reserved             | _                    | 1 (0x0001)              |  |

| R147:0(R0x093)       | Reserved             | -                    | 0 (0x0000)              |  |

| R149:0(R0x095)       | Reserved             | -                    | 0 (0x0000)              |  |

| R150:0(R0x096)       | Reserved             | _                    | 0 (0x0000)              |  |

| R151:0(R0x097)       | Reserved             | -                    | 0 (0x0000)              |  |

| R152:0(R0x098)       | Reserved             | _                    | 0 (0x0000)              |  |

| R153:0(R0x099)       | Reserved             | _                    | 0 (0x0000)              |  |

| R154:0(R0x09A)       | Reserved             | -                    | 0 (0x0000)              |  |

| R155:0(R0x09B)       | Reserved             | -                    | 0 (0x0000)              |  |

| R156:0(R0x09C)       | Reserved             | -                    | 0 (0x0000)              |  |

| R160:0(R0x0A0)       | Test_Pattern_Control | _                    | 0 (0x0000)              |  |

| R161:0(R0x0A1)       | Test_Pattern_Green   | _                    | 0 (0x0000)              |  |

#### Table 12. REGISTER LIST AND DEFAULT VALUES (continued)

| Register # Dec (Hex)            | Register Description   | Data Format (Binary) | Default Value Dec (Hex |  |

|---------------------------------|------------------------|----------------------|------------------------|--|

| R162:0(R0x0A2) Test_Pattern_Red |                        | -                    | 0 (0x0000)             |  |

| R163:0(R0x0A3)                  | Test_Pattern_Blue      | -                    | 0 (0x0000)             |  |

| R164:0(R0x0A4)                  | Test_Pattern_Bar_Width | -                    | 0 (0x0000)             |  |

| R165:0(R0x0A5)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R166:0(R0x0A6)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R167:0(R0x0A7)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R168:0(R0x0A8)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R169:0(R0x0A9)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R170:0(R0x0AA)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R171:0(R0x0AB)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R172:0(R0x0AC)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R173:0(R0x0AD)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R174:0(R0x0AE)                  | Reserved               | -                    | 32 (0x0020)            |  |

| R175:0(R0x0AF)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R176:0(R0x0B0)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R177:0(R0x0B1)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R178:0(R0x0B2)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R179:0(R0x0B3)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R180:0(R0x0B4)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R181:0(R0x0B5)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R182:0(R0x0B6)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R183:0(R0x0B7)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R184:0(R0x0B8)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R185:0(R0x0B9)                  | Reserved               | Reserved –           |                        |  |

| R186:0(R0x0BA)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R187:0(R0x0BB)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R188:0(R0x0BC)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R189:0(R0x0BD)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R190:0(R0x0BE)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R191:0(R0x0BF)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R192:0(R0x0C0)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R193:0(R0x0C1)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R194:0(R0x0C2)                  | Reserved               | _                    | 0 (0x0000)             |  |

| R195:0(R0x0C3)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R196:0(R0x0C4)                  | Reserved               | Reserved –           |                        |  |

| R197:0(R0x0C5)                  | Reserved               | Reserved –           |                        |  |

| R198:0(R0x0C6)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R199:0(R0x0C7)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R200:0(R0x0C8)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R201:0(R0x0C9)                  | Reserved               | -                    | 0 (0x0000)             |  |

| R202:0(R0x0CA)                  | Reserved               | -                    | 0 (0x0000)             |  |

#### Table 12. REGISTER LIST AND DEFAULT VALUES (continued)

| Register # Dec (Hex)    | Register Description | Data Format (Binary) | Default Value Dec (Hex) |  |

|-------------------------|----------------------|----------------------|-------------------------|--|

| R203:0(R0x0CB) Reserved |                      | -                    | 0 (0x0000)              |  |

| R204:0(R0x0CC)          | Reserved             | -                    | 0 (0x0000)              |  |

| R205:0(R0x0CD)          | Reserved             | _                    | 0 (0x0000)              |  |

| R206:0(R0x0CE)          | Reserved             | -                    | 0 (0x0000)              |  |

| R207:0(R0x0CF)          | Reserved             | -                    | 0 (0x0000)              |  |

| R208:0(R0x0D0)          | Reserved             | -                    | 0 (0x0000)              |  |

| R209:0(R0x0D1)          | Reserved             | _                    | 0 (0x0000)              |  |

| R210:0(R0x0D2)          | Reserved             | -                    | 0 (0x0000)              |  |

| R211:0(R0x0D3)          | Reserved             | -                    | 0 (0x0000)              |  |

| R212:0(R0x0D4)          | Reserved             | -                    | 0 (0x0000)              |  |

| R213:0(R0x0D5)          | Reserved             | -                    | 0 (0x0000)              |  |

| R214:0(R0x0D6)          | Reserved             | -                    | 0 (0x0000)              |  |

| R215:0(R0x0D7)          | Reserved             | _                    | 0 (0x0000)              |  |

| R216:0(R0x0D8)          | Reserved             | _                    | 0 (0x0000)              |  |

| R217:0(R0x0D9)          | Reserved             | _                    | 0 (0x0000)              |  |

| R218:0(R0x0DA)          | Reserved             | -                    | 0 (0x0000)              |  |

| R219:0(R0x0DB)          | Reserved             | -                    | 0 (0x0000)              |  |

| R220:0(R0x0DC)          | Reserved             | -                    | 0 (0x0000)              |  |

| R221:0(R0x0DD)          | Reserved             | -                    | 0 (0x0000)              |  |

| R222:0(R0x0DE)          | Reserved             | -                    | 0 (0x0000)              |  |

| R223:0(R0x0DF)          | Reserved             | _                    | 0 (0x0000)              |  |

| R224:0(R0x0E0)          | Reserved             | _                    | 0 (0x0000)              |  |

| R225:0(R0x0E1)          | Reserved             | -                    | 0 (0x0000)              |  |

| R226:0(R0x0E2)          | Reserved             | Reserved –           |                         |  |

| R227:0(R0x0E3)          | Reserved             | Reserved –           |                         |  |

| R228:0(R0x0E4)          | Reserved             | _                    | 0 (0x0000)              |  |

| R229:0(R0x0E5)          | Reserved             | _                    | 0 (0x0000)              |  |

| R230:0(R0x0E6)          | Reserved             | _                    | 0 (0x0000)              |  |

| R231:0(R0x0E7)          | Reserved             | -                    | 0 (0x0000)              |  |

| R232:0(R0x0E8)          | Reserved             | _                    | 0 (0x0000)              |  |

| R233:0(R0x0E9)          | Reserved             | -                    | 0 (0x0000)              |  |

| R234:0(R0x0EA)          | Reserved             | -                    | 0 (0x0000)              |  |

| R235:0(R0x0EB)          | Reserved             | -                    | 0 (0x0000)              |  |

| R236:0(R0x0EC)          | Reserved             | -                    | 0 (0x0000)              |  |

| R237:0(R0x0ED)          | Reserved             | Reserved –           |                         |  |

| R238:0(R0x0EE)          | Reserved             | Reserved –           |                         |  |

| R239:0(R0x0EF)          | Reserved             | -                    | 0 (0x0000)              |  |

| R240:0(R0x0F0)          | Reserved             | -                    | 0 (0x0000)              |  |

| R241:0(R0x0F1)          | Reserved             | -                    | 0 (0x0000)              |  |

| R248:0(R0x0F8)          | Reserved             | -                    | 0 (0x0000)              |  |

| R250:0(R0x0FA)          | Reserved             | _                    | 0 (0x0000)              |  |

#### Table 12. REGISTER LIST AND DEFAULT VALUES (continued)

(1 = read-only, always 1; 0 = read-only, always 0; d = programmable; ? = read-only, dynamic)

| Register # Dec (Hex) | Register Description | Data Format (Binary) | Default Value Dec (Hex) |

|----------------------|----------------------|----------------------|-------------------------|

| R251:0(R0x0FB)       | Reserved             | -                    | 0 (0x0000)              |

| R252:0(R0x0FC)       | Reserved             | -                    | 0 (0x0000)              |

| R253:0(R0x0FD)       | Reserved             | -                    | 0 (0x0000)              |

| R255:0(R0x0FF)       | Chip_Version_Alt     | ???? ???? ???? ????  | 6145 (0x1801)           |

#### **Register Description**

Table 13 lists sensor register descriptions.

#### Table 13. REGISTER DESCRIPTION

| Reg. #         | Bits                                                                                                                                                                                                                                                                                                                                                        | Default                                  | Name                                                                                                                                                                                                                                                                                         |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R0:0           | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x1801                                   | Chip Version (RO)                                                                                                                                                                                                                                                                            |  |  |

| R0x000         | 15:8                                                                                                                                                                                                                                                                                                                                                        | RO                                       | Part ID<br>Two-digit BCD value typically derived from the reticle ID code<br>Legal values: [0, 255]                                                                                                                                                                                          |  |  |

|                | 7:4                                                                                                                                                                                                                                                                                                                                                         | RO                                       | Analog Revision<br>Constant value incremented with each mask change for the same Part ID<br>Legal values: [0, 15]                                                                                                                                                                            |  |  |

|                | 3:0                                                                                                                                                                                                                                                                                                                                                         | RO                                       | Digital Revision<br>Constant value incremented with each digital functionality change for the same<br>Part ID                                                                                                                                                                                |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                             |                                          | Legal values: [0, 15]                                                                                                                                                                                                                                                                        |  |  |

|                | Chip version                                                                                                                                                                                                                                                                                                                                                | ſ                                        | 1                                                                                                                                                                                                                                                                                            |  |  |

| R1:0<br>R0x001 | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x0036                                   | Row Start (RW)                                                                                                                                                                                                                                                                               |  |  |

| 10,001         | will be used. Wri                                                                                                                                                                                                                                                                                                                                           | tes are synchroniz                       | corner of the FOV. If this register is set to an odd value, the next lower even value<br>red to frame boundaries. Affected by Synchronize_Changes.<br>gal values: [0, 2004], even                                                                                                            |  |  |

| R2:0           | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x0010                                   | Column Start (RW)                                                                                                                                                                                                                                                                            |  |  |

| R0x002         | The X coordinate of the upper–left corner of the FOV. The value will be rounded down to the nearest multiple of 2 times the column bin factor. Writes are synchronized to frame boundaries. Affected by Synchronize_Changes. Legal values: [0, 2750], even                                                                                                  |                                          |                                                                                                                                                                                                                                                                                              |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                             | Column = 0 Mirr                          | it is in the form shown below, where n is an integer:<br>or Column – 1                                                                                                                                                                                                                       |  |  |

|                | no bin                                                                                                                                                                                                                                                                                                                                                      | 4n                                       | 4n + 2                                                                                                                                                                                                                                                                                       |  |  |

|                | Bin 2x<br>Bin 4x                                                                                                                                                                                                                                                                                                                                            | 8n<br>16n                                | 8n + 4<br>16n + 8                                                                                                                                                                                                                                                                            |  |  |

| R3:0           | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x0797                                   | Row Size (RW)                                                                                                                                                                                                                                                                                |  |  |

| R0x003         | are synchronized                                                                                                                                                                                                                                                                                                                                            | to frame bounda                          | If this register is set to an even value, the next higher odd value will be used. Writes ries. Affected by Synchronize_Changes gal values: [1, 2005], odd                                                                                                                                    |  |  |

| R4:0           | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x0A1F                                   | Column Size (RW)                                                                                                                                                                                                                                                                             |  |  |

| R0x004         | The width of the field of view minus one. If this register is set to an even value, the next higher odd value will be use<br>In other words, it should be (2 × n × (Column_Bin + 1) – 1) for some integer n. Writes are synchronized to frame<br>boundaries. Affected by Synchronize_Changes. Causes a Bad Frame if written<br>Legal values: [1, 2751], odd |                                          |                                                                                                                                                                                                                                                                                              |  |  |

| R5:0           | 15:0                                                                                                                                                                                                                                                                                                                                                        | 0x0000                                   | Horizontal Blank (RW)                                                                                                                                                                                                                                                                        |  |  |

| R0x005         | decrease frame<br>horizontal blank                                                                                                                                                                                                                                                                                                                          | rate. Setting a valu<br>depends on the m | h row, in pixel clocks. Incrementing this register will increase exposure and<br>ue less than the minimum will use the minumum horizontal blank. The minimum<br>ode of the sensor. Writes are synchronized to frame boundaries. Affected by<br>Bad Frame if written. Legal values: [0, 4095] |  |  |