Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## DDR SDRAM SM ALL-OUTLINE DIM M

MT9VDDT1672H - 128MB, MT9VDDT3272H - 256MB, MT9VDDT6472H - 512MB, MT9VDDT12872H - 1GB

For the latest data sheet, please refer to the Micron® Web site: www.micron.com/products/modules

#### **Features**

- 200-pin, small-outline, dual in-line memory module (SODIMM)

- Supports ECC error detection and correction

- Fast data transfer rates: PC1600, PC2100, or PC2700

- Utilizes 200 MT/s, 266 MT/s, and 333 MT/s DDR SDRAM components

- 128MB (16 Meg x 72), 256MB (32 Meg x 72), 512MB (64 Meg x 72), and 1GB (128 Meg x 72)

- VDD = VDDQ = +2.5V

- VDDSPD = +2.3V to +3.6V

- 2.5VI/O (SSTL\_2 compatible)

- Commands entered on each positive CK edge

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

- Bidirectional data strobe (DQS) transmitted/ received with data—i.e., source-synchronous data capture

- Differential clock inputs CK and CK#

- Four internal device banks for concurrent operation

- Programmable burst lengths: 2, 4, or 8

- Auto precharge option

- · Auto Refresh and Self Refresh Modes

- 15.625µs (128MB) or 7.8125µs (256MB, 512MB,

1GB) maximum average periodic refresh interval

- Serial Presence Detect (SPD) with EEPROM

- Programmable READ CAS latency

- Gold edge contacts

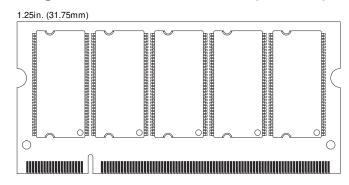

#### Figure 1: 200-Pin SODIMM (MO-224)

| OPTIONS                                                                                                                                                                  | MARKING                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| <ul> <li>Operating Temperature Range<br/>Commercial (0°C ≤ T<sub>A</sub> ≤ +70°C)</li> </ul>                                                                             | None                                                          |

| Industrial $(-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C})$                                                                                       | $I^2$                                                         |

| <ul> <li>Package</li> <li>200-pin SODIMM (standard)</li> <li>200-pin SODIMM (lead-free)</li> </ul>                                                                       | $rac{G}{Y^2}$                                                |

| <ul> <li>Memory clock, Speed, CAS Latency<br/>6.0ns (167 MHz), 333 MT/s, CL = 2.5<br/>7.5ns (133 MHz), 266 MT/s, CL = 2<br/>7.5ns (133 MHz), 266 MT/s, CL = 2</li> </ul> | $ \begin{array}{r} -335 \\ -262^{2} \\ -26A^{2} \end{array} $ |

| 7.5ns (133 MHz), 266 MT/s, CL = 2.5<br>10ns (100 MHz), 200 MT/s, CL = 2                                                                                                  |                                                               |

| • PCB<br>1.25in. (31.75mm)                                                                                                                                               | See page 2 note                                               |

NOTE: 1. CL = Device CAS (READ) Latency.

2. Consult Micron for product availability.

#### Table 1: Address Table

|                        | 128MB              | 256MB              | 512MB              | 1GB               |

|------------------------|--------------------|--------------------|--------------------|-------------------|

| Refresh Count          | 4K                 | 8K                 | 8K                 | 8K                |

| Row Addressing         | 8K (A0–A11)        | 8K (A0–A12)        | 8K (A0–A12)        | 16K (A0–A13)      |

| Device Bank Addressing | 4 (BA0, BA1)       | 4 (BA0, BA1)       | 4 (BA0, BA1)       | 4 (BA0, BA1)      |

| Device Configuration   | 128Mb (16 Meg x 8) | 256Mb (32 Meg x 8) | 512Mb (64 Meg x 8) | 1Gb (128 Meg x 8) |

| Column Addressing      | 1K (A0–A9)         | 1K (A0–A9)         | 2K (A0–A9, A11)    | 2K (A0–A9, A11)   |

| Module Rank Addressing | 1 (SO#)            | 1 (\$0#)           | 1 (SO#)            | 1 (\$0#)          |

Table 2: Part Numbers and Timing Parameters

| PART NUMBER           | M ODULE<br>DENSITY | CONFIGURATION | M ODULE<br>BANDWIDTH | M EM ORY CLOCK/<br>DATA RATE | LATENCY<br>(CL - <sup>†</sup> RCD - <sup>†</sup> RP) |

|-----------------------|--------------------|---------------|----------------------|------------------------------|------------------------------------------------------|

| MT9VDDT1672H(I)G-335  | 128MB              | 16 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT1672H(I)Y-335  | 128MB              | 16 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT1672H(I)G-262  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT1672H(I)Y-262  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT1672H(I)G-26A  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT1672H(I)Y-26A  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT1672H(I)G-265  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT1672H(I)Y-265  | 128MB              | 16 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT1672H(I)G-202  | 128MB              | 16 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT1672H(I)Y-202  | 128MB              | 16 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT3272H(I)G-335  | 256MB              | 32 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT3272H(I)Y-335  | 256MB              | 32 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT3272H(I)G-262  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT3272H(I)Y-262  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT3272H(I)G-26A  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT3272H(I)Y-26A  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT3272H(I)G-265  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT3272H(I)Y-265  | 256MB              | 32 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT3272H(I)G-202  | 256MB              | 32 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT3272H(I)Y-202  | 256MB              | 32 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT6472H(I)G-335  | 512MB              | 64 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT6472H(I)Y-335  | 512MB              | 64 Meg x 72   | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT6472H(I)G-262  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT6472H(I)Y-262  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT6472H(I)G-26A  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT6472H(I)Y-26A  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT6472H(I)G-265  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT6472H(I)Y-265  | 512MB              | 64 Meg x 72   | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT6472H(I)G-202  | 512MB              | 64 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT6472H(I)Y-202  | 512MB              | 64 Meg x 72   | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT12872H(I)G-335 | 1GB                | 128 Meg x 72  | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT12872H(I)Y-335 | 1GB                | 128 Meg x 72  | 2.7 GB/s             | 6.0ns/333 MT/s               | 2.5-3-3                                              |

| MT9VDDT12872H(I)G-262 | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT12872H(I)Y-262 | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-2-2                                                |

| MT9VDDT12872H(I)G-26A | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT12872H(I)Y-26A | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2-3-3                                                |

| MT9VDDT12872H(I)G-265 | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT12872H(I)Y-265 | 1GB                | 128 Meg x 72  | 2.1 GB/s             | 7.5ns/266 MT/s               | 2.5-3-3                                              |

| MT9VDDT12872H(I)G-202 | 1GB                | 128 Meg x 72  | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

| MT9VDDT12872H(I)Y-202 | 1GB                | 128 Meg x 72  | 1.6 GB/s             | 10ns/200 MT/s                | 2-2-2                                                |

#### NOTE:

All part numbers end with a two-place code (not shown), designating component and PCB revisions. Consult factory for current revision codes. Example: MT9VDDT3272HG-265A1.

Table 3: Pin Assignment (200-Pin SODIMM Front)

| PIN | SYMBOL | PIN | SYMBOL              | PIN | SYM BOL             | PIN | SYM BOL |

|-----|--------|-----|---------------------|-----|---------------------|-----|---------|

| 1   | VREF   | 51  | Vss                 | 101 | A9                  | 151 | DQ42    |

| 3   | Vss    | 53  | DQ19                | 103 | Vss                 | 153 | DQ43    |

| 5   | DQ0    | 55  | DQ24                | 105 | A7                  | 155 | Vdd     |

| 7   | DQ1    | 57  | VDD                 | 107 | A5                  | 157 | Vdd     |

| 9   | Vdd    | 59  | DQ25                | 109 | А3                  | 159 | Vss     |

| 11  | DQS0   | 61  | DQS3                | 111 | A1                  | 161 | Vss     |

| 13  | DQ2    | 63  | Vss                 | 113 | VDD                 | 163 | DQ48    |

| 15  | Vss    | 65  | DQ26                | 115 | A10                 | 165 | DQ49    |

| 17  | DQ3    | 67  | DQ27                | 117 | BA0                 | 167 | Vdd     |

| 19  | DQ8    | 69  | VDD                 | 119 | WE#                 | 169 | DQS6    |

| 21  | Vdd    | 71  | CB0                 | 121 | S0#                 | 171 | DQ50    |

| 23  | DQ9    | 73  | CB1                 | 123 | NC/A13 <sup>2</sup> | 173 | Vss     |

| 25  | DQS1   | 75  | Vss                 | 125 | Vss                 | 175 | DQ51    |

| 27  | Vss    | 77  | DQS8                | 127 | DQ32                | 177 | DQ56    |

| 29  | DQ10   | 79  | CB2                 | 129 | DQ33                | 179 | VDD     |

| 31  | DQ11   | 81  | VDD                 | 131 | Vdd                 | 181 | DQ57    |

| 33  | VDD    | 83  | CB3                 | 133 | DQS4                | 183 | DQS7    |

| 35  | CK0    | 85  | NC                  | 135 | DQ34                | 185 | Vss     |

| 37  | CK0#   | 87  | Vss                 | 137 | Vss                 | 187 | DQ58    |

| 39  | Vss    | 89  | CK2                 | 139 | DQ35                | 189 | DQ59    |

| 41  | DQ16   | 91  | CK2#                | 141 | DQ40                | 191 | Vdd     |

| 43  | DQ17   | 93  | VDD                 | 143 | VDD                 | 193 | SDA     |

| 45  | Vdd    | 95  | NC                  | 145 | DQ41                | 195 | SCL     |

| 47  | DQS2   | 97  | NC                  | 147 | DQS5                | 197 | VDDSPD  |

| 49  | DQ18   | 99  | NC/A12 <sup>1</sup> | 149 | Vss                 | 199 | NC      |

Table 4: Pin Assignment (200-pin SODIMM Back)

| PIN | SYMBOL | PIN | SYMBOL | PIN | SYM BOL | PIN | SYM BOL |

|-----|--------|-----|--------|-----|---------|-----|---------|

| 2   | VREF   | 52  | Vss    | 102 | A8      | 152 | DQ46    |

| 4   | Vss    | 54  | DQ23   | 104 | Vss     | 154 | DQ47    |

| 6   | DQ4    | 56  | DQ28   | 106 | A6      | 156 | Vdd     |

| 8   | DQ5    | 58  | VDD    | 108 | A4      | 158 | CK1#    |

| 10  | Vdd    | 60  | DQ29   | 110 | A2      | 160 | CK1     |

| 12  | DM0    | 62  | DM3    | 112 | A0      | 162 | Vss     |

| 14  | DQ6    | 64  | Vss    | 114 | Vdd     | 164 | DQ52    |

| 16  | Vss    | 66  | DQ30   | 116 | BA1     | 166 | DQ53    |

| 18  | DQ7    | 68  | DQ31   | 118 | RAS#    | 168 | Vdd     |

| 20  | DQ12   | 70  | VDD    | 120 | CAS#    | 170 | DM6     |

| 22  | Vdd    | 72  | CB4    | 122 | NC      | 172 | DQ54    |

| 24  | DQ13   | 74  | CB5    | 124 | NC      | 174 | Vss     |

| 26  | DM1    | 76  | Vss    | 126 | Vss     | 176 | DQ55    |

| 28  | Vss    | 78  | DM8    | 128 | DQ36    | 178 | DQ60    |

| 30  | DQ14   | 80  | CB6    | 130 | DQ37    | 180 | Vdd     |

| 32  | DQ15   | 82  | VDD    | 132 | Vdd     | 182 | DQ61    |

| 34  | Vdd    | 84  | CB7    | 134 | DM4     | 184 | DM7     |

| 36  | Vdd    | 86  | NC     | 136 | DQ38    | 186 | Vss     |

| 38  | Vss    | 88  | Vss    | 138 | Vss     | 188 | DQ62    |

| 40  | Vss    | 90  | Vss    | 140 | DQ39    | 190 | DQ63    |

| 42  | DQ20   | 92  | VDD    | 142 | DQ44    | 192 | Vdd     |

| 44  | DQ21   | 94  | Vdd    | 144 | VDD     | 194 | SA0     |

| 46  | Vdd    | 96  | CKE0   | 146 | DQ45    | 196 | SA1     |

| 48  | DM2    | 98  | NC     | 148 | DM5     | 198 | SA2     |

| 50  | DQ22   | 100 | A11    | 150 | Vss     | 200 | NC      |

#### NOTE:

- 1. Pin 99 is NC for 128MB and A12 for 256MB, 512MB, and 1GB.

- 2. Pin 123 is NC for 128MB, 256MB, and 512MB and A13 for 1GB.

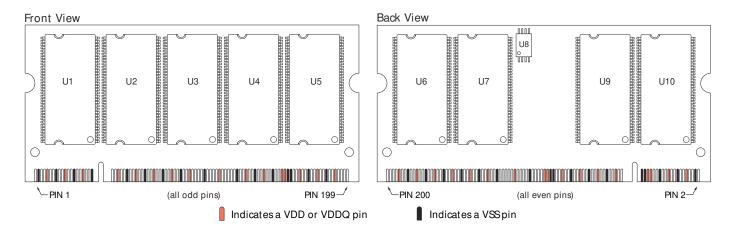

Figure 2: Module Layout

## Table 5: Pin Descriptions

Pin numbers may not correlate with symbols; refer to Pin Assignment Tables on page 3 for more information

| PIN NUMBERS                                                                                                                                           | SYMBOL                                                           | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 118, 119, 120                                                                                                                                         | WE#, CAS#, RAS#                                                  | Input            | Command Inputs: RAS#, CAS#, and WE# (along with S#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 35, 37, 89, 91, 158, 160                                                                                                                              | CK0, CK0#, CK1,<br>CK1#, CK2, CK2#                               | Input            | Clock: CK, CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK, and negative edge of CK#. Output data (DQs and DQS) is referenced to the crossings of CK and CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 96                                                                                                                                                    | CKE0                                                             | Input            | Clock Enable: CKE HIGH activates and CKE LOW deactivates the internal clock, input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all device banksidle), or ACTIVE POWER-DOWN (row ACTIVE in any device bank). CKE is synchronous for POWER-DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit and for disabling the outputs. CKE must be maintained HIGH throughout read and write accesses. Input buffers (excluding CK, CK# and CKE) are disabled during POWER-DOWN. Input buffers (excluding CKE) are disabled during SELF REFRESH. CKE is an SSTL_2 input but will detect an LVCMOS LOW level after VDD is applied. |

| 121                                                                                                                                                   | <b>S</b> 0#                                                      | Input            | Chip Selects: S# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when S# is registered HIGH. S# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 116, 117                                                                                                                                              | BA0, BA1                                                         | Input            | Bank Address: BA0, BA1 define to which device bank an ACTIVE, READ, WRITE, or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 99 (256MB, 512MB, 1GB),<br>100, 101, 102, 105, 106, 107,<br>108, 109, 110, 111, 112, 115,<br>123 (1GB)                                                | A0-A11<br>(128MB)<br>A0-A12<br>(256MB, 512MB)<br>A0-A13<br>(1GB) | Input            | Address Inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit (A10) for READ/WRITE commands, to select one location out of the memory array in the respective device bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one device bank (A10 LOW, device bank selected by BA0, BA1) or all device banks (A10 HIGH). The address inputs also provide the op-code during a MODE REGISTER SET command. BA0 and BA1 define which mode register (mode register or extended mode register) is loaded during the LOAD MODE REGISTER command.                                                                                                |

| 11, 25, 47, 61, 77, 133, 147,<br>169, 183                                                                                                             | DQS0-DQS8                                                        | Input/<br>Output | Data Strobe: Output with READ data, input with WRITE data. DQS is edge-aligned with READ data, centered in WRITE data. Used to capture data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12, 26, 48, 62, 78, 134, 148,<br>170, 184                                                                                                             | DM0-DM8                                                          | Input            | Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input-only, the DM loading is designed to match that of DQ and DQS pins.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 71,72, 73, 74, 79, 80, 83, 84                                                                                                                         | CB0-CB7                                                          | Input/<br>Output | Check Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5–8, 13–20, 23–24, 29–32, 41–44, 49–50, 53–56, 59–60, 65–68, 127–130, 135–136, 139–142, 145–146, 151–154, 163–166, 171–172, 175–178, 181–182, 187–190 | DQ0-DQ63                                                         | Input/<br>Output | Data I/Os: Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Table 5: Pin Descriptions (Continued)

Pin numbers may not correlate with symbols; refer to Pin Assignment Tables on page 3 for more information

| PIN NUMBERS                                                                                                                 | SYMBOL  | TYPE             | DESCRIPTION                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 195                                                                                                                         | SCL     | Input            | Serial Clock for Presence-Detect: SCL is used to synchronize the presence-detect data transfer to and from the module.                                 |

| 194, 196, 198                                                                                                               | SA0-SA2 | Input            | Presence-Detect Address Inputs: These pins are used to configure the presence-detect device.                                                           |

| 193                                                                                                                         | SDA     | Input/<br>Output | Serial Presence-Detect Data: SDA is a bidirectional pin used to transfer addresses and data into and out of the presence-detect portion of the module. |

| 1, 2                                                                                                                        | VREF    | Supply           | SSTL_2 reference voltage.                                                                                                                              |

| 9–10, 21–22, 33–34, 36, 45–46, 57–58, 69–70, 81–82, 92–94, 113–114, 131–132, 143–144, 155–157, 167–168, 17–180, 191–192     | VDD     | Supply           | Power Supply: +2.5V ±0.2V.                                                                                                                             |

| 3–4 15–16, 27–28, 38–40, 51–52, 63–64, 75–76, 87–88, 90, 103–104, 125–126, 137–138, 149–150, 159, 161–162, 173–174, 185–186 | Vss     | Supply           | Ground.                                                                                                                                                |

| 197                                                                                                                         | VDDSPD  | Supply           | Serial EEPROM positive power supply: +2.3V to +3.6V.                                                                                                   |

| 85, 95, 97, 122,<br>123 (128MB, 256MB,<br>512MB), 199 (128MB),<br>98, 124, 200                                              | NC      | _                | No Connect: These pins should be left unconnected.                                                                                                     |

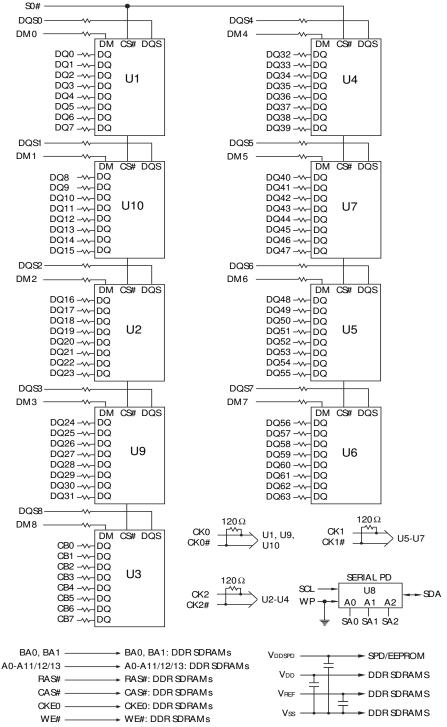

Figure 3: Functional Block Diagram

#### NOTE:

- 1. All resistor values are  $22\Omega$  unless otherwise specified.

- Per industry standard, Micron modules utilize various component speed grades, as referenced in the module part numbering guide at www.micron.com/numberguide.

Standard modules use the following DDR SDRAM devices: MT46V16M8TG (128MB); MT46V32M8TG (256MB); MT46V64M8TG (512MB); MT46V128M8TG (1GB)

Lead-free modules use the following DDR SDRAM devices: MT46V16M8P (128MB); MT46V32M8P (256MB); MT46V64M8P (512MB); MT46V128M8P (1GB)

Contact Micron for availability of IT modules.

#### **General Description**

The MT9VDDT1672H, MT9VDDT3272H, MT9VDDT6472H, and MT9VDDT12872H are high-speed CMOS, dynamic random-access, 128MB, 256MB, 512MB, and 1GB memory modules organized in x72 (ECC) configuration. DDR SDRAM modules use internally configured quad-bank DDR SDRAM devices.

DDR SDRAM modules use a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the DDR SDRAM module effectively consists of a single 2n-bit wide, one-clock-cycle data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transmitted externally, along with data, for use in data capture at the receiver. DQS is an intermittent strobe transmitted by the DDR SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs.

DDR SDRAM modules operate from differential clock inputs (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to DDR SDRAM modules are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the device bank and row to be accessed (BAO, BA1 select device bank; A0–A11 select device rofw for 128MB; A0–A12 select device row for 256MB and 512MB; A0–A13 select device row for 1GB). The address bits registered coincident with the READ or WRITE command are used to select the device bank and the starting device column location for the burst access.

DDR SDRAM modules provide for programmable READ or WRITE burst lengths of 2, 4, or 8 locations. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

The pipelined, multibank architecture of DDR SDRAM modules allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

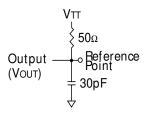

An auto refresh mode is provided, along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL\_2. All outputs are SSTL\_2, Class II compatible. For more information regarding DDR SDRAM operation, refer to the 128Mb, 256Mb, 512Mb, or 1Gb DDR SDRAM component data sheets.

#### **Serial Presence-Detect Operation**

DDR SDRAM modules incorporate serial presence-detect (SPD). The SPD function is implemented using a 2,048-bit EEPROM. This nonvolatile storage device contains 256 bytes. The first 128 bytes can be programmed by Micron to identify the module type and various SDRAM organizations and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the system logic and the module EEPROM device occur via a standard I<sup>2</sup>C bus using the DIMM's SCL (clock) and SDA (data) signals, together with SA (2:0), which provide eight unique DIMM/EEPROM addresses. Write protect (WP) is tied to ground on the module, permanently disabling hardware write protect.

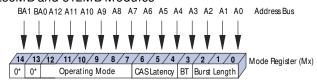

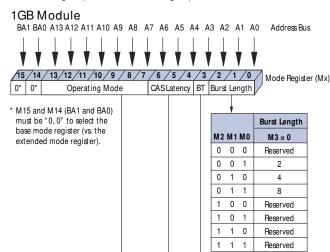

#### Mode Register Definition

The mode register is used to define the specific mode of operation of DDR SDRAM devices. This definition includes the selection of a burst length, a burst type, a CAS latency and an operating mode, as shown in Figure 4, Mode Register Definition Diagram, on page 8. The mode register is programmed via the MODE REGISTER SET command (with BA0 = 0 and BA1 = 0) and will retain the stored information until it is programmed again or the device loses power (except for bit A8, which is self-clearing).

Reprogramming the mode register will not alter the contents of the memory, provided it is performed correctly. The mode register must be loaded (reloaded) when all device banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

Mode register bits A0–A2 specify the burst length, A3 specifies the type of burst (sequential or interleaved), A4–A6 specify the CAS latency, and A7–A11 (128MB), A7–A12 (256MB, 512MB) or A7–A13 (1GB) specify the operating mode.

#### Burst Length

Read and write accesses to DDR SDRAM devices are burst oriented, with the burst length being programmable, as shown in Mode Register Diagram. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 2, 4, or 8 locations are available for both the sequential and the interleaved burst types.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, meaning that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A1–Ai when the burst length is set to two, by A2–Ai when the burst length is set to four and by A3–Ai when the burst length is set to eight (where Ai is the most significant column address bit for a given configuration; see Note 5 of Table 6, Burst Definition Table, on page 9). The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. The programmed burst length applies to both READ and WRITE bursts.

#### Burst Type

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in Table 6, Burst Definition Table, on page 9.

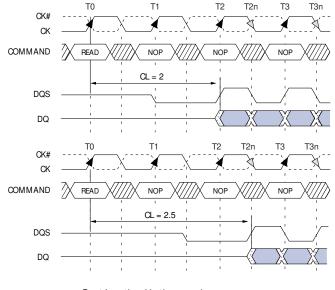

#### Read Latency

The READ latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first bit of output data. The latency can be set to 2 or 2.5 clocks, as shown in Figure 5, CAS Latency Diagram, on page 9.

If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available nominally coincident with clock edge n+m. Table 7, CAS Latency (CL) Table, indicates the operating fre-

quencies at which each CAS latency setting can be used.

# Figure 4: Mode Register Definition Diagram

# 128M B Module BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Bus 13/12/11/10/9/8/7/6/5/4/3/2/1/0 Mode Register (Mx) 0\* O\* Operating Mode CASLatency BT Burst Length

\* M13 and M12 (BA0 and BA1) must be "0, 0" to select the base mode register (vs. the extended mode register).

#### 256MB and 512MB Modules

\* M14 and M13 (BA0 and BA1) must be "0, 0" to select the base mode register (vs. the extended mode register).

| М6 | М5 | M4 | CAS Latency |

|----|----|----|-------------|

| 0  | 0  | 0  | Reserved    |

| 0  | 0  | 1  | Reserved    |

| 0  | 1  | 0  | 2           |

| 0  | 1  | 1  | Reserved    |

| 1  | 0  | 0  | Reserved    |

| 1  | 0  | 1  | Reserved    |

| 1  | 1  | 0  | 2.5         |

| 1  | 1  | 1  | Reserved    |

0

Burst Type

Sequential Interleaved

| ı | M 13 | M12 | M 11 | M 10 | М9 | М8 | М7 | M 6-M 0 | Operating Mode             |

|---|------|-----|------|------|----|----|----|---------|----------------------------|

|   | 0    | 0   | 0    | 0    | 0  | 0  | 0  | Valid   | Normal Operation           |

|   | 0    | 0   | 0    | 0    | 0  | 1  | 0  | Valid   | Normal Operation/Reset DLL |

|   | -    | -   | -    | -    | -  | -  | -  | -       | All other states reserved  |

Table 6: Burst Definition Table

|                 |                   |            |    |                      | CESSES WITHIN JRST    |

|-----------------|-------------------|------------|----|----------------------|-----------------------|

| BURST<br>LENGTH | COLUMN<br>ADDRESS |            |    | TYPE =<br>SEQUENTIAL | TYPE =<br>INTERLEAVED |

|                 |                   |            | Α0 |                      |                       |

| 0               |                   |            | 0  | 0-1                  | 0-1                   |

| 2               |                   |            | 1  | 1-0                  | 1-0                   |

|                 |                   | <b>A</b> 1 | Α0 |                      |                       |

|                 |                   | 0          | 0  | 0-1-2-3              | 0-1-2-3               |

| 4               |                   | 0          | 1  | 1-2-3-0              | 1-0-3-2               |

| 7               |                   | 1          | 0  | 2-3-0-1              | 2-3-0-1               |

|                 |                   | 1          | 1  | 3-0-1-2              | 3-2-1-0               |

|                 | <b>A2</b>         | Α1         | Α0 |                      |                       |

|                 | 0                 | 0          | 0  | 0-1-2-3-4-5-6-7      | 0-1-2-3-4-5-6-7       |

|                 | 0                 | 0          | 1  | 1-2-3-4-5-6-7-0      | 1-0-3-2-5-4-7-6       |

|                 | 0                 | 1          | 0  | 2-3-4-5-6-7-0-1      | 2-3-0-1-6-7-4-5       |

| 8               | 0                 | 1          | 1  | 3-4-5-6-7-0-1-2      | 3-2-1-0-7-6-5-4       |

|                 | 1                 | 0          | 0  | 4-5-6-7-0-1-2-3      | 4-5-6-7-0-1-2-3       |

|                 | 1                 | 0          | 1  | 5-6-7-0-1-2-3-4      | 5-4-7-6-1-0-3-2       |

|                 | 1                 | 1          | 0  | 6-7-0-1-2-3-4-5      | 6-7-4-5-2-3-0-1       |

|                 | 1                 | 1          | 1  | 7-0-1-2-3-4-5-6      | 7-6-5-4-3-2-1-0       |

#### NOTE:

- For a burst length of two, A1-Ai select the two-dataelement block; A0 selects the first access within the block

- For a burst length of four, A2–Ai select the four-dataelement block; A0–A1 select the first access within the block.

- For a burst length of eight, A3-Ai select the eight-dataelement block; A0-A2 select the first access within the block.

- Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

- 5. i = 9 for 128MB, 256MB; i = 9, 11 for 512MB, 1GB.

Table 7: CAS Latency (CL) Table

|       | ALLOWABLE OPERATING<br>CLOCK FREQUENCY (MHZ) |              |  |  |  |  |  |

|-------|----------------------------------------------|--------------|--|--|--|--|--|

| SPEED | CL = 2                                       | CL = 2.5     |  |  |  |  |  |

| -335  | 75 ≤ f ≤ 133                                 | 75 ≤ f ≤ 167 |  |  |  |  |  |

| -262  | 75 ≤ f ≤ 133                                 | 75 ≤ f ≤ 133 |  |  |  |  |  |

| -26A  | 75 ≤ f ≤ 133                                 | 75 ≤ f ≤ 133 |  |  |  |  |  |

| -265  | 75 ≤ f ≤ 100                                 | 75 ≤ f ≤ 133 |  |  |  |  |  |

| -202  | $75 \le f \le 100$                           | N/A          |  |  |  |  |  |

Figure 5: CAS Latency Diagram

Burst Length = 4 in the cases shown Shown with nominal  ${}^{\dagger}AC$ ,  ${}^{\dagger}DQSCK$ , and  ${}^{\dagger}DQSQ$

TRANSTIONING DATA ON'T CARE

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

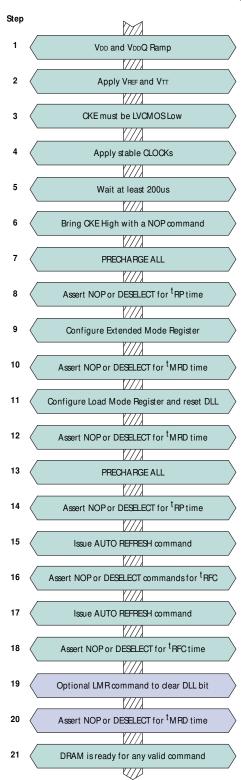

## Operating Mode

The normal operating mode is selected by issuing a MODE REGISTER SET command with bits A7-A11 (128MB), A7-A12 (256MB, 512MB) or A7-A13 (1GB) each set to zero, and bits A0-A6 set to the desired values. A DLL reset is initiated by issuing a MODE REGISTER SET command with bits A7 and A9-A11 (128MB); A7 and A9-A12 (256MB, 512MB); or A7 and A9-A13 (1GB) each set to zero, bit A8 set to one, and bits A0-A6 set to the desired values. Although not required by the Micron device, JEDEC specifications recommend when a LOAD MODE REGISTER command is issued to reset the DLL, it should always be followed by a LOAD MODE REGISTER command to select normal operating mode.

All other combinations of values for A7-A11 (128MB); A7-A12 (256MB, 512MB); or A7-A13 (1GB) are reserved for future use and/or test modes. Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

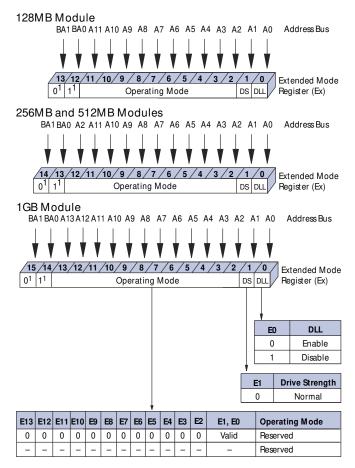

#### **Extended Mode Register**

The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable and output drive strength. These functions are controlled via the bits shown in Figure 6, Extended Mode Register Definition Diagram. The extended mode register is programmed via the LOAD MODE REGISTER command to the mode register (with BA0 = 1 and BA1 = 0) and will retain the stored information until it is programmed again or the device loses power. The enabling of the DLL should always be followed by a LOAD MODE REGISTER command to the mode register (BA0/BA1 both LOW) to reset the DLL.

The extended mode register must be loaded when all device banks are idle and no bursts are in progress, and the controller must wait the specified time before initiating any subsequent operation. Violating either of these requirements could result in unspecified operation.

#### DLL Enable/Disable

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after having disabled the DLL for the purpose of debug or evaluation. (When the device exits self refresh mode, the DLL is enabled automatically.) Any time the DLL is enabled, 200 clock cycles with CKE HIGH must occur before a READ command can be issued.

# Figure 6: Extended Mode Register Definition Diagram

#### NOTE:

- BA1 and BA0 (E13 and E12 for 128MB, E14 and E13 for 256MB, 512MB, or E15 and E14 for 1GB) must be "0, 1" to select the Extended Mode Register (vs. the base Mode Register).

- 2. QFC# is not supported.

#### Commands

Table 8, Commands Truth Table, and Table 9, DM Operation Truth Table, provide a general reference of available commands. For a more detailed description

of commands and operations, refer to the 128Mb, 256Mb, 512Mb, or 1Gb DDR SDRAM component data sheets.

#### Table 8: Commands Truth Table

CKE is HIGH for all commands shown except SELF REFRESH; all states and sequences not shown are illegal or reserved

| NAME (FUNCTION)                                        | CS# | RAS# | CAS# | WE# | ADDRESS  | NOTES |

|--------------------------------------------------------|-----|------|------|-----|----------|-------|

| DESELECT (NOP)                                         | Н   | Х    | Х    | Х   | Х        | 1     |

| NO OPERATION (NOP)                                     | L   | Н    | Н    | Н   | Х        | 1     |

| ACTIVE (Select bank and activate row)                  | L   | L    | Н    | Н   | Bank/Row | 2     |

| READ (Select bank and column, and start READ burst)    | L   | Н    | L    | Н   | Bank/Col | 3     |

| WRITE (Select bank and column, and start WRITE burst)  | L   | Н    | L    | L   | Bank/Col | 3     |

| BURST TERMINATE                                        | L   | Н    | Н    | L   | Χ        | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L   | L    | Н    | L   | Code     | 5     |

| AUTO REFRESH or SELF REFRESH (Enter self refresh mode) | L   | L    | L    | Н   | Х        | 6, 7  |

| LOAD MODE REGISTER                                     | L   | L    | L    | L   | Op-Code  | 8     |

#### NOTE:

- 1. DESELECT and NOP are functionally interchangeable.

- BA0-BA1 provide device bank address and A0-A11 (128MB), A0-A12 (256MB, 512MB) or A0-A13 (1GB) provide row address.

- 3. BA0-BA1 provide device bank address; A0-A9 (128MB, 256MB) or A0-A9,11 (512MB, 1GB), provide column address; A10 HIGH enables the auto precharge feature (nonpersistent), and A10 LOW disables the auto precharge feature.

- 4. Applies only to read bursts with auto precharge disabled; this command is undefined (and should not be used) for READ bursts with auto precharge enabled and for WRITE bursts.

- 5. A10 LOW: BA0-BA1 determine which device bank is precharged. A10 HIGH: all device banks are precharged and BA0-BA1 are "Don't Care."

- 6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

- 7. Internal refresh counter controls row addressing; all inputs and I/Os are "Don't Care" except for CKE.

- 8. BA0-BA1 select either the mode register or the extended mode register (BA0 = 0, BA1 = 0 select the mode register; BA0 = 1, BA1 = 0 select extended mode register; other combinations of BA0-BA1 are reserved). A0-A11 (128MB), A0-A12 (256MB, 512MB) or A0-A13 (1GB) provide the op-code to be written to the selected mode register.

#### Table 9: DM Operation Truth Table

Used to mask write data; provided coincident with the corresponding data

| NAME (FUNCTION) | DM | DQS   |

|-----------------|----|-------|

| WRITE Enable    | L  | Valid |

| WRITE Inhibit   | Н  | Х     |

#### **Absolute Maximum Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the opera-

tional sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| VDD Supply Voltage                |

|-----------------------------------|

| Relative to Vss1V to +3.6V        |

| VDDQ Supply Voltage               |

| Relative to Vss1V to +3.6V        |

| VREF and Inputs Voltage           |

| Relative to Vss1V to +3.6V        |

| I/O Pin Voltage                   |

| Relative to Vss0.5V to VDDQ +0.5V |

| Operating Temperature,                |                |

|---------------------------------------|----------------|

| $T_A$ (ambient - commercial)          | 0°C to +70°C   |

| T <sub>A</sub> (ambient - industrial) | 40°C to +85°C  |

| Storage Temperature (plastic)         | 55°C to +150°C |

| Short Circuit Output Current          | 50m A          |

|                                       |                |

#### Table 10: DC Electrical Characteristics and Operating Conditions

Notes: 1–5, 14; notes appear on pages 20–23;  $0^{\circ}C \le T_A \le +70^{\circ}C$

| PARAM ETER/CONDITION                                                                                                             |                                                     | SYMBOL  | MIN         | MAX         | UNITS | NOTES      |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|-------------|-------------|-------|------------|

| Supply Voltage                                                                                                                   |                                                     | VDD     | 2.3         | 2.7         | V     | 32, 36     |

| I/O Supply Voltage                                                                                                               |                                                     | VddQ    | 2.3         | 2.7         | V     | 32, 36, 39 |

| I/O Reference Voltage                                                                                                            |                                                     | VREF    | 0.49 x VDDQ | 0.51 x VDDQ | V     | 6, 39      |

| I/O Termination Voltage (system)                                                                                                 |                                                     | Vπ      | VREF - 0.04 | VREF + 0.04 | V     | 7, 39      |

| Input High (Logic 1) Voltage                                                                                                     |                                                     | VIH(DC) | VREF + 0.15 | VDD + 0.3   | V     | 25         |

| Input Low (Logic 0) Voltage                                                                                                      |                                                     | VIL(DC) | -0.3        | VREF - 0.15 | V     | 25         |

| INPUT LEAKAGE CURRENT Any input $0V \le VIN \le VDD$ , $VREF$ pin $0V \le VIN \le 1.35V$ (All other pins not under test = $0V$ ) | Command/<br>Address, RAS#,<br>CAS#, WE#,<br>CKE, S# | lı      | -18         | 18          | μΑ    | 46         |

|                                                                                                                                  | CK, CK#                                             |         | -6          | 6           |       |            |

|                                                                                                                                  | DM                                                  |         | -2          | 2           |       |            |

| OUTPUT LEAKAGE CURRENT<br>(DQs are disabled; 0V ≤ Vout ≤ VDDQ)                                                                   | DQ, DQS                                             | loz     | -5          | 5           | μΑ    | 46         |

| OUTPUT LEVELS                                                                                                                    |                                                     | Іон     | -16.8       | _           | mA    |            |

| High Current (VOUT = VDDQ - 0.373V, minimum VREF, minimum VTT) Low Current (VOUT = 0.373V, maximum VREF, maximum VTT)            |                                                     | lol     | 16.8        | _           | mA    | 33, 34     |

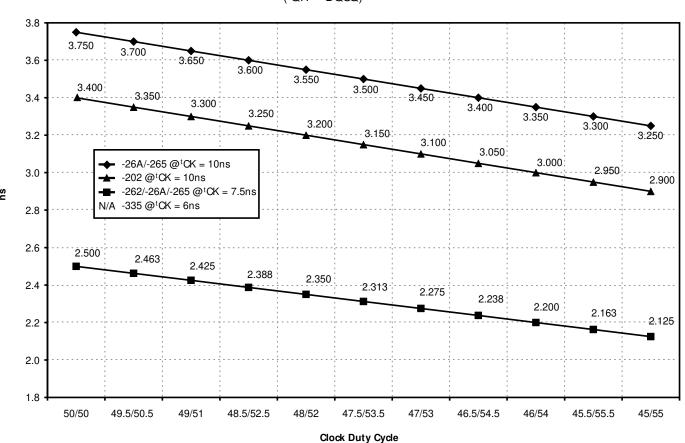

## Table 11: AC Input Operating Conditions

Notes: 1–5,12, 48; notes appear on pages 20–23;  $0^{\circ}C \le T_A \le +70^{\circ}C$ ; VDD = VDDQ = +2.5V ±0.2V

| PARAMETER/CONDITION          | SYMBOL   | MIN          | MAX          | UNITS | NOTES  |

|------------------------------|----------|--------------|--------------|-------|--------|

| Input High (Logic 1) Voltage | VIH(AC)  | VREF + 0.310 | _            | V     | 25, 35 |

| Input Low (Logic 0) Voltage  | VIL(AC)  | _            | VREF - 0.310 | V     | 25, 35 |

| I/O Reference Voltage        | VREF(AC) | 0.49 x VDDQ  | 0.51 x VDDQ  | V     | 6      |

## Table 12: IDD Specifications and Conditions – 128MB

DDR SDRAM components only

Notes: 1–5, 8, 10, 12, 47; notes appear on pages 20–23;  $0^{\circ}\text{C} \le T_{\text{A}} \le +70^{\circ}\text{C}$ ; VDD = VDDQ = +2.5V ±0.2V

|                                                                                                                                                                                                                                                               |                                            |         | MAX   |       |                        |       |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|-------|-------|------------------------|-------|----------------|

| PARAM ETER/CONDITION                                                                                                                                                                                                                                          |                                            | SYM BOL | -335  | -262  | -26A/<br>-265/<br>-202 | UNITS | NOTES          |

| OPERATING CURRENT: One device bank; Active-Precharge;<br><sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM and DQSinputs changing once per clock cyle; Address and control inputs changing once every two clock cycles |                                            | IDD0    | 1,125 | 990   | 945                    | mA    | 20, 41         |

| OPERATING CURRENT: One device bank; Activ<br>Burst = 2; <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); IOU<br>control inputs changing once per clock cycle                                                                 |                                            | IDD1    | 1,215 | 1,080 | 1,080                  | mA    | 20, 41         |

| PRECHARGE POWER-DOWN STANDBY CURREIGIE; Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK (MIN); CKE                                                                                                                                                         |                                            | IDD2P   | 27    | 27    | 27                     | mA    | 21,28, 43      |

| IDLE STANDBY CURRENT: CS# = HIGH; All devi<br><sup>†</sup> CK MIN; CKE = HIGH; Address and other cont<br>once per clock cycle. VIN = VREF for DQ, DQS, a                                                                                                      | rol inputs changing                        | IDD2F   | 405   | 405   | 360                    | mA    | 46             |

| ACTIVE POWER-DOWN STANDBY CURRENT: Cactive; Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK (MIN); C                                                                                                                                                       |                                            | IDD3P   | 225   | 225   | 180                    | mA    | 21, 28 ,<br>43 |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CKE bank; Active-Precharge; <sup>t</sup> RC = <sup>t</sup> RAS(MAX); <sup>t</sup> CK and DQS inputs changing twice per clock cycle control inputs changing once per clock cycle                                           | $C = {}^{t}CK (MIN); DQ, DM$               | IDD3N   | 450   | 450   | 405                    | mA    |                |

| OPERATING CURRENT: Burst = 2; Reads; Continuous active; Address and control inputs change cycle; <sup>t</sup> CK = <sup>t</sup> CK (MIN); IOUT = 0mA                                                                                                          |                                            | IDD4R   | 1,260 | 1,170 | 1,125                  | mA    | 20, 41         |

| OPERATING CURRENT: Burst = 2; Writes; Contidevice bank active; Address and control input clock cycle; <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM, and DQS twice per clock cycle                                                                          | s changing once per                        | IDD4W   | 1,260 | 1,125 | 1,080                  | mA    | 20             |

| AUTO REFRESH CURRENT                                                                                                                                                                                                                                          | <sup>t</sup> REFC = <sup>t</sup> RFC (MIN) | IDD5    | 2,385 | 1,980 | 1,980                  | mA    | 20,43          |

| Ī                                                                                                                                                                                                                                                             | <sup>t</sup> REFC = 15.625µs               | IDD5A   | 45    | 45    | 45                     | mA    | 24, 43         |

| SELF REFRESH CURRENT: CKE ≤ 0.2V                                                                                                                                                                                                                              |                                            | IDD6    | 27    | 27    | 18                     | mA    | 9              |

| OPERATING CURRENT: Four device bank interlowith auto precharge, <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> C control inputs change only during Active REA commands                                                               | K (MIN); Address and                       | IDD7    | 3,195 | 2,970 | 2,925                  | mA    | 20, 42         |

## Table 13: IDD Specifications and Conditions - 256MB

DDR SDRAM components only

Notes: 1–5, 8, 10, 12, 47; notes appear on pages 20–23;  $0^{\circ}\text{C} \le T_{\text{A}} \le +70^{\circ}\text{C}$ ; VDD = VDDQ = +2.5V ±0.2V

|                                                                                                                                                                                                                                                               |                              |         |       | MAX   |                        |       |                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------|-------|-------|------------------------|-------|----------------|

| PARAM ETER/CONDITION                                                                                                                                                                                                                                          |                              | SYM BOL | -335  | -262  | -26A/<br>-265/<br>-202 | UNITS | NOTES          |

| OPERATING CURRENT: One device bank; Active-Precharge;<br><sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>†</sup> CK = <sup>t</sup> CK (MIN); DQ, DM and DQSinputs changing once per clock cyle; Address and control inputs changing once every two clock cycles |                              | IDD0    | 1,125 | 1,125 | 1,080                  | mA    | 20, 41         |

| OPERATING CURRENT: One device bank; Activ<br>Burst = 4; <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); low<br>control inputs changing once per clock cycle                                                                 | JT = 0mA; Address and        | IDD1    | 1,530 | 1,440 | 1,305                  | mA    | 20, 41         |

| PRECHARGE POWER-DOWN STANDBY CURRE idle; Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK (MIN); CKI                                                                                                                                                        |                              | IDD2P   | 36    | 36    | 36                     | mA    | 21,28, 43      |

| IDLE STANDBY CURRENT: CS# = HIGH; All dev <sup>†</sup> CK MIN; CKE = HIGH; Address and other con- once per clock cycle. VIN = VREF for DQ, DQS,                                                                                                               | trol inputs changing         | IDD2F   | 450   | 405   | 405                    | mA    | 46             |

| ACTIVE POWER-DOWN STANDBY CURRENT: (active; Power-down mode; <sup>t</sup> CK = <sup>t</sup> CK (MIN); C                                                                                                                                                       |                              | IDD3P   | 270   | 225   | 225                    | mA    | 21, 28 ,<br>43 |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CKE bank; Active-Precharge; <sup>†</sup> RC = <sup>†</sup> RAS(MAX); <sup>†</sup> ChandDQS inputs changing twice per clock cycle control inputs changing once per clock cycle                                             | $K = {}^{t}CK(MIN); DQ, DM$  | IDD3N   | 540   | 450   | 450                    | mA    |                |

| OPERATING CURRENT: Burst = 2; Reads; Contibank active; Address and control inputs chancycle; <sup>†</sup> CK = <sup>†</sup> CK (MIN); IOUT = 0mA                                                                                                              |                              | IDD4R   | 1,575 | 1,350 | 1,350                  | mA    | 20, 41         |

| OPERATING CURRENT: Burst = 2; Writes; Cont device bank active; Address and control input clock cycle; <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM, and DQ twice per clock cycle                                                                           | ts changing once per         | IDD4W   | 1,575 | 1,350 | 1,350                  | mA    | 20             |

| AUTO REFRESH CURRENT                                                                                                                                                                                                                                          | tREFC = tRFC (MIN)           | IDD5    | 2,295 | 2,115 | 2,115                  | mA    | 20,43          |

|                                                                                                                                                                                                                                                               | <sup>t</sup> REFC = 7.8125μs | IDD5A   | 54    | 54    | 54                     | mA    | 24, 43         |

| SELF REFRESH CURRENT: CKE ≤ 0.2V                                                                                                                                                                                                                              |                              | IDD6    | 36    | 36    | 36                     | mA    | 9              |

| OPERATING CURRENT: Four device bank interl<br>with auto precharge, <sup>†</sup> RC = <sup>†</sup> RC (MIN); <sup>†</sup> CK = <sup>†</sup> C<br>control inputs change only during Active REA<br>commands                                                      | CK (MIN); Address and        | IDD7    | 3,690 | 3,150 | 3,150                  | mA    | 20, 42         |

## Table 14: IDD Specifications and Conditions - 512MB

DDR SDRAM components only

Notes: 1–5, 8, 10, 12, 47; notes appear on pages 20–23;  $0^{\circ}\text{C} \le T_{\text{A}} \le +70^{\circ}\text{C}$ ; VDD = VDDQ = +2.5V ±0.2V

|                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                               |        | MAX   |       |                        |       |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|------------------------|-------|---------------|

| PARAM ETER/CONDITION                                                                                                                                                                                                |                                                                                                                                                                                                                                                               | SYMBOL | -335  | -262  | -26A/<br>-265/<br>-202 | UNITS | NOTES         |

| <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM an once per clock cyle; Address and control inp every two clock cycles                                                     | OPERATING CURRENT: One device bank; Active-Precharge;<br><sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM and DQSinputs changing once per clock cyle; Address and control inputs changing once every two clock cycles |        |       | 1,170 | 1,035                  | mA    | 20, 41        |

| OPERATING CURRENT: One device bank; Act Burst = 4; <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); lc control inputs changing once per clock cycle                                | out = 0mA; Address and                                                                                                                                                                                                                                        | IDD1   | 1,440 | 1,440 | 1,305                  | mA    | 20, 41        |

| PRECHARGE POWER-DOWN STANDBY CURFidle; Power-down mode; <sup>†</sup> CK = <sup>†</sup> CK (MIN); Ch                                                                                                                 |                                                                                                                                                                                                                                                               | IDD2P  | 45    | 45    | 45                     | mA    | 21, 28,<br>43 |

| IDLE STANDBY CURRENT: CS# = HIGH; All de <sup>†</sup> CK MIN; CKE = HIGH; Address and other conceper clock cycle. Vin = VREF for DQ, DQS                                                                            | ntrol inputs changing                                                                                                                                                                                                                                         | IDD2F  | 405   | 405   | 360                    | mA    | 44            |

| ACTIVE POWER-DOWN STANDBY CURRENT: active; Power-down mode; <sup>†</sup> CK = <sup>†</sup> CK (MIN);                                                                                                                |                                                                                                                                                                                                                                                               | IDD3P  | 315   | 315   | 270                    | mA    | 21,28,<br>43  |

| ACTIVE STANDBY CURRENT: CS# = HIGH; CK bank; Active-Precharge; <sup>†</sup> RC = <sup>†</sup> RAS(MAX); <sup>†</sup> C andDQSinputs changing twice per clock cycleontrol inputs changing once per clock cycleontrol | CK = <sup>t</sup> CK (MIN); DQ, DM<br>le; Address and other                                                                                                                                                                                                   | IDD3N  | 450   | 450   | 405                    | mA    |               |

| OPERATING CURRENT: Burst = 2; Reads; Cont<br>bank active; Address and control inputs char<br>cycle; <sup>t</sup> CK = <sup>t</sup> CK (MIN); IOUT = 0mA                                                             |                                                                                                                                                                                                                                                               | IDD4R  | 1,485 | 1,485 | 1,305                  | mA    | 20, 41        |

| OPERATING CURRENT: Burst = 2; Writes; Condevice bank active; Address and control input clock cycle; <sup>†</sup> CK = <sup>†</sup> CK (MIN); DQ, DM, and DO twice per clock cycle                                   | uts changing once per                                                                                                                                                                                                                                         | IDD4W  | 1,575 | 1,395 | 1,215                  | mA    | 20            |

| AUTO REFRESH CURRENT                                                                                                                                                                                                | <sup>t</sup> REFC = <sup>t</sup> RFC (MIN)                                                                                                                                                                                                                    | IDD5   | 2,610 | 2,610 | 2,520                  | mA    | 20, 43        |

|                                                                                                                                                                                                                     | <sup>t</sup> REFC = 7.8125μs                                                                                                                                                                                                                                  | IDD5A  | 90    | 90    | 90                     | mA    | 24, 43        |

| SELF REFRESH CURRENT: CKE ≤ 0.2V                                                                                                                                                                                    |                                                                                                                                                                                                                                                               | IDD6   | 45    | 45    | 45                     | mA    | 9             |

| OPERATING CURRENT: Four device bank inte with auto precharge, <sup>†</sup> RC = <sup>†</sup> RC (MIN); <sup>†</sup> CK = <sup>†</sup> control inputs change only during Active RE commands                          | CK (MIN); Address and                                                                                                                                                                                                                                         | IDD7   | 3,645 | 3,600 | 3,150                  | mA    | 20, 42        |

## Table 15: IDD Specifications and Conditions – 1GB

DDR SDRAM components only

Notes: 1–5, 8, 10, 12, 47; notes appear on pages 20–23;  $0^{\circ}\text{C} \le T_{\text{A}} \le +70^{\circ}\text{C}$ ; VDD = VDDQ = +2.5V ±0.2V

|                                                                                                                                                                                                                                                             |                                                                |         | MAX   |       |                        |       |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|-------|-------|------------------------|-------|---------------|

| PARAM ETER/CONDITION                                                                                                                                                                                                                                        |                                                                | SYM BOL | -335  | -262  | -26A/<br>-265/<br>-202 | UNITS | NOTES         |

| OPERATING CURRENT: One device bank; Active-Precharge; <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); DQ, DM and DQS inputs changing once per clock cyle; Address and control inputs changing once every two clock cycles |                                                                | IDD0    | 1,170 | 1,170 | 1,305                  | mA    | 20, 41        |