# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Si825x Multi-phase POL Reference Design User's Guide

### 1. Kit Contents

The non-isolated Si825x Multi-Phase Point of Load (POL) Reference Design contains the following items:

- 40 Amp Si8250-based Multi-Phase POL Target Board

- USB to SMBus<sup>™</sup> Bridge Board

- USB Debug Adapter

- USB Cable

- Silicon Laboratories IDE and Product Information CD-ROM. CD content includes the following:

- Silicon Laboratories Integrated Development Environment (IDE)

- Keil 8051 Development Tools (macro assembler, linker, evaluation C compiler)

- Source code examples and register definition files

- Multi-Phase POL Firmware Kernel

- Application Builder tool suite (waveform editor, compensator, system and MCU wizards)

- SMBus<sup>TM</sup> Monitor Software

- Documentation: Kernel flowcharts and Si825x data sheet

- Si825x Multi-Phase POL Reference Design User's Guide (this document)

- **Note:** The full version of the Kernel when compiled is approximately 14 kB. This exceeds the 4 kB limit of the compiler that is shipped with the kit's software development tools. To avoid a compiler limit issue, either buy the full Keil compiler toolset or compile the limited version of the Kernel.

# 2. Hardware Overview

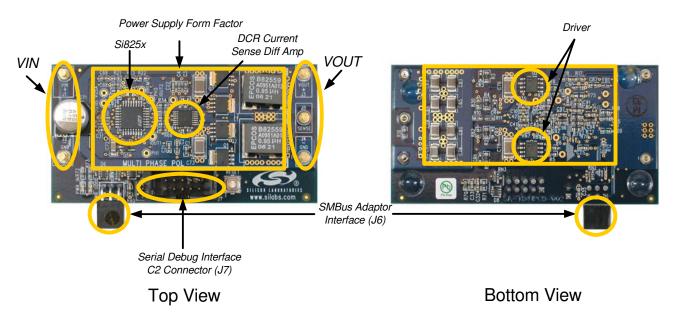

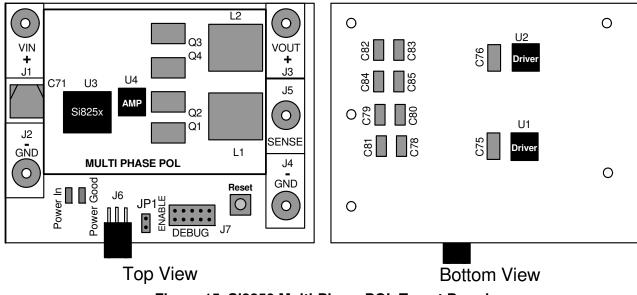

The Si825x Multi-Phase POL Reference Design implements a digitally-controlled POL with a DPWM (digital pulse width modulation) switching frequency of 391 kHz. The Si8250 Multi-Phase POL Target Board (Figure 1) contains system power stages and digital control circuits with debug connectors for the Si8250 digital power controller. The user can also access and control the target board using SMBus.

Figure 1. Si8250 Multi-Phase POL Target Board

# 3. Si8250 Multi Phase POL Target Board Stand-Alone Operation

The POL target board comes preloaded with firmware algorithms, and is designed to provide a 3.3 V output with up to 40 Amps of output current.

To operate the target board as a stand-alone power supply, perform the following steps:

- 1. Connect a V<sub>IN</sub> power supply to the V<sub>IN</sub> terminals (J1 and J2) as shown in Figure 2. Do not yet turn the power supply on.

- Connect a load to the V<sub>OUT</sub> terminals (J3 and J4) as shown in Figure 2. For initial testing, a 2 Ω, 15 W resistor is recommended. For higher output currents, an electronic load simulator can be used.

- 3. Turn the V<sub>IN</sub> supply on. The converter will start up and provide 3.3 V at V<sub>OUT</sub>.

Figure 2. Board Power Configuration

# 4. Development/Debug Operation: Initial Hardware Setup

This section describes the use of the Si8250 Multi-Phase POL Target Board with the Silicon Laboratories integrated development environment (IDE) and Application Builder tools. To configure the hardware for connection to the IDE:

- 1. Connect a  $V_{IN}$  power supply to the  $V_{IN}$  terminals (J1 and J2) as shown in Figure 2. Do not yet turn the power supply on.

- Connect the USB Debug Adaptor's ribbon cable to the Si8250 Multi-Phase POL Target Board at J7 as shown in Figure 3.

- 3. Connect the USB cable to the USB Debug Adapter's USB input plug.

- 4. Connect the USB cable from the USB Debug Adapter to a USB port on the PC.

- 5. Turn the  $V_{IN}$  supply on.

Figure 3. Overall View of the Debug Connection (Load not Connected)

# 5. Development/Debug Operation: Software Setup

The Si825x Multi-Phase POL Reference Design comes with Application Builder software (detailed in "8. Si825x Application Builder" on page 12), a configurable real-time software Kernel, and a software Kernel compiled specifically for the Si8250 Multi-Phase POL Target Board.

The Kernel is royalty-free application software for the Si825x family of digital power controllers that greatly reduces application program development time, effort, and engineering risk. The Application Builder is used to customize the Kernel and create C-code source level application software for the Si825x end application. The Application Builder directly modifies the source code in the Kernel, which is then compiled and downloaded to the Si825x. For more information on the Kernel, see application note "AN271: Si8250 Real-Time Kernel Overview".

The Multi\_Phase\_POL directory (*SiLabs\Power\Reference\_Designs\Multi\_Phase\_POL\Firmware*) contains the Kernel configured for the Si8250 Multi-Phase POL Target Board.

Kernel software can be loaded/reloaded to the target board using the Silicon Laboratories IDE. Note that hardware must be set up as detailed in "4. Development/Debug Operation: Initial Hardware Setup" on page 4. Follow the instructions below to configure and download the **Multi\_Phase\_POL** application software for the Si8250 Multi-Phase POL Target Board.

- **Note:** A thorough understanding of the IDE is required before one can use the development/Debug Mode of the kit. The IDE is detailed in "7. Silicon Laboratories Integrated Development Environment".

- The included CD-ROM contains the Silicon Laboratories Integrated Development Environment (IDE), Application Builder examples, the PMBus Monitor, Keil software 8051 tools, and additional documentation. Insert the CD-ROM into your PC's CD-ROM drive. An installer will automatically launch allowing you to install the software or read documentation by clicking buttons on the installation panel. If the installer does not automatically start when you insert the CD-ROM, run *autorun.exe* found in the root directory of the CD-ROM. Refer to the *ReleaseNotes.txt* file on the CD-ROM for the latest information regarding known problems and restrictions. See "7. Silicon Laboratories Integrated Development Environment" on page 9 for further information on the development tools.

- 2. Open the IDE by selecting **Silicon Laboratories**  $\rightarrow$  **Silicon Laboratories IDE** from the PC programs menu.

Next, the example project included with the kit is opened. Select Project→Open Project... from the IDE menus. In the Project Workspace window, browse to the "SiLabs\Power\Reference\_Designs\Multi\_Phase\_POL\Firmware\Multi\_phase\_POL\Source" directory and select the \*.wsp project file. Press Open to close the window and open the project.

- **Note:** This example will only work with the full version of the Keil compiler. If the demonstration compiler is used, use the files in "*SiLabs\Power\Reference\_Designs\Multi\_Phase\_POL\Firmware\Multi\_phase\_POL\_basic\Source*". This code will compile to less than 4 kB of code.

- 4. The Si8250 Multi-Phase POL Target Board has several connection requirements that must be specified before connecting to the board. Select Options→Connection Options... from the IDE menu. In the Connection Options window, select USB Debug Adapter in the Serial Adapter section. Next, select C2 in the Debug Interface section. The Si825x family of devices use the Silicon Laboratories 2-wire (C2) debug interface. Click OK to close the window.

- 5. Click the **Connect** button in the toolbar or select **Debug**  $\rightarrow$  **Connect** from the menu to connect to the device.

- Build the project by clicking on the Build/Make Project button in the toolbar or by selecting Project→Build/ Make Project from the menu.

- Note: After the project has been built the first time, the Build/Make Project command will only build the files that have been changed since the previous build. To rebuild all files and project dependencies, click on the Rebuild All button in the toolbar or select Project→Rebuild All from the menu.

- 7. Download the project to the target by clicking the Download Code button in the toolbar.

- Note: To enable automatic downloading if the program build is successful, select Enable automatic connect/download after build in the Project→Target Build Configuration dialog. If errors occur during the build process, the IDE will not attempt the download.

- Connect a load to the V<sub>OUT</sub> terminals (J3 and J4) as shown in Figure 2 on page 3. For initial testing, a 2 Ω, 15 W resistor is recommended. For higher output currents, an electronic load simulator can be used.

- 9. Run the converter firmware by pressing the "Go" button in the IDE toolbar. The converter will start up and provide 3.3 V at V<sub>OUT</sub>.

- 10. Save the project when finished with the debug session to preserve the current target build configuration, editor settings, and location of all open debug views. To save the project, select **Project**→**Save Project** from the menu.

# 6. PMBus Operation

PMBus is a connectivity solution designed for networking multiple power supplies using a single management bus. The Real-time Kernel provided with the Si825x Multi-Phase POL Reference Design includes optional support for PMBus. In addition, the Si825x POL design kit also comes with a PMBus Monitor application and USB to SMBus Bridge Board to manage the power supply through PMBus.

- 1. The PMBus Monitor software is installed during the initial software setup. (See "5. Development/Debug Operation: Software Setup" on page 5.)

- 2. Connect the board as shown in "3. Si8250 Multi Phase POL Target Board Stand-Alone Operation" on page 3. Note that the PMBus Monitor may also be operated with the USB Debug Adaptor. If this is desired, connect the target board as shown in "4. Development/Debug Operation: Initial Hardware Setup" on page 4.

- 3. Drivers must be installed to allow the PMBus Monitor to communicate with the USB to SMBus Bridge Board. The driver files are located by default in the "*Silabs\Power\Si825x AppBuilder\PMBus Monitor\USB-SMBus Bridge Board Drivers*" directory. Run the *PreInstaller.exe* application. This program will copy the driver files to the PC's "Program Files" directory and then register the driver files so the board will be recognized when it is connected. Windows Logo testing warnings may appear. Press the **Continue Anyway** button.

- 4. Connect the USB to SMBus Bridge Board to an available USB slot on your PC with a USB cable.

- 5. Windows will open a Found New Hardware Wizard window. Press Next after selecting the (Recommended) option. Windows Logo testing warnings may appear. Press the Continue Anyway button. Press "Finish" to finish installing the USB to SMBus Bridge Board.

- 6. Connect the Si8250 Multi-Phase POL Target Board to the USB to SMBus Bridge Board as shown in Figure 4.

Figure 4. USB to SMBus Bridge Board Connection (Load not Connected)

- 7. Open the Application Builder by selecting Silicon Laboratories→Si825x Application Builder from the PC programs menu.

- 8. Run the PMBus Monitor application by selecting **Options→Launch PMBus Monitor Tool** from the Application Builder. The window shown in Figure 5 will appear. The PMBus Monitor can be used to control and configure the target board. The target can be enabled/disabled through the monitor. The PMBus Monitor allows parameters, such as fault thresholds, to be changed. It also reports operating conditions and problems.

| ower Supply Informatio | n                  | Power Supply Status  |  |

|------------------------|--------------------|----------------------|--|

| Input Voltage (V)      | Output Voltage (V) | 📕 Unit is Busy       |  |

| 12.4                   | 3.330              | 🗾 Unit is Off        |  |

| Input Current (A)      | Output Current (A) | 📕 VOUT Over Voltage  |  |

| 0.0                    | 4.0                | 📕 IOUT Over Current  |  |

| 0.0                    | 4.0                | 📕 VIN Under Voltage  |  |

| Duty Cycle             | Frequency (kHz)    | 📕 Temperature        |  |

| 24.5                   | 380.0              | E CML                |  |

| Temper                 | ature (°C)         | 📕 Other              |  |

|                        | 22.5               | Details Clear Faults |  |

| n Configuration        | Off Configura      | ation Connection     |  |

| Low Margin Out Volt    | age Soft OI        | ff Pause             |  |

| Command Output Vol     | tage               |                      |  |

Figure 5. View of the PMBus Monitor

# 7. Silicon Laboratories Integrated Development Environment

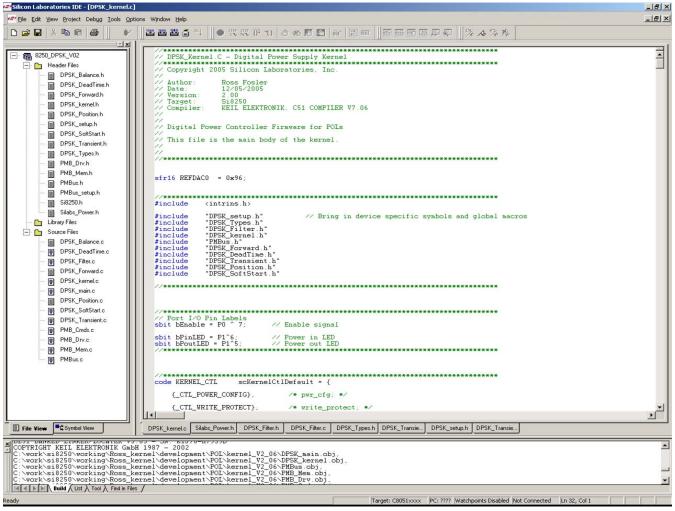

The Silicon Laboratories IDE combines an editor, project manager, code development tools, and a debugger into a single intuitive environment for code development and in-system debugging. No additional target RAM, program memory, or communications channels are required. The use of third-party compilers and assemblers is also supported. This development kit includes the Keil Software A51 macro assembler, BL51 linker, and evaluation version C51 C compiler. These tools can be used from within the Silicon Laboratories IDE. Figure 6 shows the IDE.

Figure 6. IDE

#### 7.1. System Requirements

Silicon Laboratories IDE requirements are as follows:

- Pentium-class host PC running Microsoft Windows 95 or later or Microsoft Windows NT or later.

- One available USB port.

- 64 MB RAM and 40 MB free HD space recommended.

#### 7.2. Assembler and Linker

A full-version Keil A51 macro assembler and BL51 banking linker are included with the development kit and are installed during IDE installation. The complete assembler and linker reference manual can be found online under the **Help** menu in the IDE or in the "*SiLabs\MCU\hlp*" directory (A51.pdf).

### 7.3. Evaluation C51 C Compiler

An evaluation version of the Keil C51 C compiler is included with the development kit and is installed during IDE installation. The evaluation version of the C51 compiler is the same as the full professional version except, that code size is limited to 4 kB, and the floating point library is not included. The C51 compiler reference manual can be found under the **Help** menu in the IDE or in the "*SiLabs\MCU\hlp*" directory (C51.pdf).

#### 7.4. Using the Keil Software 8051 Tools with the Silicon Laboratories IDE

To perform source-level debugging with the IDE, you must configure the Keil 8051 tools to generate an absolute object file in the OMF-51 format with object extensions and debug records enabled. You may build the OMF-51 absolute object file by calling the Keil 8051 tools at the command line (e.g. batch file or make file) or by using the project manager built into the IDE. The default configuration when using the Silicon Laboratories IDE project manager enables object extension and debug record generation. Refer to application note "AN104: Integrating Keil 8051 Tools Into the Silicon Labs IDE" for additional information on using the Keil 8051 tools with the Silicon Laboratories IDE.

To build an absolute object file using the Silicon Laboratories IDE project manager, you must first create a project. A project consists of a set of files, IDE configuration, debug views, and a target build configuration (list of files and tool configurations used as input to the assembler, compiler, and linker when building an output object file).

The following sections illustrate the steps necessary to manually create a project with one or more source files, build a program, and download the program to the target in preparation for debugging. (The IDE will automatically create a single-file project using the currently open and active source file if you select "Build/Make Project" before a project is defined.)

#### 7.4.1. Creating a New Project

- 1. Select **Project** → **New Project** to open a new project and reset all configuration settings to default.

- 2. Select **File**→**New File** to open an editor window. Create your source file(s) and save the file(s) with a recognized extension, such as \*.c, \*.h, or \*.asm, to enable color syntax highlighting.

- 3. Right-click on **New Project** in the **Project Window**. Select **Add files to project**. Select files in the file browser and click "Open". Continue adding files until all project files have been added.

- 4. For each of the files in the **Project Window** that you want assembled, compiled, and linked into the target build, right-click on the file name and select **Add file to build**. Each file will be assembled or compiled as appropriate (based on file extension) and linked into the build of the absolute object file.

- **Note:** If a project contains a large number of files, the "Group" feature of the IDE can be used to organize them. Right-click on **New Project** in the **Project Window**. Select **Add Groups to project**. Add predefined groups or add customized groups. Right-click on the group name and choose **Add file to group**. Select files to be added. Continue adding files until all project files have been added.

#### 7.4.2. Building and Downloading the Program for Debugging

- 1. Once all source files have been added to the target build, build the project by clicking on the "Build/Make Project" button in the toolbar or selecting **Project**→**Build/Make Project** from the menu.

- **Note:** After the project has been built the first time, the Build/Make Project command will only build the files that have been changed since the previous build. To rebuild all files and project dependencies, click on the "Rebuild All" button in the toolbar or select **Project->Rebuild All** from the menu.

- Before connecting to the target device, several connection options may need to be set. Open the "Connection Options" window by selecting Options→Connection Options... in the IDE menu. First, select the adapter that was included with the kit in the "Serial Adapter" section. Next, the correct "Debug Interface" must be selected. Si825x family devices use the Silicon Laboratories 2-wire (C2) debug interface. Once all the selections are made, click the OK button to close the window.

- 3. Click the **Connect** button in the toolbar or select **Debug**  $\rightarrow$  **Connect** from the menu to connect to the device.

- 4. Download the project to the target by clicking the **Download Code** button in the toolbar.

- Note: To enable automatic downloading if the program build is successful, select Enable automatic connect/download after build in the Project→Target Build Configuration dialog. If errors occur during the build process, the IDE will not attempt the download.

5. When finished with the debug session, save the project to preserve the current target build configuration, editor settings, and the location of all open debug views. To save the project, select Project→Save Project As... from the menu. Create a new name for the project, and click on Save.

#### 7.5. Si825x Debug Mode

The IDE contained in the Si825x Multi-Phase POL Reference Design has an online debug feature that optionally enables the user to inspect or update special function registers (SFRs) in the Si825x while it is operating. For example, filter coefficients can be optimized by simply typing in new coefficient values while the supply is connected to a network analyzer and running. The IDE can also be operated in Standard mode where SFR inspect and update is allowed only when the Si825x is not running. As shown in Figure 7, the IDE can be set for Online Debug Mode or Standard Debug mode by clicking on the circled mode switch.

| 🥙 Silicon Laboratories IDE                                              | 🗢 Silicon Laboratories IDE                             |

|-------------------------------------------------------------------------|--------------------------------------------------------|

| Elle Edit View Project Debug Tools Options Window Help                  | Eile Edit View Project Debug Tools Options Window Help |

| 」 <b>□ ☞ ■   ½ ℡ 竜   垂 〔09</b> 〕] <b>22 22 23 2 - "↓</b> ]] ●   33 33 6 | ×∎ × ħ €  5 (►)  22 28 26 5 ч↓   ●   33                |

| New_Project.                                                            | New_Project                                            |

Figure 7. Si825x IDE Debug Modes

# 8. Si825x Application Builder

In addition to the IDE, the Si825x family is supported with an intuitive toolset that leverages traditional power supply control design methods minimizing the digital supply design learning curve. The toolset consists of a real-time firmware Kernel (C-language source code), and the **Application Builder** (see Figure 8). The Application Builder includes device peripheral configuration options with the **Peripheral Configuration Wizard**. Additionally, the Application Builder tools are used to modify Kernel operations. Three key development tools within the Application Builder are the **DPWM Timing Diagram Editor**, the **System Parameter Programmer**, and the **Compensation Editor**. These tools are detailed in the following sections. The flow diagrams for the Kernel are included on the CD.

| Application Builder - Untitled Si8250 File Options Peripherals System Configuration V | ew Help |          |

|---------------------------------------------------------------------------------------|---------|----------|

|                                                                                       |         |          |

| 🔗 Untitled Si8250                                                                     |         |          |

| ///////////////////////////////////////                                               | 25 12 L | ^        |

| <pre>// Generated Initialization Fil</pre>                                            |         |          |

| ///////////////////////////////////////                                               | /////   |          |

| #include "si8250.h"                                                                   |         |          |

| //Definitions for Settings                                                            |         |          |

| #define KERNEL_ISOLATED                                                               | 1       |          |

| #define KERNEL_PMBUS_ENABLE                                                           | 1       |          |

| // Definitions for System Parame                                                      | ters    |          |

| #define KERNEL_POWER_CONFIG                                                           | Ox1E    |          |

| #define KERNEL_VIN_SCALE                                                              | 0x67    |          |

| #define KERNEL_VIN_OV_FAULT                                                           | 60L     |          |

| #define KERNEL_VIN_OV_WARN                                                            | 57L     |          |

| #define KERNEL_VIN_UV_WARN                                                            | 34L     |          |

| #define KERNEL_VIN_UV_FAULT                                                           | 32L     |          |

| #define KERNEL VOUT SCALE                                                             | 100000L |          |

| #define KERNEL_VOUT_HIGH                                                              | 1050L   |          |

| #define KERNEL_VOUT                                                                   | 1000L   |          |

| #define KERNEL_VOUT_LOW                                                               | 950L    | -        |

| Haafina VEDNEI VOUT TOTM                                                              |         | <u> </u> |

|                                                                                       |         |          |

|                                                                                       |         |          |

|                                                                                       |         |          |

Figure 8. Si825x Application Builder

#### 8.1. DPWM Timing Diagram Editor

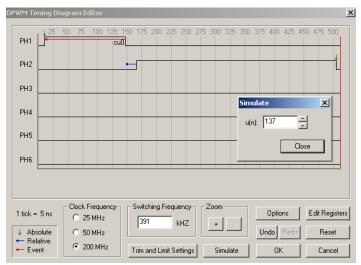

The **DPWM Timing Diagram Editor** permits designers to generate DPWM initialization code by simply drawing the timing for their end system. The wizard accommodates up to six output phases and can be used to establish positive or negative dead-times, relative edges, absolute edges, and other timing required by the end system. Refer to the Si825x data sheet for a description of the different edges.

This example illustrates how to use the **DPWM Timing Diagram Editor** to create and simulate the timing for a single-phase POL as well as generate the initialization code in the Kernel.

- 1. To open the **DPWM Timing Diagram Editor** window, open the Application Builder and select **System Configuration**→**DPWM Timing Diagram Editor** from the menu.

- To create an absolute edge on Phase 1, hold the mouse above the Phase 1 zero timing line (default) at time tick 10. Then, either double click with the left mouse button or right-click at that point and select Absolute Edge. An absolute edge at time tick 10 will be created (see Figure 9).

- To finish the timing for Phase 1, specify hardware modulation using (Cu0). This event edge will be modulated relative to its absolute edge at time tick 10. To create this edge, hold the mouse above the Phase 1 timing line to the right of time tick 10 at time tick 60. Either double-click or right-click at that point and select Event (Cu0) Edge. Next, select the edge to reference by clicking on edge 1 in Phase 1. A relative falling (Cu0) edge will be created at time tick 60 since u(n) defaults to 50 (see Figure 9).

| PWM Timing Diagram Editor                                                                                                                                                                                                                                                                | DPWM Timing Diagram Editor                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PH1<br>PH2<br>PH3<br>PH4<br>PH6                                                                                                                                                                                                                                                          | PH1         100 125 150 175 200 225 250 275 300 325 350 375 400 425 450 475 500           PH2         PH3           PH4         PH4           PH5         PH6                                                                                                      |

| 1 tick = 5 ns     Clock Frequency     C 25 MHz     Switching Frequency     Zoom     Options     Edit Registers       ↓ Absolute     C 50 MHz     391     kHZ     +     Undo     Redo     Reset       ← Relative     C 200 MHz     Trim and Limit Settings     Simulate     OK     Cancel | 1 tick = 5 ns     Clock Frequency     Switching Frequency     Zoom     Options     Edit Registers       ↓ Absolute     C 50 MHz     331     kHZ     +     Undo     Reset       ← Relative     C 200 MHz     Trim and Limit Settings     Simulate     OK     Cancel |

Figure 9. DPWM Timing Diagram Editor—Phase 1

- 1. Now, create the timing for Phase 2. For Phase 2, the goal is to create a relative rising edge relative to the falling edge of Phase 1 and an absolute falling edge on Phase2 at time tick 505. To create the relative rising edge, hold the mouse above the Phase 2 zero timing line (default) at time tick 100. Then, either double-click with the left mouse button or right-click at that point and select **Relative Edge**. Next, select the edge to reference by clicking on Phase 1's falling edge. A relative edge at approximately time tick 90 will be created (see Figure 10).

- 2. To finish the timing for Phase 2, create an absolute falling at time tick 505. To create this edge, hold the mouse above the Phase 2 timing line at time tick 505. Then, either double-click with the left mouse button or right-click at that point and select **Absolute Edge**. An absolute edge at time tick 505 will be created (see Figure 10).

# Si825x Multi-Phase POL-RD

| DPWM Timing Diagram Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DPWM Timing Diagram Editor                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| PH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PH1                                                                                                                   |

| РН3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | РНЗ                                                                                                                   |

| PH4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PH4                                                                                                                   |

| РН5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PH5                                                                                                                   |

| РН6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | РН6                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                       |

| 1 tick = 5 ns     Clock Frequency     Switching Frequency     Zoom     Options     Edit Registers <ul> <li>Absolute</li> <li>Relative</li> <li>200 MHz</li> <li>Trim and Limit Settings</li> <li>Simulate</li> <li>OK</li> <li>Cancel</li> </ul> <li>Com</li> <li>Options</li> <li>Edit Registers</li> <li>Edit R</li> | 1 tick = 5 ns     Clock Frequency-<br>2 5 MHz     Switching Frequency-<br>391     Zoom     Options     Edit Registers |

Figure 10. DPWM Timing Diagram Editor—Phase 2

3. Click the **Simulate** button to display the Simulate Window (see Figure 11). Use the arrows to increase and decrease the value of u(n). Notice that Phase 1's edge should modulate with its absolute edge starting at 10 ticks. Phase 2 should also modulate. However, its rising edge starts relative to Phase 1's falling edge.

Figure 11. DPWM Timing Diagram Editor—Timing Simulator

4. Now that the desired timing for the two-phase system has been created, click on OK. The Application Builder will automatically extract the correct DPWM timing initialization data for the Kernel. These coefficients can be saved to a new project file if desired for later use. Click on File→Save Project to save this project. To generate an IDE project, select File→Build IDE Project... and select the directory for project generation.

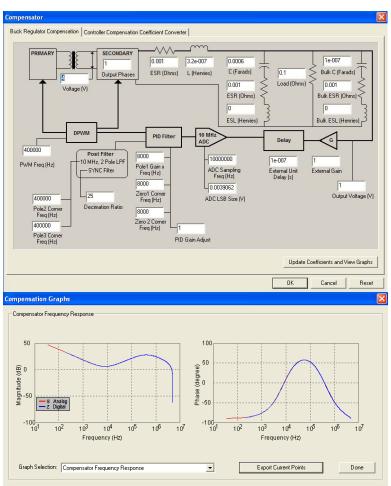

#### 8.2. Compensation Editor

The **Compensation Editor** is a loop simulation and coefficient generator tool for frequency compensating the system. To open the **Compensation Editor** window, open the Application Builder and select **System Configuration**→**Compensation Editor** from the menu. The Compensation Editor for a buck regulator is shown in Figure 12. As shown, this tool provides fields for the user to enter power stage parameters, such as the output filter component and parasitic values; controller parameters, such as PWM frequency and pole/zero locations; and Si825x-specific data, such as ADC sample frequency. The simulator comes pre-populated with default values for the **Si8250 Half-Bridge Target Board**. These model parameters can be changed as desired to accommodate other buck topologies. To view the gain and phase plots with the default parameters, click on the View Graphs button, and their plots will be generated a short time later. Moreover, clicking on the View Graphs button, the user can view different responses of the buck regulator. Sample graphs are shown in Figure 12.

Table 1 shows two frequency responses for the multi-phase POL: one for steady-state operation and one for operation during a transient. During transients, the Si8250 automatically extends loop bandwidth by writing faster coefficients to the loop compensation filter (DSP filter engine). This nonlinear control response improves system transient response, reducing both the magnitude and duration of the output transient.

|                     | Steady-State Response | Transient Response |

|---------------------|-----------------------|--------------------|

| Loop Gain Bandwidth | 45 kHz                | 95 kHz             |

| Phase Margin        | 54º                   | 25º                |

Table 1. Si8250 Multi-Phase POL Target Board's Frequency Response

Figure 12. Compensation Editor, Input/Output Windows

#### 8.3. System Parameter Programmer

The **System Setting Programmer** allows the designer to input all system settings (UVLO, OV, OCP, etc.) and then converts these parameters to HEX and populates the resulting initialization code in the Kernel. To open the **System Settings** window, open the Application Builder and select **System Configuration** $\rightarrow$ **System Settings** from the menu (see Figure 13).

| Settings                                                                                  |                                                                                                       |                                | ×                                             |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|

| Soft Stop Parameters Fau                                                                  | It Responses  <br>put Voltage Threshold<br>Over Voltage<br>Fault Limit (V)                            | Peak Current Limit Detector    | On/Off Configuration<br>Soft Start Parameters |

| (No Change in State)<br>57<br>Supply On<br>34<br>(No Change in State)<br>32<br>Supply Off | Over Voltage<br>Warn Limit (V)<br>Under Voltage<br>Warn Limit (V)<br>Under Voltage<br>Fault Limit (V) | 103<br>Input Voltage Scale (V) |                                               |

|                                                                                           |                                                                                                       | OK                             | Cancel Reset                                  |

Figure 13. System Parameters Window

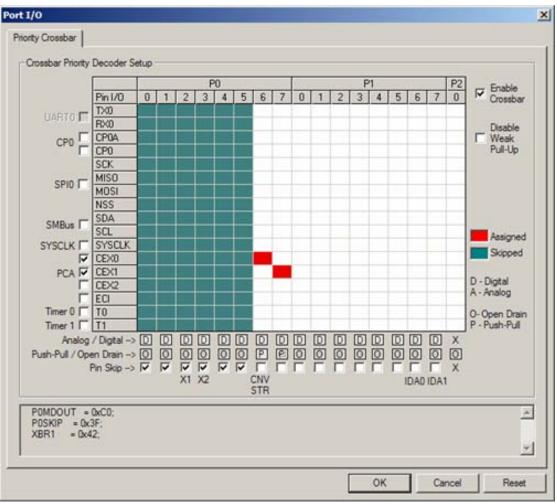

#### 8.4. Peripheral Configuration Wizard

The **Peripheral Configuration Wizard** can be used to automatically generate initialization code for the Si825x's onchip peripherals (ADC2, comparator, UART, SMBus<sup>TM</sup>, etc.). The peripheral windows can be accessed by clicking on the **Peripherals** menu in the Application Builder. Figure 14 illustrates the **Port I/O** window. For more details on using this wizard, consult the "Help" file by clicking on **Help**→**Help...**.

Figure 14. Peripheral Configuration Wizard—Port I/O Window

# 9. Restoring Factory Defaults

The Si825x Multi-Phase POL Reference Design includes hex files created for the multi-phase POL application. Downloading these hex files to the Si8250 Multi-Phase POL Target Board will restore the board to its factory defaults.

#### 9.1. Restoring the Si8250

To download the factory default Si8250 hex file to the target board, perform the following steps:

- 1. Connect the USB Debug Adaptor's ribbon cable to the Si8250 Multi-Phase POL Target Board at J7 as shown in Figure 3 on page 4.

- 2. Open the IDE by selecting Silicon Laboratories →Silicon Laboratories IDE from the PC programs menu.

- 3. The Si8250 Multi-Phase POL Target Board has several connection requirements that need to be specified before connecting to the board. Select Options→Connection Options... from the IDE menu. In the Connection Options window, select USB Debug Adapter in the Serial Adapter section. Next, select C2 in the Debug Interface section. The Si825x family of devices use the Silicon Laboratories 2-wire (C2) debug interface. Press OK to close the window.

- 4. Click the **Connect** button in the toolbar or select **Debug**→**Connect** from the menu to connect to the device.

- 5. Select **Debug** → **Download Object File...** from the IDE menus to open the download window.

- 6. Press the Browse button to open the Download Filename... window.

- 7. In the List files of type: drop down box, select the Intel-Hex option.

- 8. Browse to the "*SiLabs\Power\Reference\_Designs\Multi\_Phase\_POL\Firmware\multi\_phase\_POL\hex*" directory and select the \***.hex** file. Press OK to close the window.

- 9. Press the Download button to download the file.

- 10.Click the **Disconnect** button in the toolbar, or select **Debug**→**Disconnect** from the menu to disconnect from the device.

- 11. Power cycle the device to run the downloaded program.

# 10. Si8250 Multi-Phase POL Target Board

The Si8250 Multi-Phase POL Target Board has a Si8250-IQ installed. Refer to Figure 15 for the locations of the various I/O connectors and major components.

- J1, J2 VIN, Supply Input power connection 10-15 V, 10 A

- J3, J4 VOUT, Supply output connection for load simulator

- J5, J4 Alternate VOUT monitoring node

- J6 SMBus adapter

- J7 Si8250 Debug Interface

- JP1 Si8250 ENABLE Polarity Select

- LED VIN Power Good Indicator

- LED VOUT Power Good indicator

- RESET Si8250 and Target Board Reset

Figure 15. Si8250 Multi-Phase POL Target Board

#### 10.1. System Clock Sources

The Si8250-IQ device installed on the target board features a calibrated programmable internal oscillator that is enabled as the system clock source on reset. After reset, the device operates at a frequency of 80 kHz by default using the internal low-frequency oscillator but may be configured by software to operate at other frequencies. Refer to the Si825x family data sheet for more information on configuring the system clock source.

#### 10.2. Switches and LEDs

One switch is provided on the target board. Switch S1 is connected to the RESET pin of the Si8250. Pressing S1 puts the Si8250 device into its hardware-reset state.

Two LEDs are also provided on the target board. The POWER IN LED is used to indicate that the POL target board is properly powered. The POWER GOOD LED is used to indicate that VOUT power is being regulated by the Si8250. See Table 2 for a description of each LED and on board switches.

| Label     | Reference | Description                                    |

|-----------|-----------|------------------------------------------------|

| RST       | S1        | Si8250 Reset Switch                            |

| POWERIN   | LED       | Indicates that $V_{IN}$ is operating properly  |

| POWERGOOD | LED       | Indicates that $V_{OUT}$ is regulated properly |

#### Table 2. Target Board Switch and LED Descriptions

#### 10.3. V<sub>IN</sub> (J1, J2)

The user-provided power supply should be connected to connectors J1 and J2 where J2 is the reference. The power source must be from 10–15 V with at least 10 A maximum output.

Table 3. J1, J2 Pin Descriptions

| Jumper # | Description   |

|----------|---------------|

| J1       | 10–15 V, 10 A |

| J2       | GND           |

#### 10.4. V<sub>OUT</sub> (J3, J4)

Connectors J3 and J4 are the dc output from the Si8250 Multi-Phase POL Target Board. A load (preferably electronic) should be connected here.

Table 4. J3, J4 Pin Descriptions

| Jumper # | Description               |

|----------|---------------------------|

| J3       | 3.3 V (Nominal), 40 A max |

| J4       | GND                       |

#### 10.5. V<sub>OUT</sub> (J5, J4)

Connectors J5 and J4 provide an alternate output monitoring note that minimizes output loading while  $V_{OUT}$  is being monitored.

| Jumper # | Description                                       |

|----------|---------------------------------------------------|

| J5       | Alternate V <sub>OUT</sub> Sense, minimal loading |

| J4       | GND                                               |

#### Table 5. J5, J4 Pin Descriptions

#### 10.6. SMBus Connector (J6)

The J6 connector is the SMBus interface connector for the Si8250 Multi-Phase POL Target Board. Table 6 shows the J6 pin definitions.

| Pin # | Description |

|-------|-------------|

| 1     | SCL         |

| 2     | DGND        |

| 3     | SDA         |

| 4     | DGND        |

| 5     | SMBA        |

| 6     | DGND        |

#### Table 6. J6 Pin Descriptions

#### 10.7. Si8250 DEBUG Interface (J7)

The Si8250 DEBUG connector (J7) provides access to the DEBUG (C2) pins of the Si8250 device on the target board. It is used to connect the USB Debug Adapter to the target board for in-circuit debugging and programming. Table 7 shows the J7 Si8250 DEBUG pin definitions.

#### Table 7. P1 Si8250 DEBUG Connector Pin Descriptions

| Pin #       | Description   |

|-------------|---------------|

| 1           | +2.5 V        |

| 2, 3, 9     | DGND          |

| 4           | C2D           |

| 7           | RST/C2CK      |

| 5, 6, 8, 10 | Not Connected |

#### 10.8. Si8250 ENABLE Polarity Select (JP1)

The JP1 jumper selects the polarity of the reset line for the Si8250. When installed, the reset signal is active high; otherwise, it is active low.

#### 10.9. Voltage and Current Sense Test Points

The Si8250 Multi-Phase POL Target Board has several test points for  $V_{REF}$ ,  $V_{INSENSE}$ ,  $I_{IN}$ ,  $V_{SENSE}$ , all PHn,  $I_{PK}$ , and more. These test points correspond to the respective pins on the Si8250-IQ integrated circuit as well as other useful inspection points. See "12. Schematics" on page 23.

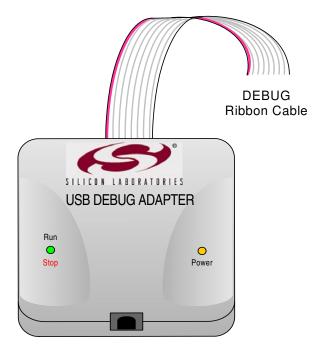

# 11. USB Debug Adapter

The USB Debug Adapter provides the interface between the PC's USB port and the Si825x's in-system debug/ programming circuitry. The attached 10-pin DEBUG ribbon cable connects the adapter to the target board and the target device's debug interface signals. (The USB Debug Adapter supports both Silicon Laboratories JTAG and C2 debug interfaces.) Power is provided to the adapter from the USB connection to the PC. The USB Debug Adapter is capable of providing power to a circuit board via pin 10 of the DEBUG connector. The Si8250 Multi-Phase POL Target Board is not designed to be powered from this source. Table 8 shows the pin definitions for the DEBUG ribbon cable connector.

**Note:** The USB Debug Adapter requires a target system clock of 32 kHz or greater. With the default settings, the USB Debug Adapter can supply up to 100 mA to a target system.

| Pin #   | Description   |

|---------|---------------|

| 1, 8    | Not Connected |

| 2, 3, 9 | GND (Ground)  |

| 4       | TCK (C2D)     |

| 5       | TMS           |

| 6       | TDO           |

| 7       | TDI (C2CK)    |

| 10      | USB Power     |

Table 8. USB Debug Adapter DEBUG Connector Pin Descriptions

USB Connector

Figure 16. USB Debug Adapter

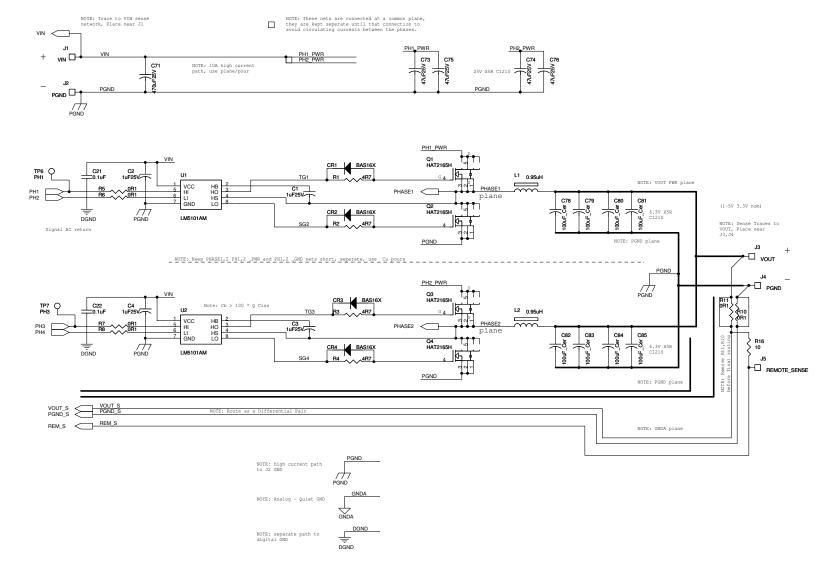

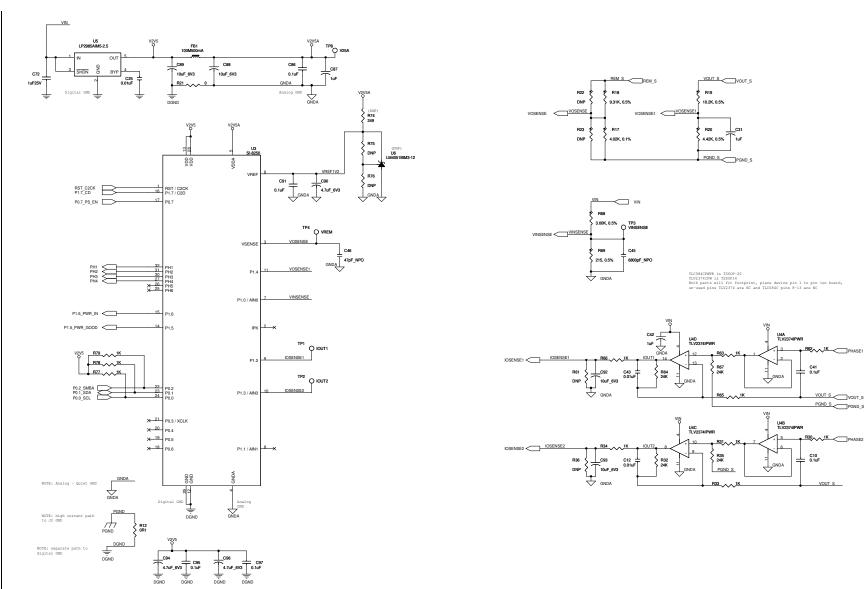

Figure 17. Si8250 Multi-Phase POL Target Board Schematic (Power)

12

**Schematics**

23

Rev. 0.2

Si825x

**Multi-Phase**

POL-RD

Figure 18. Si8250 Multi-Phase POL Target Board Schematic (Control)

24

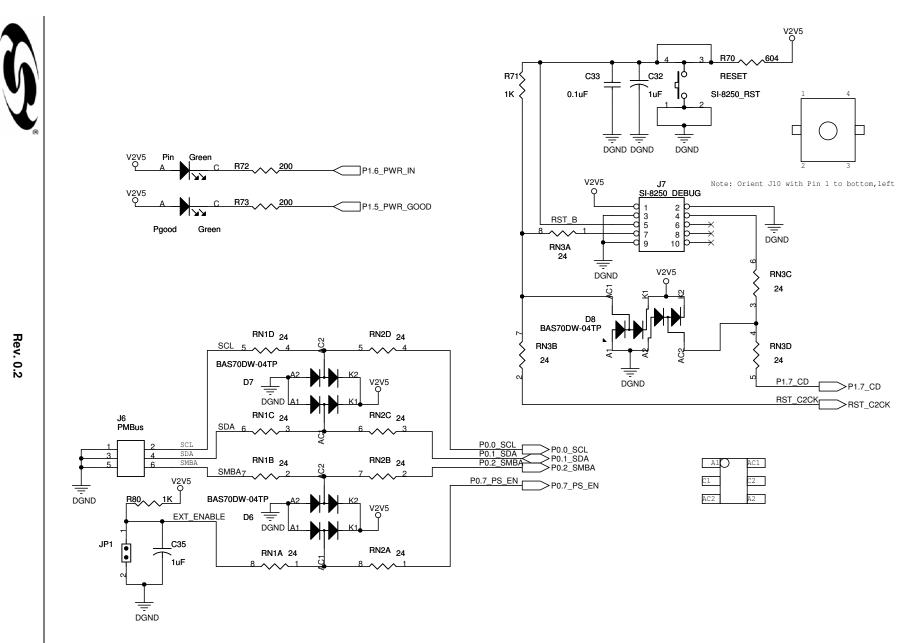

Figure 19. Si8250 Multi-Phase POL Target Board Schematic (Debug)

2

С

~

ABS