Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## N25Q128

# 128-Mbit 3 V, multiple I/O, 4-Kbyte subsector erase on boot sectors, XiP enabled, serial flash memory with 108 MHz SPI bus interface

#### **Features**

- SPI-compatible serial bus interface

- 108 MHz (maximum) clock frequency

- 2.7 V to 3.6 V single supply voltage

- Supports legacy SPI protocol and new Quad I/O or Dual I/O SPI protocol

- Quad/Dual I/O instructions resulting in an equivalent clock frequency up to 432 MHz:

- XIP mode for all three protocols

- Configurable via volatile or non-volatile registers: enables XiP mode directly after power on

- Program/Erase suspend instructions

- Continuous read (entire memory) via single instruction:

- Fast Read

- Quad or Dual Output Fast Read

- Quad or Dual I/O Fast Read

- Flexible to fit application:

- Configurable number of dummy cycles

- Output buffer configurable

- Fast POR instruction: decrease power-on time.

- Reset function (upon customer request)

- 64-byte user-lockable, one-time programmable (OTP) area

- Erase capability

- Subsector (4-Kbyte) granularity in the 8 boot sectors (bottom or top parts)

- Sector (64-Kbyte) granularity

- Write protections

- Software write protection applicable to every 64-Kbyte sector (volatile lock bit)

- Hardware write protection: protected area size defined by non-volatile bits (BP0, BP1, BP2, BP3 and TB bit)

- Additional smart protections available upon customer request

- Electronic signature

- JEDEC standard two-byte signature (BA18h)

- Additional 2 Extended Device ID (EDID) bytes to identify device factory options

- Unique ID code (UID) with 14 bytes readonly, available upon customer request

- More than 100,000 program/erase cycles per sector

- More than 20 years data retention

- Packages (all packages RoHS compliant)

- F8 = VDFPN8 8 x 6 mm (MLP8)

- 12 = TBGA24 6 x 8 mm

- F6 = VDFPN8 6 x 5 mm (MLP)

- SF = SO16 (300 mils body width)

- SE = SO8W (SO8 208 mils body width)

Contents N25Q128 - 3 V

## **Contents**

| 1 | Desc  | cription.  |                                                                    | 12 |

|---|-------|------------|--------------------------------------------------------------------|----|

| 2 | Sign  | al descr   | iptions                                                            | 16 |

|   | 2.1   | Serial d   | ata output (DQ1)                                                   | 16 |

|   | 2.2   | Serial d   | ata input (DQ0)                                                    | 16 |

|   | 2.3   | Serial C   | Clock (C)                                                          | 16 |

|   | 2.4   | Chip Se    | elect (S)                                                          | 16 |

|   | 2.5   | Hold (H    | OLD) or Reset (Reset)                                              | 17 |

|   | 2.6   | Write p    | rotect/enhanced program supply voltage ( $\overline{W}$ /VPP), DQ2 | 18 |

|   | 2.7   | •          | oply voltage                                                       |    |

|   | 2.8   |            | ound                                                               |    |

| 3 | SPI   | Modes .    |                                                                    | 19 |

| 4 | SPI F | Protocol   | s                                                                  | 21 |

|   | 4.1   | Extende    | ed SPI protocol                                                    | 21 |

|   | 4.2   |            | SPI (DIO-SPI) protocol                                             |    |

|   | 4.3   |            | PI (QIO-SPI) protocol                                              |    |

| 5 | Oper  | rating fea | atures                                                             | 23 |

|   | 5.1   | Extende    | ed SPI Protocol Operating features                                 | 23 |

|   |       | 5.1.1      | Read Operations                                                    |    |

|   |       | 5.1.2      | Page programming                                                   |    |

|   |       | 5.1.3      | Dual input fast program                                            | 23 |

|   |       | 5.1.4      | Dual Input Extended Fast Program                                   | 23 |

|   |       | 5.1.5      | Quad Input Fast Program                                            | 24 |

|   |       | 5.1.6      | Quad Input Extended Fast Program                                   | 24 |

|   |       | 5.1.7      | Subsector erase, sector erase and bulk erase                       | 24 |

|   |       | 5.1.8      | Polling during a write, program or erase cycle                     |    |

|   |       | 5.1.9      | Active power and standby power modes                               |    |

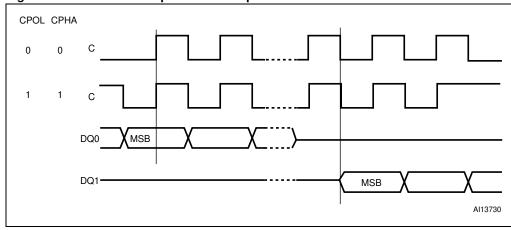

|   |       | 5.1.10     | Hold (or Reset) condition                                          |    |

|   | 5.2   |            | PI (DIO-SPI) Protocol                                              |    |

|   |       | 5.2.1      | Multiple Read Identification                                       | 27 |

|   |       |            |                                                                    |    |

N25Q128 - 3 V Contents

|   |        | 5.2.2                                                                            | Dual Command Fast reading                                                                                                                                                                                                                                                                                                                                                             | . 27                                                 |

|---|--------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   |        | 5.2.3                                                                            | Page programming                                                                                                                                                                                                                                                                                                                                                                      | . 27                                                 |

|   |        | 5.2.4                                                                            | Subsector Erase, Sector Erase and Bulk Erase                                                                                                                                                                                                                                                                                                                                          | . 28                                                 |

|   |        | 5.2.5                                                                            | Polling during a Write, Program or Erase cycle                                                                                                                                                                                                                                                                                                                                        | . 28                                                 |

|   |        | 5.2.6                                                                            | Read and Modify registers                                                                                                                                                                                                                                                                                                                                                             | . 28                                                 |

|   |        | 5.2.7                                                                            | Active Power and Standby Power modes                                                                                                                                                                                                                                                                                                                                                  | . 28                                                 |

|   |        | 5.2.8                                                                            | HOLD (or Reset) condition                                                                                                                                                                                                                                                                                                                                                             | . 28                                                 |

|   | 5.3    | Quad S                                                                           | PI (QIO-SPI)Protocol                                                                                                                                                                                                                                                                                                                                                                  | 29                                                   |

|   |        | 5.3.1                                                                            | Multiple Read Identification                                                                                                                                                                                                                                                                                                                                                          | . 29                                                 |

|   |        | 5.3.2                                                                            | Quad Command Fast reading                                                                                                                                                                                                                                                                                                                                                             | . 29                                                 |

|   |        | 5.3.3                                                                            | QUAD Command Page programming                                                                                                                                                                                                                                                                                                                                                         | . 29                                                 |

|   |        | 5.3.4                                                                            | Subsector Erase, Sector Erase and Bulk Erase                                                                                                                                                                                                                                                                                                                                          | . 30                                                 |

|   |        | 5.3.5                                                                            | Polling during a Write, Program or Erase cycle                                                                                                                                                                                                                                                                                                                                        | . 30                                                 |

|   |        | 5.3.6                                                                            | Read and Modify registers                                                                                                                                                                                                                                                                                                                                                             | . 31                                                 |

|   |        | 5.3.7                                                                            | Active Power and Standby Power modes                                                                                                                                                                                                                                                                                                                                                  | . 31                                                 |

|   |        | 5.3.8                                                                            | HOLD (or Reset) condition                                                                                                                                                                                                                                                                                                                                                             | . 31                                                 |

|   |        | 5.3.9                                                                            | VPP pin Enhanced Supply Voltage feature                                                                                                                                                                                                                                                                                                                                               | . 31                                                 |

| 6 | Volati | ile and I                                                                        | Non Volatile Registers                                                                                                                                                                                                                                                                                                                                                                | 32                                                   |

|   | 6.1    | Legacy                                                                           | SPI Status Register                                                                                                                                                                                                                                                                                                                                                                   | 34                                                   |

|   |        | 6.1.1                                                                            | WIP bit                                                                                                                                                                                                                                                                                                                                                                               | . 34                                                 |

|   |        | 6.1.2                                                                            | WEL bit                                                                                                                                                                                                                                                                                                                                                                               | . 34                                                 |

|   |        | 6.1.3                                                                            | BP3, BP2, BP1, BP0 bits                                                                                                                                                                                                                                                                                                                                                               | . 34                                                 |

|   |        | 6.1.4                                                                            | TB bit                                                                                                                                                                                                                                                                                                                                                                                | . 34                                                 |

|   |        | 6.1.5                                                                            | SRWD bit                                                                                                                                                                                                                                                                                                                                                                              | . 35                                                 |

|   | 6.2    | Non Vol                                                                          | atile Configuration Register                                                                                                                                                                                                                                                                                                                                                          | 36                                                   |

|   |        |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |

|   |        | 6.2.1                                                                            | Dummy clock cycles NV configuration bits (NVCR bits from 15 to 12)                                                                                                                                                                                                                                                                                                                    | . 37                                                 |

|   |        | 6.2.1<br>6.2.2                                                                   | Dummy clock cycles NV configuration bits (NVCR bits from 15 to 12) XIP NV configuration bits (NVCR bits from 11 to 9)                                                                                                                                                                                                                                                                 |                                                      |

|   |        |                                                                                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                 | . 38                                                 |

|   |        | 6.2.2                                                                            | XIP NV configuration bits (NVCR bits from 11 to 9)                                                                                                                                                                                                                                                                                                                                    | . 38<br>. 38                                         |

|   |        | 6.2.2<br>6.2.3                                                                   | XIP NV configuration bits (NVCR bits from 11 to 9) Output Driver Strength NV configuration bits (NVCR bits from 8 to 6) .                                                                                                                                                                                                                                                             | . 38<br>. 38<br>. 38                                 |

|   |        | 6.2.2<br>6.2.3<br>6.2.4                                                          | XIP NV configuration bits (NVCR bits from 11 to 9) Output Driver Strength NV configuration bits (NVCR bits from 8 to 6) . Fast POR NV configuration bit (NVCR bit 5)                                                                                                                                                                                                                  | . 38<br>. 38<br>. 38                                 |

|   |        | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                 | XIP NV configuration bits (NVCR bits from 11 to 9) Output Driver Strength NV configuration bits (NVCR bits from 8 to 6) . Fast POR NV configuration bit (NVCR bit 5)                                                                                                                                                                                                                  | . 38<br>. 38<br>. 38<br>. 39                         |

|   | 6.3    | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7                               | XIP NV configuration bits (NVCR bits from 11 to 9)                                                                                                                                                                                                                                                                                                                                    | . 38<br>. 38<br>. 38<br>. 39<br>. 39                 |

|   | 6.3    | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7                               | XIP NV configuration bits (NVCR bits from 11 to 9)                                                                                                                                                                                                                                                                                                                                    | . 38<br>. 38<br>. 38<br>. 39<br>. 39                 |

|   | 6.3    | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Volatile                   | XIP NV configuration bits (NVCR bits from 11 to 9)                                                                                                                                                                                                                                                                                                                                    | . 38<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40         |

|   | 6.3    | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>Volatile<br>6.3.1<br>6.3.2 | XIP NV configuration bits (NVCR bits from 11 to 9)  Output Driver Strength NV configuration bits (NVCR bits from 8 to 6).  Fast POR NV configuration bit (NVCR bit 5)  Hold (Reset) disable NV configuration bit (NVCR bit 4)  Quad Input NV configuration bit (NVCR bit 3)  Dual Input NV configuration bit (NVCR bit 2)  Configuration Register  Dummy clock cycle: VCR bits 7 to 4 | . 38<br>. 38<br>. 38<br>. 39<br>. 39<br>. 40<br>. 41 |

|     |       | 6.4.1                                                                                                                 | Quad Input Command VECR<7>                                                                                                                                                                                                                                                                                                                             | 43                                                                    |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|     |       | 6.4.2                                                                                                                 | Dual Input Command VECR<6>                                                                                                                                                                                                                                                                                                                             | 43                                                                    |

|     |       | 6.4.3                                                                                                                 | Reset/Hold disable VECR<4>                                                                                                                                                                                                                                                                                                                             | 44                                                                    |

|     |       | 6.4.4                                                                                                                 | Accelerator pin enable: QIO-SPI protocol / QIFP/QIEFP VECR<3> .                                                                                                                                                                                                                                                                                        | 44                                                                    |

|     |       | 6.4.5                                                                                                                 | Output Driver Strength VECR<2:0>                                                                                                                                                                                                                                                                                                                       | 44                                                                    |

|     | 6.5   | Flag St                                                                                                               | atus Register                                                                                                                                                                                                                                                                                                                                          | . 45                                                                  |

|     |       | 6.5.1                                                                                                                 | P/E Controller Status bit                                                                                                                                                                                                                                                                                                                              | 46                                                                    |

|     |       | 6.5.2                                                                                                                 | Erase Suspend Status bit                                                                                                                                                                                                                                                                                                                               | 46                                                                    |

|     |       | 6.5.3                                                                                                                 | Erase Status bit                                                                                                                                                                                                                                                                                                                                       | 46                                                                    |

|     |       | 6.5.4                                                                                                                 | Program Status bit                                                                                                                                                                                                                                                                                                                                     | 47                                                                    |

|     |       | 6.5.5                                                                                                                 | VPP Status bit                                                                                                                                                                                                                                                                                                                                         | 47                                                                    |

|     |       | 6.5.6                                                                                                                 | Program Suspend Status bit                                                                                                                                                                                                                                                                                                                             | 47                                                                    |

|     |       | 6.5.7                                                                                                                 | Protection Status bit                                                                                                                                                                                                                                                                                                                                  | 48                                                                    |

| 7   | Prot  | ection n                                                                                                              | nodes                                                                                                                                                                                                                                                                                                                                                  | . 49                                                                  |

|     | 7.1   | SPI Pr                                                                                                                | otocol-related protections                                                                                                                                                                                                                                                                                                                             | . 49                                                                  |

|     | 7.2   | Specifi                                                                                                               | c hardware and software protection                                                                                                                                                                                                                                                                                                                     | . 49                                                                  |

|     |       |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

| 8   | Mem   | ory org                                                                                                               | anization                                                                                                                                                                                                                                                                                                                                              | . 53                                                                  |

|     |       | , ,                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

|     | Instr | uctions                                                                                                               |                                                                                                                                                                                                                                                                                                                                                        | . 77                                                                  |

|     |       | uctions<br>Extend                                                                                                     | led SPI Instructions                                                                                                                                                                                                                                                                                                                                   | <b>. 77</b><br>. 77                                                   |

|     | Instr | Extend<br>9.1.1                                                                                                       | led SPI Instructions Read Identification (RDID)                                                                                                                                                                                                                                                                                                        | <b>. 77</b><br>. 77<br>80                                             |

|     | Instr | Extend<br>9.1.1<br>9.1.2                                                                                              | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ)                                                                                                                                                                                                                                                                                 | . <b>77</b> . 77 . 80                                                 |

|     | Instr | Extend<br>9.1.1                                                                                                       | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ)                                                                                                                                                                                                                                     | . <b>77</b> . 77 . 80 . 81                                            |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3                                                                                               | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR)                                                                                                                                                                                                        | . <b>77</b> . 77 . 80 . 81 . 82                                       |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4                                                                                      | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ)                                                                                                                                                                                                                                     | . <b>77</b> . 77 . 80 . 81 . 82 . 83                                  |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5                                                                             | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read                                                                                                                                                                                     | . 77<br>. 77<br>. 80<br>. 81<br>. 82<br>. 83<br>. 84                  |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6                                                                    | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read                                                                                                                                                               | . 77<br>. 77<br>. 80<br>. 81<br>. 82<br>. 83<br>. 84<br>. 85          |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7                                                           | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read                                                                                                                                            | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86                          |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8                                                  | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP)                                                                                                                            | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86 . 87                     |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8<br>9.1.9                                         | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP) Write Enable (WREN)                                                                                                        | . 77 80 81 82 83 84 85 86 87 88                                       |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8<br>9.1.9<br>9.1.10                               | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP) Write Enable (WREN)                                                                                                        | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86 . 87 . 88 . 90           |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8<br>9.1.9<br>9.1.10<br>9.1.11                     | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP) Write Enable (WREN) Write Disable (WRDI) Page Program (PP)                                                                 | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86 . 87 . 88 . 90           |

| 8 9 | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8<br>9.1.9<br>9.1.10<br>9.1.11<br>9.1.12           | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP) Write Enable (WREN) Write Disable (WRDI) Page Program (PP) Dual Input Fast Program (DIFP)                                  | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86 . 87 . 88 . 90 . 92 . 94 |

|     | Instr | 9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>9.1.6<br>9.1.7<br>9.1.8<br>9.1.9<br>9.1.10<br>9.1.11<br>9.1.12<br>9.1.13 | led SPI Instructions Read Identification (RDID) Read Data Bytes (READ) Read Data Bytes at Higher Speed (FAST_READ) Dual Output Fast Read (DOFR) Dual I/O Fast Read Quad Output Fast Read Quad I/O Fast Read Read OTP (ROTP) Write Enable (WREN) Write Disable (WRDI) Page Program (PP) Dual Input Fast Program (DIFP) Dual Input Extended Fast Program | . 77 . 77 . 80 . 81 . 82 . 83 . 84 . 85 . 86 . 87 . 90 . 92 . 94      |

|     | 9.1.16 | Program OTP instruction (POTP)                 | 96    |

|-----|--------|------------------------------------------------|-------|

|     | 9.1.17 | Subsector Erase (SSE)                          | 98    |

|     | 9.1.18 | Sector Erase (SE)                              | 99    |

|     | 9.1.19 | Bulk Erase (BE)                                | . 100 |

|     | 9.1.20 | Program/Erase Suspend                          | . 101 |

|     | 9.1.21 | Program/Erase Resume                           | . 102 |

|     | 9.1.22 | Read Status Register (RDSR)                    | . 103 |

|     | 9.1.23 | Write status register (WRSR)                   | . 103 |

|     | 9.1.24 | Read Lock Register (RDLR)                      | . 105 |

|     | 9.1.25 | Write to Lock Register (WRLR)                  | . 106 |

|     | 9.1.26 | Read Flag Status Register                      | . 107 |

|     | 9.1.27 | Clear Flag Status Register                     | . 107 |

|     | 9.1.28 | Read NV Configuration Register                 | . 108 |

|     | 9.1.29 | Write NV Configuration Register                | . 108 |

|     | 9.1.30 | Read Volatile Configuration Register           | . 109 |

|     | 9.1.31 | Write Volatile Configuration Register          | . 110 |

|     | 9.1.32 | Read Volatile Enhanced Configuration Register  | . 111 |

|     | 9.1.33 | Write Volatile Enhanced Configuration Register | . 111 |

| 9.2 | DIO-SP | I Instructions                                 | .112  |

|     | 9.2.1  | Multiple I/O Read Identification protocol      | . 114 |

|     | 9.2.2  | Dual Command Fast Read (DCFR)                  | . 115 |

|     | 9.2.3  | Read OTP (ROTP)                                | . 116 |

|     | 9.2.4  | Write Enable (WREN)                            | . 116 |

|     | 9.2.5  | Write Disable (WRDI)                           | . 117 |

|     | 9.2.6  | Dual Command Page Program (DCPP)               | . 117 |

|     | 9.2.7  | Program OTP instruction (POTP)                 | . 119 |

|     | 9.2.8  | Subsector Erase (SSE)                          | . 119 |

|     | 9.2.9  | Sector Erase (SE)                              | . 120 |

|     | 9.2.10 | Bulk Erase (BE)                                | . 121 |

|     | 9.2.11 | Program/Erase Suspend                          | . 121 |

|     | 9.2.12 | Program/Erase Resume                           | . 122 |

|     | 9.2.13 | Read Status Register (RDSR)                    | . 123 |

|     | 9.2.14 | Write status register (WRSR)                   | . 123 |

|     | 9.2.15 | Read Lock Register (RDLR)                      | . 124 |

|     | 9.2.16 | Write to Lock Register (WRLR)                  | . 124 |

|     | 9.2.17 | Read Flag Status Register                      | . 125 |

|     | 9.2.18 | Clear Flag Status Register                     | . 126 |

|     |        |                                                |       |

|       |       | 9.2.19    | Read NV Configuration Register                                 | 26 |

|-------|-------|-----------|----------------------------------------------------------------|----|

|       |       | 9.2.20    | Write NV Configuration Register                                | 27 |

|       |       | 9.2.21    | Read Volatile Configuration Register                           | 27 |

|       |       | 9.2.22    | Write Volatile Configuration Register                          | 28 |

|       |       | 9.2.23    | Read Volatile Enhanced Configuration Register                  | 29 |

|       |       | 9.2.24    | Write Volatile Enhanced Configuration Register                 | 29 |

|       | 9.3   | QIO-SI    | PI Instructions                                                | 30 |

|       |       | 9.3.1     | Multiple I/O Read Identification (MIORDID)                     | 32 |

|       |       | 9.3.2     | Quad Command Fast Read (QCFR)                                  | 33 |

|       |       | 9.3.3     | Read OTP (ROTP)13                                              | 35 |

|       |       | 9.3.4     | Write Enable (WREN)13                                          | 36 |

|       |       | 9.3.5     | Write Disable (WRDI)                                           | 37 |

|       |       | 9.3.6     | Quad Command Page Program (QCPP)                               | 37 |

|       |       | 9.3.7     | Program OTP instruction (POTP)                                 | 39 |

|       |       | 9.3.8     | Subsector Erase (SSE)                                          | 40 |

|       |       | 9.3.9     | Sector Erase (SE)                                              | 41 |

|       |       | 9.3.10    | Bulk Erase (BE)                                                | 42 |

|       |       | 9.3.11    | Program/Erase Suspend14                                        | 42 |

|       |       | 9.3.12    | Program/Erase Resume14                                         | 43 |

|       |       | 9.3.13    | Read Status Register (RDSR)14                                  | 44 |

|       |       | 9.3.14    | Write status register (WRSR)                                   | 45 |

|       |       | 9.3.15    | Read Lock Register (RDLR)14                                    | 46 |

|       |       | 9.3.16    | Write to Lock Register (WRLR)14                                | 47 |

|       |       | 9.3.17    | Read Flag Status Register                                      | 48 |

|       |       | 9.3.18    | Clear Flag Status Register                                     | 49 |

|       |       | 9.3.19    | Read NV Configuration Register                                 | 50 |

|       |       | 9.3.20    | Write NV Configuration Register15                              | 51 |

|       |       | 9.3.21    | Read Volatile Configuration Register                           | 52 |

|       |       | 9.3.22    | Write Volatile Configuration Register                          | 53 |

|       |       | 9.3.23    | Read Volatile Enhanced Configuration Register                  | 54 |

|       |       | 9.3.24    | Write Volatile Enhanced Configuration Register                 | 55 |

| 10    | XIP ( | Operation | ons                                                            | 57 |

|       | 10.1  | Enter >   | (IP mode by setting the Non Volatile Configuration Register 15 | 58 |

|       | 10.2  | Enter >   | KIP mode by setting the Volatile Configuration Register        | 30 |

|       | 10.3  |           | ode hold and exit                                              |    |

|       | 10.4  |           | emory reset after a controller reset                           |    |

| C/102 |       |           |                                                                |    |

N25Q128 - 3 V Contents

| 11 | Power-up and power-down163                                   |

|----|--------------------------------------------------------------|

|    | 11.1 Fast POR                                                |

|    | 11.2 Rescue sequence in case of power loss during WRNVCR 165 |

| 12 | Initial delivery state                                       |

| 13 | Maximum rating                                               |

| 14 | DC and AC parameters                                         |

| 15 | Package mechanical                                           |

| 16 | Ordering information180                                      |

| 17 | Revision history                                             |

List of tables N25Q128 - 3 V

## List of tables

| l able 1. | Signal names                                                                    |      |

|-----------|---------------------------------------------------------------------------------|------|

| Table 2.  | Status register format                                                          |      |

| Table 3.  | Non-Volatile Configuration Register                                             | . 36 |

| Table 4.  | Maximum allowed frequency (MHz)                                                 |      |

| Table 5.  | Volatile Configuration Register                                                 |      |

| Table 6.  | Volatile Enhanced Configuration Register                                        |      |

| Table 7.  | Flag Status Register                                                            |      |

| Table 8.  | Software protection truth table (Sectors 0 to 255, 64 Kbyte granularity)        | . 50 |

| Table 9.  | Protected area sizes, Upper (TB bit = 0)                                        | . 51 |

| Table 10. | Protected area sizes, Lower (TB bit = 1)                                        | . 52 |

| Table 11. | Memory organization (uniform)                                                   | . 54 |

| Table 12. | Memory organization (bottom)                                                    | . 61 |

| Table 13. | Memory organization (top)                                                       |      |

| Table 14. | Instruction set: extended SPI protocol                                          | . 79 |

| Table 15. | Read Identification data-out sequence                                           | . 81 |

| Table 16. | Extended Device ID table (first byte)                                           | . 81 |

| Table 17. | Suspend Parameters                                                              |      |

| Table 18. | Operations Allowed / Disallowed During Device States                            | 102  |

| Table 19. | Protection modes                                                                | 105  |

| Table 20. | Lock Register out                                                               | 106  |

| Table 21. | Lock Register in                                                                | 107  |

| Table 22. | Instruction set: DIO-SPI protocol                                               | 113  |

| Table 23. | Instruction set: QIO-SPI protocol                                               | 131  |

| Table 24. | NVCR XIP bits setting example                                                   | 159  |

| Table 25. | VCR XIP bits setting example                                                    | 160  |

| Table 26. | Power-up timing and VWI threshold                                               | 164  |

| Table 27. | Absolute maximum ratings                                                        | 166  |

| Table 28. | Operating conditions                                                            |      |

| Table 29. | AC measurement conditions                                                       | 167  |

| Table 30. | Capacitance                                                                     |      |

| Table 31. | DC Characteristics                                                              |      |

| Table 32. | AC Characteristics                                                              | 169  |

| Table 33. | Reset Conditions                                                                | 171  |

| Table 34. | VDFPN8 (MLP8) Very thin Dual Flat Package No lead,                              |      |

|           | 8 × 6 mm, package mechanical data                                               | 174  |

| Table 35. | VDFPN8 (MLP8) Very thin pitch Dual Flat Package No lead,                        |      |

|           | 6 × 5 mm, package mechanical data                                               |      |

| Table 36. | SO16 wide - 16-lead plastic small outline, 300 mils body width, mechanical data | 176  |

| Table 37. | SO8 wide – 8 lead plastic small outline, 208 mils body width,                   |      |

|           | package mechanical data                                                         |      |

| Table 38. | TBGA 6x8 mm 24-ball package dimensions                                          |      |

| Table 39. | Ordering information scheme                                                     |      |

| Table 40. | Valid Order Information Line Items                                              | 181  |

| Table 41. | Document revision history                                                       | 182  |

Numonyx

N25Q128 - 3 V List of figures

## List of figures

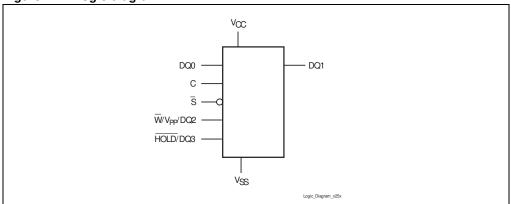

| Figure 1.  | Logic diagram                                                               | 13  |

|------------|-----------------------------------------------------------------------------|-----|

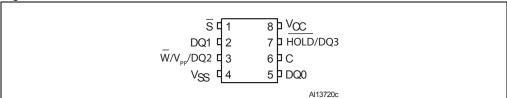

| Figure 2.  | VDFPN8 connections                                                          | 14  |

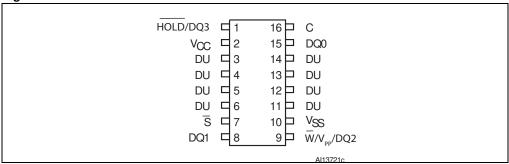

| Figure 3.  | SO16 connections                                                            | 14  |

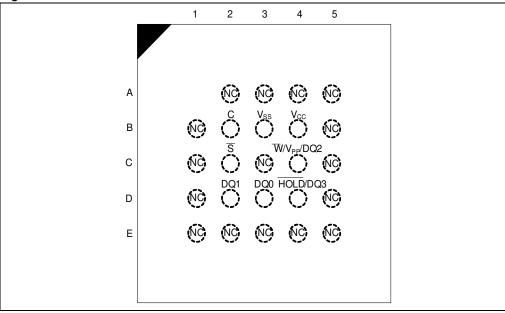

| Figure 4.  | BGA connections                                                             | 15  |

| Figure 5.  | Bus master and memory devices on the SPI bus                                | 19  |

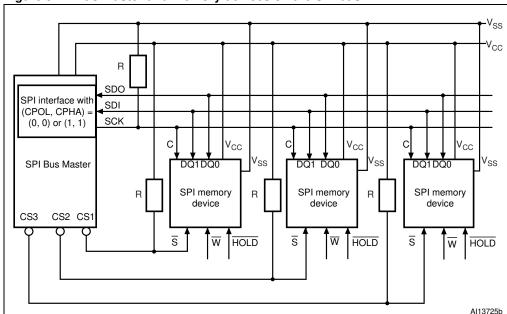

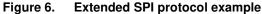

| Figure 6.  | Extended SPI protocol example                                               | 20  |

| Figure 7.  | Hold condition activation                                                   | 25  |

| Figure 8.  | Non Volatile and Volatile configuration Register Scheme                     | 33  |

| Figure 9.  | Block diagram                                                               |     |

| Figure 10. | Read identification instruction and data-out sequence                       | 81  |

| Figure 11. | Read Data Bytes instruction and data-out sequence                           | 82  |

| Figure 12. | Read Data Bytes at Higher Speed instruction and data-out sequence           | 83  |

| Figure 13. | Dual Output Fast Read instruction sequence                                  | 84  |

| Figure 14. | Dual I/O Fast Read instruction sequence                                     | 85  |

| Figure 15. | Quad Output Fast Read instruction sequence                                  | 86  |

| Figure 16. | Quad Input/ Output Fast Read instruction sequence                           |     |

| Figure 17. | Read OTP instruction and data-out sequence                                  |     |

| Figure 18. | Write Enable instruction sequence                                           |     |

| Figure 19. | Write Disable instruction sequence                                          |     |

| Figure 20. | Page Program instruction sequence                                           |     |

| Figure 21. | Dual Input Fast Program instruction sequence                                | 93  |

| Figure 22. | Dual Input Extended Fast Program instruction sequence                       |     |

| Figure 23. | Quad Input Fast Program instruction sequence                                |     |

| Figure 24. | Quad Input Extended Fast Program instruction sequence                       |     |

| Figure 25. | Program OTP instruction sequence                                            |     |

| Figure 26. | How to permanently lock the OTP bytes                                       |     |

| Figure 27. | Subsector Erase instruction sequence                                        |     |

| Figure 28. | Sector Erase instruction sequence                                           |     |

| Figure 29. | Bulk Erase instruction sequence                                             |     |

| Figure 30. | Read Status Register instruction sequence                                   |     |

| Figure 31. | Write Status Register instruction sequence                                  |     |

| Figure 32. | Read Lock Register instruction and data-out sequence                        |     |

| Figure 33. | Write to Lock Register instruction sequence                                 |     |

| Figure 34. | Read Flag Status Register instruction sequence                              |     |

| Figure 35. | Clear Flag Status Register instruction sequence                             |     |

| Figure 36. | Read NV Configuration Register instruction sequence                         |     |

| Figure 37. | Write NV Configuration Register instruction sequence                        |     |

| Figure 38. | Read Volatile Configuration Register instruction sequence                   |     |

| Figure 39. | Write Volatile Configuration Register instruction sequence                  |     |

| Figure 40. | Read Volatile Enhanced Configuration Register instruction sequence          |     |

| Figure 41. | Write Volatile Enhanced Configuration Register instruction sequence         |     |

| Figure 42. | Multiple I/O Read Identification instruction and data-out sequence DIO-SPI. |     |

| Figure 43. | Dual Command Fast Read instruction and data-out sequence DIO-SPI            |     |

| Figure 44. | Read OTP instruction and data-out sequence DIO-SPI                          |     |

| Figure 45. | Write Enable instruction sequence DIO-SPI.                                  |     |

| Figure 46. | Write Disable instruction sequence DIO-SPI                                  |     |

| Figure 47. | Dual Command Page Program instruction sequence DIO-SPI, 02h                 |     |

| Figure 48. | Dual Command Page Program instruction sequence DIO-SPI, A2h                 | 118 |

9/183

List of figures N25Q128 - 3 V

| Figure 49.  | Dual Command Page Program instruction sequence DIO-SPI, D2h                 |     |

|-------------|-----------------------------------------------------------------------------|-----|

| Figure 50.  | Program OTP instruction sequence DIO-SPI                                    |     |

| Figure 51.  | Subsector Erase instruction sequence DIO-SPI                                | 120 |

| Figure 52.  | Sector Erase instruction sequence DIO-SPI                                   |     |

| Figure 53.  | Bulk Erase instruction sequence DIO-SPI                                     |     |

| Figure 54.  | Program/Erase Suspend instruction sequence DIO-SPI                          |     |

| Figure 55.  | Program/Erase Resume instruction sequence DIO-SPI                           |     |

| Figure 56.  | Read Status Register instruction sequence DIO-SPI                           |     |

| Figure 57.  | Write Status Register instruction sequence DIO-SPI                          |     |

| Figure 58.  | Read Lock Register instruction and data-out sequence DIO-SPI                |     |

| Figure 59.  | Write to Lock Register instruction sequence DIO-SPI                         |     |

| Figure 60.  | Read Flag Status Register instruction sequence DIO-SPI                      |     |

| Figure 61.  | Clear Flag Status Register instruction sequence DIO-SPI                     |     |

| Figure 62.  | Read NV Configuration Register instruction sequence DIO-SPI                 | 126 |

| Figure 63.  | Write NV Configuration Register instruction sequence DIO-SPI                |     |

| Figure 64.  | Read Volatile Configuration Register instruction sequence DIO-SPI           |     |

| Figure 65.  | Write Volatile Configuration Register instruction sequence DIO-SPI          |     |

| Figure 66.  | Read Volatile Enhanced Configuration Register instruction sequence DIO-SPI  |     |

| Figure 67.  | Write Volatile Enhanced Configuration Register instruction sequence DIO-SPI |     |

| Figure 68.  | Multiple I/O Read Identification instruction and data-out sequence QIO-SPI  |     |

| Figure 69.  | Quad Command Fast Read instruction and data-out sequence QIO-SPI, 0Bh       |     |

| Figure 70.  | Quad Command Fast Read instruction and data-out sequence QIO-SPI, 6Bh       |     |

| Figure 71.  | Quad Command Fast Read instruction and data-out sequence QIO-SPI, EBh       |     |

| Figure 72.  | Read OTP instruction and data-out sequence QIO-SPI                          |     |

| Figure 73.  | Write Enable instruction sequence QIO-SPI                                   |     |

| Figure 74.  | Write Disable instruction sequence QIO-SPI                                  |     |

| Figure 75.  | Quad Command Page Program instruction sequence QIO-SPI, 02h                 |     |

| Figure 76.  | Quad Command Page Program instruction sequence QIO-SPI, 12h                 |     |

| Figure 77.  | Quad Command Page Program instruction sequence QIO-SPI, 32h                 |     |

| Figure 78.  | Program OTP instruction sequence QIO-SPI                                    |     |

| Figure 79.  | Subsector Erase instruction sequence QIO-SPI                                |     |

| Figure 80.  | Sector Erase instruction sequence QIO-SPI                                   | 141 |

| Figure 81.  | Bulk Erase instruction sequence QIO-SPI                                     |     |

| Figure 82.  | Program/Erase Suspend instruction sequence QIO-SPI                          |     |

| Figure 83.  | Program/Erase Resume instruction sequence QIO-SPI                           |     |

| Figure 84.  | Read Status Register instruction sequence QIO-SPI                           |     |

| Figure 85.  | Write Status Register instruction sequence QIO-SPI                          |     |

| Figure 86.  | Read Lock Register instruction and data-out sequence QIO-SPI                |     |

| Figure 87.  | Write to Lock Register instruction sequence QIO-SPI                         | 148 |

| Figure 88.  | Read Flag Status Register instruction sequence QIO-SPI                      |     |

| Figure 89.  | Clear Flag Status Register instruction sequence QIO-SPI                     |     |

| Figure 90.  | Read NV Configuration Register instruction sequence QIO-SPI                 |     |

| Figure 91.  | Write NV Configuration Register instruction sequence QIO-SPI                |     |

| Figure 92.  | Read Volatile Configuration Register instruction sequence QIO-SPI           |     |

| Figure 93.  | Write Volatile Configuration Register instruction sequence QIO-SPI          |     |

| Figure 94.  | Read Volatile Enhanced Configuration Register instruction sequence QIO-SPI  |     |

| Figure 95.  | Write Volatile Enhanced Configuration Register instruction sequence QIO-SPI |     |

| Figure 96.  | N25Q128 Read functionality Flow Chart                                       |     |

| Figure 97.  | XIP mode directly after power on                                            |     |

| Figure 98.  | XiP: enter by VCR 2/2 (QIOFR in normal SPI protocol example)                |     |

| Figure 99.  | Power-up timing, Fast POR selected                                          |     |

| Figure 100. | Power-up timing. Fast POR not selected                                      | 164 |

10/183 № numonyx

N25Q128 - 3 V List of figures

| Figure 101. | AC measurement I/O waveform                                                     | 167 |

|-------------|---------------------------------------------------------------------------------|-----|

| Figure 102. | Reset AC waveforms while a program or erase cycle is in progress                | 170 |

| Figure 103. | Serial input timing                                                             | 171 |

| Figure 104. | Write protect setup and hold timing during WRSR when SRWD=1                     | 172 |

| Figure 105. | Hold timing                                                                     | 172 |

| Figure 106. | Output timing                                                                   | 173 |

| Figure 107. | VPP <sub>H</sub> timing                                                         | 173 |

| Figure 108. | VDFPN8 (MLP8) Very thin Dual Flat Package No lead,                              |     |

|             | 8 × 6 mm, package outline                                                       | 174 |

| Figure 109. | VDFPN8 (MLP8) Very thin pitch Dual Flat Package No lead,                        |     |

|             | 6 × 5 mm, package outline                                                       | 175 |

| Figure 110. | SO16 wide - 16-lead plastic small outline, 300 mils body width, package outline | 176 |

| Figure 111. | SO8W – 8 lead plastic small outline, 208 mils body width, package outline       | 177 |

| Figure 112. | TBGA - 6 x 8 mm, 24-ball, mechanical package outline                            | 178 |

Description N25Q128 - 3 V

## 1 Description

The N25Q128 is a 128 Mbit (16Mb x 8) serial Flash memory, with advanced write protection mechanisms. It is accessed by a high speed SPI-compatible bus and features the possibility to work in XIP ("eXecution in Place") mode.

The N25Q128 supports innovative, high-performance quad/dual I/O instructions, these new instructions allow to double or quadruple the transfer bandwidth for read and program operations.

Furthermore the memory can be operated with 3 different protocols:

- Standard SPI (Extended SPI protocol)

- Dual I/O SPI

- Quad I/O SPI

The Standard SPI protocol is enriched by the new quad and dual instructions (Extended SPI protocol). For Dual I/O SPI (DIO-SPI) all the instructions codes, the addresses and the data are always transmitted across two data lines. For Quad I/O SPI (QIO-SPI) the instructions codes, the addresses and the data are always transmitted across four data lines thus enabling a tremendous improvement in both random access time and data throughput.

The memory can work in "XIP mode", that means the device only requires the addresses and not the instructions to output the data. This mode dramatically reduces random access time thus enabling many applications requiring fast code execution without shadowing the memory content on a RAM.

The XIP mode can be used with QIO-SPI, DIO-SPI, or Extended SPI protocol, and can be entered and exited using different dedicated instructions to allow maximum flexibility: for applications required to enter in XIP mode right after power up of the device, this can be set as default mode by using dedicated Non Volatile Register (NVR) bits.

It is also possible to reduce the power on sequence time with the Fast POR (Power on Reset) feature, enabling a reduction of the latency time before the first read instruction can be performed. Another feature is the ability to pause and resume program and erase cycles by using dedicated Program/Erase Suspend and Resume instructions.

The N25Q128 memory offers the following additional Features to be configured by using the Non Volatile Configuration Register (NVCR) for default /Non-Volatile settings or by using the Volatile and Volatile Enhanced Configuration Registers for Volatile settings:

- the number of dummy cycles for fast read instructions (single, dual and, quad I/O) according to the operating frequency

- the output buffer impedance

- the type of SPI protocol (extended SPI, DIO-SPI or QIO-SPI)

- the required XIP mode

- Fast or standard POR sequence

- the Hold (Reset) functionality enabling/disabling

The memory is organized as 248 (64-Kbyte) main sectors, in products with Bottom or Top architecture there are 8 64-Kbyte boot sectors, and each boot sector is further divided into 16 4-Kbyte subsectors (128 subsectors in total). The boot sectors can be erased a 4-Kbyte subsector at a time or as a 64-Kbyte sector at a time. The entire memory can be also erased at a time or by sector.

N25Q128 - 3 V Description

The memory can be write protected by software using a mix of volatile and non-volatile protection features, depending on the application needs. The protection granularity is of 64-Kbyte (sector granularity) for volatile protections.

The N25Q128 has 64 one-time-programmable bytes (OTP bytes) that can be read and programmed using two dedicated instructions, Read OTP (ROTP) and Program OTP (POTP), respectively. These 64 bytes can be permanently locked by a particular Program OTP (POTP) sequence. Once they have been locked, they become read-only and this state cannot be reversed.

Many different N25Q128 configurations are available, please refer to the ordering scheme page for the possibilities. Additional features are available as security options (The Security features are described in a dedicated Application Note). Please contact your nearest Numonyx Sales office for more information.

Note:

Reset functionality is available in devices with a dedicated part number. See Section 16: Ordering information.

Table 1. Signal names

| Signal                  | Description                                                               | I/O                |

|-------------------------|---------------------------------------------------------------------------|--------------------|

| С                       | Serial Clock                                                              | Input              |

| DQ0                     | Serial Data input                                                         | I/O <sup>(1)</sup> |

| DQ1                     | Serial Data output                                                        | I/O <sup>(2)</sup> |

| s                       | Chip Select                                                               | Input              |

| W/VPP/DQ2               | Write Protect/Enhanced Program supply voltage/additional data I/O         | I/O <sup>(3)</sup> |

| HOLD/DQ3 <sup>(4)</sup> | Hold (Reset function available upon customer request)/additional data I/O | I/O <sup>(3)</sup> |

| V <sub>CC</sub>         | Supply voltage                                                            | -                  |

| V <sub>SS</sub>         | Ground                                                                    | -                  |

- Provides dual and quad I/O for Extended SPI protocol instructions, dual I/O for Dual I/O SPI protocol instructions, and quad I/O for Quad I/O SPI protocol instructions.

- 2. Provides dual and quad instruction input for Extended SPI protocol, dual instruction input for Dual I/O SPI protocol, and quad instruction input for Quad I/O SPI protocol.

- 3. Provides quad I/O for Extended SPI protocol instructions, and quad I/O for Quad I/O SPI protocol instructions.

- 4. Reset functionality available with a dedicated part number. See Section 16: Ordering information.

Description N25Q128 - 3 V

Note:

There is an exposed central pad on the underside of the VDFPN8 package. This is pulled, internally, to VSS, and must not be connected to any other voltage or signal line on the PCB.

Figure 2. VDFPN8 connections

Reset functionality available in devices with a dedicated part number. See Section 16: Ordering information.

Figure 3. SO16 connections

- 1. DU = don't use.

- 2. See Package mechanical section for package dimensions, and how to identify pin-1.

- 3. Reset functionality available in devices with a dedicated part number. See Section 16: Ordering information.

N25Q128 - 3 V Description

Figure 4. BGA connections

- 1. NC = No Connect.

- 2. See Figure 112.: TBGA 6 x 8 mm, 24-ball, mechanical package outline.

Signal descriptions N25Q128 - 3 V

## 2 Signal descriptions

#### 2.1 Serial data output (DQ1)

This output signal is used to transfer data serially out of the device. Data are shifted out on the falling edge of Serial Clock (C). When used as an Input, It is latched on the rising edge of the Serial Clock (C).