Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **NAU8822**

## 24-bit Stereo Audio Codec with Speaker Driver

#### **Description**

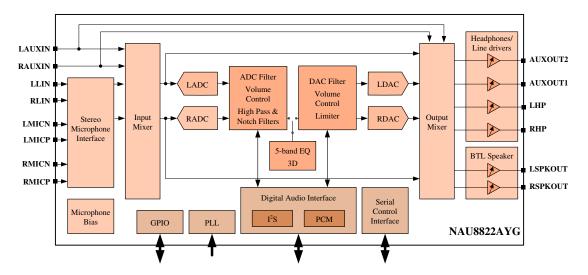

The NAU8822 is a low power, high quality CODEC for portable and general purpose audio applications. In addition to precision 24-bit stereo ADCs and DACs, this device integrates a broad range of additional functions to simplify implementation of complete audio system solutions. The NAU8822 includes drivers for speaker, headphone, and differential or stereo line outputs, and integrates preamps for stereo differential microphones, significantly reducing external component requirements. Also, a fractional PLL is available to accurately generate any audio sample rate for the CODEC using any commonly available system clock from 8MHz through 33MHz.

Advanced on-chip digital signal processing includes a 5-band equalizer, a 3-D audio enhancer, a mixed-signal automatic level control for the microphone or line input through the ADC, and a digital limiter/dynamic-range-compressor (DRC) function for the playback path. Additional digital filtering options are available in the ADC path, to simplify implementation of specific application requirements such as "wind noise reduction" and speech band enhancement. The digital audio input/output interface can operate as either a master or a slave.

The NAU8822 operates with analog supply voltages from 2.5V to 3.6V, while the digital core can operate at 1.7V to conserve power. The loudspeaker BTL output pair and two auxiliary line outputs can operate using a 5V supply to increase output power capability, enabling the NAU8822 to drive 1 Watt into an external speaker. Internal register controls enable flexible power saving modes by powering down sub-sections of the chip under software control.

The NAU8822 is specified for operation from -40°C to +85°C, and is available with full automotive AEC-/Q100 & TS16949 qualification. It is packaged in a cost-effective, space-saving 32-lead QFN package.

#### **Key Features**

- DAC: 94dB SNR and -84dB THD ("A" weighted)

- ADC: 90dB SNR and -80dB THD ("A" weighted)

- Integrated BTL speaker driver: 1W into 8Ω

- Integrated head-phone driver: 40mW into  $16\Omega$

- Integrated programmable microphone amplifier

- Integrated line input and line output

- On-chip PLL

- Integrated DSP with specific functions:

- 5-band equalizer

- 3-D audio enhancement

- Input automatic level control (ALC/AGC)/limiter

- Output dynamic-range-compressor/limiter

- Notch filter and high pass filter

- Standard audio interfaces: PCM and I<sup>2</sup>S

- Serial control interfaces with read/write capability

- Realtime readback of signal level and DSP status

- Supports any sample rate from 8kHz to 48kHz

#### **Applications**

- Personal Media Players

- Smartphones

- Personal Navigation Devices

- Portable Game Players

- Camcorders

- Digital Still Cameras

- Portable TVs

- Stereo Bluetooth Headsets

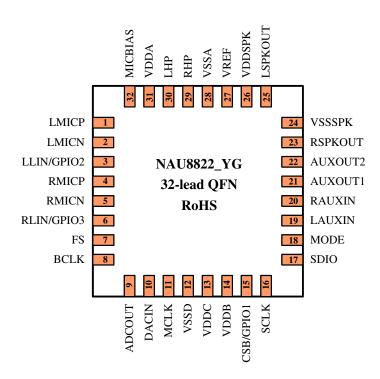

## **Pinout**

| Part Number | Dimension | Package | Package<br>Material |

|-------------|-----------|---------|---------------------|

| NAU8822_YG  | 5 x 5 mm  | 32-QFN  | Green               |

# **Pin Descriptions**

| Pin# | Name       | Туре           | Functionality                                                                         |  |

|------|------------|----------------|---------------------------------------------------------------------------------------|--|

| 1    | LMICP      | Analog Input   | Left MICP Input (common mode)                                                         |  |

| 2    | LMICN      | Analog Input   | Left MICN Input                                                                       |  |

| 3    | LLIN/GPIO2 | Analog Input / | Left Line Input / alternate Left MICP Input / GPIO2                                   |  |

|      |            | Digital I/O    |                                                                                       |  |

| 4    | RMICP      | Analog Input   | Right MICP Input (common mode)                                                        |  |

| 5    | RMICN      | Analog Input   | Right MICN Input                                                                      |  |

| 6    | RLIN/GPIO3 | Analog Input / | Right Line Input/ alternate Right MICP Input / Digital Output                         |  |

|      |            | Digital I/O    | In 4-wire mode: Must be used for GPIO3                                                |  |

| 7    | FS         | Digital I/O    | Digital Audio DAC and ADC Frame Sync                                                  |  |

| 8    | BCLK       | Digital I/O    | Digital Audio Bit Clock                                                               |  |

| 9    | ADCOUT     | Digital Output | Digital Audio ADC Data Output                                                         |  |

| 10   | DACIN      | Digital Input  | Digital Audio DAC Data Input                                                          |  |

| 11   | MCLK       | Digital Input  | Master Clock Input                                                                    |  |

| 12   | VSSD       | Supply         | Digital Ground                                                                        |  |

| 13   | VDDC       | Supply         | Digital Core Supply                                                                   |  |

| 14   | VDDB       | Supply         | Digital Buffer (Input/Output) Supply                                                  |  |

| 15   | CSB/GPIO1  | Digital I/O    | 3-Wire MPU Chip Select or GPIO1 multifunction input/output                            |  |

| 16   | SCLK       | Digital Input  | 3-Wire MPU Clock Input / 2-Wire MPU Clock Input                                       |  |

| 17   | SDIO       | Digital I/O    | 3-Wire MPU Data Input / 2-Wire MPU Data I/O                                           |  |

| 18   | MODE       | Digital Input  | Control Interface Mode Selection Pin                                                  |  |

| 19   | LAUXIN     | Analog Input   | Left Auxiliary Input                                                                  |  |

| 20   | RAUXIN     | Analog Input   | Right Auxiliary Input                                                                 |  |

| 21   | AUXOUT1    | Analog Output  | Headphone Ground / Mono Mixed Output / Line Output                                    |  |

| 22   | AUXOUT2    | Analog Output  | Headphone Ground / Line Output                                                        |  |

| 23   | RSPKOUT    | Analog Output  | BTL Speaker Positive Output or Right high current output                              |  |

| 24   | VSSSPK     | Supply         | Speaker Ground (ground pin for RSPKOUT, LSPKOUT, AUXOUT2 and AUXTOUT1 output drivers) |  |

| 25   | LSPKOUT    | Analog Output  | BTL Speaker Negative Output or Left high current output                               |  |

| 26   | VDDSPK     | Supply         | Speaker Supply (power supply pin for RSPKOUT, LSPKOUT,                                |  |

|      |            | 11 7           | AUXOUT2 and AUXTOUT1 output drivers)                                                  |  |

| 27   | VREF       | Reference      | Decoupling for Midrail Reference Voltage                                              |  |

| 28   | VSSA       | Supply         | Analog Ground                                                                         |  |

| 29   | RHP        | Analog Output  | Headphone Positive Output / Line Output Right                                         |  |

| 30   | LHP        | Analog Output  | Headphone Negative Output / Line Output Left                                          |  |

| 31   | VDDA       | Supply         | Analog Power Supply                                                                   |  |

| 32   | MICBIAS    | Analog Output  | Microphone Bias                                                                       |  |

## **Electrical Characteristics**

Conditions: VDDC = 1.8V, VDDA = VDDB = VDDSPK = 3.3V (VDDSPK = 1.5\*VDDA when Boost), MCLK = 12.88MHz,  $T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, 24-bit audio data, 64X oversampling rate, unless otherwise stated.

| Parameter                              | Symbol             | Comments/Conditions                   | Min | Тур          | Max   | Units            |

|----------------------------------------|--------------------|---------------------------------------|-----|--------------|-------|------------------|

| Analog to Digital Converter (ADC)      |                    |                                       |     |              |       |                  |

| Full scale input signal <sup>1</sup>   | $V_{INFS}$         | PGABST = 0dB                          |     | 1.0          |       | Vrms             |

|                                        |                    | PGAGAIN = 0dB                         |     | 0            |       | dBV              |

| Signal-to-noise ratio                  | SNR                | Gain = 0dB, A-weighted                | tbd | 90           |       | dB               |

| Total harmonic distortion <sup>2</sup> | THD+N              | Input = -3dB FS input                 |     | -80          | tbd   | dB               |

| Channel separation                     |                    | 1kHz input signal                     |     | 103          |       | dB               |

| Digital to Analog Converter (DAC)      | driving RHF        | / LHP with 10kΩ / 50pF load           |     | •            |       |                  |

| Full-scale output                      |                    | Gain paths all at 0dB gain            |     | VDDA / 3.3   | 3     | $V_{rms}$        |

| Signal-to-noise ratio                  | SNR                | A-weighted                            | 88  | 94           |       | dB               |

| Total harmonic distortion <sup>2</sup> | THD+N              | $R_L = 10k\Omega$ ; full-scale signal |     | -84          | tbd   | dB               |

| Channel separation                     |                    | 1kHz input signal                     |     | 96           |       | dB               |

| Output Mixers                          |                    |                                       |     |              |       |                  |

| Maximum PGA gain into mixer            |                    |                                       |     | +6           |       | dB               |

| Minimum PGA gain into mixer            |                    |                                       |     | -15          |       | dB               |

| PGA gain step into mixer               |                    | Guaranteed monotonic                  |     | 3            |       | dB               |

| Speaker Output (RSPKOUT / LSPI         | <b>COUT</b> with 8 | Ω bridge-tied-load)                   |     | •            |       |                  |

| Full scale output 4                    |                    | SPKBST = 0                            |     | VDDA / 3.3   | 3     | $V_{rms}$        |

|                                        |                    | VDDSPK=VDDA                           |     |              |       |                  |

|                                        |                    | SPKBST = 1                            | (V  | DDA / 3.3) ; | * 1.5 | V <sub>rms</sub> |

|                                        |                    | VDDSPK=1.5*VDDA                       |     |              |       |                  |

| Total harmonic distortion <sup>2</sup> | THD+N              | $P_o = 200 \text{mW}$                 |     | -63          |       | dB               |

|                                        |                    | VDDSPK=3.3V                           |     |              |       |                  |

|                                        |                    | $P_o = 320 \text{mW}$                 |     | -64          |       | dB               |

|                                        |                    | VDDSPK = 3.3V                         |     |              |       |                  |

|                                        |                    | $P_0 = 860 \text{mW},$                |     | -60          |       | dB               |

|                                        |                    | VDDSPK = 1.5*VDDA                     |     |              |       |                  |

|                                        |                    | $P_{o} = 1000 \text{mW},$             |     | -36          |       | dB               |

|                                        |                    | VDDSPK = 1.5*VDDA                     |     |              |       |                  |

| Signal-to-noise ratio                  | SNR                | VDDSPK = 3.3V                         |     | 91           |       | dB               |

|                                        |                    |                                       |     |              |       |                  |

|                                        |                    | VDDSPK = 1.5*VDDA                     |     | 90           |       | dB               |

| 7                                      | Dann               | LIDDGDI. 2 211                        |     | 0.1          |       | 15               |

| Power supply rejection ratio           | PSRR               | VDDSPK = 3.3V                         |     | 81           |       | dB               |

| (50Hz - 22kHz)                         |                    | VDDSPK = 1.5*VDDA                     |     | 72           |       | dB               |

|                                        |                    | VDDSFK = 1.5 VDDA                     |     | 12           |       | uБ               |

| Analog Outputs (RHP / LHP; RSPI        | KOUT / LSPF        | KOUT)                                 |     |              |       |                  |

| Maximum programmable gain              |                    |                                       | _   | +6           |       | dB               |

| Minimum programmable gain              |                    |                                       |     | -57          |       | dB               |

| Programmable gain step size            |                    | Guaranteed monotonic                  |     | 1            |       | dB               |

| Mute attenuation                       |                    | 1kHz full scale signal                |     | 85           |       | dB               |

## Electrical Characteristics, cont'd.

Conditions: VDDC = 1.8V, VDDA = VDDB = VDDSPK = 3.3V (VDDSPK = 1.5\*VDDA when Boost), MCLK = 12.288MHz,  $T_A = +25$ °C, 1kHz signal, fs = 48kHz, 24-bit audio data, unless otherwise stated.

| Parameter                                                   | Symbol              | Comments/Conditions                                 | Min       | Тур          | Max          | Units                  |

|-------------------------------------------------------------|---------------------|-----------------------------------------------------|-----------|--------------|--------------|------------------------|

| Headphone Output (RHP / LHP wi                              | th $32\Omega$ load) |                                                     |           |              |              |                        |

| 0dB full scale output voltage                               |                     |                                                     |           | VDDA / 3.3   | 3            | $V_{rms}$              |

| Signal-to-noise ratio                                       | SNR                 | A-weighted                                          |           | 92           |              | dB                     |

| Total harmonic distortion <sup>2</sup>                      | THD+N               | $R_L = 16\Omega$ , $P_o = 20$ mW,<br>VDDA = 3.3V    |           | -80          |              | dB                     |

|                                                             |                     | $R_L = 32\Omega$ , $P_o = 20$ mW,<br>VDDA = 3.3V    |           | -85          |              | dB                     |

| AUXOUT1 / AUXOUT2 with 10kΩ                                 | / 50pF load         |                                                     |           | •            | •            | •                      |

| Full scale output                                           |                     | AUX1BST = 0<br>AUX2BST = 0<br>VDDSPK=VDDA           |           | VDDA / 3.3   |              | V <sub>rms</sub>       |

|                                                             |                     | AUX1BST = 1<br>AUX2BST = 1<br>VDDSPK=1.5*VDDA       | (VI       | DDA / 3.3) * | ` 1.5        | V <sub>rms</sub>       |

| Signal-to-noise ratio                                       | SNR                 |                                                     |           | 87           |              | dB                     |

| Total harmonic distortion <sup>2</sup>                      | THD+N               |                                                     |           | -83          |              | dB                     |

| Channel separation                                          |                     | 1kHz signal                                         |           | 99           |              | dB                     |

| Power supply rejection ratio (50Hz - 22kHz)                 | PSRR                | VDDSPK = 1.5*VDDA                                   |           | 53<br>56     |              | dB<br>dB               |

|                                                             |                     |                                                     |           |              |              | -                      |

| Microphone Inputs (LMICP, LMIC                              | CN, RMICP, I        | RMICN, LLIN, RLIN) and Pr                           | ogrammabl | e Gain Amj   | olifier (PGA | 1)                     |

| Full scale input signal <sup>1</sup>                        |                     | PGABST = 0dB<br>PGAGAIN = 0dB                       |           | 1.0          |              | Vrms<br>dBV            |

| Programmable gain                                           |                     |                                                     | -12       | 1            | 35.25        | dB                     |

| Programmable gain step size                                 |                     | Guaranteed Monotonic                                |           | 0.75         |              | dB                     |

| Mute Attenuation                                            |                     |                                                     |           | 120          |              | dB                     |

| Input resistance                                            |                     | Inverting Input                                     |           |              |              |                        |

| 1                                                           |                     | PGA Gain = 35.25dB<br>PGA Gain = 0dB                |           | 1.6<br>47    |              | $k\Omega$<br>$k\Omega$ |

|                                                             |                     | PGA Gain = -12dB Non-inverting Input                |           | 75<br>94     |              | kΩ<br>kΩ               |

| Input capacitance                                           |                     | Tion myering input                                  |           | 10           |              | pF                     |

| PGA equivalent input noise                                  |                     | 0 to 20kHz, Gain set to 35.25dB                     |           | 120          |              | μV                     |

| Input Boost Mixer                                           |                     |                                                     |           |              |              |                        |

| Gain boost                                                  |                     | Boost disabled<br>Boost enabled                     |           | 0<br>20      |              | dB<br>dB               |

| Gain range LLIN / RLIN or<br>LAUXIN / RAUXIN to boost/mixer |                     |                                                     | -12       | -            | 6            | dB                     |

| Gain step size to boost/mixer                               |                     |                                                     |           | 3            |              | dB                     |

| Auxiliary Analog Inputs (LAUXIN,                            | RAUXIN)             |                                                     |           |              |              |                        |

| Full scale input signal <sup>1</sup>                        |                     | Gain = 0dB                                          |           | 1.0<br>0     |              | Vrms<br>dBV            |

| Input resistance                                            |                     | Aux direct-to-out path, only<br>Input gain = +6.0dB |           | 20           |              | kΩ                     |

|                                                             |                     | Input gain = 0.0dB<br>Input gain = -12dB            |           | 40<br>159    |              | kΩ<br>kΩ               |

| Input capacitance                                           |                     |                                                     |           | 10           |              | pF                     |

|                                                             | •                   | •                                                   | -         |              |              |                        |

### Electrical Characteristics, cont'd.

Conditions: VDDC = 1.8V, VDDA = VDDB = VDDSPK = 3.3V (VDDSPK = 1.5\*VDDA when Boost), MCLK = 12.288MHz,  $T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, 24-bit audio data, unless otherwise stated.

| Parameter                            | Symbol               | Comments/Conditions                          | Min           | Тур                           | Max           | Units        |

|--------------------------------------|----------------------|----------------------------------------------|---------------|-------------------------------|---------------|--------------|

| Automatic Level Control (ALC) &      | Limiter: ADO         | path only                                    |               |                               |               |              |

| Target record level                  |                      |                                              | -22.5         |                               | -1.5          | dBFS         |

| Programmable gain                    |                      |                                              | -12           |                               | 35.25         | dB           |

| Gain hold time <sup>3</sup>          | t <sub>HOLD</sub>    | Doubles every gain step, with 16 steps total | 0 / 2.67      | 7 / 5.33 /                    | / 43691       | ms           |

| Gain ramp-up (decay) <sup>3</sup>    | t <sub>DCY</sub>     | ALC Mode<br>ALC = 0                          |               | 3 / 16 / / 4                  |               | ms           |

|                                      |                      | Limiter Mode<br>ALC = 1                      |               | 2 / 4 / / 1                   |               | ms           |

| Gain ramp-down (attack) <sup>3</sup> | $t_{ATK}$            | ALC Mode<br>ALC = 0                          | 1 /           | 2 / 4 / / 1                   | 024           | ms           |

|                                      |                      | Limiter Mode<br>ALC = 1                      | 0.25          | / 0.5 / 1 /                   | / 128         | ms           |

| Mute Attenuation                     |                      |                                              |               | 120                           |               | dB           |

| Microphone Bias                      |                      |                                              |               |                               |               |              |

| Bias voltage                         | V <sub>MICBIAS</sub> | See Figure 3                                 |               | , 0.60,0.65,<br>5, 0.85, or 0 | ,             | VDDA<br>VDDA |

| Bias current source                  | I <sub>MICBIAS</sub> |                                              |               | 3                             |               | mA           |

| Output noise voltage                 | V <sub>n</sub>       | 1kHz to 20kHz                                |               | 14                            |               | nV/√Hz       |

| Digital Input/Output                 | •                    |                                              |               | •                             | •             |              |

| Input HIGH level                     | V <sub>IL</sub>      |                                              | 0.7 *<br>VDDB |                               |               | V            |

| Input LOW level                      | $V_{IH}$             |                                              |               |                               | 0.3 *<br>VDDB | V            |

| Output HIGH level                    | $V_{OH}$             | $I_{Load} = 1 \text{mA}$                     | 0.9 *<br>VDDB |                               |               | V            |

| Output LOW level                     | $V_{OL}$             | $I_{Load} = -1  \text{mA}$                   |               |                               | 0.1 *<br>VDDB | V            |

| Input capacitance                    |                      |                                              |               | 10                            |               | pF           |

#### Notes

- 1. Full Scale is relative to the magnitude of VDDA and can be calculated as FS = VDDA/3.3.

- 2. Distortion is measured in the standard way as the combined quantity of distortion products plus noise. The signal level for distortion measurements is at 3dB below full scale, unless otherwise noted.

- 3. Time values scale proportionally with MCLK. Complete descriptions and definitions for these values are contained in the detailed descriptions of the ALC functionality.

- 4. When SPKBST, AUX1BST & AUX2BST in R49 set, VDDSPK should be 1.5xVDDA (but not exceeding maximum recommended operating voltage) to optimize available dynamic range in the AUXOUT1 and AUXOUT2 line output stages. Output DC bias level is optimized for VDDSPK = 5.0Vdc (boost mode) and VDDA = 3.3Vdc.

- 5. Unused analog input pins should be left as no-connection.

- 6. Unused digital input pins should be tied to ground.

## **Absolute Maximum Ratings**

| Condition                                                  | Min        | Max         | Units |

|------------------------------------------------------------|------------|-------------|-------|

| VDDB, VDDC, VDDA supply voltages                           | -0.3       | +3.61       | V     |

| VDDSPK supply voltage (default register configuration)     | -0.3       | +5.80       | V     |

| VDDSPK supply voltage (optional low voltage configuration) | -0.3       | +3.61       | V     |

| Core Digital Input Voltage range                           | VSSD – 0.3 | VDDC + 0.30 | V     |

| Buffer Digital Input Voltage range                         | VSSD – 0.3 | VDDB + 0.30 | V     |

| Analog Input Voltage range                                 | VSSA – 0.3 | VDDA + 0.30 | V     |

| Industrial operating temperature                           | -40        | +85         | °C    |

| Storage temperature range                                  | -65        | +150        | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely influence product reliability and result in failures not covered by warranty.

## **Operating Conditions**

| Condition                     | Symbol                 | Min  | Typical | Max  | Units |

|-------------------------------|------------------------|------|---------|------|-------|

| Digital supply range (Core)   | VDDC                   | 1.65 |         | 3.60 | V     |

| Digital supply range (Buffer) | VDDB                   | 1.65 |         | 3.60 | V     |

| Analog supply range           | VDDA                   | 2.50 |         | 3.60 | V     |

| Speaker supply (SPKBST=0)     | VDDSPK                 | 2.50 |         | 5.50 | V     |

| Speaker supply (SPKBST=1)     | VDDSPK                 | 2.50 |         | 5.50 | V     |

| Ground                        | VSSD<br>VSSA<br>VSSSPK |      | 0       |      | V     |

1. VDDA must be  $\geq$  VDDB.

2. VDDB must be  $\geq$  VDDC.

# **Table of Contents**

| 1 | GE         | NERAL DESCRIPTION                                                                                                                | 12 |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1.1      | Analog Inputs                                                                                                                    | 12 |

|   | 1.1.2      | 2 Analog Outputs                                                                                                                 | 12 |

|   | 1.1.3      | ADC, DAC, and Digital Signal Processing                                                                                          | 13 |

|   | 1.1.4      | Realtime Signal Level Readout and DSP Status                                                                                     | 13 |

|   | 1.1.5      | Digital Interfaces                                                                                                               | 13 |

|   | 1.1.6      | 6 Clock Requirements                                                                                                             | 13 |

| 2 | POV        | WER SUPPLY                                                                                                                       | 15 |

|   | 2.1.1      |                                                                                                                                  |    |

|   | 2.1.2      | Power Related Software Considerations                                                                                            | 16 |

|   | 2.1.3      | S Software Reset                                                                                                                 | 16 |

| 3 | INP        | PUT PATH DETAILED DESCRIPTIONS                                                                                                   |    |

|   | 3.1        | Programmable Gain Amplifier (PGA)                                                                                                |    |

|   | 3.1.1      |                                                                                                                                  |    |

|   | 3.2        | Positive Microphone Input (MICP)                                                                                                 | 18 |

|   | 3.3        | Negative Microphone Input (MICN)                                                                                                 | 19 |

|   | 3.4        | Microphone biasing                                                                                                               |    |

|   | 3.5        | Line/Aux Input Impedance and Variable Gain Stage Topology  Left and Right Line Inputs (LLIN and RLIN)                            |    |

|   | 3.6<br>3.7 | Auxiliary inputs (LAUXIN, RAUXIN)                                                                                                |    |

|   | 3.8        | ADC Mix/Boost Stage                                                                                                              |    |

|   | 3.9        | Input Limiter / Automatic Level Control (ALC)                                                                                    |    |

|   | 3.9.1      | Normal Mode Example Operation                                                                                                    | 23 |

|   | 3.9.2      | 2 ALC Parameter Definitions                                                                                                      | 24 |

|   | 3.10       | ALC Peak Limiter Function                                                                                                        | 24 |

|   | 3.10       | .1 ALC Normal Mode Example Using ALC Hold Time Feature                                                                           | 25 |

|   | 3.11       | Noise Gate (Normal Mode Only)                                                                                                    |    |

|   | 3.12       | ALC Example with ALC Min/Max Limits and Noise Gate Operation                                                                     |    |

|   | 3.12       |                                                                                                                                  |    |

|   | 3.13       | Limiter Mode                                                                                                                     |    |

| 4 | 4.1        | Sampling / Oversampling Rate, Polarity Control, Digital Passthrough                                                              |    |

|   | 4.2        | ADC Digital Volume Control and Update Bit Functionality                                                                          |    |

|   | 4.3        | ADC Programmable High Pass Filter                                                                                                |    |

|   | 4.4        | Programmable Notch Filter                                                                                                        | 30 |

| 5 | DA         | C DIGITAL BLOCK                                                                                                                  | 32 |

|   | 5.1        | DAC Soft Mute                                                                                                                    |    |

|   | 5.2        | DAC AutoMute                                                                                                                     |    |

|   | 5.3<br>5.4 | DAC Sampling / Oversampling Rate, Polarity Control, Digital Passthrough  DAC Digital Volume Control and Update Bit Functionality |    |

|   | 5.5        | DAC Automatic Output Peak Limiter / Volume Boost                                                                                 |    |

|   | 5.6        | 5-Band Equalizer                                                                                                                 |    |

|   | 5.7        | 3D Stereo Enhancement                                                                                                            | 35 |

|   | 5.8        | Companding                                                                                                                       | 35 |

| 5.   | .9    | μ-law                                                                       | 35 |

|------|-------|-----------------------------------------------------------------------------|----|

| 5.   | .10   | A-law                                                                       | 35 |

| 5.   | .11   | 8-bit Word Length                                                           | 36 |

| 6    | AN    | ALOG OUTPUTS                                                                | 37 |

| 6.   | .1    | Main Mixers (LMAIN MIX and RMAIN MIX)                                       | 37 |

| 6.   | 2     | Auxiliary Mixers (AUX1 MIXER and AUX2 MIXER)                                | 37 |

| 6.   | .3    | Right Speaker Submixer                                                      | 38 |

| 6.   | 4     | Headphone Outputs (LHP and RHP)                                             | 38 |

| 6.   | .5    | Speaker Outputs                                                             | 39 |

| 6.   | 6     | Auxiliary Outputs                                                           | 40 |

| 7    | MIS   | SCELLANEOUS FUNCTIONS                                                       | 40 |

| 7.   | .1    | Slow Timer Clock                                                            | 40 |

| 7.   | 2     | General Purpose Inputs and Outputs (GPIO1, GPIO2, GPIO3) and Jack Detection | 40 |

| 7.   | .3    | Automated Features Linked to Jack Detection                                 | 41 |

| 8    | CLO   | OCK SELECTION AND GENERATION                                                | 42 |

| 8.   |       | Phase Locked Loop (PLL) General Description                                 |    |

|      | 8.1.1 |                                                                             |    |

| 8.   | 2     | CSB/GPIO1 as PLL output                                                     | 44 |

| 9    |       | NTROL INTERFACES                                                            |    |

| ´ 9. |       | Selection of Control Mode                                                   |    |

| 9.   |       | 2-Wire-Serial Control Mode (I <sup>2</sup> C Style Interface)               |    |

| 9.   |       | 2-Wire Protocol Convention                                                  |    |

| 9.   | _     | 2-Wire Write Operation                                                      |    |

| 9.   |       | 2-Wire Read Operation                                                       |    |

| 9.   |       | SPI Control Interface Modes                                                 |    |

| 9.   | -     | SPI 3-Wire Write Operation                                                  |    |

| 9.   |       | SPI 4-Wire 24-bit Write and 32-bit Read Operation                           |    |

| 9.   | _     | SPI 4-Wire Write Operation                                                  |    |

| 9.   | 10    | SPI 4-Wire Read Operation                                                   |    |

| 9.   | .11   | Software Reset                                                              |    |

| 10   | DIC   | SITAL AUDIO INTERFACES                                                      |    |

| 10   | 0.1   | Right-Justified Audio Data                                                  |    |

| 10   | 0.2   | Left-Justified Audio Data                                                   |    |

| 10   | 0.3   | I <sup>2</sup> S Audio Data                                                 |    |

| 1(   | 0.4   | PCM A Audio Data                                                            |    |

| 10   | 0.5   | PCM B Audio Data                                                            |    |

| 10   | 0.6   | PCM Time Slot Audio Data                                                    |    |

| 10   | 0.7   | Control Interface Timing                                                    |    |

| 10   | 0.8   | Audio Interface Timing:                                                     | 56 |

| 11   | APF   | PLICATION INFORMATION                                                       | 57 |

| 1    | 1.1   | Typical Application Schematic                                               | 57 |

| 1    | 1.2   | Recommended power up and power down sequences                               |    |

|      | 11.2  |                                                                             |    |

|      | 11.2  |                                                                             |    |

|      | 11.2  |                                                                             |    |

|      |       | ·                                                                           |    |

|      | 1.3   | Power Consumption                                                           |    |

|      | 1.4   | Supply Currents of Specific Blocks                                          |    |

| 12   | API   | PENDIX A: DIGITAL FILTER CHARACTERISTICS                                    | 64 |

| 13 | AP   | PENDIX B:   | : COMPANDING TABLES               | 69 |

|----|------|-------------|-----------------------------------|----|

|    | 13.1 | μ-Law / A-l | Law Codes for Zero and Full Scale | 69 |

|    | 13.2 | μ-Law / A-l | Law Output Codes (Digital mW)     | 69 |

| 14 | AP   | PENDIX C:   | : DETAILS OF REGISTER OPERATION   | 70 |

| 15 | AP   | PENDIX D    | : REGISTER OVERVIEW               | 87 |

| 16 | PA   | CKAGE DI    | MENSIONS                          | 89 |

| 17 | OF   | DERING IN   | NFORMATION                        | 90 |

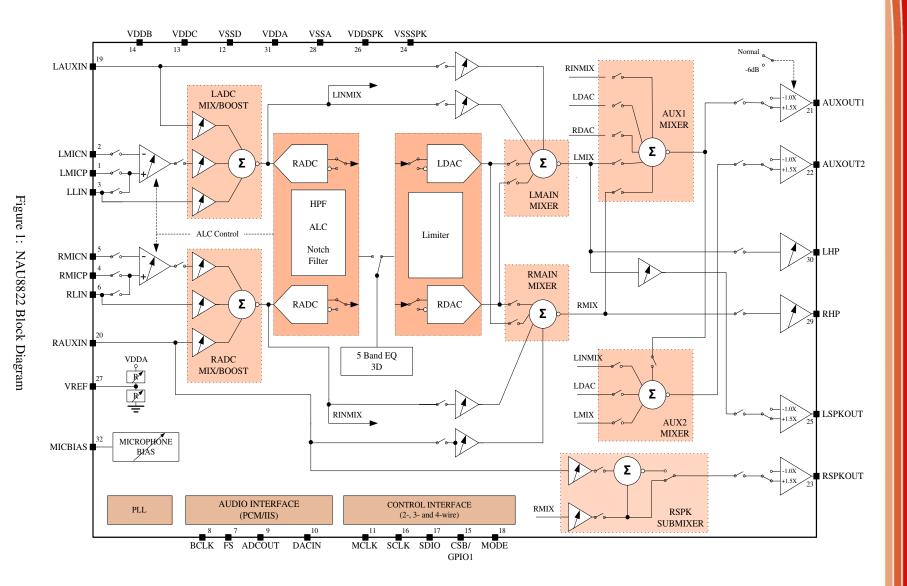

## 1 General Description

The NAU8822 is an upgrade to the WAU8822, and delivers reduced out-of-band noise energy, improved ALC and DSP signal processing, read-out capability of realtime signal level, readout of DSP status, and added controls for industry leading pop/click noise management. Additionally, handling of settings for 5-volt and 3-volt operation are simplified, and all registers unique to Nuvoton are moved to higher addresses. This makes the part a direct hardware and software drop-in replacement for common industry parts.

The NAU8822 is a stereo part with identical left and right channels that share common support elements. Additionally, the right channel auxiliary output path includes a dedicated submixer that supports mixing the right auxiliary input directly into the right speaker output driver. This enables the right speaker channel to output audio that is not present on any other output.

### 1.1.1 Analog Inputs

All inputs, except for the wide range programmable amplifier (PGA), have available analog input gain conditioning of -15dB through +6dB in 3dB steps. All inputs also have individual muting functions with excellent channel isolation and off-isolation from all outputs. All inputs are suitable for full quality, high bandwidth signals.

Each of the left-right stereo channels includes a low noise differential PGA amplifier, programmable for high-gain input. This may be used for a microphone level through line level source. Gain may be set from +35.25db through -12dB at the analog difference-amplifier type programmable amplifier input stage. A separate additional 20dB analog gain is available on this input path, between the PGA output and ADC mixer input. The output of the ADC mixer may be routed to the ADC and/or analog bypass to the analog output sections.

Each channel also has a line level input. This input may be routed to the input PGA, and/or directly to the ADC input mixer.

Each channel has a separate additional auxiliary input. This is a line level input which may be routed the ADC input mixer and/or directly to the analog output mixers.

## 1.1.2 Analog Outputs

There are six high current analog audio outputs. These are very flexible outputs that can be used individually or in stereo pairs for a wide range of end uses. However, these outputs are optimized for specific functions and are described in this section using the functional names that are applicable to those optimized functions.

Each output receives its signal source from built-in analog output mixers. These mixers enable a wide range of signal combinations, including muting of all sources. Additionally, each output has a programmable gain function, output mute function, and output disable function.

The RHP and LHP headphone outputs are optimized for driving a stereo pair of headphones, and are powered from the main analog voltage supply rail, VDDA. These outputs may be coupled using traditional DC blocking series capacitors. Alternatively, these may be configured in a no-capacitor DC coupled design using a virtual ground at ½ VDDA provided by an AUXOUT analog output operating in the non-boost output mode.

The AUXOUT1 and AUXOUT2 analog outputs are powered from the VDDSPK supply rail and VSSSPK ground return path. The supply rail may be the same as VDDA, or may be a separate voltage up to 5.5Vdc. This higher voltage enables these outputs to have an increased output voltage range and greater output power capability.

The RSPKOUT and LSPKOUT loudspeaker outputs are powered from the VDDSPK power supply rail and VSSGND ground return path. RSPKOUT receives its audio signal via an additional submixer. This submixer supports combining a traditional alert sound (from the RAUXIN input) with the right channel headphone output mixer signal. This submixer also provides the signal invert function that is necessary for the normal BTL (Bridge Tied Load) configuration used to drive a high power external loudspeaker. Alternatively, each loudspeaker output may be used individually as a separate high current analog output driver.

A programmable low-noise MICBIAS microphone bias supply output is included. This is suitable for both conventional electret (ECM) type microphone, and to power the newer MEMS all-silicon type microphones.

<u>Important:</u> For analog outputs depopping purpose, when powering up speakers, headphone, AUXOUTs, certain delays are generated after enabling sequence. However, the delays are created by MCLK and sample rate register. For correct operation, sending I2S signal no earlier than 250ms after speaker or headphone enabled and MCLK appearing.

### 1.1.3 ADC, DAC, and Digital Signal Processing

Each left and right channel has an independent high quality ADC and DAC associated with it. These are high performance, 24-bit delta-sigma converters that are suitable for a very wide range of applications.

The ADC and DAC functions are each individually supported by powerful analog mixing and routing. The ADC output may be routed to the digital output path and/or to the input of the DAC in a digital passthrough mode. The ADC and DAC blocks are also supported by advanced digital signal processing subsystems that enable a very wide range of programmable signal conditioning and signal optimizing functions. All digital processing is with 24-bit precision, as to minimize processing artifacts and maximize the audio dynamic range supported by the NAU8822.

The ADCs are supported by a wide range, mixed-mode Automatic Level Control (ALC), a high pass filter, and a notch filter. All of these features are optional and highly programmable. The high pass filter function is intended for DC-blocking or low frequency noise reduction, such as to reduce unwanted ambient noise or "wind noise" on a microphone input. The notch filter may be programmed to greatly reduce a specific frequency band or frequency, such as a 50Hz, 60Hz, or 217Hz unwanted noise.

The DACs are supported by a programmable limiter/DRC (Dynamic Range Compressor). This is useful to optimize the output level for various applications and for use with small loudspeakers. This is an optional feature that may be programmed to limit the maximum output level and/or boost an output level that is too small.

Digital signal processing is also provided for a 3D Audio Enhancement function, and for a 5-Band Equalizer. These features are optional, and are programmable over wide ranges. This pair of digital processing features may be applied jointly to either the ADC audio path or to the DAC audio path, but not to both paths simultaneously.

### 1.1.4 Realtime Signal Level Readout and DSP Status

In addition to general read-back ability of all its registers, the NAU8822 includes powerful capalities to readback signal related DSP information not possible with almost any other CODEC. In conjunction with the ALC, the software by means of the readback function can determine the realtime signal level at the inputs, as well as the realtime actual gain setting being used by the ALC. Additionally, other signal related information can also be determined, such as the Noise Gate on/off status and Automute/Softmute function status. These greatly enhance both the ability to optimize software and to enhance dynamic end product functionality.

### 1.1.5 Digital Interfaces

Command and control of the device is accomplished using a 2-wire/3-wire/4-wire serial control interface. This is a simple, but highly flexible interface that is compatible with many commonly used command and control serial data protocols and host drivers.

Digital audio input/output data streams are transferred to and from the device separately from command and control. The digital audio data interface supports either I2S or PCM audio data protocols, and is compatible with commonly used industry standard devices that follow either of these two serial data formats.

## 1.1.6 Clock Requirements

The clocking signals required for the audio signal processing, audio data I/O, and control logic may be provided externally, or by optional operation of a built-in PLL (Phase Locked Loop).

The PLL is provided as a low cost, zero external component count optional method to generate required clocks in almost any system. The PLL is a fractional-N divider type design, which enables generating accurate desired audio sample rates derived from a very wide range of commonly available system clocks.

The frequency of the system clock provided as the PLL reference frequency may be any stable frequency in the range between 8MHz and 33MHz. Because the fractional-N multiplication factor is a very high precision 24-bit value, any desired sample rate supported by the NAU8822 can be generated with very high accuracy, typically

limited by the accuracy of the external reference frequency. Reference clocks and sample rates outside of these ranges are also possible, but may involve performance tradeoffs and increased design verification.

## 2 Power Supply

This device has been designed to operate reliably using a wide range of power supply conditions and power-on/power-off sequences. There are no special requirements for the sequence or rate at which the various power supply pins change. Any supply can rise or fall at any time without harm to the device. However, pops and clicks may result from some sequences. Optimum handling of hardware and software power-on and power-off sequencing is described in more detail in the Applications section of this document.

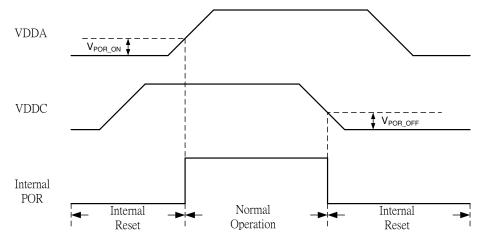

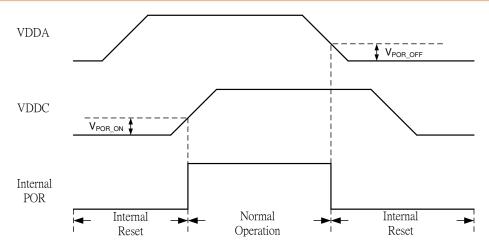

#### 2.1.1 Power-On Reset

The NAU8822 does not have an external reset pin. The device reset function is automatically generated internally when power supplies are too low for reliable operation. The internal reset is generated any time that either VDDA or VDDC is lower than is required for reliable maintenance of internal logic conditions. The reset threshold voltage for VDDA and VDDC is approximately 0.5Vdc. If both VDDA and VDDC are being reduced at the same time, the threshold voltage may be slightly lower. Note that these are much lower voltages than are required for normal operation of the chip. These values are mentioned here as general guidance as to overall system design.

If either VDDA or VDDC is below its respective threshold voltage, an internal reset condition is asserted. During this time, all registers and controls are set to the hardware determined initial conditions. Software access during this time will be ignored, and any expected actions from software activity will be invalid.

When both VDDA and VDDC reach a value above their respective thresholds, an internal reset pulse is generated which extends the reset condition for an additional time. The duration of this extended reset time is approximately 50 microseconds, but not longer than 100 microseconds. The reset condition remains asserted during this time. If either VDDA or VDDC at any time becomes lower than its respective threshold voltage, a new reset condition will result. The reset condition will continue until both VDDA and VDDC again higher than their respective thresholds. After VDDA and VDDC are again both greater than their respective threshold voltage, a new reset pulse will be generated, which again will extend the reset condition for not longer than an additional 100 microseconds.

Figure 2: Power-on reset timing chart when VDDC applied before VDDA

Figure 3: Power-on reset timing chart when VDDA applied before VDDC

| Symbol         | Min | Typical | Max | Unit |

|----------------|-----|---------|-----|------|

| $V_{POR\_ON}$  | -   | 0.5     | -   | V    |

| $V_{POR\_OFF}$ | -   | 0.5     | -   | V    |

#### 2.1.2 Power Related Software Considerations

There is no direct way for software to determine that the device is actively held in a reset condition. If there is a possibility that software could be accessing the device sooner than 100 microseconds after the VDDA and VDDC supplies are valid, the reset condition can be determined indirectly. This is accomplished by writing a value to any register other than register 0x00, with that value being different than the power-on reset initial values. The optimum choice of register for this purpose may be dependent on the system design, and it is recommended the system engineer choose the register and register test bit for this purpose. After writing the value, software will then read back the same register. When the register test bit reads back as the new value, instead of the power-on reset initial value, software can reliably determine that the reset condition has ended.

Although it is not required, it is strongly recommended that a Software Reset command should be issued after power-on and after the power-on reset condition is ended. This will help insure reliable operation under every power sequencing condition that could occur.

If there is any possibility that VDDA or VDDC could be unreliable during system operation, software may be designed to monitor whether a power-on reset condition has happened. This can be accomplished by writing a test bit to a register that is different from the power-on initial conditions. This test bit should be a bit that is never used for any other reason, and does not affect desired operation in any way. Then, software at any time can read this bit to determine if a power-on reset condition has occurred. If this bit ever reads back other than the test value, then software can reliably know that a power-on reset event has occurred. Software can subsequently re-initialize the device and the system as required by the system design.

#### 2.1.3 Software Reset

All chip registers can be reset to power-on default conditions by writing any value to register 0, using any of the control modes. Writing valid data to any other register disables the reset, but all registers need to have the correct operating data written. See the applications section on powering NAU8822 up for information on avoiding pops and clicks after a software reset.

## 3 Input Path Detailed Descriptions

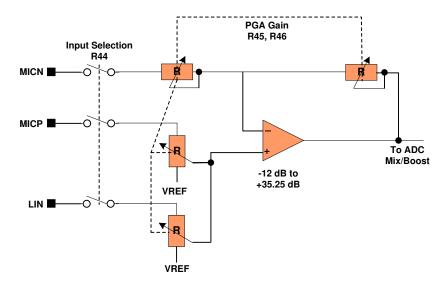

The NAU8822 provides multiple inputs to acquire and process audio signals from microphones or other sources with high fidelity and flexibility. There are left and right input paths, each with three input pins, which can be used to capture signals from single-ended, differential or dual-differential microphones. These input channels each include a programmable gain amplifier (PGA). The outputs of the PGAs, plus two additional auxiliary inputs, are then connected to the input boost/mix stages for maximum flexibility handling various signal sources.

All inputs are maintained at a DC bias at approximately ½ of the AVDD supply voltage. Connections to these inputs should be AC-coupled by means of DC blocking capacitors suitable for the device application.

Differential microphone input (MICN & MICP pins) and Programmable Gain Amplifier

The NAU8822 features a low-noise, high common mode rejection ratio (CMRR), differential microphone input pair, MICP and MICN, which are connected to a PGA gain stage. The differential input structure is essential in noisy digital systems where amplification of low-amplitude analog signals is necessary such as in portable digital media devices and cell phones. Differential inputs very useful to reduce ground noise in systems in which there are ground voltage differences between different chips and other components. When properly implemented, the differential input architecture offers an improved power-supply rejection ratio (PSRR) and higher ground noise immunity.

## 3.1 Programmable Gain Amplifier (PGA)

Each PGA supports three possible inputs, MICP, MICN, and LIN. These are the microphone differential pair and a separate line level input. The PGA has a gain range of -12dB through +35.25dB in evenly spaced decibel increments of 0.75dB. Operation of the PGA is subject to control by the following registers:

- R2 Power management controls for the left and right PGA

- R2 Power management controls for ADC Mix/Boost (must be "on" for any PGA path to function)

- R7 Zero crossing timeout control

- R32 Automatic Level Control (ALC) for the left and right PGA

- R44 Input selection options for the left and right PGA

- R45 Volume (gain), mute, update bit, and zero crossing control for the left PGA

- R46 Volume (gain), mute, update bit, and zero crossing control for the right PGA

<u>Important:</u> The R45 and R46 update bits are write-only bits. The primary intended purpose of the update bit is to enable simultaneous changes to both the left and right PGA volume values, even though these values must be written sequentially. When there is a write operation to either R45 or R46 volume settings, but the update bit is not set (value = 0), the new volume setting is stored as pending for the future, but does not go into effect. When there is a write operation to either R45 or R46 and the update bit is set (value = 1), then the new value in the register being written is immediately put into effect, and any pending value in the other PGA volume register is put into effect at the same time.

Note: If the ALC automatic level control is enabled, the function of the ALC is to automatically adjust the R45 or R46 volume setting. If ALC is enabled for the left or right, or both channels, then software should avoid changing the volume setting for the affected channel or channels. The reason for this is to avoid unexpected volume changes caused by competition between the ALC and the direct software control of the volume setting.

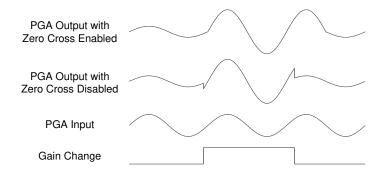

Zero-Crossing controls are implemented to suppress clicking sounds that may occur when volume setting changes take place while an audio input signal is active. When the zero crossing function is enabled (logic = 1), any volume change for the affected channel will not take place until the audio input signal passes through the zero point in its peak-to-peak swing. This prevents any instantaneous voltage change to the audio signal caused by volume setting changes. If the zero crossing function is disabled (logic = 0), volume changes take place instantly on condition of the Update Bit, but without regard to the instantaneous voltage level of the affected audio input signal.

The R7 zero crossing timeout control is an additional feature to limit the amount of time that a volume change to the PGA is delayed pending a zero crossing event. If the input signal is such that there are no zero crossing events, and the timeout control is enabled (level = 1), any new volume setting to either PGA will automatically be put into effect after between 2.5 and 3.5 periods of the Slow Timer Clock (see description under "Miscellaneous Functions").

### 3.1.1 Zero Crossing Example

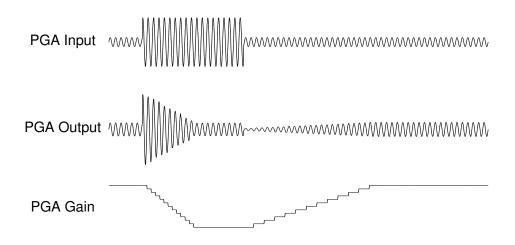

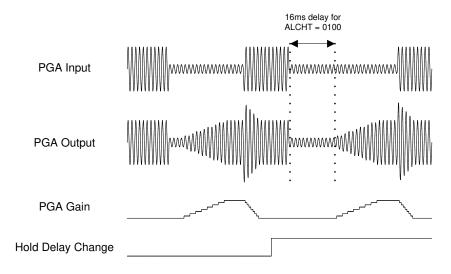

This drawing shows in a graphical form the problem and benefits of using the zero crossing feature. There is a major audible improvement as a result of using the zero crossing feature.

Figure 4: Zero Crossing Gain Update Operation

Figure 5: PGA Input Structure Simplified Schematic

## 3.2 Positive Microphone Input (MICP)

The positive (non-inverting) microphone input (MICP) can be used separately, or as part of a differential input configuration. This input pin connects to the positive (non-inverting) terminal of the PGA amplifier under control of register R44. When the R44 associated control bit is set (logic = 1), a switch connects MICP to the PGA input. When the associated control bit is not set (logic = 0), the MICP pin is connected to a resistor of approximately  $30k\Omega$  which is tied to VREF. The purpose of the tie to VREF is to reduce any pop or click sound by keeping the DC level of the MICP pin close to VREF at all times.

Note: If the MICP signal is not used differentially with MICN, the PGA gain values will be valid only if the MICN pin is terminated to a low impedance signal point. This termination should normally be an AC coupled path to signal ground.

This input impedance is constant regardless of the gain value. The nominal input impedance for this input is given by the following table. Impedance for specific gain values not listed in this table can be estimated through interpolation between listed values.

| Nominal Input Impedance | Gain<br>(dB) | Impedance (kΩ) |

|-------------------------|--------------|----------------|

|                         | -12          | 94             |

|                         | -9           | 94             |

| LMICP & RMICP to        | -6           | 94             |

| non-inverting PGA input | -3           | 94             |

|                         | 0            | 94             |

| or                      | 3            | 94             |

| LLIN & RLIN to          | 6            | 94             |

| non-inverting PGA input | 9            | 94             |

|                         | 12           | 94             |

|                         | 18           | 94             |

|                         | 30           | 94             |

|                         | 35.25        | 94             |

Table 1: Microphone and Line Non-Inverting Input Impedances

## 3.3 Negative Microphone Input (MICN)

The negative (inverting) microphone input (MICN) can be used separately, or as part of a differential input configuration. This input pin connects to the negative (inverting) terminal of the PGA amplifier under control of register R44. When the R44 associated control bit is set (logic = 1), a switch connects MICP to the PGA input. When the associated control bit is not set (logic = 0), the MICN pin is connected to a resistor of approximately  $30k\Omega$  which is tied to VREF. The purpose of the tie to VREF is to reduce any pop or click sound by keeping the DC level of the MICN pin close to VREF at all times.

It is important for a system designer to know that the MICN input impedance varies as a function of the selected PGA gain. This is normal and expected for a difference amplifier type topology. The nominal resistive impedance values for this input over the possible gain range are given by the following table. Impedance for specific gain values not listed in this table can be estimated through interpolation between listed values.

| Nominal Input Impedance               | Gain<br>(dB) | Impedance<br>(kΩ) |

|---------------------------------------|--------------|-------------------|

| LMICN or RMICN to inverting PGA input | -12          | 75                |

|                                       | -9           | 69                |

|                                       | -6           | 63                |

|                                       | -3           | 55                |

|                                       | 0            | 47                |

|                                       | 3            | 39                |

|                                       | 6            | 31                |

|                                       | 9            | 25                |

|                                       | 12           | 19                |

|                                       | 18           | 11                |

|                                       | 30           | 2.9               |

|                                       | 35.25        | 1.6               |

Table 2: Microphone Inverting Input Impedances

System designers should also note that at the highest gain values, the input impedance is relatively low. For most inputs, the best strategy if higher gain values are needed is to use the input PGA in combination with the +20dB gain boost available on the PGA Mix/Boost stage that immediately follows the PGA output. A good guideline is to use the PGA gain for up to around 20dB of gain. If more gain than this is required and the lower input impedance of the PGA at high gains is a problem, a combination of the PGA and boost stage should be used. In this type of combined gain configuration, it is preferred to have at least 6dB gain at the PGA input stage to benefit from the PGA low noise characteristics.

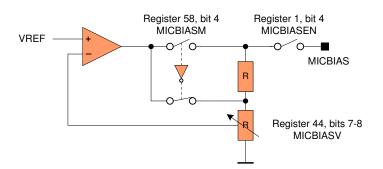

### 3.4 Microphone biasing

The MICBIAS pin provides a low-noise microphone DC bias voltage as may be required for operation of an external microphone. This built-in feature can typically provide up to 3mA of microphone bias current. This DC bias voltage is suitable for powering either traditional ECM (electret) type microphones, or for MEMS types microphones with an independent power supply pin.

Seven different bias voltages are available for optimum system performance, depending on the specific application. The microphone bias pin normally requires an external filtering capacitor as shown on the schematic in the Application section. The microphone bias function is controlled by the following registers:

- R1 Power control for MICBIAS feature (enabled when bit 4 = 1)

- R58 Optional low-noise mode and different bias voltage levels (enabled when bit 4 = 1)

- R44 Primary MICBIAS voltage selection

The low-noise feature results in greatly reduced noise in the external MICBIAS voltage by placing a resistor of approximately 200-ohms in series with the output pin. This creates a low pass filter in conjunction with the external micbias filter capacitor, but without any additional external components. The low noise feature is enabled when the mode control bit 4 in register R58 is set (level = 1)

| Register 44,<br>Bits 7-8 | Register 58,<br>Bit 4 | Microphone<br>Bias Voltage |

|--------------------------|-----------------------|----------------------------|

| DILS 7-0                 | DIL 4                 | <u>bias voitage</u>        |

| 00                       | 0                     | 0.90 * VDDA                |

| 01                       | 0                     | 0.65 * VDDA                |

| 10                       | 0                     | 0.75 * VDDA                |

| 11                       | 0                     | 0.50 * VDDA                |

| 00                       | 1                     | 0.85 * VDDA                |

| 01                       | 1                     | 0.60 * VDDA                |

| 10                       | 1                     | 0.70 * VDDA                |

| 11                       | 1                     | 0.50 * VDDA                |

Figure 6: Microphone Bias Generator

## 3.5 Line/Aux Input Impedance and Variable Gain Stage Topology

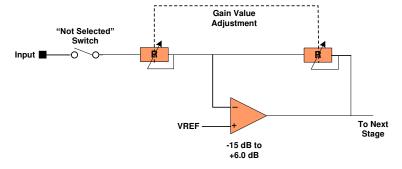

Except for the input PGAs, other variable gain stages are implemented similarly to the simplified schematic shown here. The gain value changes affect input impedance in the ranges detailed in the description of each type of input path. If a path is in the "not selected" condition, then the input impedance will be in a high impedance condition. If an external input pin is not used anywhere in the system, it will be coupled to a DC tie-off of approximately  $30k\Omega$  coupled to VREF. The unused input/output tie-off function is explained in more detail in the Application Information section of this document.

Figure 7: Variable Gain Stage Simplified Schematic

The input impedance presented to these inputs depends on the input routing choices and gain values. If an input is routed to more than one internal input node, then the effective input impedance will be the parallel combination of the impedance of the multiple nodes that are used. The impedance looking into the PGA non-inverting input is constant as listed in the section discussing the microphone input PGAs. The nominal resistive input impedances looking into the ADC Mix/Boost input inputs are listed in the following table:

| Inputs                                                                          | Gain<br>(dB) | Impedance<br>(kΩ) |

|---------------------------------------------------------------------------------|--------------|-------------------|

| LAUXIN & RAUXIN to L/RADC MIX/BOOST amp or  LLIN & RLIN to L/RADC MIX/BOOST amp | Not Selected | High-Z            |

|                                                                                 | -12          | 159               |

|                                                                                 | -9           | 113               |

|                                                                                 | -6           | 80                |

|                                                                                 | -3           | 57                |

|                                                                                 | 0            | 40                |

|                                                                                 | 3            | 28                |

|                                                                                 | 6            | 20                |

Table 3: MIX/BOOST Amp Impedances

The nominal resistive input impedances presented to signal pins that are directly routed to an output mixer are listed in the following table. If an input is connected to other active nodes, then this value is in parallel with the resistive input impedance of any such other node.

| Inputs                           | Gain<br>(dB) | Impedance<br>(kΩ) |

|----------------------------------|--------------|-------------------|

| LAUXIN & RAUXIN to<br>bypass amp | -15          | 225               |

|                                  | -12          | 159               |

|                                  | -9           | 113               |

| Or  RAUXIN to RSPK SUBMIXER amp  | -6           | 80                |

|                                  | -3           | 57                |

|                                  | 0            | 40                |

|                                  | 3            | 28                |

|                                  | 6            | 20                |

Table 4: Bypass Amp and RSPK SUBMIXER Input Impedances

## 3.6 Left and Right Line Inputs (LLIN and RLIN)

A third possible input to the left or right PGA is an optional associated LIN left or right line level input. These inputs may be routed to the PGA non-inverting input, and/or connect directly to the ADC Mixer/Boost stage. If routed to the PGA, this signal is processed as an alternate pin for the MICP signal. LIN may be received differentially in relation to the MICN pin and has available the same gain range as for MICP. As in the operational case of using the MICP input, the MICN input must have a low impedance path to signal ground, so that the gain values chosen in the PGA are valid.

Note: It <u>not</u> recommended that both the LIN line input path to the PGA and the MICP path to the PGA be enabled at the same time. This will cause the differential gain to be unbalanced, and result in poor common mode rejection. Also, this will result in the LIN and MICP signals being connected together through internal chip resistors.

The line input pins, may alternatively be configured to operate as a GPIO (General Purpose Input/Output) logic input pin. This intended purpose is static logic voltage level sensing to determine if a headset is present or not as part of a physical detection of a possible external headset. Only one GPIO pin at any one time can be assigned for this purpose.

Registers that affect operation of the LLIN and RLIN inputs are:

R2 ADC Mix/Boost power control (must be "on" for any LIN path to function)

R9 GPIO selection for headset detect function

R44 PGA input selection control bits

If selected, all other PGA control registers (see PGA description)

R47 Left line input ADC Mix/Boost volume and mute (bits 4, 5, and 6)

R48 Right line input ADC Mix/Boost volume and mute (bits 4, 5, and 6)

## 3.7 Auxiliary inputs (LAUXIN, RAUXIN)

The left and right channels each have an additional input that is separate from the programmable amplifier stage. These are the left and right auxiliary inputs, LAUXIN and RAUXIN. These inputs may be routed to either or both the associated ADC Mix/Boost stage, or the associated LCH MIX or RCH MIX output mixer.

The RAUXIN input may additionally be routed to the Right Speaker Submixer in the analog output section. This path enables a sound to be output from the RSPKOUT speaker output, but without being audible anywhere else in the system. One purpose of this path is to support a traditional "beep" sound, such as from a microprocessor toggle bit. This is a historical application scenario which is now uncommon.

The auxiliary inputs are affected by the following registers:

ADC Mix/Boost if used (see ADC Mix/Boost section)

LCH MIXER or RCH MIXER if used (see output mixer section)

BEEP MIXER if used (see Beep Mixer section)

Note: no power control registers affect only the auxiliary inputs

The input impedance presented to these inputs depends on the input routing choices and gain values. If an input is routed to more than one internal input node, then the effective input impedance will be the parallel combination of the impedance of the multiple nodes that are used. The input impedances presented to these inputs are the same as those listed for the LLIN and RLIN inputs.

## 3.8 ADC Mix/Boost Stage

The left and right channels each have an independent ADC Mix/Boost stage. Most analog input signals must pass through the ADC Mix/Boost stage before use anywhere else in this device. The only analog inputs that can completely bypass the ADC Mix/Boost stage are the LAUXIN and RAUXIN auxiliary inputs.

The ADC mixer stage has three inputs, AUX, LIN, and PGA. The AUX input is for the associated auxiliary input, and the LIN is for the associated line input. The PGA input is an internal connection to the associated programmable gain amplifier servicing the microphone and line inputs.

All three inputs to the ADC Mix/Boost stage can be independently muted, and all three inputs have independent gain controls. The AUX and LIN inputs have an available gain range of -12dB through +6dB in 3dB steps. The PGA input path has a choice of 0dB or 20dB of gain in addition to the gain in the PGA.

Registers that affect the ADC Mix/Boot stage are:

R2 Power control for left and right channels

R45 mute function for left channel PGA (bit 6 = 0 = muted condition)

R46 mute function for right channel PGA (bit 6 = 0 = muted condition)

R47 gain and mute control for left channel AUX and LIN

R48 gain and mute control for right channel AUX and LIN

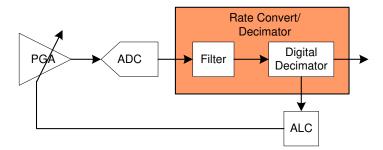

## 3.9 Input Limiter / Automatic Level Control (ALC)