# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High-Voltage Current-Mode PWM Controller Featuring Peak Power Excursion and Extremely Low Stand-by Power Consumption

The NCP1249 is a highly integrated high–voltage PWM controller capable of delivering a rugged and high performance offline power supply with extremely low no–load consumption. With a supply range up to 30 V, the controller hosts a jittered 65–kHz switching circuitry operated in peak current mode control. When the power on the secondary side starts to decrease, the controller automatically folds back its switching frequency down to a minimum level of 26 kHz. As the power further goes down, the part enters skip cycle while freezing the peak current setpoint.

To help build rugged converters, the controller features several key protective features: a internal brown–out, a non–dissipative Over Power Protection for a constant maximum output current regardless of the input voltage and two latched over voltage protection inputs – either through a dedicated pin or via the VCC input.

The controller architecture is arranged to authorize a transient peak power excursion when the peak current hits the limit. At this point, the switching frequency is increased from 65 kHz to 130 kHz until the peak requirement disappears. The timer duration is then modulated as the converter crosses a peak power excursion mode (long) or undergoes a short circuit (short).

NCP1249 comes in both Active ON (A and B versions) and Active OFF (C and D versions).

# Features

- High-voltage Current Source for Lossless Start-up Sequence

- Remote Input for Standby Operation Control

- Automatic and Lossless X2 Capacitors Discharge Function

- 65-kHz Fixed-frequency Current-mode Control Operation with 130-kHz Excursion

- Internal and Adjustable Over Power Protection (OPP) Circuit

- Internal Brown–Out Protection Circuit

- Frequency Foldback down to 26 kHz and Skip–cycle in Light Load Conditions

- Adjustable Ramp Compensation

- Internally Fixed 4-ms Soft-start

- 100% to 25% Timer Reduction from Overload to Short–circuit Fault

- Frequency Jittering in Normal and Frequency Foldback Modes

- Latched OVP Input for Improved Robustness and Latched OVP on V<sub>cc</sub>

- Up to 30 V Vcc Maximum Rating

- +300 mA/ -500 mA Source/Sink Drive Capability

- Extremely Low No-load Standby Power

- Option for Auto–Recovery or Latched Short–Circuit Protection

- Internal Thermal Shutdown with Hysteresis

- These are Pb–Free Devices

# **Typical Applications**

• Converters Requiring Peak–power Capability such as Printers Power Supplies, ac–dc Adapters for Game Stations

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.

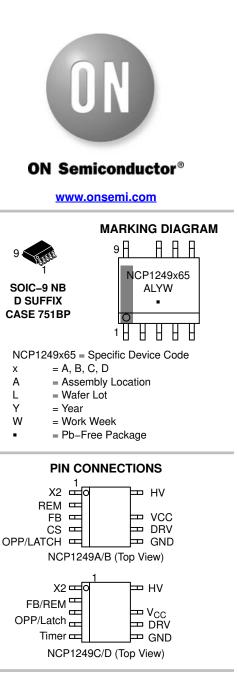

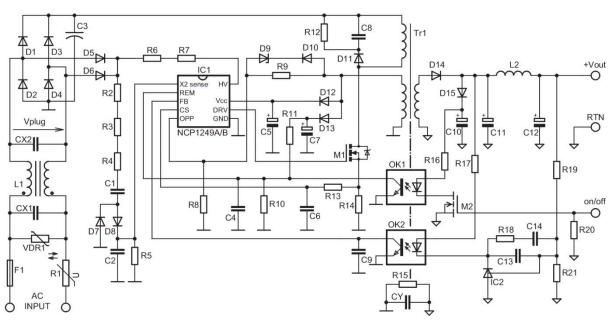

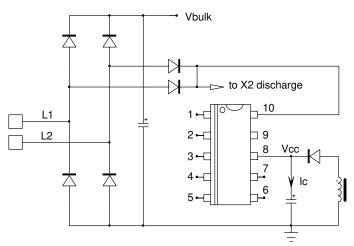

Figure 1. Typical Application Example – NCP1249 (A/B)

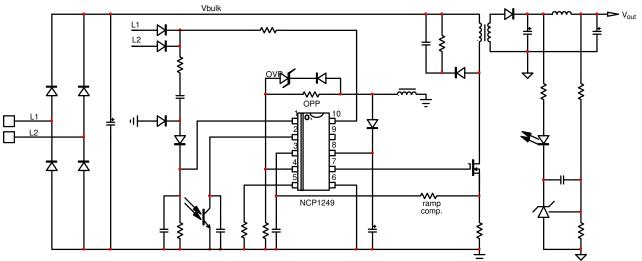

Figure 2. Typical Application Example – NCP1249 (C/D)

### **Table 1. PIN FUNCTIONS**

| A/B | C/D | Pin Name  | Function                                                 | Pin Description                                                                                                                                          |

|-----|-----|-----------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1   | X2        | X2–capacitors discharge                                  | When the voltage on this pin disappears, the controller ensures the X2–capacitors discharge.                                                             |

| 2   | 2   | REM       | Remote input                                             | Initiates ultra low consumption mode (off-mode) when brought<br>above 8 V (A/B) or below 0.4 V (C/D).                                                    |

| 3   | 2   | FB        | Feedback pin                                             | Connecting an opto-coupler to this pin allows regulation.                                                                                                |

| 4   | 3   | CS        | Current sense + ramp<br>compensation                     | This pin monitors the primary peak current but also offers a means to introduce slope compensation.                                                      |

| 5   | 4   | OPP/Latch | Adjust the Over Power Protection<br>Latches off the part | A resistive divider from the auxiliary winding to this pin sets the<br>OPP compensation level. When brought above 3 V, the part is<br>fully latched off. |

| 6   | 6   | GND       | -                                                        | The controller ground.                                                                                                                                   |

| 7   | 7   | DRV       | Driver output                                            | The driver's output to an external MOSFET gate.                                                                                                          |

| 8   | 8   | VCC       | Supplies the controller                                  | This pin is connected to an external auxiliary voltage and supplies the controller. When above a certain level, the part fully latches off.              |

| 9   | 9   | NC        | -                                                        | Increases insulation distance between high and low voltage pins.                                                                                         |

| 10  | 10  | HV        | High-voltage input                                       | This pin provides a charging current during start–up and auto–recovery faults but also a means to efficiently discharge the input X2 capacitors.         |

| Х   | 5   | TIMER     | Fault timer adjustment                                   | A resistor to ground adjusts the timer duration in fault condition.                                                                                      |

### Table 2. MAXIMUM RATINGS TABLE

| Symbol             | Rating                                                                                 | Value                        | Unit |

|--------------------|----------------------------------------------------------------------------------------|------------------------------|------|

| V <sub>cc</sub>    | Power Supply voltage, VCC pin, continuous voltage                                      | -0.3 to 30                   | V    |

| V <sub>HV</sub>    | High Voltage (HV) Pin (pin 10)                                                         | -0.3 to 500                  | V    |

| I <sub>HV</sub>    | High Voltage (pin 10) Input Current                                                    | 20                           | mA   |

| Vpin_x             | Maximum voltage on low power pins (X2, REM, FB, CS, OPP)                               | -0.3 to 10                   | V    |

| V <sub>DRV</sub>   | Maximum voltage on drive pin                                                           | –0.3 to V <sub>cc</sub> +0.3 | V    |

| I <sub>OPP</sub>   | Maximum injected current into the OPP pin                                              | -2                           | mA   |

| $R_{\theta J-A}$   | Thermal Resistance Junction-to-Air                                                     | 211                          | °C/W |

| T <sub>J,max</sub> | Maximum Junction Temperature                                                           | 150                          | °C   |

|                    | Storage Temperature Range                                                              | -60 to +150                  | °C   |

|                    | ESD Capability, HBM model (All pins except HV) per JEDEC standard JESD22, Method A114E | 2                            | kV   |

|                    | ESD Capability, Machine Model per JEDEC standard JESD22, Method A115A                  | 200                          | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

### **Table 3. OPTIONS AND ORDERING INFORMATION**

| Device         | Overload<br>Protection | Switching<br>Frequency | Peak Frequency | Package   | Shipping†     |

|----------------|------------------------|------------------------|----------------|-----------|---------------|

| NCP1249AD65R2G | Latched                | 65 kHz                 | 130 kHz        |           |               |

| NCP1249BD65R2G | Autorecovery           | 65 kHz                 | 130 kHz        | SOIC-9    | 2500 / Tape & |

| NCP1249CD65R2G | Latched                | 65 kHz                 | 130 kHz        | (Pb-Free) | Reel          |

| NCP1249DD65R2G | Autorecovery           | 65 kHz                 | 130 kHz        |           |               |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging. Specifications Brochure, BRD8011/D.

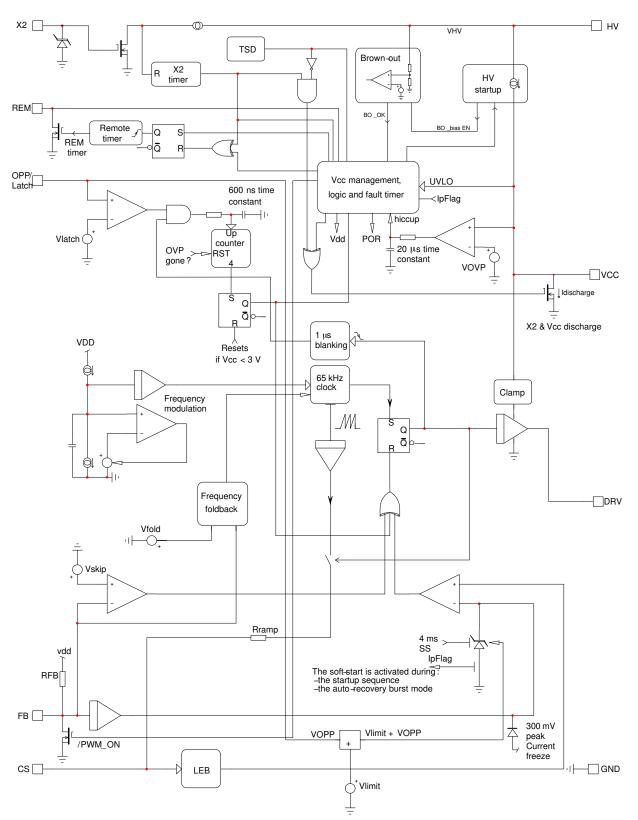

Figure 3. Internal Circuit Architecture – NCP1249 (A/B)

### **Table 4. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol                       | Rating                                                                                                       | Pin   | Min | Тур | Max  | Unit |

|------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|------|

| HV STARTUP CU                | RRENT SOURCE                                                                                                 |       |     |     |      |      |

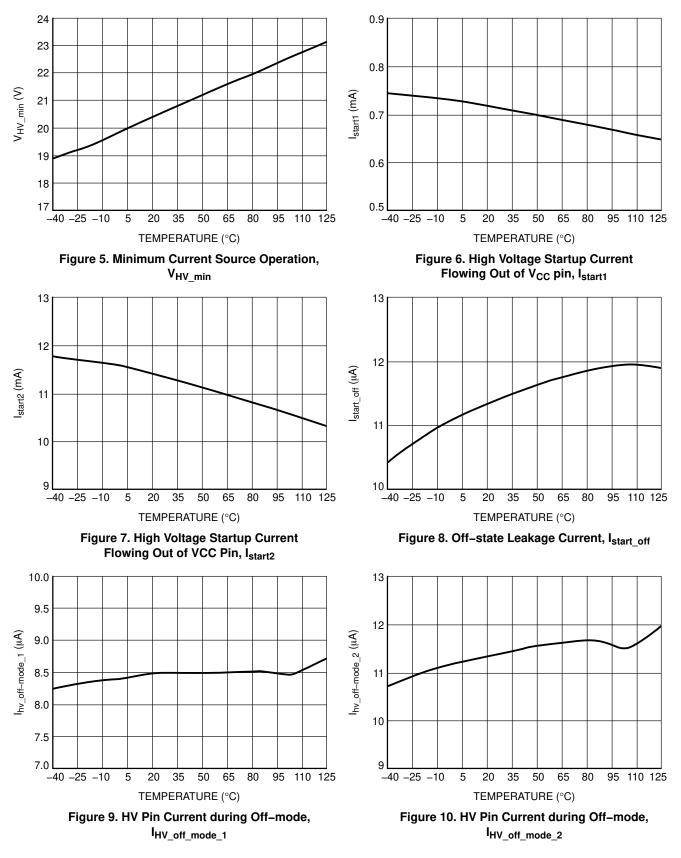

| V <sub>HV_min</sub>          | Minimum voltage for current source operation ( $V_{CC} = 4V$ )                                               | 10    | -   | 30  | 60   | V    |

| I <sub>start1</sub>          | Current flowing out of VCC pin ( $V_{CC} = 0 V$ )                                                            | 8, 10 | 0.2 | 0.7 | 1    | mA   |

| I <sub>start2</sub>          | Current flowing out of VCC pin ( $V_{CC} = V_{CC_{ON}} - 0.5 V$ )                                            | 8, 10 | 6   | 10  | 15   | mA   |

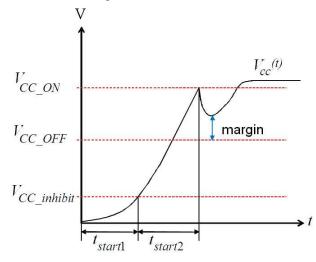

| V <sub>CC_inhibit</sub>      | V <sub>CC</sub> level for I <sub>start1</sub> to I <sub>start2</sub> transition                              | 8     | 0.5 | 1   | 1.25 | V    |

| I <sub>start_off</sub>       | Off-state leakage current ( $V_{HV}$ = 500 V, $V_{CC}$ = 15 V)                                               | 10    | -   | 15  | -    | μA   |

| I <sub>HV_off</sub> -mode_1  | HV pin leakage current when off-mode is active ( $V_{HV}$ = 141 V)                                           | 10    | _   | -   | 15   | μA   |

| I <sub>HV_off</sub> -mode_2  | HV pin leakage current when off-mode is active ( $V_{HV}$ = 325 V)                                           | 10    | -   | -   | 19   | μA   |

| V <sub>HV_min_off-mode</sub> | Minimum voltage on HV pin during off-mode ( $V_{REM} = 10V, V_{CC} = 0V$ )                                   | 10    | -   | -   | 10   | V    |

| SUPPLY SECTIO                |                                                                                                              |       | 1   |     |      |      |

| V <sub>CC_ON</sub>           | V <sub>CC</sub> increasing level at which driving pulses are authorized                                      | 8     | 16  | 18  | 20   | V    |

| V <sub>CC_OFF</sub>          | V <sub>CC</sub> decreasing level at which driving pulses are stopped                                         | 8     | 9.5 | 10  | 11   | V    |

| V <sub>CC_HYST</sub>         | Hysteresis V <sub>CC ON</sub> – V <sub>CC OFF</sub>                                                          | 8     | 6   | -   | -    | V    |

| V <sub>CC_bias</sub>         | V <sub>CC</sub> level during a fault                                                                         | 8     | 4.7 | 5.5 | 6.5  | V    |

|                              | Internal IC consumption with $I_{FB}{=}75~\mu\text{A},f_{SW}{=}65~\text{kHz}$ and $C_L$ = 0                  | 8     | -   | 1.6 | 2.6  | mA   |

| I <sub>CC2</sub>             | Internal IC consumption with I <sub>FB</sub> =75 $\mu$ A, f <sub>SW</sub> =65 kHz and C <sub>L</sub> = 1 nF  | 8     | -   | 2.3 | 3.4  | mA   |

| I <sub>CC3</sub>             | Internal IC consumption with IFB=75 $\mu$ A, f <sub>SW</sub> =130 kHz and C <sub>L</sub> = 0                 | 8     | -   | 1.9 | 2.9  | mA   |

| I <sub>CC4</sub>             | Internal IC consumption with I <sub>FB</sub> =75 $\mu$ A, f <sub>SW</sub> =130 kHz and C <sub>L</sub> = 1 nF | 8     | -   | 3.3 | 4.4  | mA   |

| I <sub>CC_skip</sub>         | Internal IC consumption while in skip mode                                                                   | 8     | 660 | 960 | 1360 | μA   |

| I <sub>CC_latch</sub>        | Internal IC consumption during Latch – off mode                                                              | 8     | -   | 350 | 520  | μA   |

| BROWN-OUT                    |                                                                                                              |       |     |     |      |      |

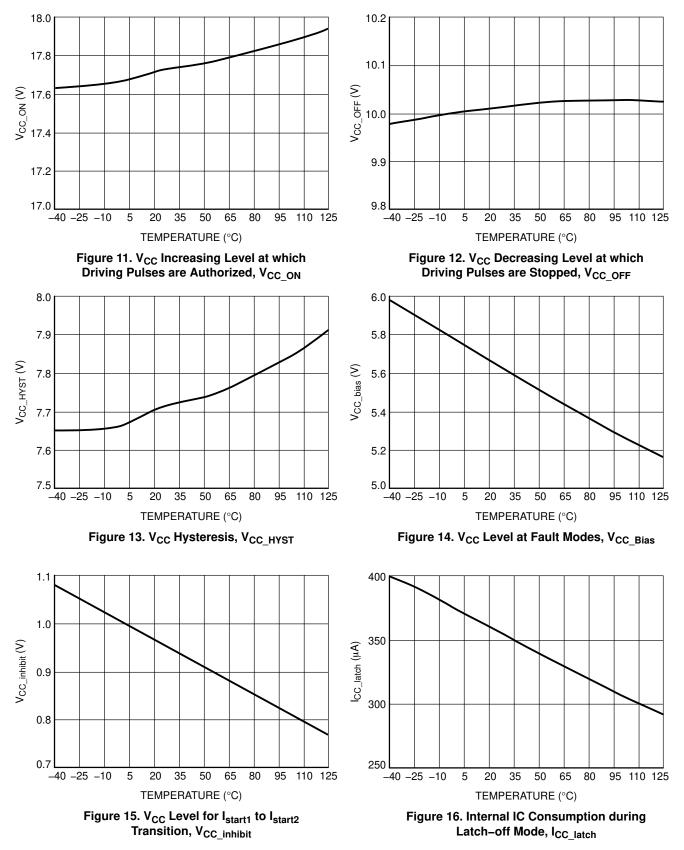

| V_BO_on                      | Brown–Out turn–on threshold (V <sub>HV</sub> going up)                                                       | 10    | 92  | 101 | 110  | V    |

| V_BO_off                     | Brown–Out turn–off threshold (V <sub>HV</sub> going down)                                                    | 10    | 84  | 93  | 102  | V    |

| BO_Timer                     | Timer duration for line cycle drop-out                                                                       | 10    | 40  | -   | 100  | ms   |

| X2 DISCHARGE                 | CIRCUITRY                                                                                                    |       | 1   |     |      |      |

| V <sub>th_X2</sub>           | X2 timer disable switch threshold voltage                                                                    | 1     | 1   | 1.5 | 2    | V    |

| V <sub>th_X2_hyst</sub>      | Hysteresis on the X2 pin                                                                                     | 1     | -   | 100 | -    | mV   |

| V_X2_clamp                   | X2 input clamp voltage                                                                                       | 1     | _   | 4   | -    | V    |

| X2_Timer                     | X2 timer duration                                                                                            | 1     | 70  | -   | 140  | ms   |

| I_x2_leak                    | X2 input leakage current ( $V_{X2} = 2.5 V$ )                                                                | 1     | _   | -   | 0.3  | μA   |

| I_x2_dis                     | Maximum discharge switch current (V <sub>CC</sub> = 10V)                                                     | 10    | 6   | 10  | 13   | mA   |

| DRIVE OUTPUT                 |                                                                                                              |       |     |     |      |      |

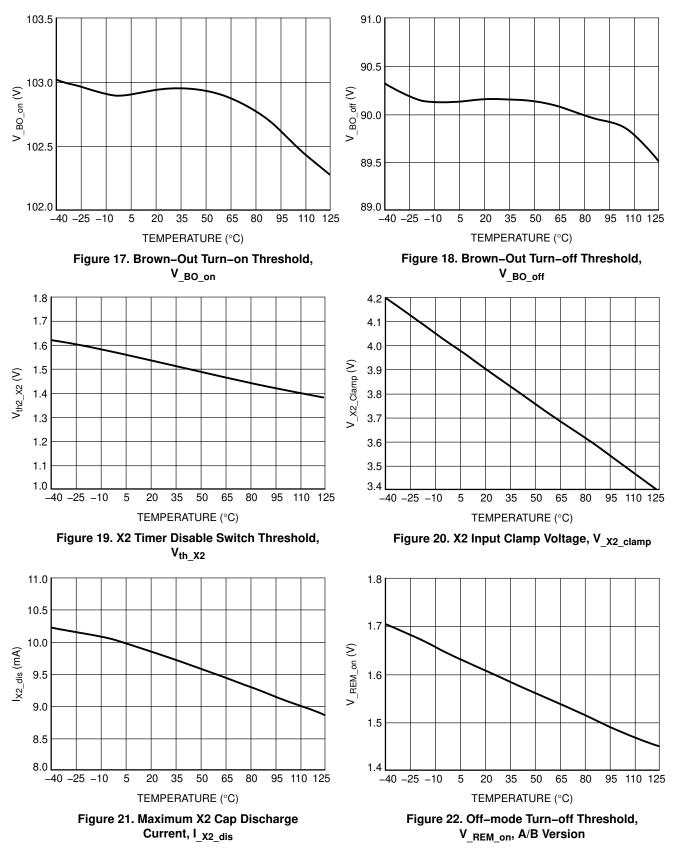

| Tr                           | Output voltage rise-time @ $C_L = 1 \text{ nF}$ , 10–90% of output signal                                    | 7     | -   | 40  | 80   | ns   |

| T <sub>f</sub>               | Output voltage fall-time @ $C_L = 1 \text{ nF}$ , 10-90% of output signal                                    | 7     | _   | 30  | 70   | ns   |

| R <sub>OH</sub>              | Source resistance                                                                                            | 7     | -   | 13  | -    | Ω    |

| R <sub>OL</sub>              | Sink resistance                                                                                              | 7     | _   | 6   | -    | Ω    |

| Isource                      | Peak source current, V <sub>GS</sub> = 0 V – note 1                                                          | 7     |     | 300 |      | mA   |

| I <sub>sink</sub>            | Peak sink current, V <sub>GS</sub> = 12 V – note 1                                                           | 7     |     | 500 | 1    | mA   |

Guaranteed by design

See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV.

A 1–MΩ resistor is connected from pin 4 to the ground for the measurement.

\*C/D version

### Table 4. ELECTRICAL CHARACTERISTICS

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol                | Rating                                                                       | Pin   | Min | Тур  | Max | Unit |

|-----------------------|------------------------------------------------------------------------------|-------|-----|------|-----|------|

| DRIVE OUTPUT          |                                                                              |       |     |      |     |      |

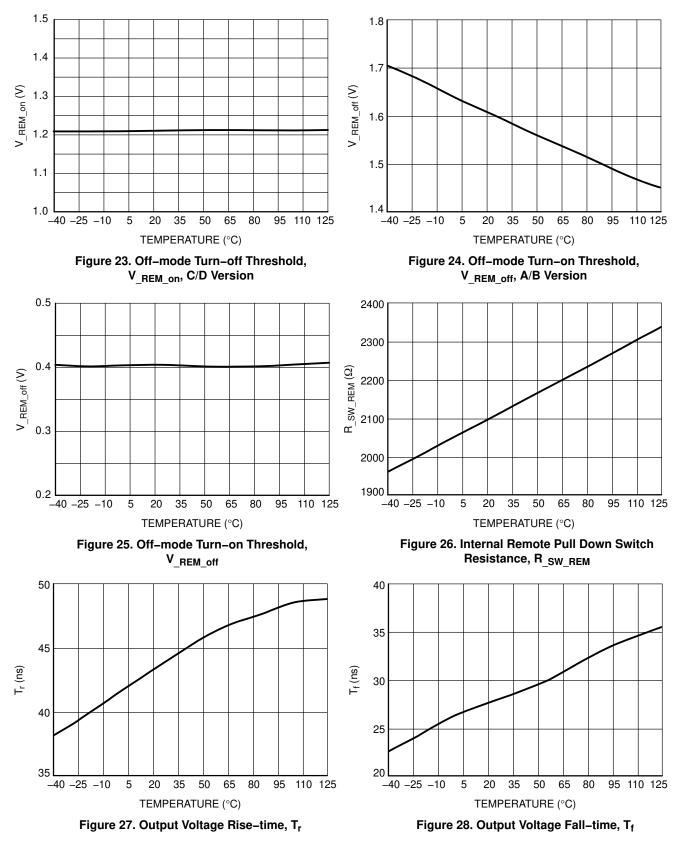

| V <sub>DRV_low</sub>  | DRV pin level at V_CC close to V_CC_OFF with a 33–k $\Omega$ resistor to GND | 7     | 8   | -    | -   | V    |

| V <sub>DRV_high</sub> | DRV pin level at V <sub>CC</sub> = V <sub>OVP</sub> –0.2 V, DRV unloaded     | 7     | 10  | 12   | 14  | V    |

| CURRENT COMP          | ARATOR                                                                       |       |     |      |     |      |

| I <sub>IB</sub>       | Input Bias Current @ 0.8 V input level on pin 4                              | 4, 3* |     | 0.02 |     | μA   |

|                       |                                                                              |       |     |      |     |      |

| V <sub>limit</sub>     | Maximum internal current setpoint – Tj = 25 $^{\circ}$ C – pin 5 grounded                          | 4, 3* | 0.744 | 0.8  | 0.856 | V  |

|------------------------|----------------------------------------------------------------------------------------------------|-------|-------|------|-------|----|

| V <sub>limit</sub>     | Maximum internal current setpoint –<br>Tj from –40° to 125°C – pin 5 grounded                      | 4, 3* | 0.72  | 0.8  | 0.88  | V  |

| V <sub>fold_cs</sub>   | Default internal voltage set point for frequency foldback trip point $\approx 47\%$ of $V_{limit}$ | 4, 3* |       | 475  |       | mV |

| V <sub>freeze_cs</sub> | Internal peak current setpoint freeze ( $\approx$ 31% of V <sub>limit</sub> )                      | 4, 3* |       | 250  |       | mV |

| T <sub>DEL</sub>       | Propagation delay from current detection to gate off-state                                         | 4, 3* |       | 100  | 150   | ns |

| T <sub>LEB</sub>       | Leading Edge Blanking Duration                                                                     | 4, 3* |       | 300  |       | ns |

| T <sub>SS</sub>        | Internal soft-start duration activated upon startup, auto-recovery                                 | -     |       | 4    |       | ms |

| I <sub>OPPo</sub>      | Setpoint decrease for pin 5 biased to -250 mV - (Note 2)                                           | 4, 3* |       | 31.3 |       | %  |

| I <sub>OOPv</sub>      | Voltage setpoint for pin 5 biased to $-250$ mV $-$ (Note 2) Tj from $-40^{\circ}$ to 125 °C        | 4, 3* | 0.5   | 0.55 | 0.62  | V  |

| I <sub>OPPs</sub>      | Setpoint decrease for pin 5 grounded                                                               | 4, 3* |       | 0    |       | %  |

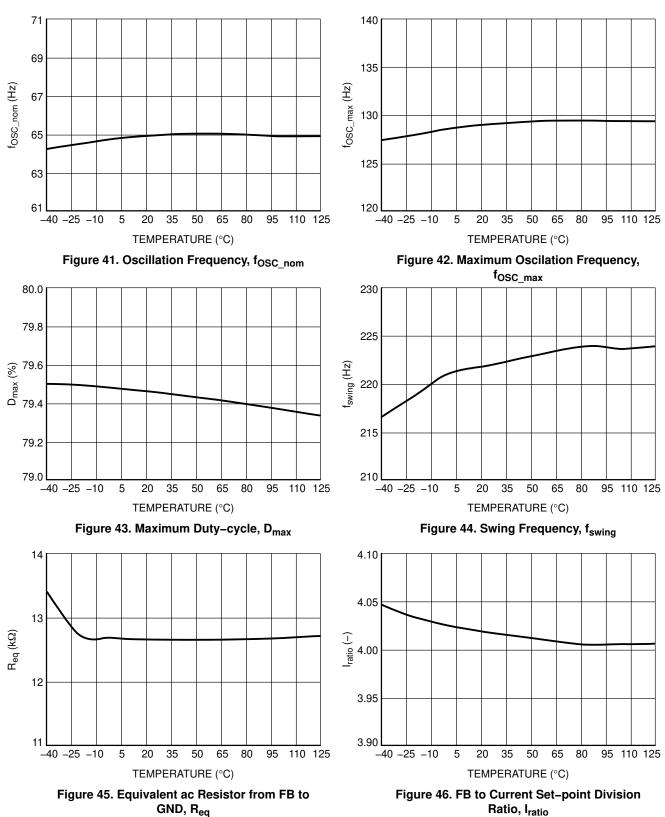

### INTERNAL OSCILLATOR

| f <sub>OSC_nom</sub> | Oscillation frequency, $V_{FB} < V_{FBtrans}$ , pin 5 grounded | -, 4* | 57  | 65  | 71  | kHz |

|----------------------|----------------------------------------------------------------|-------|-----|-----|-----|-----|

| V <sub>FBtrans</sub> | Feedback voltage above which fsw increases                     | 3, 2* |     | 3.2 |     | V   |

| f <sub>OSC_max</sub> | Maximum oscillation frequency for $V_{FB}$ above $V_{FBmax}$   | -     | 115 | 130 | 140 | kHz |

| V <sub>FBmax</sub>   | Feedback voltage above which f <sub>sw</sub> is constant       | 3, 2* | 3.8 | 4   | 4.2 | V   |

| D <sub>max</sub>     | Maximum duty ratio                                             | -     | 76  | 80  | 84  | %   |

| f <sub>jitter</sub>  | Frequency jittering in percentage of fOSC                      | -     |     | ±5  |     | %   |

| f <sub>swing</sub>   | Swing frequency over the whole frequency range                 | -     |     | 240 |     | Hz  |

### **REMOTE SECTION**

| V_REM_on (A/B)              | Remote pin voltage below which is the off–mode deactivated $(V_{REM}\mbox{ going down})\ (V_{CC}$ = 0 V) | 2 | 1    | 1.5  | 2    | V  |

|-----------------------------|----------------------------------------------------------------------------------------------------------|---|------|------|------|----|

| V_ <sub>REM_off</sub> (A/B) | Remote pin voltage above which is the off-mode activated (V <sub>REM</sub> going up)                     | 2 | 7.2  | 8    | 8.8  | V  |

| V_REM_off (C/D)             | Feedback voltage below which the part enters into off-mode                                               | 2 |      | 0.4  |      | V  |

| V_REM_on (C/D)              | Feedback voltage above which is the off-mode deactivated                                                 | 2 | 1.5  | 2    | 2.5  | V  |

| I <sub>FBREM</sub> (C/D)    | Feedback current that lifts the feedback pin upon off-mode exit                                          | 2 |      | 2.4  | 4    | μA |

| REM_Timer                   | Remote timer duration                                                                                    | 2 | 70   | -    | 140  | ms |

| R_SW_REM                    | Internal remote pull down switch resistance                                                              | 2 | 1000 | -    | 3000 | Ω  |

| I_REM_leak                  | Remote input leakage current ( $V_{REM} = 9 V$ ) (Note 1)                                                | 2 | I    | 0.02 | 1    | μA |

FEEDBACK SECTION

| R <sub>up(FB)</sub> | Internal pull-up resistor             | 3, 2* |    | 17 |    | kΩ |

|---------------------|---------------------------------------|-------|----|----|----|----|

| R <sub>eq</sub>     | Equivalent ac resistor from FB to gnd | 3, 2* | 10 | 15 | 20 | kΩ |

2. Guaranteed by design

3. See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV. 4. A  $1-M\Omega$  resistor is connected from pin 4 to the ground for the measurement.

\*C/D version

### **Table 4. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}$ C, for min/max values  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, Max  $T_J = 150^{\circ}$ C,  $V_{CC} = 12$  V unless otherwise noted)

| Symbol                   | Rating                                                                                        | Pin            | Min | Тур  | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------|----------------|-----|------|-----|------|

| FEEDBACK SECT            | TION                                                                                          |                |     |      |     |      |

| I <sub>ratio</sub>       | Pin 3 to current setpoint division ratio                                                      | 3,4,<br>(2,3)* |     | 4    |     | -    |

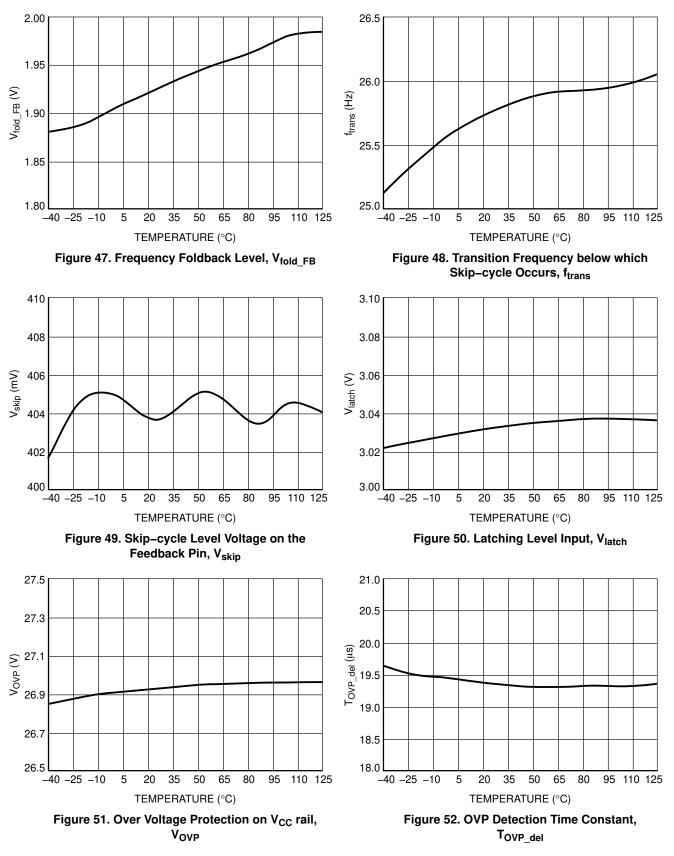

| V <sub>freeze_FB</sub>   | Feedback voltage below which the peak current is frozen                                       | 3, 2*          |     | 1    |     | V    |

| FREQUENCY FO             | LDBACK                                                                                        |                |     | -    |     | -    |

| $V_{fold\_FB}$           | Frequency foldback level on the feedback pin – $\approx\!\!47\%$ of maximum peak current      | 3, 2*          |     | 1.9  |     | V    |

| f <sub>trans</sub>       | Transition frequency below which skip-cycle occurs                                            | -              | 22  | 26   | 30  | kHz  |

| V <sub>fold_end</sub>    | End of frequency foldback feedback level, $f_{sw} = f_{min}$                                  | 3, 2*          |     | 1.5  |     | V    |

| V <sub>skip</sub>        | Skip-cycle level voltage on the feedback pin                                                  | 3, 2*          |     | 400  |     | mV   |

| Skip hysteresis          | Hysteresis on the skip comparator – note 1                                                    | 3, 2*          |     | 30   |     | mV   |

| INTERNAL SLOP            | E COMPENSATION                                                                                |                |     |      |     |      |

| V <sub>ramp</sub>        | Internal ramp level @ 25°C – note 3                                                           | 4, 3*          |     | 2.5  |     | V    |

| R <sub>ramp</sub>        | Internal ramp resistance to CS pin                                                            | 4, 3*          |     | 20   |     | kΩ   |

| PROTECTIONS              |                                                                                               |                |     |      |     |      |

| V <sub>latch</sub>       | Latching level input                                                                          | 5, 4*          | 2.7 | 3    | 3.3 | V    |

| T <sub>latch-blank</sub> | Blanking time after drive turn off                                                            | 5, 4*          |     | 1    |     | μs   |

| T <sub>latch-count</sub> | Number of clock cycles before latch confirmation                                              | -              |     | 4    |     | -    |

| T <sub>latch-del</sub>   | OVP detection time constant                                                                   | 5, 4*          |     | 600  |     | ns   |

| V <sub>OVL</sub>         | Feedback voltage at which an overload is considered – OPP pin is grounded                     | 3, 2*          |     | 3.2  |     | V    |

| V <sub>SC</sub>          | Feedback voltage above which a short-circuit is considered                                    | 3, 2*          | 3.9 | 4.1  | 4.3 | V    |

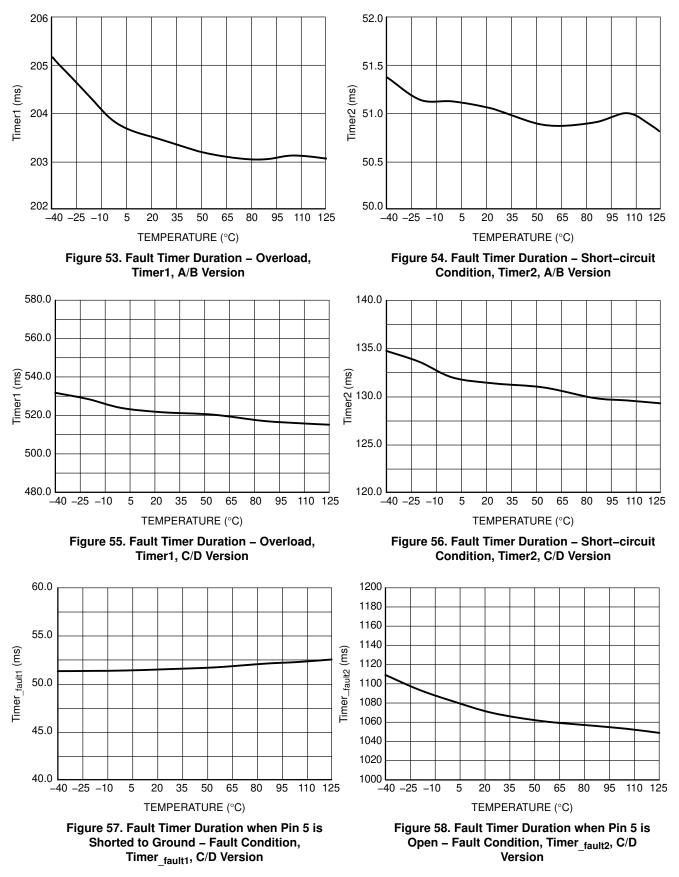

| Timer <sub>1</sub> (A/B) | Fault timer duration when $3.2 < V_{FB} < 4.1 V - overload$                                   | -              | 100 | 200  | 300 | ms   |

| Timer <sub>2</sub> (A/B) | Fault timer duration when $V_{FB} > 4.1 V$ is Timer <sub>1</sub> /4 – short–circuit condition | -              | 25  | 50   | 75  | ms   |

| Timer <sub>1</sub> (C/D) | Fault timer duration for a 22 $k\Omega$ resistor from pin 5 to ground – overload              | 5*             | 350 | 500  | 650 | ms   |

| Timer <sub>2</sub> (C/D) | Fault timer duration when $V_{FB} > 4.1 V$ is Timer <sub>1</sub> /4 – short–circuit condition | 5*             | 88  | 125  | 162 | ms   |

| Timer_fault1 (C/D)       | Timer duration when pin 5 is shorted to ground – fault condition                              | 5*             |     | 50   |     | ms   |

| Timer_fault2 (C/D)       | Timer duration when pin 5 is open – fault condition                                           | 5*             |     | 1000 |     | ms   |

| V <sub>OVP</sub>         | Latched Over voltage protection on the $V_{cc}$ rail                                          | 8              | 26  | 27.5 | 29  | V    |

| T <sub>OVP_del</sub>     | Delay before OVP on $V_{cc}$ confirmation                                                     | 8              |     | 20   | 30  | μs   |

| T <sub>A-rec_timer</sub> | Auto-recovery timer duration                                                                  | _              | 0.7 | -    | -   | s    |

### TEMPERATURE SHUTDOWN

| T <sub>TSD</sub>      | Temperature shutdown T <sub>J</sub> going up | - | 150 | °C |

|-----------------------|----------------------------------------------|---|-----|----|

| T <sub>TSD(HYS)</sub> | Temperature shutdown hysteresis              | - | 30  | °C |

Guaranteed by design

See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV.

4. A 1–M $\Omega$  resistor is connected from pin 4 to the ground for the measurement.

\*C/D version

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **TYPICAL CHARACTERISTICS** 11 16 10 15 9 R<sub>OH</sub> (Ω) 14 8 13 7 12 6 5 11 -40 -25 -10 5 50 80 95 110 125 80 95 110 125 20 35 65 -40 -25 -10 5 20 35 50 65 TEMPERATURE (°C) TEMPERATURE (°C) Figure 29. Source Resistance, RoL Figure 30. Sink Resistance, R<sub>OH</sub> 11.0 14.0 13.5 10.5 (>) <sup>13.0</sup> <sup>46</sup> <sup>12.5</sup> 12.0 10.0 12.0 9.5 11.5 9.0 11.0 50 80 -40 -25 -10 5 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 65 95 110 125 20 TEMPERATURE (°C) TEMPERATURE (°C) Figure 32. DRV Pin Level at $V_{CC}$ Close to $V_{OVP}$ , Figure 31. DRV Pin Level at V<sub>CC</sub> Close to V<sub>CC OFF</sub>, V<sub>DRVIow</sub> **V**DRVhigh 0.85 500 0.83 490 V<sub>fold\_CS</sub> (mV) 0.81 (jimit ) 0.79 0.79 480 0.77 0.75 470 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C)

Figure 33. Maximum Internal Current Set-point, Vlimit

$R_{OL}$  ( $\Omega$ )

VDRV\_low (V)

Figure 34. Default Internal Voltage Set Point for Frequency Foldback, V<sub>fold CS</sub>

#### 250 55 54 245 53 V<sub>freeze\_cs</sub> (mV) T<sub>DEL</sub> (ns) 240 52 51 235 50 230 49 -40 -25 -10 80 -40 -25 -10 5 20 35 50 65 80 95 110 125 5 20 35 50 65 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 35. Internal Peak Current Set-point Figure 36. Propagation Delay from Current Freeze, $V_{freeze\_CS}$ Detection to Gate Off-state, T<sub>DEL</sub> 330 4.3 320 4.2 T<sub>LEB</sub> (ns) T<sub>ss</sub> (ms) 310 4.1 300 4.0 290 3.9 -40 -25 -10 5 35 50 65 80 95 110 125 -40 -25 -10 5 65 80 95 110 125 20 20 35 50 TEMPERATURE (°C) TEMPERATURE (°C) Figure 37. Leading Edge Blanking Duration, Figure 38. Internal Soft-start Duration, T<sub>ss</sub> TLEB 0.60 31.0 30.5 0.58 30.0 0.56 (%) °440 ОРРи 0.54 29.0 0.52 28.5 0.50 28.0 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C)

# **TYPICAL CHARACTERISTICS**

Figure 39. CS Voltage Setpoint for OPP, I<sub>OPPv</sub>

Figure 40. Set-point Decrease for OPP, IOPPO

#### 1.8 2.50 2.45 1.7 I<sub>CC1</sub> (mA) I<sub>CC2</sub> (mA) 2.40 1.6 2.35 1.5 2.30 -40 -25 -10 5 20 35 50 80 65 95 110 125 -40 -25 -10 35 65 80 95 110 125 5 20 50 TEMPERATURE (°C) TEMPERATURE (°C) Figure 59. Internal IC Consumption, I<sub>CC1</sub> Figure 60. Internal IC Consumption, I<sub>CC2</sub> 3.3 1.8 1.7 I<sub>CC3</sub> (mA) I<sub>CC4</sub> (mA) 3.2 1.6 3.1 1.5 -40 -25 -10 80 -40 -25 -10 5 20 35 50 65 80 95 110 125 5 20 35 50 65 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C) Figure 61. Internal IC Consumption, I<sub>CC3</sub> Figure 62. Internal IC Consumption, I<sub>CC4</sub> 0.9 0.8 lcc\_skip (mA) 0.7 0.6 0.5 -40 -25 -10 5 65 80 95 110 125 20 35 50 TEMPERATURE (°C) Figure 63. Internal IC Consumption during Skip Mode, I<sub>CC\_skip</sub>

# **APPLICATION INFORMATION**

### Introduction

The NCP1249 implements a standard current mode architecture where the switch-off event is dictated by the peak current setpoint. This component represents the ideal candidate where low part-count and cost effectiveness are the key parameters, particularly in low-cost ac-dc adapters, open-frame power supplies etc. The NCP1249 brings all the necessary components normally needed in today modern power supply designs, bringing several enhancements such as a non-dissipative OPP, a brown-out protection or peak power excursion for loads exhibiting variations over time. Accounting for the new needs of extremely low standby power requirements, the part includes an automatic X2-capacitor discharge circuitry that prevents the designer from installing power-consuming resistors across the front-end filtering capacitors. The controller is also able to enter a deep sleep mode via its dedicated remote pin.

- High–Voltage start–up: low standby power results cannot be obtained with the classical resistive start–up network. In this part, a high–voltage current–source provides the necessary current at start–up and turns off afterwards.

- Internal Brown–Out protection: a portion of the bulk voltage is internally sensed via the high–voltage pin monitoring (pin 10). When the voltage on this pin is too low, the part stops pulsing. No re–start attempt is made until the controller senses that the voltage is back within its normal range. When the brown–out comparator senses the voltage is acceptable, it sends a general reset to the controller (de–latch occurs) and authorizes to re–start.

- X2-capacitors discharge capability: per IEC-950 standard, the time constant of the front-end filter capacitors and their associated discharge resistors must be less than 1 s. This is to avoid electrical stress when the user unplugs the converter and inadvertently touches the power cord terminals. By providing an automatic means to discharge the X2 capacitors, the NCP1249 prevents the designer from installing the discharge resistors, helping to further save power.

- Off-mode: Off-mode helps to achieve low power consumption of an SMPS during no load conditions. The IC goes into Off-mode when the REM pin is brought higher (A/B, lower C/D) than the internal reference voltage V\_REM\_off. The disable input is pulled low, VCC capacitor is discharged and consumption of all internal blocks is reduced once the off-mode is activated. Off mode is terminated when remote pin voltage crosses V\_REM\_on threshold or application is unplugged from the mains.

- Current-mode operation with internal slope compensation: implementing peak current mode control at a fixed 65-kHz frequency, the NCP1249 offers an internal ramp compensation signal that can

easily by summed up to the sensed current. Sub harmonic oscillations can thus be compensated via the inclusion of a simple resistor in series with the current–sense information.

- Frequency excursion: when the power demand forces the peak current setpoint to reach the internal limit (0.8 V/R<sub>sense</sub> typically), the frequency is authorized to increase to let the converter deliver more power. The frequency excursion stops when 130 kHz are reached.

- Internal OPP: by routing a portion of the negative voltage present during the on-time on the auxiliary winding to the dedicated OPP pin (pin 5), the user has a simple and non-dissipative means to alter the maximum peak current setpoint as the bulk voltage increases. If the pin is grounded, no OPP compensation occurs. If the pin receives a negative voltage down to -250 mV, then a peak current reduction down to 31.3% typical can be achieved. For an improved performance, the maximum voltage excursion on the sense resistor is limited to 0.8 V.

- EMI jittering: an internal low-frequency modulation signal varies the pace at which the oscillator frequency is modulated. This helps spreading out energy in conducted noise analysis. To improve the EMI signature at low power levels, the jittering will not be disabled in frequency foldback mode (light load conditions).

- Frequency foldback capability: a continuous flow of pulses is not compatible with no–load/light–load standby power requirements. To excel in this domain, the controller observes the feedback pin and when it reaches a level of 1.5 V, the oscillator then starts to reduce its switching frequency as the feedback level continues to decrease. When the feedback pin reaches 1 V, the peak current setpoint is internally frozen and the frequency continues to decrease. It can go down to 26 kHz (typical) reached for a feedback level of 450 mV roughly. At this point, if the power continues to drop to 400 mV, the controller enters classical skip–cycle mode.

- Internal soft-start: a soft-start precludes the main power switch from being stressed upon start-up. In this controller, the soft-start is internally fixed to 4 ms. Soft-start is activated when a new startup sequence occurs or during an auto-recovery hiccup.

- Latch input: the NCP1249 includes a latch input (pin 5) that can be used to sense an overvoltage condition on the adapter. If this pin is brought higher than the internal reference voltage V<sub>latch</sub>, then the circuit permanently latches off. The VCC pin is pulled down to a fixed level, keeping the controller latched. The latch reset occurs when the user disconnects the adapter from the mains.

- V<sub>CC</sub> OVP: a latched OVP protects the circuit against V<sub>cc</sub> runaways. The fault must be present at least 20 μs to be validated. Reset occurs when the user disconnects the adapter from the mains.

- Short-circuit protection: short-circuit and especially over-load protections are difficult to implement when a strong leakage inductance between auxiliary and power windings affects the transformer (the aux winding level does not properly collapse in presence of an output short). Here, every time the internal 0.8-V maximum peak current limit is activated (or less when OPP is used), an error flag is asserted and a time period starts, thanks to the programmable timer. The controller can distinguish between two faulty situations:

- There is an extra demand of power, still within the power supply capabilities. In that case, the feedback level is in the vicinity of 3.2–4 V. It corresponds to 0.8 V as the maximum peak current setpoint without OPP. The timer duration is then 100% of its normal value. If the fault disappears, e.g. the peak current setpoint no longer hits the maximum value (e.g. 0.8 V at no OPP), then the timer is reset.

- The output is frankly shorted. The feedback level is thus pushed to its upper stop (4.5 V) and the timer is reduced to 25% of its normal value.

- In either mode, when the fault is validated, all pulses are stopped and the controller enters an auto-recovery burst mode, with a soft-start sequence at the beginning of each cycle. Please note the presence of a divider by two which ignores one hiccup cycle over two (double hiccup type of burst).

- As soon as the fault disappears, the SMPS resumes operation. Please note that some version offers an auto-recovery mode as we just described, some do not and latch off in case of a short circuit.

### Start-up Sequence

The start-up sequence of the NCP1249 involves a high-voltage current source whose input is in pin 10. As this start-up source also performs line sensing for brown-out operation, it is recommended to wire it according to Figure 64 sketch.

Figure 64. The startup resistor can be connected to the input mains for further power dissipation reduction

In this drawing, the high–voltage pin is not connected to the bulk, but to the full–wave rectified ac input. It is important to keep this configuration as the X2 circuitry will also use it.

The first step starts with the calculation of the needed  $V_{CC}$  capacitor which will supply the controller until the auxiliary winding takes over. Experience shows that this time  $t_1$  can be between 5 and 20 ms. Considering that we need at least an energy reservoir for a  $t_1$  time of 10 ms, the  $V_{CC}$  capacitor must be larger than:

$$C_{Vcc} \ge \frac{I_{CC4} \times t_1}{V_{CC\_ON} - V_{CC\_OFF}} \ge \frac{3 \text{ m} \times 10 \text{ m}}{18 - 10} \ge 3.75 \text{ }\mu\text{F}^{(eq. 1)}$$

In this calculation, we adopted the consumption at the highest switching frequency since this is the point at which the IC will work in cold–start case. Let us select a  $4.7 \ \mu F$

capacitor at first and experiments in the laboratory will let us know if we were too optimistic for  $t_1$ . The V<sub>CC</sub> capacitor being known, we can now evaluate the charging time to bring the V<sub>CC</sub> voltage from 0 to the V<sub>CC\_ON</sub> of the IC, 18 V typical. This time sequence can actually be split into two events: 0 V to V<sub>CC\_inhibit</sub> and V<sub>CC\_inhibit</sub> to V<sub>CC\_ON</sub>. This is because the HV source is protected from short–circuits on the VCC pin. In case this happens, the source detects that the V<sub>CC</sub> voltage is less than V<sub>CC\_inhibit</sub> and only delivers I<sub>start1</sub> which is below 1 mA: the die power consumption is maintained to the lowest value. In normal operation, when the voltage has normally reached V<sub>CC\_inhibit</sub>, the source toggles to the full current and charges the V<sub>CC</sub> capacitor at a larger current, I<sub>start2</sub>. The first time duration involves I<sub>start1</sub> and V<sub>CC inhibit</sub>.

$$t_{start1} = \frac{V_{CC\_inhibit} \times C_{Vcc}}{I_{start1}} = \frac{1 \times 4.7 \,\mu}{700 \,\mu} \approx 6.7 \,\text{ms} \tag{eq. 2}$$

The second duration involves V<sub>CC\_ON</sub> and I<sub>start2</sub>:

$$t_{start2} = \frac{\left(V_{CC\_ON} - V_{CC\_inhibit}\right)C_{Vcc}}{I_{start2}} = \frac{(18 - 1) \times 4.7 \,\mu}{10 \,\text{m}} \approx 8 \,\text{ms} \qquad (\text{eq. 3})$$

The total start-up time is thus around 14-15 ms.

Figure 65. The V<sub>CC</sub> at start–up is made of two segments given the short–circuit protection implemented on the HV source

In case the V<sub>CC</sub> capacitor must be increased to cope with no–load standby requirements, there is plenty of margin to keep the total start–up sequence duration below 1 s. Assume the V<sub>CC</sub> capacitor is 100  $\mu$ F, then the total start–up time would be below 400 ms.

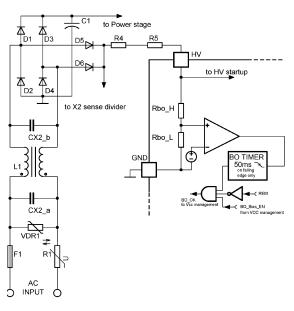

### **Brown-out Circuitry**

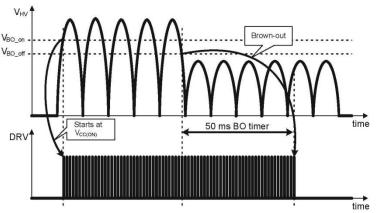

The NCP1249 features, on its HV pin, a true AC line monitoring circuitry – refer to Figure 66. This system includes a minimum start–up threshold and auto–recovery brown–out protection; both of them independent of the input voltage ripple. The thresholds are fixed, but they are designed to fit most of the standard AC–DC converter applications. When the HV pin voltage drops below  $V_{BO_off}$ threshold for more than 50 ms, the brown–out condition is detected and confirmed. Thus the controller stops operation – refer to Figure 67. The V<sub>CC</sub> capacitor is discharged to  $Vcc_{bias}$  level. The HV current source maintains V<sub>CC</sub> at  $Vcc_{bias}$  level until the input voltage is back above  $V_{BO_on}$ . The controller then fully discharges V<sub>CC</sub> capacitor first to restart internal logic. Standard startup attempt is then placed by the controller.

### Figure 66. Simplified Block Diagram of Brown-out Detection Circuitry

The Internal HV BO sensing network is formed by high impedance resistor divider with minimum resistance of 20 M $\Omega$ . This solution reducing power losses during off-mode and thus helps to pass maximum standby power consumption limit. The internal BO network solution provides excellent noise and PCB leakage currents immunity that is hard to achieve when using external resistor divider built from SMT chip resistors.

Figure 67. Brown-out Event Detection

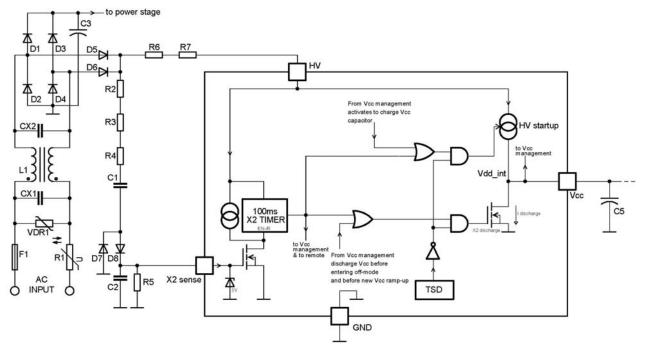

### X2 and $V_{\mbox{CC}}$ Discharge Circuitry

The NCP1249 X2 discharge circuitry uses dedicated pin (X2) together with external charge pump sensing network to detect whether is application plugged into the mains or not. Advantage of this solution is that the internal IC consumption can be reduced to extremely low level by keeping all internal blocks unbiased except simple and low

consuming X2 timer disable circuitry. The internal X2 timer with typical duration of 100 ms is used to overcome unwanted activation of the X2 discharge switch in case of AC line dropout. The internal X2 discharge switch is activated once the X2 timer elapses. The HV startup current source is enabled in the same time thus the discharge path for X2 capacitor exists – refer to Figure 68.

Figure 68. Simplified Block Diagram of X2 and Vcc Capacitor Discharge Circuitry

The time duration of X2 capacitors discharging could be calculated by:

$$t = \frac{U_{C_{X1,2}}}{I_{X2_{dis}}} \cdot C_{X1,2}$$

(eq. 4)

The X2 capacitor discharging process can be interrupted by increasing voltage on X2 pin back above  $V_{th_X2}$ .

The over temperature protection block is active during discharging process to protect controller chip against

unwanted overheat that could occur in case the X2 pin is opened and the high voltage is present on the HV pin (like during open – short pins testing for instance).

The X2 discharge switch is also activated to discharge V<sub>CC</sub> capacitor when entering into fault mode (latch mode, auto-recovery mode or the HV pin voltage drops below  $V_{BO_off}$  threshold for more than 50 ms), off-mode and also before controller V<sub>CC</sub> restart.

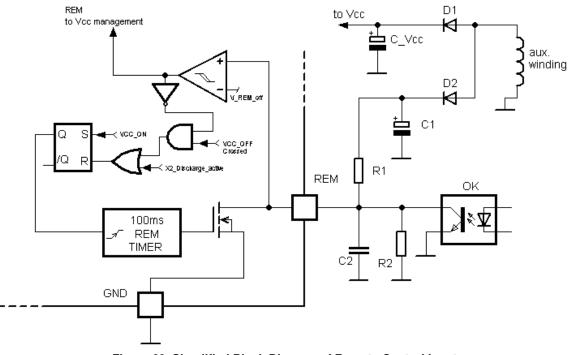

### Remote Input with Remote Timer – A/B Version

The NCP1249A/B features dedicated input (REM pin) that allows user to activate ultra low consumption mode during which the IC consumption is reduced to only very low HV pin leakage current (refer to  $I_{HV_{off}-mode_{-1}}$  and  $I_{HV_{off}-mode_{-2}}$  parameters). The off-mode is activated when

remote pin voltage exceeds  $V_{REM_off}$  threshold (8 V typically). Normal operating mode (i.e. on-mode) is then initiated again when remote input voltage drops back below  $V_{REM_on}$  threshold (1.5 V typically) – refer to Figure 69 for better understanding.

Figure 69. Simplified Block Diagram of Remote Control Input

The off-mode is activated when the remote input is pulled up by auxiliary remote supply (refer to Figure 69.). The normal operation mode is then activated when dedicated opto-coupler pulls the remote input down. There could occur situation, in the application, that the auxiliary remote supply stays charged while the secondary bias has been lost. The application then cannot restart until the auxiliary remote supply capacitor fully discharges. Thus the remote input hosts internal pull down switch and remote timer with duration *REM\_timer*. The controller pulls down remote pin using this circuitry in order to allow correct application restart in case the auxiliary bias capacitor (C1) stays charged while the secondary side is fully discharged already. The remote timer is activated each time the application starts after these events:

- Start after application was plugged into the mains (X2 discharger signal resets remote timer latch in this case)

- Start after application has been un-latched by re-plugging to the mains (X2 discharger signal resets remote timer latch in this case)

- Restart from fault conditions in auto-recovery versions

- Restart after V<sub>CC</sub> has been lost while remote pin was at low state

- Restart after BO event

• Restart after OVP/OTP event

The remote timer helps to assure correct application start or re-start from fault conditions by forcing controller operation for 100 ms typically. However, the secondary controller drives remote pin via opto-coupler during normal operating conditions in order to switch between on-mode and off-mode states. The on-mode is activated for very short time during no-load conditions – just to re-fill primary and secondary capacitors to keep application biased. The remote timer thus cannot be used in this case because it would increase no-load power consumption by forcing application on-mode operation for longer time than it is naturally needed. The remote timer with internal pull down switch is thus not activated in this case (i.e. when application restarts from off-mode operation).

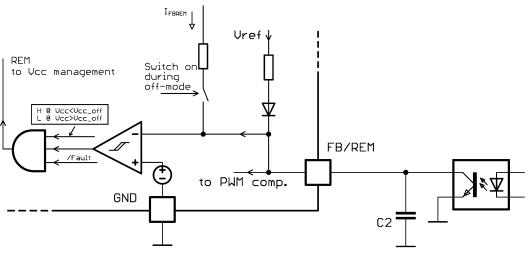

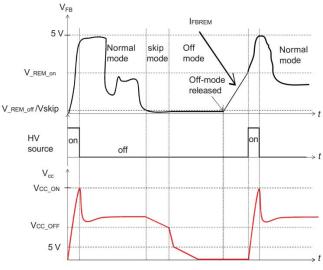

### Feedback/Remote Input – C/D Version

The off mode is activated when the remote pin is low and  $V_{CC_OFF}$  threshold is crossed i.e. when the skip mode takes so long time that  $V_{CC}$  is lost.  $V_{CC}$  capacitor is then discharged by internal consumption. Maximum skip mode duration before the NCP1249 enters off-mode is thus given by value of  $V_{CC}$  capacitor, total consumption during skip mode and voltage level on  $V_{CC}$  capacitor in the time when flyback controller enters skip mode.

Figure 70. Simplified Block Diagram of FB/REM Control Input

To force the controller entering the off mode, the voltage on the feedback pin has to go below the skip cycle level, 400 mV typically. At this moment, all pulses are blocked and the auxiliary V<sub>CC</sub> declines down to 0 V at a pace fixed by the V<sub>CC</sub> capacitor and the controller consumption. When it passes below the V<sub>CC\_OFF</sub> threshold, because the FB pin is still maintained low, the controller does not reactivate the high-voltage start-up source and the circuit remains locked, consuming the least power. The circuit remains off as long as the feedback pin pulled to ground.

When the feedback pin is released, an internal current source ( $I_{FBREM}$ ), pulls the feedback voltage up, above the

inhibition comparator. At this moment, the high-voltage source is good to go and it refuels the V<sub>CC</sub> capacitor until a new start-up sequence occurs. If the feedback pin is driven by a dedicated off-mode controller, shortly after the new start-up sequence, the feedback pin will go down again, initiating another off cycle. The resulting output voltage exhibits a large low-frequency ripple, naturally decreasing the overall consumption budget of the converter. Typical V<sub>CC</sub> and feedback signals while in this mode are drawn in Figure 71.

Figure 71. Combined FB/REM Pin Behavior

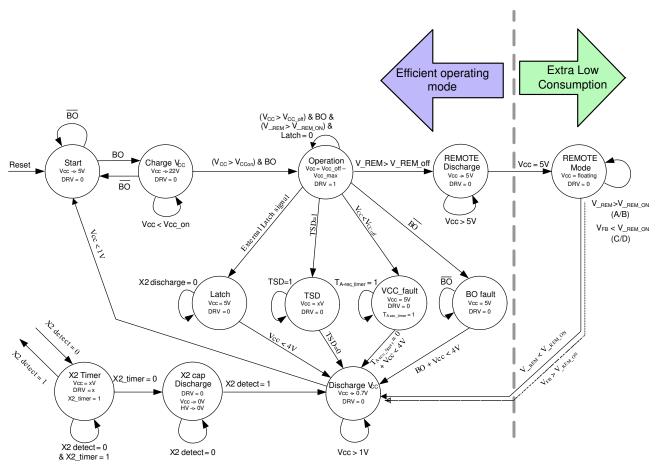

### **Operating Status Diagram**

The NCP1249A/B  $V_{CC}$  management behavior is clearly described in status diagram on Figure 72.

Figure 72. V<sub>CC</sub> Management Status Diagram

### **Internal Over Power Protection**

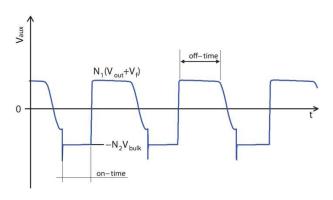

There are several known ways to implement Over Power Protection (OPP), all suffering from particular problems. These problems range from the added consumption burden on the converter or the skip-cycle disturbance brought by the current-sense offset. A way to reduce the power capability at high line is to capitalize on the negative voltage swing present on the auxiliary diode anode. During the turn-on time, this point dips to -NVin, N being the turns ratio between the primary winding and the auxiliary winding. The negative plateau observed on Figure 73 will have amplitude depending on the input voltage. The idea implemented in this chip is to sum a portion of this negative swing with the 0.8 V internal reference level. For instance, if the voltage swings down to -150 mV during the on time, then the internal peak current set point will be fixed to 0.8 - 0.150 =650 mV. The adopted principle appears in Figure 74 and shows how the final peak current set point is constructed.

# Figure 73. The signal obtained on the auxiliary winding swings negative during the on-time

Let's assume we need to reduce the peak current from 2.5 A at low line, to 2 A at high line. This corresponds to a 20% reduction or a set point voltage of 640 mV. To reach this level, then the negative voltage developed on the OPP pin must reach:

$$V_{OPP} = 640 \text{ m} - 800 \text{ m} = -160 \text{ mV}$$

(eq. 5)