Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Fully Integrated Li-Ion Switching Battery Charger with Power Path Management and USB On-The-Go Support

The NCP1851 is a fully programmable single cell Lithium-ion switching battery charger optimized for charging from a USB compliant input supply and AC adaptor power source. The device integrates a synchronous PWM controller, power MOSFETs, and the entire charge cycle monitoring including safety features under software supervision. An optional battery FET can be placed between the system and the battery in order to isolate and supply the system. The NCP1851 junction temperature and battery temperature are monitored during charge cycle, and both current and voltage can be modified accordingly through I<sup>2</sup>C setting. The charger activity and status are reported through a dedicated pin to the system. The input pin is protected against overvoltages.

The NCP1851 also provides USB OTG support by boosting the battery voltage as well as providing overvoltage protected power supply for USB transceiver.

#### **Features**

- 1.6 A Buck Converter with Integrated Pass Devices

- Input Current Limiting to Comply to USB Standard

- Automatic Charge Current for AC Adaptor Charging

- High Accuracy Voltage and Current Regulation

- Input Overvoltage Protection up to +28 V

- Factory Mode

- 500 mA Boosted Supply for USB OTG Peripherals

- Reverse Leakage Protection Prevents Battery Discharge

- Protected USB Transceiver Supply Switch

- Dynamic Power Path with Optional Battery FET

- Battery Temperature Sensing for Safe Operation (JEITA)

- Silicon Temperature Supervision for Optimized Charge Cycle

- Safety Timers

- Flag Output for Charge Status and Interrupts

- I<sup>2</sup>C Control Bus up to 3.4 MHz

- Small Footprint 2.2 x 2.55 mm CSP Package

- These Devices are Pb-Free and are RoHS Compliant

#### **Applications**

- Smart Phone

- Handheld Devices

- Tablets

- PDAs

#### ON Semiconductor®

http://onsemi.com

#### 25 BUMP FLIP-CHIP CASE 499BN

XXXX AYWW

XXXX = Specific Device Code

A = Assembly Location

Y = Year

WW = Work Week

G or ■ = Pb-Free Package

\*Pb-Free indicator, "G" or microdot " ■", may or may not be present.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 30 of this data sheet.

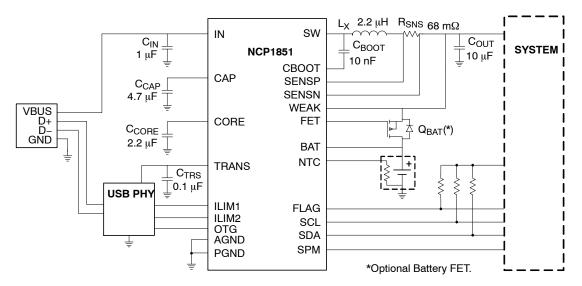

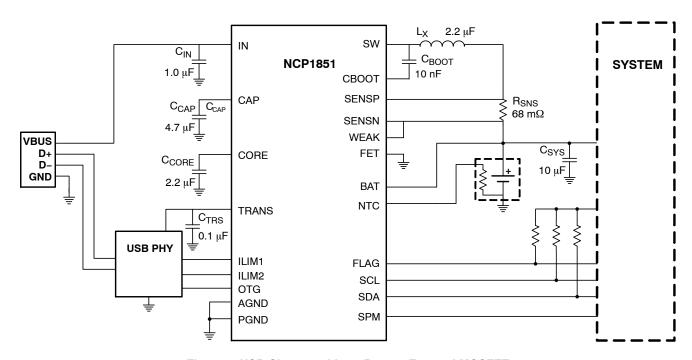

Figure 1. Typical Application Circuit

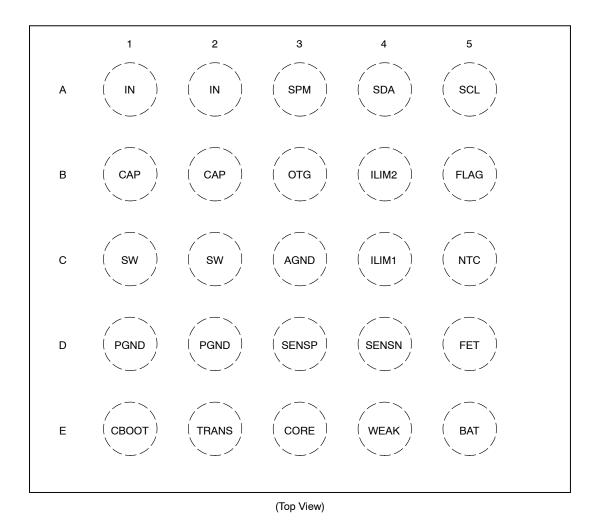

### **PIN CONNECTIONS**

Figure 2. Package Outline CSP

### **Table 1. PIN FUNCTION DESCRIPTION**

| Pin | Name  | Туре                     | Description                                                                                                                                                                                                                                                             |

|-----|-------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | IN    | POWER                    | Battery Charger Input. These two pins must be decoupled by at least 1 μF capacitor and                                                                                                                                                                                  |

| A2  | IN    | POWER                    | connected together.                                                                                                                                                                                                                                                     |

| A3  | SPM   | DIGITAL INPUT            | System Power Monitor input.                                                                                                                                                                                                                                             |

| A4  | SDA   | DIGITAL<br>BIDIRECTIONAL | I <sup>2</sup> C data line                                                                                                                                                                                                                                              |

| A5  | SCL   | DIGITAL INPUT            | I <sup>2</sup> C clock line                                                                                                                                                                                                                                             |

| B1  | CAP   | POWER                    | CAP pin is the intermediate power supply input for all internal circuitry. Bypass with at                                                                                                                                                                               |

| B2  | CAP   | POWER                    | least 4.7 μF capacitor. Must be tied together.                                                                                                                                                                                                                          |

| ВЗ  | OTG   | DIGITAL INPUT            | Enables OTG boost mode. OTG = 0, the boost is powered OFF OTG = 1 turns boost converter ON                                                                                                                                                                              |

| B4  | ILIM2 | DIGITAL INPUT            | Automatic charge current / Input current limiter level selection (can be defeated by I <sup>2</sup> C).                                                                                                                                                                 |

| B5  | FLAG  | OPEN DRAIN<br>OUTPUT     | Charging state active low. This is an open drain pin that can either drive a status LED or connect to interrupt pin of the system.                                                                                                                                      |

| C1  | SW    | ANALOG OUTPUT            | Connection from power MOSFET to the Inductor.                                                                                                                                                                                                                           |

| C2  | SW    | ANALOG OUTPUT            | These pins must be connected together.                                                                                                                                                                                                                                  |

| С3  | AGND  | ANALOG GROUND            | Analog ground / reference. This pin should be connected to the ground plane and must be connected together.                                                                                                                                                             |

| C4  | ILIM1 | DIGITAL INPUT            | Input current limiter level selection (can be defeated by I <sup>2</sup> C).                                                                                                                                                                                            |

| C5  | NTC   | ANALOG INPUT             | Input for the battery NTC (10 K $\Omega$ / B = 3900) or (4.7 K $\Omega$ / B = 3900) If not used, this pin must be tied to GND to configure the NCP1851 and warn that NTC is not used.                                                                                   |

| D1  | PGND  | POWER GND                | Power ground. These pins should be connected to the ground plane and must be connected together.                                                                                                                                                                        |

| D2  | PGND  | POWER GND                | ted together.                                                                                                                                                                                                                                                           |

| D3  | SENSP | ANALOG INPUT             | Current sense input. This pin is the positive current sense input. It should be connected to the R <sub>SENSE</sub> resistor positive terminal.                                                                                                                         |

| D4  | SENSN | ANALOG INPUT             | Current sense input. This pin is the negative current sense input. It should be connected to the R <sub>SENSE</sub> resistor negative terminal. This pin is also voltage sense input of the voltage regulation loop when the FET is present and open.                   |

| D5  | FET   | ANALOG OUTPUT            | Battery FET driver output. When not used, this pin must be directly tied to ground.                                                                                                                                                                                     |

| E1  | СВООТ | ANALOG IN/OUT            | Floating Bootstrap connection. A 10 nF capacitor must be connected between CBOOT and SW.                                                                                                                                                                                |

| E2  | TRANS | ANALOG OUTPUT            | Output supply to USB transceiver. This pin can source a maximum of 50 mA to the external USB PHY or any other IC that needs +5 V USB. This pin is Overvoltage protected and will never be higher than 5.5 V. This pin should be bypassed by a 100 nF ceramic capacitor. |

| E3  | CORE  | ANALOG OUTPUT            | $5$ V reference voltage of the IC. This pin should be bypassed by a 2.2 $\mu\text{F}$ capacitor. No load must be connected to this pin.                                                                                                                                 |

| E4  | WEAK  | ANALOG OUTPUT            | Weak battery charging current source input.                                                                                                                                                                                                                             |

| E5  | BAT   | ANALOG INPUT             | Battery connection                                                                                                                                                                                                                                                      |

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                  | Symbol                             | Value                        | Unit    |

|-----------------------------------------------------------------------------------------|------------------------------------|------------------------------|---------|

| IN (Note 1)                                                                             | V <sub>IN</sub>                    | -0.3 to +28                  | V       |

| CAP (Note 1)                                                                            | $V_{CAP}$                          | -0.3 to +28                  | V       |

| Power balls: SW (Note 1)                                                                | $V_{SW}$                           | -0.3 to +24                  | V       |

| CBOOT (Note 1)                                                                          | V <sub>CBOOT</sub>                 | -0.3 to V <sub>SW</sub> +7.0 | V       |

| Sense/Control balls: SENSP, SENSN, VBAT, FET, TRANS, CORE, NTC, FLAG and WEAK. (Note 1) | V <sub>CTRL</sub>                  | -0.3 to +7.0                 | V       |

| Digital Input: SCL, SDA, SPM, OTG, ILIM1 and ILIM2 (Note 1) Input Voltage Input Current | V <sub>DG</sub><br>I <sub>DG</sub> | -0.3 to +7.0 V<br>20         | V<br>mA |

| Storage Temperature Range                                                               | T <sub>STG</sub>                   | -65 to +150                  | °C      |

| Maximum Junction Temperature (Note 2)                                                   | T <sub>J</sub>                     | -40 to +TSD                  | °C      |

| Moisture Sensitivity (Note 3)                                                           | MSL                                | Level 1                      |         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

**Table 3. OPERATING CONDITIONS**

| Symbol            | Parameter                          | Conditions      | Min | Тур | Max               | Unit |

|-------------------|------------------------------------|-----------------|-----|-----|-------------------|------|

| V <sub>IN</sub>   | Operational Power Supply           |                 | 3   |     | V <sub>INOV</sub> | V    |

| $V_{DG}$          | Digital input voltage level        |                 | 0   |     | 5.5               | V    |

| T <sub>A</sub>    | Ambient Temperature Range          |                 | -40 | 25  | +85               | °C   |

| I <sub>SINK</sub> | FLAG sink current                  |                 |     |     | 10                | mA   |

| C <sub>IN</sub>   | Decoupling input capacitor         |                 |     | 1   |                   | μF   |

| C <sub>CAP</sub>  | Decoupling Switcher capacitor      |                 |     | 4.7 |                   | μF   |

| C <sub>CORE</sub> | Decoupling core supply capacitor   |                 |     | 2.2 |                   | μF   |

| C <sub>OUT</sub>  | Decoupling system capacitor        |                 |     | 10  |                   | μF   |

| L <sub>X</sub>    | Switcher Inductor                  |                 |     | 2.2 |                   | μН   |

| R <sub>SNS</sub>  | Current sense resistor             |                 |     | 68  |                   | mΩ   |

| $R_{\theta JA}$   | Thermal Resistance Junction to Air | (Notes 2 and 4) |     | 60  |                   | °C/W |

| TJ                | Junction Temperature Range         |                 | -40 | 25  | +125              | °C   |

<sup>1.</sup> According to JEDEC standard JESD22-A108.

A thermal shutdown protection avoids irreversible damage on the device due to power dissipation. See Electrical Characteristics.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020.

<sup>4.</sup> The  $R_{\theta JA}$  is dependent on the PCB heat dissipation. Board used to drive this data was a 2s2p JEDEC PCB standard.

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-40^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to  $+125^{\circ}C$  for  $V_{IN}$  between 3.6 V to 7 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 5$  V (Unless otherwise noted).

| Symbol              | Parameter                             |                         | Conditions                                                            | Min      | Тур  | Max  | Unit     |

|---------------------|---------------------------------------|-------------------------|-----------------------------------------------------------------------|----------|------|------|----------|

| INPUT VOI           | LTAGE                                 |                         |                                                                       | •        |      |      |          |

| V <sub>INDET</sub>  | Valid input detection threshold       |                         | V <sub>IN</sub> rising                                                | 3.55     | 3.6  | 3.65 | V        |

|                     |                                       | V <sub>IN</sub> falling |                                                                       | 2.95     | 3.0  | 3.05 | V        |

| V <sub>BUSUV</sub>  | USB under voltage detection           |                         | V <sub>IN</sub> falling                                               | 4.3      | 4.4  | 4.5  | V        |

|                     |                                       |                         | Hysteresis                                                            | 50       | 100  | 150  | mV       |

| V <sub>BUSOV</sub>  | USB over voltage detection            |                         | V <sub>IN</sub> rising                                                | 5.55     | 5.65 | 5.75 | V        |

|                     |                                       |                         | Hysteresis                                                            | 25       | 75   | 125  | mV       |

| V <sub>INOV</sub>   | Valid input high threshold            |                         | V <sub>IN</sub> rising                                                | 7.1      | 7.2  | 7.3  | V        |

|                     |                                       |                         | Hysteresis                                                            | 200      | 300  | 400  | mV       |

| INPUT CUI           | RRENT LIMITING                        |                         |                                                                       | •        |      |      |          |

| I <sub>INLIM</sub>  | Input current limit                   | V <sub>IN</sub> = 5 V   | I <sub>INLIM</sub> set to 100 mA                                      | 70       | 85   | 100  | mA       |

|                     |                                       |                         | I <sub>INLIM</sub> set to 500 mA                                      | 425      | 460  | 500  | mA       |

|                     |                                       |                         | I <sub>INLIM</sub> set to 900 mA                                      | 800      | 850  | 900  | mA       |

|                     |                                       |                         | I <sub>INLIM</sub> set to 1500 mA                                     | 1.4      | 1.45 | 1.5  | Α        |

| INPUT SUF           | PPLY CURRENT                          |                         |                                                                       |          |      |      |          |

| I <sub>Q_SW</sub>   | VBUS supply current                   | No load                 | , Charger active state                                                |          | 15   |      | mA       |

| l <sub>OFF</sub>    | 1                                     | Charger r               | not active, NTC disable                                               |          | 500  |      | μΑ       |

| CHARGER             | DETECTION                             |                         |                                                                       | <u>_</u> |      |      |          |

| V <sub>CHGDET</sub> | Charger detection threshold           | V <sub>IN</sub> –       | V <sub>SENSN</sub> , V <sub>IN</sub> rising                           | 40       | 100  | 150  | mV       |

|                     | voltage                               | V <sub>IN</sub> –       | V <sub>SENSN</sub> , V <sub>IN</sub> falling                          | 20       | 30   | 50   | mV       |

| REVERVE             | BLOCKING CURRENT                      |                         |                                                                       |          |      |      | 1        |

| I <sub>LEAK</sub>   | V <sub>BAT</sub> leakage current      | Battery leakaç<br>SI    | ge, V <sub>BAT</sub> = 4.2 V V <sub>IN</sub> = 0 V,<br>DA = SCL = 0 V |          | 5    |      | μА       |

| R <sub>RBFET</sub>  | Input RBFET On resistance (Q1)        |                         | e state, Measured between<br>nd CAP,V <sub>IN</sub> = 5 V             | -        | 100  | 200  | mΩ       |

| BATTERY             | AND SYSTEM VOLTAGE REGULAT            | ION                     |                                                                       | •        |      |      |          |

| V <sub>CHG</sub>    | Output voltage range                  | Prog                    | grammable by I <sup>2</sup> C                                         | 3.3      |      | 4.5  | V        |

|                     |                                       |                         | Default value                                                         |          | 3.6  |      | V        |

|                     | Voltage regulation accuracy           | Constant v              | roltage mode, T <sub>A</sub> = 25°C                                   | -0.5     |      | 0.5  | %        |

|                     | 1                                     |                         |                                                                       | -1       |      | 1    | %        |

|                     | I2C Programmable granularity          |                         |                                                                       |          | 25   |      | mV       |

| BATTERY             | VOLTAGE THRESHOLD                     |                         |                                                                       | 1        |      | 1    | <u> </u> |

| V <sub>SAFE</sub>   | Safe charge threshold voltage         |                         | V <sub>BAT</sub> rising                                               | 2.1      | 2.15 | 2.2  | V        |

| V <sub>PRE</sub>    | Conditioning charge threshold voltage |                         | V <sub>BAT</sub> rising                                               | 2.75     | 2.8  | 2.85 | ٧        |

| V <sub>FET</sub>    | End of weak charge threshold          | V <sub>BAT</sub> rising | Voltage range                                                         | 3.1      |      | 3.6  | V        |

|                     | voltage                               |                         | Default value                                                         |          | 3.4  |      |          |

|                     |                                       |                         | Accuracy                                                              | -2       |      | 2    | %        |

|                     |                                       |                         | I2C Programmable granularity                                          |          | 100  |      | mV       |

| V <sub>RECHG</sub>  | Recharge threshold voltage            | Polativo t              | I<br>o V <sub>CHG</sub> setting register                              | -        | 97   | 1    | %        |

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} \\ \begin{tabular}{ll} \textbf{Min \& Max Limits apply for $T_A$ between $-40^{\circ}$C to $+85^{\circ}$C and $T_J$ up to $+$ 125^{\circ}$C for $V_{IN}$ between 3.6 V to 7 V (Unless otherwise noted).} \\ \begin{tabular}{ll} \textbf{Typical values are referenced to $T_A = +$ 25^{\circ}$C and $V_{IN} = 5$ V (Unless otherwise noted).} \\ \end{tabular}$

| Symbol                                     | Parameter                                 |                                                                                                                       | Min                                       | Тур                                          | Max  | Unit |          |

|--------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|------|------|----------|

| BATTERY V                                  | VOLTAGE THRESHOLD                         |                                                                                                                       |                                           |                                              |      |      |          |

| V <sub>BUCKOV</sub>                        | Overvoltage threshold voltage             | $V_{BAT}$ rising, relative to $V_{CHG}$ setting register, measured on SENSN or SENSP, $Q_{BAT}$ close or no $Q_{BAT}$ |                                           |                                              | 115  |      | %        |

|                                            |                                           |                                                                                                                       | Q <sub>BAT</sub> open.                    |                                              | 5    |      | V        |

| CHARGE C                                   | CURRENT REGULATION                        |                                                                                                                       |                                           |                                              |      |      |          |

| I <sub>CHG</sub>                           | Charge current range                      | Pro                                                                                                                   | grammable by I <sup>2</sup> C             | 400                                          |      | 1600 | mA       |

|                                            |                                           |                                                                                                                       | Default value                             | 950                                          | 1000 | 1050 | mA       |

|                                            | Charge current accuracy                   |                                                                                                                       |                                           | -50                                          |      | 50   | mA       |

|                                            | I <sup>2</sup> C Programmable granularity |                                                                                                                       |                                           |                                              | 100  |      | mA       |

| I <sub>PRE</sub>                           | Pre-charge current                        |                                                                                                                       | V <sub>BAT</sub> < V <sub>PRE</sub>       | 80                                           | 100  | 120  | mA       |

| I <sub>SAFE</sub>                          | Safe charge current                       |                                                                                                                       | V <sub>BAT</sub> < V <sub>SAFE</sub>      | 8                                            | 10   | 12   | mA       |

| I <sub>WEAK</sub>                          | Weak battery charge current               | BATFET                                                                                                                | IWEAK[1:0] = 01                           | 80                                           | 100  | 120  | mA       |

|                                            |                                           | present,<br>V <sub>SAFE</sub> < V <sub>BAT</sub> <                                                                    | IWEAK[1:0] = 10                           | 180                                          | 200  | 220  | 1        |

|                                            |                                           | V <sub>SAFE</sub> V <sub>BAI</sub> V                                                                                  | IWEAK[1:0] = 11                           | 270                                          | 300  | 330  | 1        |

| CHARGE T                                   | ERMINATION                                |                                                                                                                       |                                           |                                              |      |      | 1        |

| I <sub>EOC</sub>                           | Charge current termination                | V <sub>BAT</sub> ≥ V <sub>RECHG</sub>                                                                                 | Current range                             | 100                                          |      | 275  | mA       |

|                                            |                                           |                                                                                                                       | Default value                             |                                              | 150  |      | -        |

|                                            |                                           |                                                                                                                       | Accuracy, I <sub>EOC</sub> < 200 mA       | -25                                          |      | 25   |          |

|                                            |                                           |                                                                                                                       | I <sup>2</sup> C Programmable granularity |                                              | 25   |      |          |

| FLAG                                       |                                           | 1                                                                                                                     |                                           | 1                                            | 1    | ı    | <u> </u> |

| V <sub>FOL</sub>                           | FLAG output low voltage                   |                                                                                                                       | FLAG = 10 mA                              |                                              |      | 0.5  | V        |

| I <sub>FLEAK</sub>                         | Off-state leakage                         |                                                                                                                       | V <sub>FLAG</sub> = 5 V                   |                                              |      | 1    | μΑ       |

| T <sub>FLGON</sub>                         | Interrupt request pulse duration          |                                                                                                                       | Single event                              | 150                                          | 200  | 250  | μS       |

| DIGITAL IN                                 | PUT (V <sub>DG</sub> )                    |                                                                                                                       |                                           |                                              |      |      | 1        |

| V <sub>IH</sub>                            | High-level input voltage                  |                                                                                                                       |                                           | 1.2                                          |      |      | V        |

| V <sub>IL</sub>                            | Low-level input voltage                   |                                                                                                                       |                                           |                                              |      | 0.4  | V        |

| R <sub>DG</sub>                            | Pull down resistor                        |                                                                                                                       |                                           |                                              | 500  |      | kΩ       |

| I <sub>DLEAKK</sub>                        | Input current                             |                                                                                                                       | V <sub>DG</sub> = 0 V                     | -0.5                                         |      | 0.5  | μΑ       |

| I <sup>2</sup> C                           | ·                                         |                                                                                                                       |                                           |                                              | 1    |      |          |

| V <sub>SYSUV</sub>                         | CAP pin supply voltage                    | I <sup>2</sup> C                                                                                                      | registers available                       | 2.5                                          |      |      | V        |

| V <sub>I</sub> <sup>2</sup> CINT*          | High level at SCL/SCA line                |                                                                                                                       | -                                         | 1.7                                          |      | 5    | V        |

| V <sub>I</sub> <sup>2</sup> CIL            | SCL, SDA low input voltage                |                                                                                                                       |                                           |                                              |      | 0.4  | V        |

| V <sub>I</sub> <sup>2</sup> CIH            | SCL, SDA high input voltage               |                                                                                                                       |                                           | 0.8*<br>V <sub>I</sub> <sup>2</sup> CI<br>NT |      |      | V        |

| V <sub>I</sub> <sup>2</sup> <sub>COL</sub> | SCL, SDA low output voltage               |                                                                                                                       | I <sub>SINK</sub> = 3 mA                  | · · ·                                        |      | 0.3  | V        |

| F <sub>SCL</sub>                           | I <sup>2</sup> C clock frequency          |                                                                                                                       |                                           |                                              |      | 3.4  | MHz      |

|                                            | THERMAL MANAGEMENT                        | 1                                                                                                                     |                                           | 1                                            | 1    |      |          |

| T <sub>SD</sub>                            | Thermal shutdown                          |                                                                                                                       | Rising                                    | 125                                          | 140  | 150  | °C       |

| OD.                                        |                                           |                                                                                                                       | Falling                                   |                                              | 115  |      | °C       |

| T <sub>H2</sub>                            | Hot temp threshold 2                      |                                                                                                                       | Relative to T <sub>SD</sub>               |                                              | -7   |      | °C       |

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} \\ \begin{tabular}{ll} \textbf{Min \& Max Limits apply for $T_A$ between $-40^{\circ}$C to $+85^{\circ}$C and $T_J$ up to $+$ 125^{\circ}$C for $V_{IN}$ between 3.6 V to 7 V (Unless otherwise noted).} \\ \begin{tabular}{ll} \textbf{Typical values are referenced to $T_A = +$ 25^{\circ}$C and $V_{IN} = 5$ V (Unless otherwise noted).} \\ \end{tabular}$

| Symbol              | Parameter                                                     | Conditions                                          | Min   | Тур                          | Max  | Unit |

|---------------------|---------------------------------------------------------------|-----------------------------------------------------|-------|------------------------------|------|------|

| JUNCTION            | THERMAL MANAGEMENT                                            |                                                     |       |                              |      |      |

| T <sub>H1</sub>     | Hot temp threshold 1                                          | Relative to T <sub>SD</sub>                         |       | -11                          |      | °C   |

| T <sub>WARN</sub>   | Thermal warning                                               | Relative to T <sub>SD</sub>                         |       | -15                          |      | °C   |

| BATTERY '           | THERMAL MANAGEMENT                                            |                                                     |       |                              |      |      |

| V <sub>NTCRMV</sub> | Battery removed threshold voltage                             | V <sub>NTC</sub> Rising                             | 2.3   | 2.325                        | 2.35 | V    |

| V <sub>COLD</sub>   | Battery cold temperature corresponding voltage threshold      | Voltage range                                       | 1.425 |                              | 1.95 | V    |

|                     |                                                               | Default                                             | 1.7   | 1.725                        | 1.75 | V    |

| V <sub>HOT</sub>    | Battery hot temperature corresponding voltage threshold       | Voltage range                                       | 375   |                              | 900  | mV   |

|                     |                                                               | Default                                             | 500   | 525                          | 550  | mV   |

|                     | V <sub>COLD</sub> and V <sub>HOT</sub> voltage<br>granularity |                                                     |       | 75                           |      | mV   |

| $V_{WARM}$          | Battery warm temperature corresponding voltage                | BATWARM = 0                                         |       | V <sub>HOT</sub> +<br>0.15   |      | V    |

|                     | threshold                                                     | BATWARM = 1                                         |       | V <sub>HOT</sub> +<br>0.225  |      | ٧    |

| V <sub>CHILLY</sub> | Battery chilly temperature corresponding voltage              | BATCHILLY= 0                                        |       | V <sub>COLD</sub> -<br>0.15  |      | ٧    |

|                     | threshold                                                     | BATCHILLY = 1                                       |       | V <sub>COLD</sub> -<br>0.225 |      | V    |

| V <sub>NTCDIS</sub> | NTC disable corresponding voltage threshold                   | V <sub>NTC</sub> Falling                            | 50    | 75                           | 100  | mV   |

| $V_{REG}$           | Internal voltage reference                                    |                                                     | 2.35  | 2.4                          | 2.45 | V    |

| R <sub>NTCPU</sub>  | Internal resistor pull up                                     |                                                     | 9.8   | 10                           | 10.2 | kΩ   |

| BUCK CON            | NVERTER                                                       |                                                     |       |                              |      |      |

| F <sub>SWCHG</sub>  | Switching Frequency                                           |                                                     | _     | 3                            | -    | MHz  |

|                     | Switching Frequency Accuracy                                  |                                                     | -10   |                              | +10  | %    |

| T <sub>DTYC</sub>   | Max Duty Cycle                                                | Average                                             |       | 99.5                         |      | %    |

| I <sub>PKMAX</sub>  | Maximum peak inductor current                                 |                                                     |       | 2                            |      | Α    |

| R <sub>ONLS</sub>   | Low side Buck MOSFET<br>R <sub>DSON</sub> (Q3)                | Measured between PGND and SW, $V_{\text{IN}}$ = 5 V | -     | 130                          | 260  | mΩ   |

| R <sub>ONHS</sub>   | High side Buck MOSFET<br>R <sub>DSON</sub> (Q2)               | Measured between CAP and SW, $V_{\text{IN}}$ = 5 V  | -     | 100                          | 200  | mΩ   |

| PROTECTE            | ED TRANSCEIVER SUPPLY                                         |                                                     | •     | -                            | -    | -    |

| V <sub>TRANS</sub>  | Voltage on TRANS pin                                          | $V_{IN} \ge 5 V$                                    |       | 5                            | 5.5  | V    |

| I <sub>TRMAX</sub>  | TRANS current capability                                      |                                                     | 50    |                              |      | mA   |

| I <sub>TROCP</sub>  | Short circuit protection                                      |                                                     |       |                              | 150  | mA   |

| TIMING              |                                                               |                                                     | 1     | •                            |      | •    |

| T <sub>WD</sub>     | Watchdog timer                                                |                                                     |       | 32                           |      | s    |

| T <sub>USB</sub>    | USB timer                                                     |                                                     | 1     | 2048                         |      | S    |

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} \\ \begin{tabular}{ll} \textbf{Min \& Max Limits apply for $T_A$ between $-40^{\circ}$C to $+85^{\circ}$C and $T_J$ up to $+$ 125^{\circ}$C for $V_{IN}$ between 3.6 V to 7 V (Unless otherwise noted).} \\ \begin{tabular}{ll} \textbf{Typical values are referenced to $T_A = +$ 25^{\circ}$C and $V_{IN} = 5$ V (Unless otherwise noted).} \\ \end{tabular}$

| Symbol              | Parameter                                                                                                                                              | Conditions                                                    |                                           |      | Тур  | Max  | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|------|------|------|------|

| TIMING              |                                                                                                                                                        |                                                               |                                           |      | •    |      |      |

| T <sub>CHG1</sub>   | Charge timer                                                                                                                                           | Safe-charge or pre-charge or weak-safe or weak- charge state. |                                           |      | 3    |      | h    |

| T <sub>CHG2</sub>   |                                                                                                                                                        | Fu                                                            | II-charge state                           |      | 2    |      | h    |

| T <sub>WU</sub>     | Wake-up timer                                                                                                                                          |                                                               |                                           |      | 64   |      | S    |

| T <sub>ST</sub>     | Charger state timer                                                                                                                                    | Minimum<br>transition time<br>from states to                  | From Weak Charge to Full<br>Charge State  |      | 32   |      | S    |

|                     |                                                                                                                                                        | states.                                                       | All others state                          |      | 16   |      | ms   |

| T <sub>VRCHR</sub>  | Deglitch time for end of charge                                                                                                                        |                                                               | V <sub>BAT</sub> rising                   |      | 15   |      | ms   |

|                     | voltage detection                                                                                                                                      |                                                               | V <sub>BAT</sub> falling                  |      | 127  |      | ms   |

| T <sub>INDET</sub>  | Deglitch time for input voltage detection                                                                                                              |                                                               | V <sub>IN</sub> rising                    |      | 15   |      | ms   |

| T <sub>DGS1</sub>   | Deglitch time for signal<br>crossing I <sub>EOC</sub> , V <sub>PRE</sub> , V <sub>SAFE</sub> ,<br>V <sub>CHGDET</sub> , V <sub>INEXT</sub> thresholds. | Risin                                                         |                                           | 15   |      | ms   |      |

| T <sub>DGS2</sub>   | Deglitch time for signal crossing V <sub>FET</sub> , V <sub>BUSUV</sub> , V <sub>BUSOV</sub> thresholds.                                               | Rising and falling edge                                       |                                           |      | 1    |      | ms   |

| BOOST CO            | ONVERTER AND OTG MODE                                                                                                                                  |                                                               |                                           |      |      |      |      |

| V <sub>IBSTL</sub>  | Boost minimum input                                                                                                                                    | Е                                                             | Boost start-up                            | 3.1  | 3.2  | 3.3  | V    |

|                     | operating range                                                                                                                                        | E                                                             | Boost running                             | 2.9  | 3    | 3.1  | V    |

| V <sub>IBSTH</sub>  | Boost maximum input operating range                                                                                                                    |                                                               |                                           | 4.4  | 4.5  | 4.6  | V    |

| V <sub>OBST</sub>   | Boost Output Voltage                                                                                                                                   | DC value mea                                                  | sured on CAP pin, no load                 | 5.00 | 5.1  | 5.15 | V    |

| V <sub>OBSTAC</sub> | Boost Output Voltage accuracy                                                                                                                          | Measured on CA                                                | AP pin Including line and load regulation | -3   |      | 3    | %    |

| I <sub>BSTMX</sub>  | Output current capability                                                                                                                              |                                                               |                                           | 500  |      |      | mA   |

| F <sub>SWBST</sub>  | Switching Frequency                                                                                                                                    |                                                               |                                           |      | 1.5  |      | MHz  |

|                     | Switching Frequency Accuracy                                                                                                                           |                                                               |                                           | -10  |      | 10   | %    |

| I <sub>BPKM</sub>   | Maximum peak inductor current                                                                                                                          |                                                               |                                           |      | 2    |      | Α    |

| V <sub>OBSTOL</sub> | Boost overload                                                                                                                                         | Boost running, voltage on IN pin                              |                                           | 4.3  | 4.4  | 4.5  | V    |

| T <sub>OBSTOL</sub> |                                                                                                                                                        | Maximum capacitance on IN pin during start-up                 |                                           |      | 10   |      | μF   |

| R <sub>OBSTOL</sub> |                                                                                                                                                        | Minimum load resistance on IN                                 | NCP1851                                   |      | 170  |      | Ω    |

|                     |                                                                                                                                                        | pin during<br>start-up                                        | NCP1851A                                  |      | 50   |      |      |

| V <sub>OBSTOV</sub> | Overvoltage protection                                                                                                                                 |                                                               | V <sub>IN</sub> rising                    | 5.55 | 5.65 | 5.75 | ٧    |

|                     |                                                                                                                                                        |                                                               | Hysteresis                                | 25   | 75   | 125  | mV   |

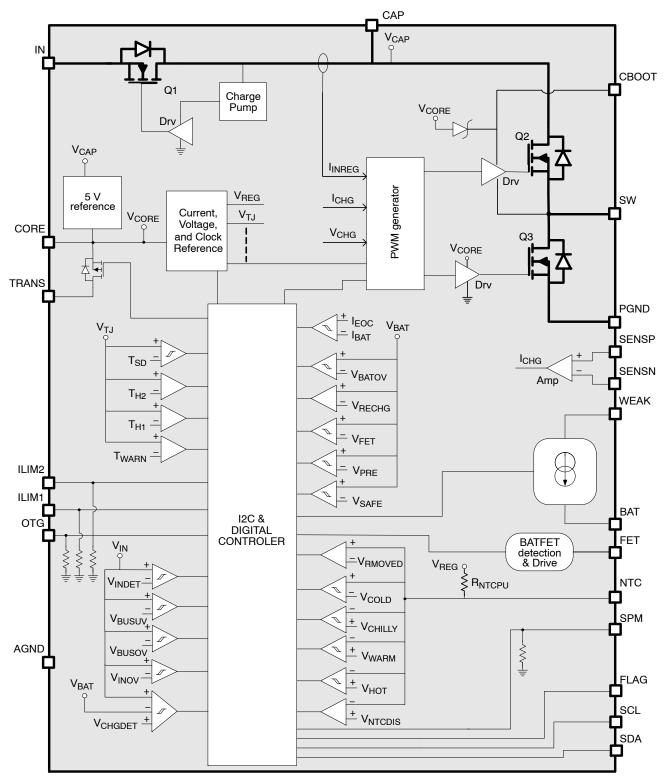

#### **BLOCK DIAGRAM**

Figure 3. Block Diagram

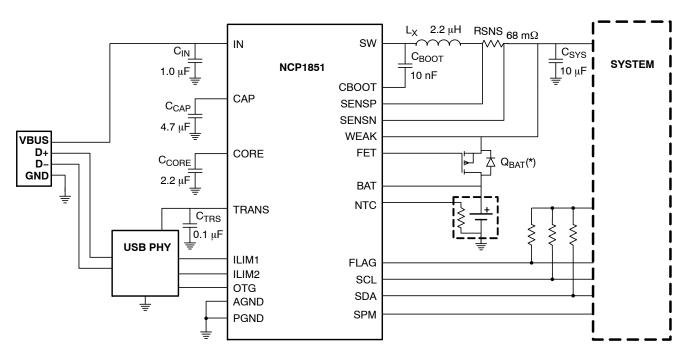

#### **TYPICAL APPLICATION CIRCUITS**

Figure 4. USB Charger with Battery External MOSFET

Figure 5. USB Charger without Battery External MOSFET

### **TYPICAL CHARACTERISTICS**

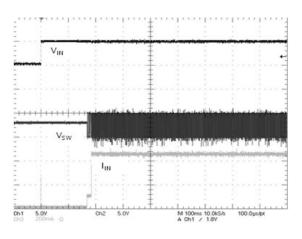

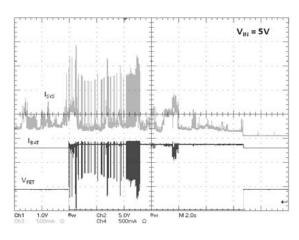

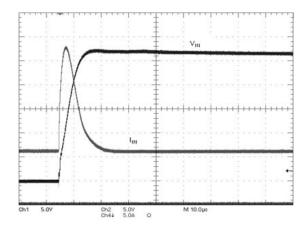

Figure 6. VBUS Insertion

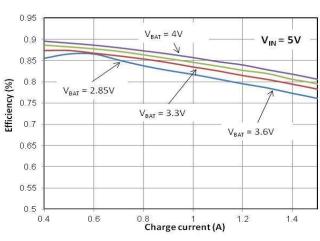

Figure 7. Charger Mode Efficiency

Figure 8. Automatic Charge Current

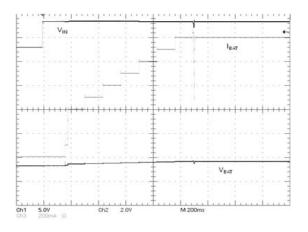

Figure 9. Dynamic Power Path

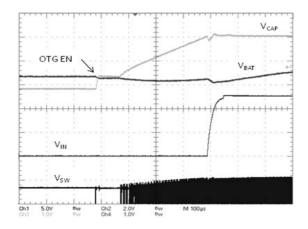

Figure 10. Boost Mode: Power-up

Figure 11. Over Voltage Protection

#### **CHARGE MODE OPERATION**

#### Overview

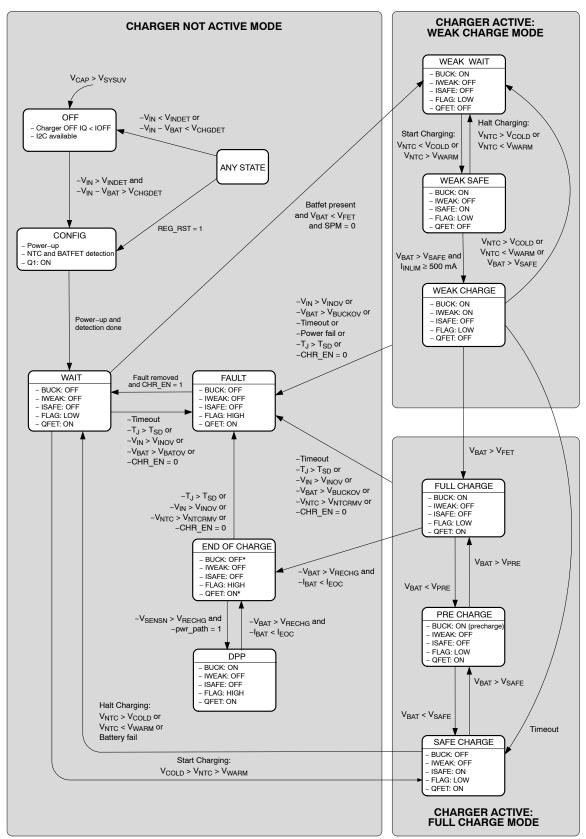

The NCP1851 is a fully programmable single cell Lithium-ion switching battery charger optimized for charging from a USB compliant input supply. The device integrates a synchronous PWM controller; power MOSFETs, and monitoring the entire charge cycle including safety features under software supervision. An optional battery FET can be placed between the system and the battery in order to isolate and supply the system in case of weak battery. The NCP1851 junction temperature and battery temperature are monitored during charge cycle and current and voltage can be modified accordingly through I<sup>2</sup>C setting. The charger activity and status are reported through a dedicated pin to the system. The input pin is protected against overvoltages.

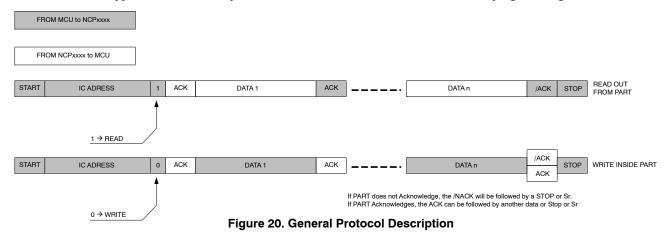

The NCP1851 is fully programmable through  $I^2C$  interface (see Registers Map section for more details). All registers can be programmed by the system controller at any time during the charge process. The charge current ( $I_{CHG}$ ), charge voltage ( $V_{CHG}$ ), and input current ( $I_{INLIM}$ ) are controlled by a dynamic voltage and current scaling for disturbance reduction. Is typically 10  $\mu$ s for each step.

NCP1851 also provides USB OTG support by boosting the battery voltage as well as an over voltage protected power supply for USB transceiver.

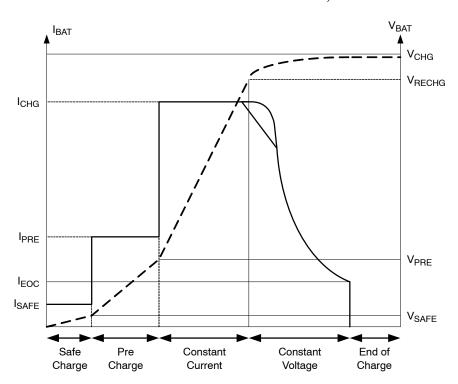

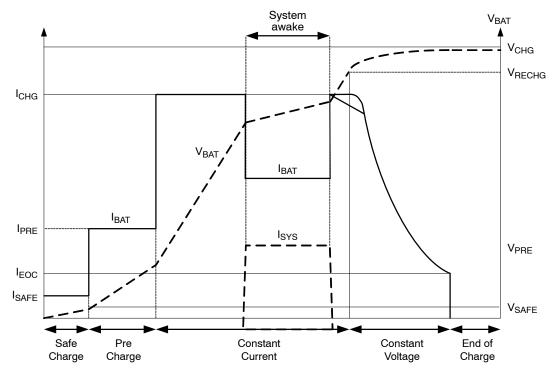

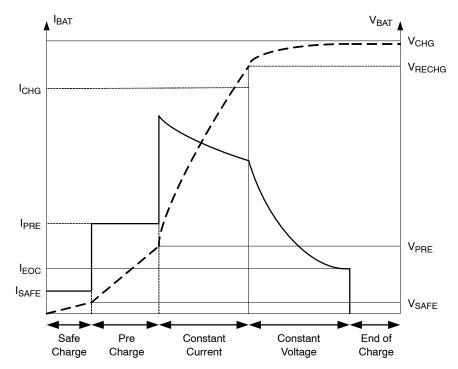

#### **Charge Profile**

In case of application without Q<sub>FET</sub> (see Figure 5), the NCP1851 provides 4 main charging phases as described below. Unexpected behaviour or limitations that can modify the charge sequence are described further (see Charging Process section).

Figure 12. Typical Charging Profile of NCP1851

#### Safe Charge:

With a disconnected battery or completely empty battery, the charge process is in *safe charge* state, the charge current is set to  $I_{SAFE}$  in order to charge up the system's capacitors or the battery. When the battery voltage reaches  $V_{SAFE}$  threshold, the battery enters in pre-conditioning.

#### *Pre Conditioning (pre-charge):*

In preconditioning (pre *charge* state), the DC-DC convertor is enabled and an I<sub>PRE</sub> current is delivered to the battery. This current is much lower than the full charge

current. The battery stays in preconditioning until the  $V_{BAT}$  voltage is lower than  $V_{PRE}$  threshold.

#### Constant Current (full charge):

In the constant current phase (full charge state), the DC–DC convertor is enabled and an  $I_{CHG}$  current is delivered to the load. As battery voltage could be sufficient, the system may be awake and sink an amount of current. In this case the charger output load is composed of the battery and the system. Thus  $I_{CHG}$  current delivered by the NCP1851 is shared between the battery and the system:  $I_{CHG} = I_{SYS} + I_{BAT}$ .

Figure 13. Typical Charging Profile of NCP1851 with System Awake

I<sub>CHG</sub> current is programmable using I2C interface (register IBAT\_SET – bits ICHG[3:0]).

#### Constant Voltage (full charge):

The constant voltage phase is also a part of the *full charge* state. When the battery voltage is close to its maximum ( $V_{CHG}$ ), the charge circuit will transition from a constant current to a constant voltage mode where the charge current will slowly decrease (taper off). The battery is now voltage controlled.  $V_{CHG}$  voltage is programmable using I2C interface (register VBAT SET– bits CTRL VBAT[5:0]).

#### End of Charge:

The charge is completed (end of charge state) when the battery is above the  $V_{RECHG}$  threshold and the charge current below the  $I_{EOC}$  level. The battery is considered fully charged and the battery charge is halted. Charging is resumed in the constant current phase when the battery voltage drops below the  $V_{RECHG}$  threshold.  $I_{EOC}$  current is programmable using I2C interface (register IBAT SET– bits IEOC[2:0]).

#### **Power Stage Control**

NCP1851 provides a fully-integrated 3MHz step-down DC-DC converter for high efficiency. For an optimized charge control, 3 feedback signals controls the PWM duty cycle. These 3 loops are: maximum input current ( $I_{INLIM}$ ), maximum charge current ( $I_{CHG}$ ) and, maximum charge voltage ( $V_{CHG}$ ). The switcher is regulated by the first loop that reaches its corresponding threshold. Typically during charge current phase ( $V_{PRE}$  <  $V_{BAT}$  <  $V_{RECHG}$ ), the measured input current and output voltage are below the programmed limit and asking for more power. But in the same time, the measured output current is at the programmed limit and thus regulates the DC-DC converter.

In order to prevent battery discharge and overvoltage protection, Q1(reverse voltage protection) and Q2(high side N-MOSFET of the DC-DC converter) are mounted in a back-to-back common drain structure while Q3 is the low side N MOSFET of the DC-DC converter. Q2 gate driver circuitry required an external bootstrap capacitor connected between CBOOT pin and SW pin.

An internal current sense monitors and limits the maximum allowable current in the inductor to I<sub>PEAK</sub> value.

#### Charger Detection, Start-up Sequence and System Off

The start-up sequence begins upon an adaptor valid voltage plug in detection:  $V_{IN} > V_{INDET}$  and  $V_{IN} - V_{BAT} > V_{CHGDET}$  (off state).

Then, the internal circuitry is powered up and the presence of NTC and BATFET are reported (register STATUS – bit BATFET and NTC). When the power–up sequence is done, the charge cycle is automatically launched. At any time and any state, the user can hold the charge process and transit to *fault* state by setting CHG\_EN to '0' (register CTRL1) in the I<sup>2</sup>C register. Furthermore, during *fault* state, NTC block can be disabled for power saving (bit NTC EN register CTRL1)

The I2C registers are accessible without valid voltage on  $V_{IN}$  if  $V_{CAP} > V_{SYSUV}$  (i.e. if  $V_{BAT}$  is higher than  $V_{SYSUV}$  + voltage drop across Q2 body diode).

At any time, the user can reset all register stack (register CTRL1 – bit REG RST).

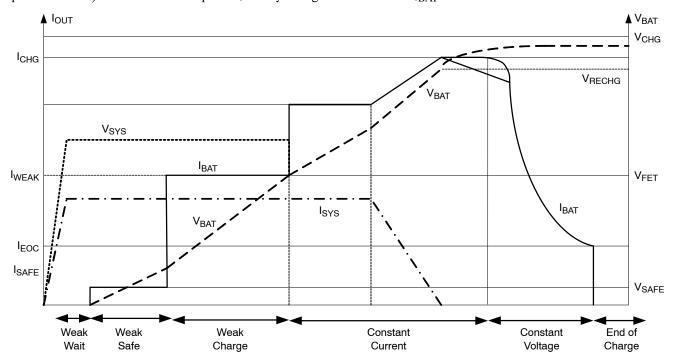

#### **Weak Battery Support**

An optional battery FET ( $Q_{BAT}$ ) can be placed between the application and the battery. In this way, the battery can be isolated from the application and so-called weak battery operation is supported.

Typically, when the battery is fully discharged, also referred to as weak battery, its voltage is not sufficient to supply the application. When applying a charger, the battery first has to be pre-charged to a certain level before operation. During this time; the application is supplied by the DC-DC converter while integrated current sources will pre-charge the battery to the sufficient level before reconnecting.

The pin FET can drive a PMOS switch ( $Q_{BAT}$ ) connected between BAT and WEAK pin. It is controlled by the charger state machine (*Charging process* section). The basic behaviour of the FET pin is that it is always low. Thus the PMOS is conducting, except when the battery is too much discharged at the time a charger is inserted under the condition where the application is not powered on. The FET pin is always low for BAT above the  $V_{FET}$  threshold. Some exceptions exist which are described in the Charging process and *Power Path Management* section. The  $V_{FET}$  threshold is programmable (register MISC\_SET – bit CTRL\_VFET).

#### Batfet detection

The presence of a PMOS ( $Q_{BAT}$ ) at the FET pin is verified by the charging process during its *config* state. To distinguish the two types of applications, in case of no battery FET the pin FET is to be tied to ground. In the *config* state an attempt will be made to raise the FET pin voltage slightly up to a detection threshold. If this is successful it is considered that a battery FET is present. The batfet detection is completed for the whole charge cycle and will be done again upon unplug condition ( $V_{BAT} < V_{INDET}$  or  $V_{IN} - V_{BAT} < V_{CHGDET}$ ) or register reset (register CTRL1– bit REG\_RST). Weak wait

# Weak wait state is entered from wait state (see Charging process section) in case of BATFET present, battery voltage

lower than  $V_{FET}$  and host system in shutdown mode (SPM = 0). The DCDC converter from VIN to SW is enabled and set to  $V_{CHG}$  while the battery FET  $Q_{BAT}$  is opened. The system is now powered by the DC-DC. The internal current source to the battery is disabled. In weak wait state, the state machine verifies if the battery temperature is OK thanks to the NTC sensor. If NTC OK or if NTC is not present (NTC pin tied to 0), this state is left for weak safe state. In case of no battery, the NCP1851 stay in weak wait state (the system is powered by DC-DC).

#### Weak safe

The voltage at  $V_{BAT}$ , is below the  $V_{SAFE}$  threshold. In weak safe state, the battery is charged with a linear current source at a current of  $I_{SAFE}$ . The DC-DC converter is enabled and set to  $V_{CHG}$  while the battery FET  $Q_{BAT}$  is opened. In case the ILIM pin is not made high or the input current limit defeated by  $I^2C$  before timer expiration, the state is left for the safe charge state after a certain amount of time (see Wake up Timer section). Otherwise, the state machine will transition to the weak charge state once the battery is above  $V_{SAFE}$ .

#### Weak charge

The voltage at  $V_{BAT}$ , is above the  $V_{SAFE}$  threshold. The DC-DC converter is enabled and set to  $V_{CHG}$ . The battery is initially charged at a charge current of  $I_{WEAK}$  supplied by a linear current source from WEAK pin (i.e. DC-DC converter) to BAT pin.  $I_{WEAK}$  value is programmable (register MISC\_SET bits IWEAK). The weak charge timer (see *Wake up Timer* section) is no longer running. When the battery is above the  $V_{FET}$  threshold (programmable), the state machine transitions to the *full charge* state thus BATFET  $Q_{BAT}$  is closed.

Figure 14. Weak Charge Profile

#### Weak Charge Exit

In some application cases, the system may not be able to start in *weak charge states* due to current capability limitation or/and configuration of the system. If so, in order to avoid unexpected "drop and retry" sequence of the buck output, the charge state machine allows only 3 system power—up sequences based on SPM pin level: If SPM pin level is toggled 3 times during *weak charge* states, the system goes directly to *safe charge* state and a *full charge mode* sequence is initiated ("Power fail" condition in Charging process section).

#### **Power Path Management**

Power path management can be supported when a battery FET  $(Q_{BAT})$  is placed between the application and the battery. When the battery is fully charged (end of charge state), power path management disconnects the battery from the system by opening  $Q_{BAT}$ , while the DC-DC remains active. This will keep the battery in a fully charged state with the system being supplied from the DC-DC. If a load transient appears exceeding the DC-DC output current and thus causing  $V_{SENSEN}$  to fall below  $V_{RECHG}$ , the FET  $Q_{BAT}$  is instantaneously closed to reconnect the battery in order to provide enough current to the application. The FET  $Q_{BAT}$  remains closed until the end of charge state conditions are reached again. The power path management function is enabled through the  $I^2C$  interface (register CRTL2 bit PWR\_PATH=1).

#### **Safety Timer Description**

The safety timer ensures proper and safe operation during charge process. The set and reset condition of the different safety timer (Watchdog timer, Charge timer, Wakeup timer and USB timer) are detailed below. When a timer expires (condition "timeout" in Charging process section), the charge process is halted.

#### Watchdog Timer

Watchdog timer ensures software remains alive once it has programmed the IC. The watchdog timer is no longer running since I<sup>2</sup>C interface is not available. Upon an I<sup>2</sup>C write, automatically a watchdog timer T<sub>WD</sub> is started. The watchdog timer is running during *charger active* states and *fault* state. Another I<sup>2</sup>C write will reset the watchdog timer. When the watchdog times out, the state machine reverts to *fault* state and reported through I<sup>2</sup>C interface (register CHINT2– bit WDTO). Also used to time out the *fault* state. This timer can be disabled (Register CTRL2 bit WDTO\_DIS).

#### Charge Timer

A charge timer T<sub>CHG</sub> is running that will make that the overall charge to the battery will not exceed a certain amount of energy. The charge timer is running during *charger active* states and halted during *charger not active* states (see *Charging process* section). The timer can also be cleared any time through I<sup>2</sup>C (register CTRL1 – bit TCHG\_RST). The state machine transitions to *fault* state when the timer expires. This timer can be disabled (Register CTRL2 bit CHGTO\_DIS).

#### USB Timer

A USB charge timer  $T_{\rm USB}$  is running in the *charger active* states while halted in the *charger non active* states. The timer keeps running as long as the lowest input current limit remains selected either by ILIM pin or  $I^2C$  (register I\_SET – bit IINLIM and IINLIM\_EN). This will avoid exceeding the maximum allowed USB charge time for un–configured connections. When expiring, the state machine will transition to *fault* state. The timer is cleared in the *off* state or by  $I^2C$  command (register CTRL1 – bit TCHG\_RST).

#### Wake up Timer

Before entering weak charge state, NCP1851 verifies if the input current available is enough to supply both the application and the charge of the battery. A wake-up timer T<sub>WU</sub> verifies if ILIM pin is raised fast enough or application powered up (by monitoring register I\_SET – bit IINLIM and IINLIM\_EN level) after a USB attachment. The wake up timer is running in weak wait state and weak safe state and clears when the input current limit is higher than 100 mA.

#### **Input Current Limitation**

In order to be USB specification compliant, the input current at  $V_{IN}$  is monitored and could be limited to the  $I_{INLIM}$  threshold. The input current limit threshold is selectable through the ILIMx pin. When low, the one unit USB current is selected ( $I_{IN} \leq 100~\text{mA}$ ), where when made high 5 units are selected ( $I_{IN} \leq 500~\text{mA}$ ). In addition, this current limit can be programmed through  $I^2C$  (register MISC\_SET bits IINLIM) therefore defeating the state of the ILIMx pin. In case of non-limited input source, current limit can be disabled (register CTRL2 bit IINLIM\_EN). The current limit is also disabled in case the input voltage exceeds the  $V_{BUSOV}$  threshold.

Figure 15. Typical Charging Profile of NCP1851 with Input Current Limit

#### Input Voltage Based Automatic Charge Current

If the input power source capability is unknown, automatic charge current will automatically increase the charge current step by step until the  $V_{IN}$  drops to  $V_{BUSUV}$ . Upon  $V_{BUSUV}$  being triggered, the charge current  $I_{CHG}$  is immediately reduced by 1 step and stays constant until  $V_{IN}$  drops again to  $V_{BUSUV}$ . The ICHG current is clamped to the  $I^2C$  register value (register IBAT\_SET, bits ICHG). This unique feature is enabled when the pins ILIM1 = 0 and ILIM2 = 1 or through  $I^2C$  register (register CRTL2 bit AICL\_EN).

| ILIM1 | ILIM2 | Input Current Limit      |  |  |  |  |

|-------|-------|--------------------------|--|--|--|--|

| 0     | 0     | 100 mA                   |  |  |  |  |

| 0     | 1     | Automatic Charge Current |  |  |  |  |

| 1     | 0     | 500 mA                   |  |  |  |  |

| 1     | 1     | 900 mA                   |  |  |  |  |

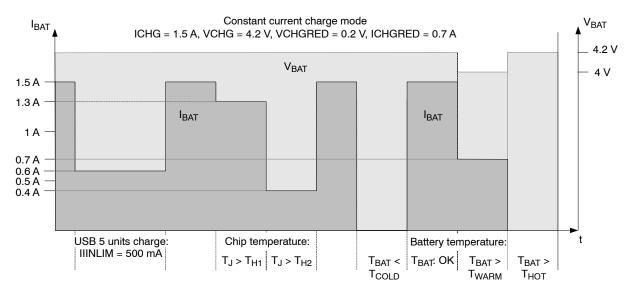

#### **Junction Temperature Management**

During the charge process, NCP1851 monitors the temperature of the chip. If this temperature increases to  $T_{WARN}$ , an interrupt request (described in section Charge status reporting ) is generated and bit TWARN\_SNS is set to '1' (register NTC\_TH\_SENSE). Knowing this, the user is free to halt the charge (register CTRL – bit CHG\_EN) or reduce the charge current (register I\_SET – bits ICHG). When chip temperature reaches  $T_{SD}$  value, the charge process is automatically halt.

Between  $T_{WARN}$  and  $T_{SD}$  threshold, a junction temperature management option is available by setting 1 to  $TJ_WARN_OPT$  bit (register CONTROL). In this case, if the die temperature hits  $T_{M1}$  threshold, an interrupt is generated again but NCP1851 will also reduce the charge current  $I_{CHG}$  by two steps or 200 mA. This should in most cases stabilize the die temperature because the power dissipation will be reduced by approximately 50 mW. If the die temperature increases further to hit  $T_{M2}$ , an interrupt is generated and the charge current is reduced to its lowest level or 400 mA. The initial charge current will be re–established when the die temperature falls below the  $T_{WARN}$  again.

If bit TJ\_WARN\_OPT = 0 (register CTRL1), the charge current is not automatically reduced, no current changes actions are taken by the chip until T<sub>SD</sub>.

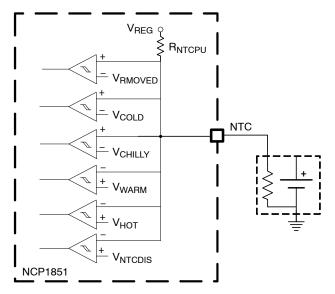

#### **Battery Temperature Management**

For battery safety, charging is not allowed for too cold or too hot batteries. The battery temperature is monitored through a negative temperature coefficient (NTC) thermistor mounted in the battery pack or on the phone PCB close to the battery pack. In some cases the NTC is handled by the platform and will not be connected to the charger IC.

NCP1851 provides a NTC pin for monitoring an external NTC thermistor. NTC pin is connected to an internal voltage  $V_{REG}$  through pull-up resistor ( $R_{NTCPU}$ ). By connecting a NTC thermistor between NTC pin and GND, internal comparators can monitors voltage variation and provides temperature information to the state machine.

Figure 16. NTC Monitoring Circuit

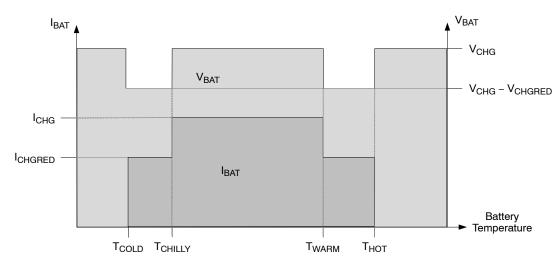

Four thresholds 'cold', 'chilly', 'warm' and 'hot' are provided those are all programmable. The corresponding voltage levels of these thresholds are respectively V<sub>COLD</sub>, V<sub>CHILLY</sub>, V<sub>WARM</sub> and V<sub>HOT</sub>. Interrupts (describe in section *Charge status reporting*) are generated when crossing either threshold. Two charging schemes are available through I<sup>2</sup>C using these four thresholds. The default scheme (bit JEITA\_OPT = 0 in CTRL1 register) will halt charging outside the cold-warm window. A second extended

temperature scheme (bit JEITA OPT = 1 in CTRL1 register) will halt charging outside the cold-hot window while reducing the charge voltage and current in the warm-hot and chilly-cold window with VCHGRED (register NTC SET1) and ICHGRED (register NTC SET1). The state machine (see Charging process section), takes the chilly-warm respectively the cold-hot window for not out of temp detection. This boils down into selecting between ICHGRED or no current for the warm-hot and cold-chilly window. In both cases, the charge voltage and charge current can be reprogrammed while in the warm-hot and cold-chilly window. Together with the programmable thresholds this effectively allows the use of different charging schemes at different temperatures as well as to accommodate to different NTC characteristics. Cold, chilly, warm and hot threshold can be set respectively with bits BATCOLD, BATCHILLY, BATWARM and BATHOT of NTC SET2 register.

In addition to the above, comparators monitor the NTC presence. When the NTC is removed ( $V_{\rm NTC} > V_{\rm NTCRMV}$ ), no more charge current is supplied to the battery and an interrupt is generated (describe in section Charge status reporting). This functionality can be disabled through programming (bit NTC\_EN in register CTRL1). When the NTC is not used in the application the NTC pin can be tied to ground ( $V_{\rm NTC} < V_{\rm NTCDIS}$ ) which will disable the battery temperature monitoring function.

Figure 17. Charge Voltage and Current versus Battery Temperature (JEITA OPT)

#### **Use Case of Current and Voltage Charge**

If configured, charge current and voltage is automatically modified by the input current limit, chip temperature and battery temperature.

Figure 18. Use Case Charge Voltage and Current

### Regulated Power Supply (Trans pin)

NCP1851 has embedded a linear voltage regulator ( $V_{TRANS}$ ) able to supply up to  $I_{TRMAX}$  to external loads. This output can be used to power USB transceiver. Trans pin

is enabled if a  $V_{BUS}$  valid is connected on input pin ( $V_{BUSUV}$  <  $V_{IN}$  <  $V_{BUSOV}$ ) and can be disabled through  $I^2C$  (bit TRANS\_EN\_REG register CTRL2).

#### **Charge Status Reporting**

#### FLAG pin

FLAG pin is to used to report charge status to the system processor and for interruption request.

During *charger active* states and *wait* state, the pin FLAG is low in order to indicate that the charge of the battery is in progress. When charge is completed or disabled or a fault occurs, the FLAG pin is high as the charge is halted.

#### STATUS and CONTROL Registers

The status register contains the current charge state, NTC and BATFET connection as well as fault and status interrupt (bits FAULTINT and STATINT in register STATUS). The charge state (bits STATE in register STATUS) is updated on the fly and corresponds to the charging state describe in Charging process section. An interruption (see description below) is generated upon a state change. In the *config* state, hardware detection is performed on BAFTET and NTC pins. From wait state, their statuses are available (bit BATFET and NTC in register STATUS). STATINT bit is set to 1 if an interruption appears on STAT\_INT register (see description below). FAULTINT bit is set to 1 if an interruption appears on registers CH1 INT, CH1 INT or BST INT. Thanks to this register, the system controller knows the chip status with only one I<sup>2</sup>C read operation. If a fault appears or a status change (STATINT bits and FAULTINT), the controller can read corresponding registers for more details.

#### **Interruption**

Upon a state or status change, the system controller is informed by sensing FLAG pin. A T<sub>FLAGON</sub> pulse is generated on this pin in order to signalize an event. The level of this pulse depends on the state of the charger (see *Charging process* section):

- When charger in is charger active states and wait state the FLAG is low and consequently the pulse level on FLAG pin is high.

- In the others states, the pulse level is low as the FLAG stable level is high.

Charge state transition even and all bits of register STAT\_INT, CH1\_INT, CH2\_INT, BST\_INT generate an interrupt request on FLAG pin and can be masked with the corresponding mask bits in registers STAT\_MSK, CH1\_MSK, CH2\_MSK and BST\_MSK. All interrupt signals can be masked with the global interrupt mask bit (bit INT\_MASK register CTRL1). All these bits are read to clear. The register map (see REGISTERS MAP section) indicated the active transition of each bits (column "TYPE" in see REGISTERS MAP section).

If more than 1 interrupt appears, only 1 pulse is generated while interrupt registers (STAT\_INT, CH1\_INT, CH2\_INT, BST\_INT) will not fully clear.

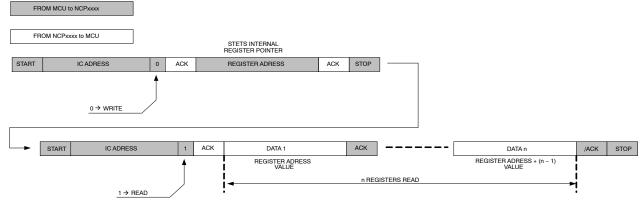

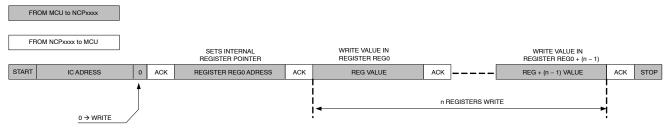

#### Sense and Status Registers