# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **NOCAP<sup>™</sup>** Advanced Stereo **Headphone Amplifier**

NCP2811 is a dual audio power amplifier designed for portable communication device applications such as mobile phones. This part is capable of delivering 27 mW of continuous average power into a 16  $\Omega$  load from a 2.7 V power supply with a THD+N of 1%.

Based on the power supply delivered to the device, an internal power management block generates a symmetrical positive and negative voltage. Thus, the internal amplifiers provide outputs referenced to Ground. In this True Ground configuration, the two external heavy coupling capacitors can be removed. It offers significant space and cost savings compared to a typical stereo application.

NCP2811 is available with an external adjustable gain (version A), or with an internal gain of -1.5 V/V (version B). It reaches a superior -100 dB PSRR and noise floor. Thus, it offers high fidelity audio sound, as well as a direct connection to the battery. It contains circuitry to prevent from "Pop & Click" noise that would otherwise occur during turn-on and turn-off transitions. The device is available in 12 bump CSP package (2 x 1.5 mm) which help to save space on the board. It is also available in WQFN12 and TSSOP-14 packages.

#### **Features**

- True Ground Configuration Output Eliminates DC-Blocking Capacitors:

- Save Board Area

- Save Component Cost

- No Low-Frequency Response Attenuation

- High PSRR (-100 dB): Direct Connection to the Battery

- "Pop and Click" Noise Protection Circuitry

- Internal Gain (-1.5 V/V) or External Adjustable Gain

- Ultra Low Current Shutdown Mode

- 2.7 V 5.0 V Operation

- Thermal Overload Protection Circuitry

- CSP 2 x 1.5 mm

- WQFN12 3 x 3 mm

- TSSOP-14

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- · Headset Audio Amplifier for

- Cellular Phones

- MP3 Player

- Personal Digital Assistant and Portable Media Player

- Portable Devices

## **ON Semiconductor®**

http://onsemi.com

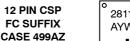

#### MARKING DIAGRAMS

2811xz AYWW

= A for NCP2811A х

12 PIN CSP

FC SUFFIX

- = B for NCP2811B

- = C for backside laminate z

- = Assembly Location Α

- = Year Y

- WW = Work Week

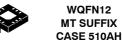

WQFN12

= Pb-Free Package

2811x ALYW.

- = A for NCP2811A х

- = B for NCP2811B

- = Assembly Location

- L = Wafer Lot

- = Year Υ

- W = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

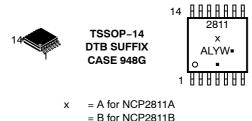

- = Assembly Location L

- = Wafer Lot γ = Year

- W = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 12 of this data sheet.

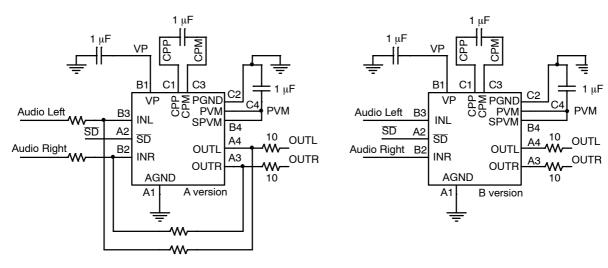

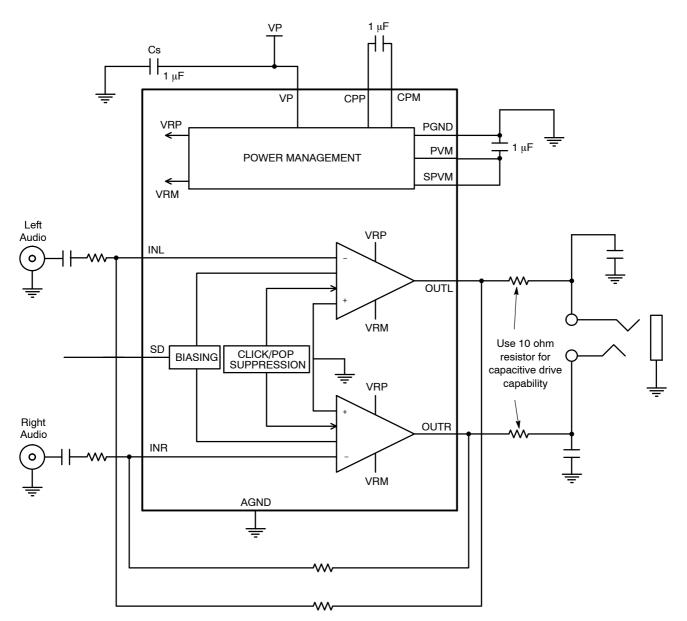

#### Figure 1. Application Schematics

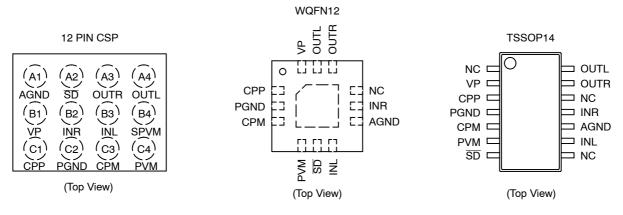

Figure 2. Pin Configurations

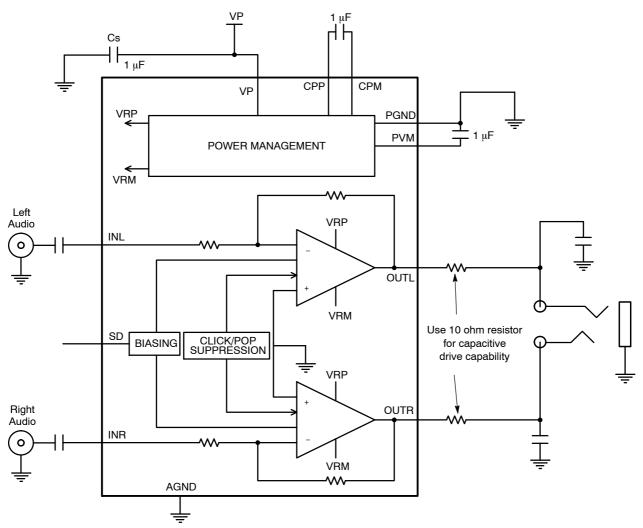

Figure 3. Typical Application Schematic version A

| Table 1. | PIN | FUNCTION | DESCRIPTION |

|----------|-----|----------|-------------|

|          |     |          |             |

| PIN<br>CSP | PIN<br>TQFN | PIN TS-<br>SOP | PIN<br>NAME | TYPE             | DESCRIPTION                                                                                                    |

|------------|-------------|----------------|-------------|------------------|----------------------------------------------------------------------------------------------------------------|

| A1         | 7           | 10             | AGND        | GROUND           | Analog ground. Connect to ground reference                                                                     |

| A2         | 5           | 7              | SD          | INPUT            | Enable activation                                                                                              |

| A3         | 10          | 13             | OUTR        | OUTPUT           | Right audio channel output signal                                                                              |

| A4         | 11          | 14             | OUTL        | OUTPUT           | Left audio channel output signal                                                                               |

| B1         | 12          | 2              | VP          | POWER            | Positive supply voltage. It can be connected for example to a Lithium/Ion battery                              |

| B2         | 8           | 11             | INR         | INPUT            | Right input of the first audio source                                                                          |

| B3         | 6           | 9              | INL         | INPUT            | Left input of the first audio source                                                                           |

| B4         | -           | -              | SPVM        | POWER            | Amplifier negative power supply voltage. Connect to PVM                                                        |

| C1         | 1           | 3              | CPP         | INPUT/<br>OUTPUT | Charge pump flying capacitor positive terminal. A 1 $\mu F$ ceramic filtering capacitor to CPM is needed       |

| C2         | 2           | 4              | PGND        | GROUND           | Power ground, connect to ground reference                                                                      |

| C3         | 3           | 5              | СРМ         | INPUT            | Charge pump flying capacitor negative terminal. A 1 $\mu\text{F}$ ceramic filtering capacitor to CPP is needed |

| C4         | 4           | 6              | PVM         | OUTPUT           | Charge pump output. A 1 $\mu\text{F}$ ceramic filtering capacitor to ground is needed                          |

#### **Table 2. MAXIMUM RATINGS**

| Rating                                                                          | Symbol            | Value                                                     | Unit |

|---------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|------|

| AVIN, PVIN Pins: Power Supply Voltage (Note 2)                                  | V <sub>P</sub>    | – 0.3 to + 6.0                                            | V    |

| INL, INR Pins: Input (Note 2)<br>A version<br>B version                         | V <sub>IN</sub>   | −V <sub>P</sub> − 0.3 to V <sub>P</sub> + 0.3<br>−2 to +2 | V    |

| SD Pin: Input (Note 2)                                                          | V <sub>YY</sub>   | –0.3 to V <sub>P</sub> + 0.3                              | V    |

| Human Body Model (HBM) ESD Rating are (Note 3)                                  | ESD HBM           | 2000                                                      | V    |

| Machine Model (MM) ESD Rating are (Note 3)                                      | ESD MM            | 200                                                       | V    |

| CSP 1.5 x 2.0 mm package (Notes 6 and 7)<br>Thermal Resistance Junction to Case | R <sub>θJC</sub>  | (Note 7)                                                  | °C/W |

| Operating Ambient Temperature Range                                             | T <sub>A</sub>    | -40 to + 85                                               | °C   |

| Operating Junction Temperature Range                                            | Т <sub>Ј</sub>    | -40 to + 125                                              | °C   |

| Maximum Junction Temperature (Note 6)                                           | T <sub>JMAX</sub> | + 150                                                     | °C   |

| Storage Temperature Range                                                       | T <sub>STG</sub>  | -65 to + 150                                              | °C   |

| Moisture Sensitivity (Note 5)                                                   | MSL               | Level 1                                                   |      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Notes:

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = 25°C.

- 2. According to JEDEC standard JESD22-A108B.

- 3. This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114 for all pins. Machine Model (MM) ±200 V per JEDEC standard: JESD22-A115 for all pins.

- 4. Latch up Current Maximum Rating: ±100 mA per JEDEC standard: JESD22-AT15 for all pins.

4. Latch up Current Maximum Rating: ±100 mA per JEDEC standard: JESD78 class II.

5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

6. The thermal shutdown set to 150°C (typical) avoids irreversible damage on the device due to power dissipation.

7. The R<sub>JA</sub> is highly dependent of the PCB Heatsink area. For example, R<sub>JA</sub> can equal 195°C/W with 50 mm<sup>2</sup> total area and also 135°C/W with 50 mm<sup>2</sup>. The bumps have the same thermal resistance and all need to be connected to optimize the power dissipation.

$$\mathsf{R}_{\theta \mathsf{C}\mathsf{A}} = \frac{125 - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{D}}} - \mathsf{R}_{\theta \mathsf{J}\mathsf{C}}$$

| Symbol               | Parameter                                  | Conditions                                                                                                                                                                                                                   | Min   | Тур                   | Max   | Unit             |

|----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|------------------|

| VP                   | Operational Power Supply                   |                                                                                                                                                                                                                              | 2.7   |                       | 5.0   | V                |

| I <sub>DD</sub>      | Supply quiescent current                   | Both channels enabled                                                                                                                                                                                                        |       | 6.0                   |       | mA               |

| I <sub>SD</sub>      | Shutdown current                           | V <sub>P</sub> = 2.7 V to 5.0 V                                                                                                                                                                                              |       |                       | 1     | μA               |

| V <sub>OS</sub>      | Output offset voltage                      | V <sub>P</sub> = 2.7 V to 5.0 V                                                                                                                                                                                              |       | ±1                    |       | mV               |

| VIH                  | High-Level input voltage SD pin            |                                                                                                                                                                                                                              | 1.2   |                       |       | V                |

| V <sub>IL</sub>      | Low-Level input voltage SD pin             |                                                                                                                                                                                                                              |       |                       | 0.4   | V                |

| R <sub>SD</sub>      | SD pin pull-down impedance                 |                                                                                                                                                                                                                              |       | 190                   |       | KΩ               |

| T <sub>WU</sub>      | Turning on time                            |                                                                                                                                                                                                                              |       | 1                     |       | ms               |

| T <sub>SD</sub>      | Thermal shutdown temperature               |                                                                                                                                                                                                                              |       | 160                   |       | °C               |

| V <sub>LP</sub>      | Max output swing (peak value)              | $V_{P} = 2.9 \text{ V to } 5.0 \text{ V}$<br>Headset $\geq 16 \Omega$<br>THD+N = 1%                                                                                                                                          | 1     |                       |       | V <sub>RMS</sub> |

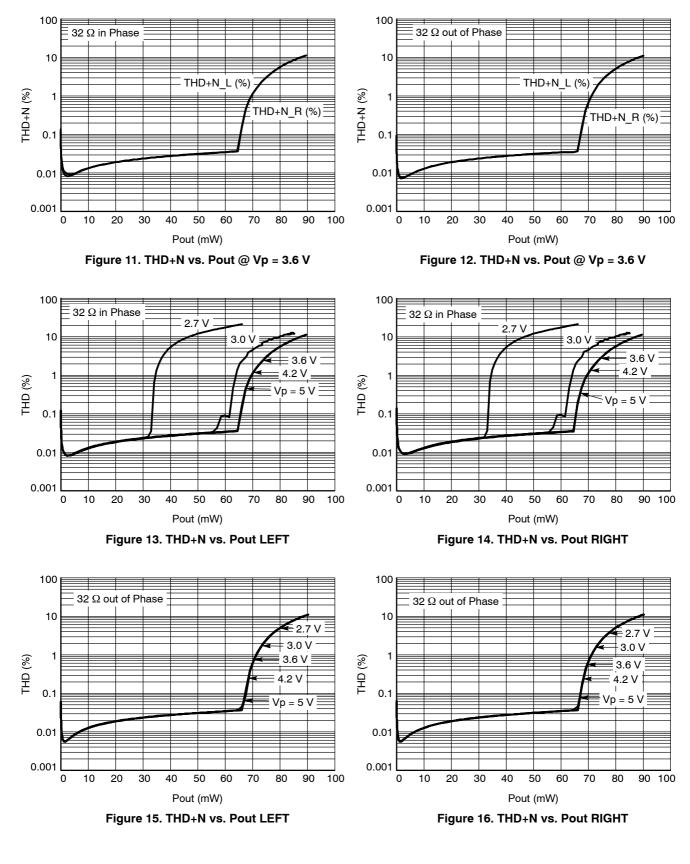

| P <sub>O</sub>       | Max output power (output in phase)         | $V_{P} = 2.7V, THD+N = 1\%$<br>Headset = 16 $\Omega$<br>$V_{P} = 2.7V, THD+N = 1\%$<br>Headset = 32 $\Omega$                                                                                                                 |       | 27<br>37              |       | mW               |

|                      |                                            | $V_{P} = 3.6V, THD+N = 1\%$<br>Headset = 16 $\Omega$<br>$V_{P} = 3.6V, THD+N = 1\%$<br>Headset = 32 $\Omega$<br>$V_{P} = 5.0V, THD+N = 1\%$<br>Headset = 16 $\Omega$<br>$V_{P} = 5.0V, THD+N = 1\%$<br>Headset = 32 $\Omega$ |       | 90<br>64<br>110<br>64 |       |                  |

|                      | Crosstalk (Note 8)                         | Headset $\geq$ 16 $\Omega$                                                                                                                                                                                                   |       | -80                   | -60   | dB               |

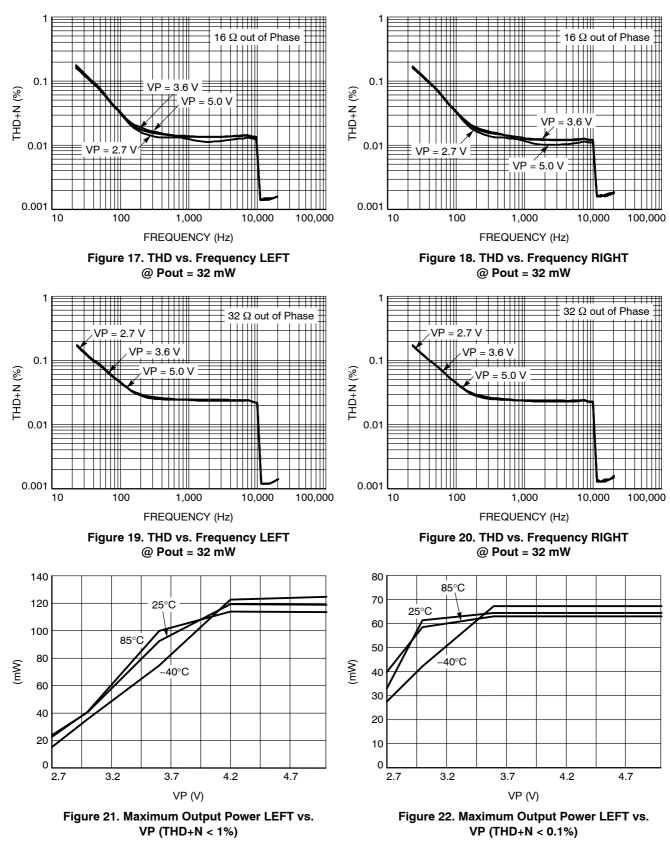

| PSRR                 | Power supply rejection ratio (Note 8)      | $V_P$ = 2.7 V to 5.0 V<br>Input shorted to ground<br>F = 217 Hz<br>F = 1 kHz                                                                                                                                                 |       | -106<br>-95           |       | dB               |

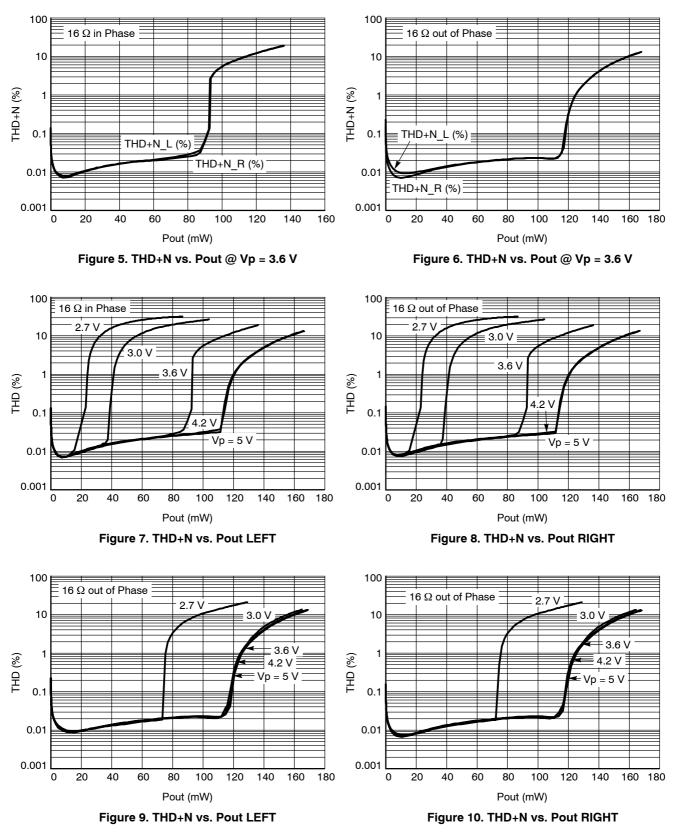

| THD+N                | Total harmonic distortion + noise (Note 8) | Headset = 16 Ω<br>P <sub>OUT</sub> = 25 mW                                                                                                                                                                                   |       | 0.01                  |       | %                |

| V <sub>N</sub>       | Output noise voltage (Note 8)              | A-Weighting filter                                                                                                                                                                                                           |       | 7                     |       | μV <sub>RM</sub> |

| Z <sub>IN</sub>      | Input impedance                            | B version only                                                                                                                                                                                                               |       | 20                    |       | KΩ               |

| Z <sub>SD</sub>      | Output impedance in shutdown mode          |                                                                                                                                                                                                                              |       | 10                    |       | KΩ               |

| UVLO                 | UVLO threshold                             | Falling edge                                                                                                                                                                                                                 |       | 2.3                   |       | V                |

| JVLO <sub>HYST</sub> | UVLO hysteresis                            |                                                                                                                                                                                                                              |       | 100                   |       | mV               |

| Av                   | Voltage Gain                               | B version only                                                                                                                                                                                                               | -1.53 | -1.5                  | -1.48 | V/V              |

**Table 3. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for T<sub>A</sub> between  $-40^{\circ}$ C to  $+85^{\circ}$ C and T<sub>J</sub> up to  $+125^{\circ}$ C for V<sub>IN</sub> between 2.7 V to 5.0 V (Unless otherwise noted). Typical values are referenced to T<sub>A</sub> =  $+25^{\circ}$ C and V<sub>IN</sub> = 3.6 V.

8. Guaranteed by design and characterized.

#### **TYPICAL OPERATING CHARACTERISTICS**

#### **TYPICAL OPERATING CHARACTERISTICS**

#### 0 -60 Ш -65 -20 -70 -75 -40 -80 Left to Right PSRR (dB) -85 (g) \_90 П -60 -95 Right to Left -80 -100 |||NCP2811B Left -105 1 | | | | | -100 -110 -115 NCP2811B Right -120 -120 10 100 1000 10,000 100,000 10 100 1000 10,000 100,000 FREQUENCY (Hz) FREQUENCY (Hz) Figure 24. Crosstalk vs. Frequency @ Vp = 3.6 V Figure 23. PSRR at Vp = 3.6 V

#### **TYPICAL OPERATING CHARACTERISTICS**

#### DETAIL OPERATING DESCRIPTION

#### **Detailed Descriptions**

The NCP2811 is a stereo headphone amplifier with a true ground architecture. This architecture eliminates the need to use 2 external big capacitors required by conventional headphone amplifier.

The structure of the NCP2811 is basically composed of 2 true ground amplifiers, an UVLO, a short circuit protection and also a thermal shutdown. A special circuitry is embedded to eliminate any pop and click noise that occurs during turn on and turn off time. The A version has an external gain selectable by two resistor, B version has a gain of 1.5 V/V.

#### NOCAP ™

NOCAP<sup>m</sup> is a patented architecture which requires only 2 small ceramic capacitors. It generates a symmetrical positive and negative voltage and it allows the output of the amplifiers to be biased around the ground.

#### **Current Limit Protection Circuit**

The NCP2811 embed a protection circuitry against short to ground. When an output is shorted to GND and when a signal appears at the input, the current is limited to 300 mA.

#### **Thermal Overload Protection**

Internal amplifiers are switched off when the temperature exceed 160°C, and will be switch on again when the temperature decrease below 140°C.

#### **Under Voltage Lockout**

When the battery voltage decreases below 2.3 V, the amplifiers are turned off. The hysteresis to turn on it again is 100 mV.

#### Pop and Click Suppression Circuitry

The NCP2811 includes a special circuitry to eliminate any pop and click noise during turn on and turn off time. Basic amplifier creates an offset during these transitions at the output which give a parasitic noise called "pop and click noise". The NCP2811 eliminates this problem.

## Gain Setting Resistor Selection (Rin & Rf, A version only)

$R_{in}$  and  $R_f$  set the closed loop gain of the amplifier. A low gain configuration (close to 1) minimizes the THD + noise values and maximizes the signal to noise ratio.

A closed loop gain in the range of 1 to 10 is recommended to optimize overall system performance.

The formula to calculate the gain is:

$$Av = -\frac{R_{f}}{R_{in}}$$

#### **Input Capacitor Selection**

The input coupling capacitor blocks the DC voltage at the amplifier input terminal. This capacitor creates a high–pass

filter with  $R_{in}$  (externally selectable for A version, 20 k $\Omega$  for B version).

The size of the capacitor must be large enough to couple in low frequencies without severe attenuation in the audio bandwith (20 Hz - 20 kHz).

The cut off frequency for the input high-pass filter is:

$$F_{c} = \frac{1}{2\pi R_{in}C_{in}}$$

A  $F_c < 20$  Hz is recommended.

#### **Charge Pump Capacitor Selection**

Use ceramic capacitor with low ESR for better performances. X5R / X7R capacitor is recommended.

The flying capacitor (C2) serves to transfer charge during the generation of the negative voltage.

The CPVM capacitor (C3) must be equal at least to the CFly capacitor to allow maximum transfer charge. The CPVM value must not exceed 1  $\mu$ F. Higher capacitor value can damage the part.

Table 4 suggests typical value and manufacturer:

#### Table 4.

| Value | Reference        | Package | Manufacturer |

|-------|------------------|---------|--------------|

| 1 μF  | C1005X5R0J105K   | 0402    | TDK          |

| 1 μF  | GRM155R60J105K19 | 0402    | Murata       |

Lower value of capacitors can be used but the maximum output power is reduced and the device may not operate to specifications.

#### Power Supply Decoupling Capacitor (C1)

The NCP2811 is a True Ground amplifier which requires the adequate decoupling capacitor to reduce noise and THD+N. Use X5R / X7R ceramic capacitor and place it closed to the CPVDD pin. A value of 1  $\mu$ F is recommended.

#### **Shutdown Function**

The device enters in shutdown mode when shutdown signal is low. During the shutdown mode, the DC quiescent current of the circuit does not exceed 500 nA. In this configuration, the output impedance is  $10 \text{ k}\Omega$  on each output.

#### **Output Resistor for Capacitive Drive Capability**

Under normal operation, NCP2811 maximum direct capacitive load is in the 80 pF range. If, for any reason, high value capacitive loads should be connected to NCP2811 outputs, an additional 10  $\Omega$  resistor should be placed between the NCP2811 output and the capacitive load to ensure amplifier stability.

#### Layout Recommendation

Connect C1 as close as possible of the Vp pin.

Connect C2 and C3 as close as possible of the NCP2811.

Route audio signal and AGND far from Vp, CPP, CPM, PVM and PGND to avoid any perturbation due to the switching.

#### **Table 5. ORDERING INFORMATION**

| Device         | Package                                                  | Shipping <sup>†</sup> |

|----------------|----------------------------------------------------------|-----------------------|

| NCP2811ADTBR2G | TSSOP-14<br>(Pb-Free)                                    | 2500/Tape & Reel      |

| NCP2811BDTBR2G | TSSOP-14<br>(Pb-Free)                                    | 2500/Tape & Reel      |

| NCP2811AFCT1G  | Flip–Chip 12<br>(Pb–Free)                                | 3000/Tape & Reel      |

| NCP2811BFCT1G  | Flip–Chip 12<br>(Pb–Free)                                | 3000/Tape & Reel      |

| NCP2811BFCCT1G | Flip-Chip 12<br>(Backside Laminate Coating)<br>(Pb-Free) | 3000/Tape & Reel      |

| NCP2811AMTTXG  | WQFN12<br>(Pb-Fre)                                       | 3000/Tape & Reel      |

| NCP2811BMTTXG  | WQFN12<br>(Pb-Free)                                      | 3000/Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

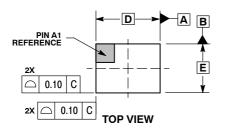

### **PACKAGE DIMENSIONS**

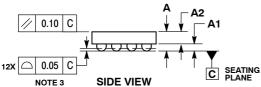

12 PIN FLIP-CHIP, 2.0x1.5, 0.5P CASE 499AZ-01 ISSUE O

NOTES:

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS. 3. COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN MAX     |      |  |

| Α   | 0.54        | 0.60 |  |

| A1  | 0.21        | 0.27 |  |

| A2  | 0.33        | 0.39 |  |

| b   | 0.29        | 0.34 |  |

| D   | 2.00 BSC    |      |  |

| Е   | 1.50 BSC    |      |  |

| е   | 0.50 BSC    |      |  |

#### **SOLDERING FOOTPRINT\***

#### PACKAGE DIMENSIONS

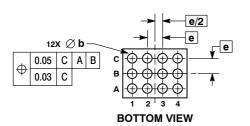

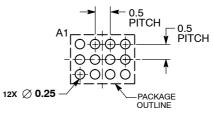

WQFN12 3x3, 0.5P CASE 510AH-01 ISSUE O

**BOTTOM VIEW**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

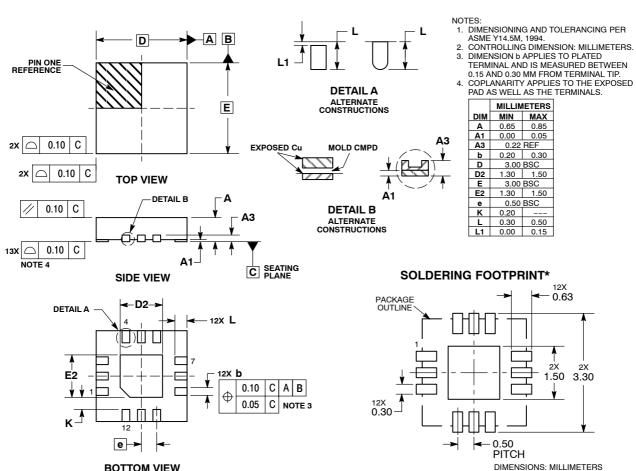

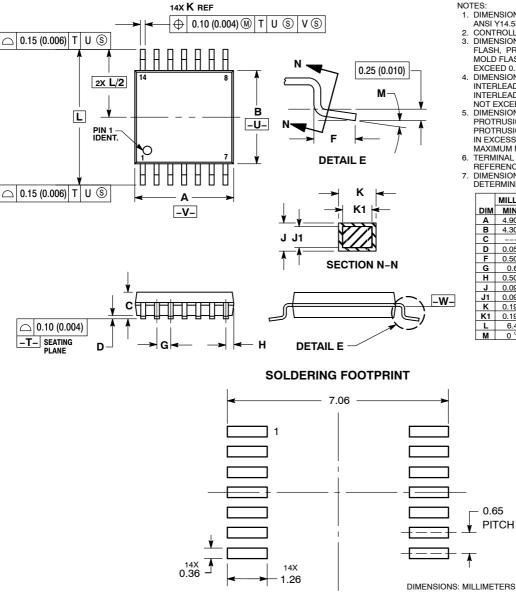

#### PACKAGE DIMENSIONS

TSSOP-14 CASE 948G-01 **ISSUE B**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EVECTED ALT (a goat) DEP OUP. EXCEED 0.15 (0.006) PER SIDE. DIMENSION B DOES NOT INCLUDE

- INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL

- NOT EXCEED 0.25 (0.010) PER SIDE. DIMENSION K DOES NOT INCLUDE DAMBAR DIMENSION & DOES NOT INCLUDE DAMBAP PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION. TERMINAL NUMBERS ARE SHOWN FOR DEFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN   | IETERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 4.90     | 5.10   | 0.193     | 0.200 |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |

| С   |          | 1.20   |           | 0.047 |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |

| G   | 0.65     | BSC    | 0.026 BSC |       |

| Н   | 0.50     | 0.60   | 0.020     | 0.024 |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |

| Κ   | 0.19     | 0.30   | 0.007     | 0.012 |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |

| L   | 6.40 BSC |        | 0.252     | BSC   |

| М   | 0 °      | 8 °    | 0 °       | 8 °   |

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILC does not convey any license under its patent rights or the rights of others. SCILC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications. intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

#### Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

#### ON Semiconductor Website: www.onsemi.com

Phone: 81-3-5773-3850

#### Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative