Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Battery Charge Front-End Protection, USB and AC/DC Supply Compliant

NCP367 is a charge path protection device which allows disconnecting the systems from its output pin in case wrong charging conditions are detected. The system is positive overvoltage protected up to +30 V. Thanks to a very low current consumption, the USB charge is compatible with this integrated component.

This device uses internal PMOS FET, making external devices unnecessary, which reduces the system cost and PCB area of the application board. First, NCP367 is able to instantaneously disconnect the output from the input if the input voltage exceeds the overvoltage threshold. Additional overcurrent protection function allows turning off internal PMOS FET when the charge current exceeds current limit, which is externally selectable.

The current limit value can be modified with control logic pin to divide it by internal gain, allowing USB 100 mA/500 mA charging or USB/Wall adapter charging up to overcurrent threshold. At the same time, Li ion Battery voltage is continuously monitored, providing more safety during the charge. Thermal shutdown protection is also available.

NCP367 provides a negative going flag (FLAG) output, which alerts the system that a fault has occurred as overvoltage (power supply or battery voltage), overcurrent or thermal event.

In addition, the device has ESD–protected input (15 kV Air) when bypassed with a 1  $\mu$ F or larger capacitor.

#### **Features**

- Overvoltage Protection Up to + 30 V

- Fast Turn Off Time

- Very Low Current Consumption/USB Compliant

- Li ion Battery Voltage Monitoring

- Overvoltage Lockout (OVLO)

- Undervoltage Lockout (UVLO)

- Overcurrent Protection Externally Adjustable (OCP) up to 2.8 A

- Thermal Shutdown

- Shutdown EN and Gain Input Pins

- Soft-Start to Eliminate Inrush Current

- Alert FLAG Output

- Compliance to IEC61000-4-2 (Level 4) 8 kV (Contact), 15 kV (Air)

- ESD Ratings: Machine Model = B Human Body Model = 2

- 8 Lead DFN 2.2x2 mm Package

- These are Pb-Free Devices

### ON Semiconductor®

www.onsemi.com

DFN8 MU SUFFIX CASE 506BP

#### MARKING DIAGRAM

XX = Specific Device Code

M = Date Code

= Pb-Free Device

(Note: Microdot may be in either location)

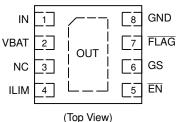

#### **PIN ASSIGNMENT**

#### (.00 ....)

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information in the package dimensions section on page 12 of this data sheet.

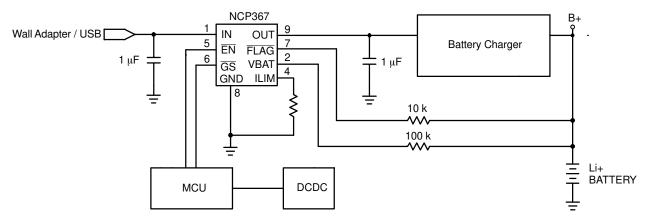

### **Typical Application**

- USB Devices

- Mobile Phones

- Peripheral

- Personal Digital Applications

- MP3 Players

Figure 1. Typical Application Circuit

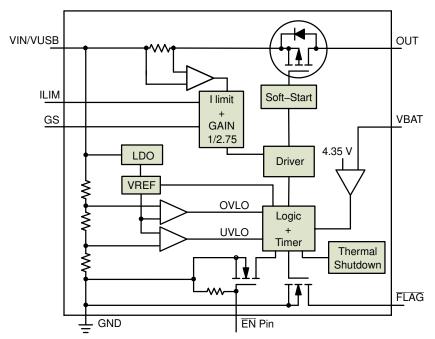

Figure 2. Functional Block Diagram

#### PIN FUNCTION DESCRIPTION

| Pin | Name             | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN               | POWER  | Input Voltage Pin. This pin is connected to the power supply: Wall Adapter or USB. A 1 $\mu$ F low ESR ceramic capacitor, or larger, must be connected between this pin and GND.                                                                                                                                                                                                                                                                                                             |

| 2   | V <sub>BAT</sub> | INPUT  | Li ion Battery voltage sense pin. A serial resistor must be placed between this pin and positive pin of the battery pack.                                                                                                                                                                                                                                                                                                                                                                    |

| 3   | NC               | OUTPUT | Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | I <sub>LIM</sub> | OUTPUT | Current Limit Pin. This pin provides the reference, based on the internal band–gap voltage reference, to limit the overcurrent, across internal PMOSFET, from IN to OUT. A 1% tolerance, or better, resistor shall be used to get the highest accuracy of the Overcurrent Limit.                                                                                                                                                                                                             |

| 5   | ĒN               | INPUT  | Enable Mode Pin. The device enters in shutdown mode when this pin is tied to a high level. In this case the output is disconnected from the input. The state of this pin does not have an impact on the fault detection of the FLAG pin.                                                                                                                                                                                                                                                     |

| 6   | GS               | INPUT  | Gain Select Pin. When the GS pin is tied to 0 level, the Overcurrent threshold is defined by Ilimit setting. See logic table. When GS pin is tied to high, the Overcurrent threshold is set to Ilimit/GS                                                                                                                                                                                                                                                                                     |

| 7   | FLAG             | OUTPUT | Fault Indication Pin. This pin allows an external system to detect fault condition. The FLAG pin goes low when input voltage is below UVLO threshold, exceeds OVLO threshold, charge current from wall adapter to battery exceeds programmed current limit, Li ion Battery voltage (4.3 V) is exceeded or internal temperature exceeds thermal shutdown limit. Since the FLAG pin is open drain functionality, an external pull–up resistor to VBattery must be added (10 kΩ minimum value). |

| 8   | GND              | POWER  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9   | OUT              | OUTPUT | Output Voltage Pin. This pin follows IN pin when "no input fault" is detected. The output is disconnected from the Vin power supply when voltage, current or thermal fault events are detected. A 1 $\mu$ F low ESR ceramic capacitor, or larger, must be connected between this pin and GND.                                                                                                                                                                                                |

NOTE: Pin out provided for concept purpose only and might change in the final product

#### **MAXIMUM RATINGS**

| Rating                                                                                                                 | Symbol             | Value                              | Unit         |

|------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------|--------------|

| Minimum Voltage (IN to GND)                                                                                            | Vmin <sub>in</sub> | -0.3                               | V            |

| Minimum Voltage (All others to GND)                                                                                    | Vmin               | -0.3                               | V            |

| Maximum Voltage (IN to GND)                                                                                            | Vmax <sub>in</sub> | 30                                 | V            |

| Maximum Voltage (All others to GND)                                                                                    | Vmax               | 7.0                                | V            |

| Maximum DC Current from Vin to Vout (PMOS)                                                                             | Imax               | 3.4                                | Α            |

| Thermal Resistance, Junction-to-Air (without PCB area)                                                                 | $R_{	heta JA}$     | 190                                | °C/W         |

| Operating Ambient Temperature Range                                                                                    | T <sub>A</sub>     | -40 to +85                         | °C           |

| Storage Temperature Range                                                                                              | T <sub>stg</sub>   | -65 to +150                        | °C           |

| Junction Operating Temperature                                                                                         | T <sub>J</sub>     | 150                                | °C           |

| ESD Withstand Voltage (IEC 61000–4–2) Human Body Model (HBM), Model = 2 (Note 1) Machine Model (MM) Model = B (Note 2) | Vesd               | 15 Air, 8.0 Contact<br>2000<br>200 | kV<br>V<br>V |

| Latchup                                                                                                                | LU                 | Class 1                            | -            |

| Moisture Sensitivity                                                                                                   | MSL                | Level 1                            | -            |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Human Body Model, 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114.

2. Machine Model, 200 pF discharged through all pins following specification JESD22/A115.

### **ELECTRICAL CHARACTERISTICS - NCP3670PMUEA**

(Min/Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and  $V_{in} = +3.5$  V. Typical values are  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Characteristic                             | Symbol               | Conditions                                                                                                                                           | Min  | Тур  | Max  | Unit |

|--------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage Range                        | V <sub>in</sub>      |                                                                                                                                                      | 1.2  |      | 28   | V    |

| Undervoltage Lockout Threshold             | UVLO                 | V <sub>in</sub> falls down UVLO threshold                                                                                                            | 1.75 | 1.85 | 1.9  | V    |

| Undervoltage Lockout<br>Hysteresis         | UVLO <sub>hyst</sub> |                                                                                                                                                      |      | 60   | 100  | mV   |

| Overvoltage Lockout Threshold NCP367OPMUEA | OVLO                 | V <sub>in</sub> rises up OVLO threshold                                                                                                              | 3.65 | 3.8  | 3.95 | V    |

| Overvoltage Lockout Hysteresis             | OVLO <sub>hyst</sub> |                                                                                                                                                      |      | 45   | 150  | mV   |

| Vin versus Vout Resistance                 | R <sub>DS(on)</sub>  | Enable Mode, Load Connected to Vout                                                                                                                  |      | 50   | 100  | mΩ   |

| Supply Quiescent Current                   | ldd                  | No Load                                                                                                                                              |      | 42   | 130  | μΑ   |

| Disable Mode                               | Idd <sub>dis</sub>   | <u>EN</u> = 1.2 V                                                                                                                                    |      | 35   | 110  | μΑ   |

| Overcurrent Threshold<br>NCP367OPMUEA      | I <sub>OCP</sub>     | $\overline{\text{EN}}$ = low, Load Connected to V <sub>out</sub> ,,<br>R <sub>ilim</sub> = 0 $\Omega$ , 1 A/ $\mu$ s, $\overline{\text{GS}}$ = 0.4 V | 2.30 | 2.85 | 3.40 | Α    |

| Overcurrent Response                       | I <sub>reg</sub>     | 1 A/μs, <del>GS</del> = low, l <sub>lim</sub> = 1.51 A                                                                                               |      | 5.0  |      | %    |

| Current Limit Gain<br>NCP367OPMUEA         | GS <sub>value</sub>  | GS = 1.2 V                                                                                                                                           |      | 2.55 |      |      |

| Battery Overvoltage Threshold              | OV <sub>BAT</sub>    | 0°C to 85°C                                                                                                                                          | 4.3  | 4.35 | 4.4  | V    |

| Battery Overvoltage Hysteresis             | OV <sub>HYS</sub>    | 0°C to 85°C                                                                                                                                          | 100  | 150  | 200  | mV   |

| V <sub>BAT</sub> Pin Leakage               | VBAT <sub>LEAK</sub> |                                                                                                                                                      |      |      | 20   | nA   |

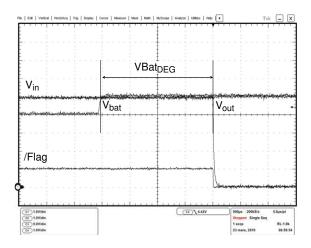

| V <sub>BAT</sub> Deglitch Time             | VBAT <sub>DEG</sub>  | V <sub>BAT</sub> > OV <sub>BAT</sub>                                                                                                                 | 0.2  | 2.0  | 4.0  | ms   |

| FLAG Output Low Voltage                    | Vol <sub>flag</sub>  | V <sub>in</sub> > OVLO<br>Sink 1 mA on FLAG pin                                                                                                      |      |      | 400  | mV   |

| FLAG Leakage Current                       | FLAG <sub>leak</sub> | FLAG level = 5 V                                                                                                                                     |      | 10   |      | nA   |

| EN Voltage High                            | V <sub>ih</sub>      |                                                                                                                                                      | 1.2  |      |      | V    |

| EN Voltage Low                             | V <sub>il</sub>      |                                                                                                                                                      |      |      | 0.4  | V    |

| EN Leakage Current                         | EN <sub>leak</sub>   |                                                                                                                                                      |      | 200  |      | nA   |

| GS Voltage High                            | V <sub>ih</sub>      |                                                                                                                                                      | 1.2  |      |      | V    |

| GS Voltage Low                             | V <sub>il</sub>      |                                                                                                                                                      |      |      | 0.4  | V    |

| GS Leakage Current                         | GS <sub>leak</sub>   |                                                                                                                                                      |      | 200  |      | nA   |

| TIMINGS                                    | •                    |                                                                                                                                                      | •    | •    | •    |      |

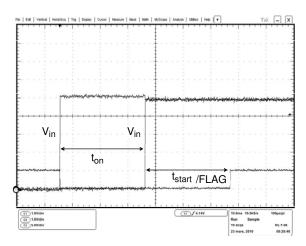

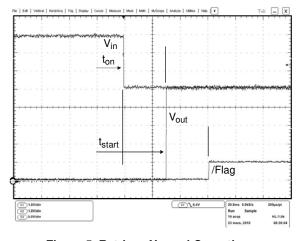

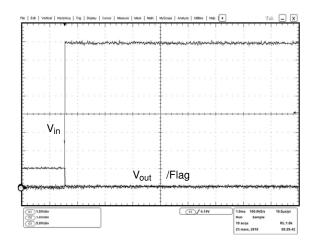

| Start Up Delay                             | t <sub>on</sub>      | From $V_{in} > UVLO$ to $V_{out} = 0.8xV_{in}$                                                                                                       | 15   | 30   | 45   | ms   |

| FLAG going up Delay                        | t <sub>start</sub>   | From $V_{out} > 0.2xV_{in}$ to $\overline{FLAG} = 1.2 \text{ V}$                                                                                     | 15   | 30   | 45   | ms   |

| Rearming Delay                             | t <sub>REARM</sub>   | OCP Active                                                                                                                                           | 15   | 30   | 45   | ms   |

| Overcurrent Regulation Time                | t <sub>REG</sub>     | OCP Active                                                                                                                                           | 1.2  | 1.8  | 3.0  | ms   |

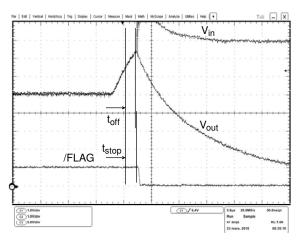

| Output Turn Off Time                       | t <sub>off</sub>     | From V <sub>in</sub> > OVLO to V <sub>out</sub> $\leq$ 0.3 V, V <sub>in</sub> increasing from 3.5 V to 6.5 V at 3 V/ $\mu$ s.                        |      | 1.5  | 5.0  | μS   |

| Alert Delay                                | t <sub>stop</sub>    | From $V_{in}$ > OVLO to $\overline{FLAG} \le 0.4$ V, (see Figure 16) $V_{in}$ increasing from 3.5 V to 6.5 V at 3 V/ $\mu s$                         |      | 1.5  |      | μS   |

| Disable Time                               | t <sub>dis</sub>     | From $\overline{\text{EN}}$ 0.4 to 1.2 V to $V_{\text{out}} \le 0.3 \text{ V}$                                                                       |      | 3.0  |      | μs   |

| Thermal Shutdown Temperature               | T <sub>sd</sub>      |                                                                                                                                                      |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis                | Tsd <sub>hyst</sub>  |                                                                                                                                                      |      | 30   |      | °C   |

NOTE: Electrical parameters are guaranteed by correlation across the full range of temperature.

### **ELECTRICAL CHARACTERISTICS – NCP367DPMUEB**

$(Min/Max\ limits\ values\ (-40^{\circ}C < T_A < +85^{\circ}C)\ and\ V_{in} = +4.0\ V.$  Typical values are  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Characteristic                                | Symbol               | Conditions                                                                                                                                                                                             | Min  | Тур  | Max  | Unit |

|-----------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage Range                           | V <sub>in</sub>      |                                                                                                                                                                                                        | 1.2  |      | 28   | V    |

| Undervoltage Lockout Threshold                | UVLO                 | V <sub>in</sub> falls down UVLO threshold                                                                                                                                                              | 1.75 | 1.85 | 1.9  | V    |

| Undervoltage Lockout<br>Hysteresis            | UVLO <sub>hyst</sub> |                                                                                                                                                                                                        |      | 60   | 100  | mV   |

| Overvoltage Lockout Threshold<br>NCP367DPMUEB | OVLO                 | V <sub>in</sub> rises up OVLO threshold                                                                                                                                                                | 4.38 | 4.54 | 4.7  | V    |

| Overvoltage Lockout Hysteresis                | OVLO <sub>hyst</sub> |                                                                                                                                                                                                        |      | 45   | 100  | mV   |

| Vin versus Vout Resistance                    | R <sub>DS(on)</sub>  | $V_{in} = 5 \text{ V}$ , Enable Mode, Load Connected to $V_{out}$                                                                                                                                      |      | 50   | 100  | mΩ   |

| Supply Quiescent Current                      | ldd                  | No Load                                                                                                                                                                                                |      | 42   | 130  | μΑ   |

| Disable Mode                                  | Idd <sub>dis</sub>   | <del>EN</del> = 1.2 V                                                                                                                                                                                  |      | 35   | 110  | μΑ   |

| Overcurrent Threshold NCP367DPMUEB            | I <sub>OCP</sub>     | $\begin{split} V_{in} = 4.3 \text{ V}, \ \overline{EN} &= \text{low, Load Connected to V}_{out},, \\ R_{ilim} &= 0 \ \Omega, \ 1 \ \text{A}/\mu\text{s}, \ \overline{GS} = 0.4 \ \text{V} \end{split}$ | 1.25 | 1.45 | 1.80 | Α    |

| Overcurrent Response                          | I <sub>reg</sub>     | 1 A/ $\mu$ s, $\overline{GS}$ = low, I <sub>lim</sub> = 1.51 A                                                                                                                                         |      | 5.0  |      | %    |

| Current Limit Gain<br>NCP367DPMUEB            | GS <sub>value</sub>  | <u>GS</u> = 1.2 V                                                                                                                                                                                      |      | 2.77 |      |      |

| Battery Overvoltage Threshold                 | OV <sub>BAT</sub>    | V <sub>in</sub> = 4.2 V, 0°C to 85°C                                                                                                                                                                   | 4.3  | 4.35 | 4.4  | V    |

| Battery Overvoltage Hysteresis                | OV <sub>HYS</sub>    | V <sub>in</sub> = 4.2 V, 0°C to 85°C                                                                                                                                                                   | 100  | 160  | 200  | mV   |

| V <sub>BAT</sub> Pin Leakage                  | VBAT <sub>LEAK</sub> | V <sub>in</sub> = 4.0 V,                                                                                                                                                                               |      |      | 20   | nA   |

| V <sub>BAT</sub> Deglitch Time                | VBAT <sub>DEG</sub>  | V <sub>BAT</sub> > OV <sub>BAT</sub>                                                                                                                                                                   | 0.2  | 2.0  | 4.0  | ms   |

| FLAG Output Low Voltage                       | Vol <sub>flag</sub>  | V <sub>in</sub> > OVLO<br>Sink 1 mA on FLAG pin                                                                                                                                                        |      |      | 400  | mV   |

| FLAG Leakage Current                          | FLAG <sub>leak</sub> | FLAG level = 5 V                                                                                                                                                                                       |      | 10   |      | nA   |

| EN Voltage High                               | V <sub>ih</sub>      |                                                                                                                                                                                                        | 1.2  |      |      | V    |

| EN Voltage Low                                | V <sub>il</sub>      |                                                                                                                                                                                                        |      |      | 0.4  | V    |

| EN Leakage Current                            | EN <sub>leak</sub>   |                                                                                                                                                                                                        |      | 200  |      | nA   |

| GS Voltage High                               | V <sub>ih</sub>      |                                                                                                                                                                                                        | 1.2  |      |      | V    |

| GS Voltage Low                                | V <sub>il</sub>      |                                                                                                                                                                                                        |      |      | 0.4  | V    |

| GS Leakage Current                            | GS <sub>leak</sub>   |                                                                                                                                                                                                        |      | 200  |      | nA   |

| TIMINGS                                       |                      |                                                                                                                                                                                                        | -    |      |      |      |

| Start Up Delay                                | t <sub>on</sub>      | From $V_{in} > UVLO$ to $V_{out} = 0.8xV_{in}$                                                                                                                                                         | 15   | 30   | 45   | ms   |

| FLAG going up Delay                           | t <sub>start</sub>   | From $V_{out} > 0.2xV_{in}$ to $\overline{FLAG} = 1.2 \text{ V}$                                                                                                                                       | 15   | 30   | 45   | ms   |

| Rearming Delay                                | t <sub>REARM</sub>   | OCP Active                                                                                                                                                                                             | 15   | 30   | 45   | ms   |

| Overcurrent Regulation Time                   | t <sub>REG</sub>     | OCP Active                                                                                                                                                                                             | 1.2  | 1.8  | 3.0  | ms   |

| Output Turn Off Time                          | t <sub>off</sub>     | From $V_{in}$ > OVLO to $V_{out} \le 0.3$ V, $V_{in}$ increasing from 4 V to 7 V at 3 V/ $\mu$ s.                                                                                                      |      | 1.5  | 5.0  | μs   |

| Alert Delay                                   | t <sub>stop</sub>    | From $V_{in}$ > OVLO to $\overline{FLAG} \le 0.4$ V, (see Figure 16) $V_{in}$ increasing from 4 V to 7 V at 3 V/ $\mu$ s                                                                               |      | 1.5  |      | μs   |

| Disable Time                                  | t <sub>dis</sub>     | From $\overline{\text{EN}}$ 0.4 to 1.2 V to $V_{out} \le 0.3 \text{ V}$                                                                                                                                |      | 3.0  |      | μS   |

| Thermal Shutdown Temperature                  | T <sub>sd</sub>      |                                                                                                                                                                                                        |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis                   | Tsd <sub>hyst</sub>  |                                                                                                                                                                                                        |      | 30   |      | °C   |

NOTE: Electrical parameters are guaranteed by correlation across the full range of temperature.

### **ELECTRICAL CHARACTERISTICS – Other OVLO version**

(Min/Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and  $V_{in} = +5.0$  V. Typical values are  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Characteristic                                                                                | Symbol               | Conditions                                                                                                                                                                                   | Min                          | Тур                          | Max                          | Unit |

|-----------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------|

| Input Voltage Range                                                                           | $V_{in}$             |                                                                                                                                                                                              | 1.2                          |                              | 28                           | V    |

| Undervoltage Lockout Threshold                                                                | UVLO                 | V <sub>in</sub> falls down UVLO threshold                                                                                                                                                    | 1.75                         | 1.85                         | 1.9                          | V    |

| Undervoltage Lockout<br>Hysteresis                                                            | UVLO <sub>hyst</sub> |                                                                                                                                                                                              |                              | 80                           | 100                          | mV   |

| Overvoltage Lockout Threshold<br>NCP367xPMUEC<br>NCP367DPMUEE<br>NCP367DPMUEL<br>NCP367OPMUEO | OVLO                 | V <sub>in</sub> rises up OVLO threshold                                                                                                                                                      | 5.64<br>5.85<br>6.60<br>6.90 | 5.85<br>6.07<br>6.84<br>7.20 | 6.05<br>6.28<br>7.08<br>7.50 | V    |

| Overvoltage Lockout Hysteresis                                                                | OVLO <sub>hyst</sub> |                                                                                                                                                                                              |                              | 100                          | 150                          | mV   |

| Vin versus Vout Resistance                                                                    | R <sub>DS(on)</sub>  | $V_{in} = 5 \text{ V}$ , Enable Mode, Load Connected to $V_{out}$                                                                                                                            |                              | 50                           | 100                          | mΩ   |

| Supply Quiescent Current                                                                      | ldd                  | No Load                                                                                                                                                                                      |                              | 42                           | 130                          | μΑ   |

| Disable Mode                                                                                  | Idd <sub>dis</sub>   | <del>EN</del> = 1.2 V                                                                                                                                                                        |                              | 40                           | 110                          | μΑ   |

| Overcurrent Threshold<br>NCP367Dx<br>NCP367Ox                                                 | I <sub>OCP</sub>     | $\begin{aligned} V_{in} &= 5 \text{ V, } \overline{EN} = \text{low, Load Connected to V}_{out},, \\ R_{ilim} &= 0  \Omega, \text{ 1 A/$\mu$s, } \overline{GS} = 0.4 \text{ V} \end{aligned}$ | 1.25<br>2.30                 | 1.51<br>2.85                 | 1.80<br>3.40                 | А    |

| Overcurrent Response                                                                          | I <sub>reg</sub>     | 1 A/μs, <del>GS</del> = low, l <sub>lim</sub> = 1.51 A                                                                                                                                       |                              | 5.0                          |                              | %    |

| Current Limit Gain NCP367D<br>NCP367O                                                         | GS <sub>value</sub>  | <del>GS</del> = 1.2 V                                                                                                                                                                        |                              | 2.70<br>2.55                 |                              |      |

| Battery Overvoltage Threshold                                                                 | OV <sub>BAT</sub>    | 0°C to 85°C                                                                                                                                                                                  | 4.3                          | 4.35                         | 4.4                          | V    |

| Battery Overvoltage Hysteresis                                                                | OV <sub>HYS</sub>    | 0°C to 85°C                                                                                                                                                                                  | 100                          | 150                          | 200                          | mV   |

| V <sub>BAT</sub> Pin Leakage                                                                  | VBAT <sub>LEAK</sub> |                                                                                                                                                                                              |                              |                              | 20                           | nA   |

| V <sub>BAT</sub> Deglitch Time                                                                | VBAT <sub>DEG</sub>  | V <sub>BAT</sub> > OV <sub>BAT</sub>                                                                                                                                                         | 0.2                          | 2.0                          | 4.0                          | ms   |

| FLAG Output Low Voltage                                                                       | Vol <sub>flag</sub>  | V <sub>in</sub> > OVLO<br>Sink 1 mA on FLAG pin                                                                                                                                              |                              |                              | 400                          | mV   |

| FLAG Leakage Current                                                                          | FLAG <sub>leak</sub> | FLAG level = 5 V                                                                                                                                                                             |                              | 10                           |                              | nA   |

| EN Voltage High                                                                               | $V_{ih}$             | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                                                         | 1.2                          |                              |                              | V    |

| EN Voltage Low                                                                                | V <sub>il</sub>      | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                                                         |                              |                              | 0.4                          | V    |

| EN Leakage Current                                                                            | EN <sub>leak</sub>   | EN = 5.5 V or GND                                                                                                                                                                            |                              | 200                          |                              | nA   |

| GS Voltage High                                                                               | $V_{ih}$             | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                                                         | 1.2                          |                              |                              | V    |

| GS Voltage Low                                                                                | V <sub>il</sub>      | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                                                         |                              |                              | 0.4                          | V    |

| GS Leakage Current                                                                            | GS <sub>leak</sub>   | EN = 5.5 V or GND                                                                                                                                                                            |                              | 200                          |                              | nA   |

| TIMINGS                                                                                       |                      |                                                                                                                                                                                              | -                            |                              | •                            | •    |

| Start Up Delay                                                                                | t <sub>on</sub>      | From $V_{in} > UVLO$ to $V_{out} = 0.8xV_{in}$                                                                                                                                               | 15                           | 30                           | 45                           | ms   |

| FLAG going up Delay                                                                           | t <sub>start</sub>   | From $V_{out} > 0.2xV_{in}$ to $\overline{FLAG} = 1.2 \text{ V}$                                                                                                                             | 15                           | 30                           | 45                           | ms   |

| Rearming Delay                                                                                | t <sub>REARM</sub>   | OCP Active                                                                                                                                                                                   | 15                           | 30                           | 45                           | ms   |

| Overcurrent Regulation Time                                                                   | t <sub>REG</sub>     | OCP Active                                                                                                                                                                                   | 1.2                          | 1.8                          | 3.0                          | ms   |

| Output Turn Off Time                                                                          | t <sub>off</sub>     | From $V_{in}$ > OVLO to $V_{out} \le 0.3$ V, $V_{in}$ increasing from 5 V to 8 V at 3 V/ $\mu$ s.                                                                                            |                              | 1.5                          | 5.0                          | μS   |

| Alert Delay                                                                                   | t <sub>stop</sub>    | From $V_{in}$ > OVLO to $\overline{FLAG} \le 0.4$ V, (see Figure 16) $V_{in}$ increasing from 5 V to 8 V at 3 V/ $\mu$ s                                                                     |                              | 1.5                          |                              | μs   |

| Disable Time                                                                                  | t <sub>dis</sub>     | From $\overline{\text{EN}}$ 0.4 to 1.2 V to $V_{out} \le 0.3 \text{ V}$                                                                                                                      |                              | 3.0                          |                              | μS   |

| Thermal Shutdown Temperature                                                                  | T <sub>sd</sub>      |                                                                                                                                                                                              |                              | 150                          |                              | °C   |

| Thermal Shutdown Hysteresis                                                                   | Tsd <sub>hyst</sub>  |                                                                                                                                                                                              |                              | 30                           |                              | °C   |

NOTE: Electrical parameters are guaranteed by correlation across the full range of temperature.

### TYPICAL OPERATING CHARACTERISTICS

Figure 3. Hot Plug-in from 0 to 5 V,  $$t_{\rm on}$$  and  $t_{\rm start}$

Figure 5. Retrieve Normal Operation,  $$t_{\mbox{\scriptsize on}}$$  and  $t_{\mbox{\scriptsize start}}$

Figure 4. Overvoltage from 5 to 8 V,  $$t_{\rm off}$$  and  $t_{\rm stop}$

Figure 6. Overvoltage from 0 to 10 V

Figure 7. Battery Overvoltage, Deglitch Time

### TYPICAL OPERATING CHARACTERISTICS

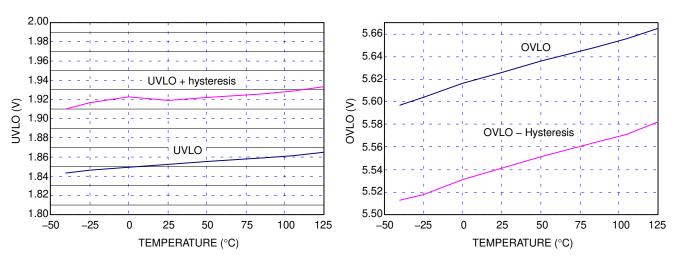

Figure 8. UVLO and Hysteresis

Figure 9. OVLO and Hysteresis vs. Temperature (5.6 V version)

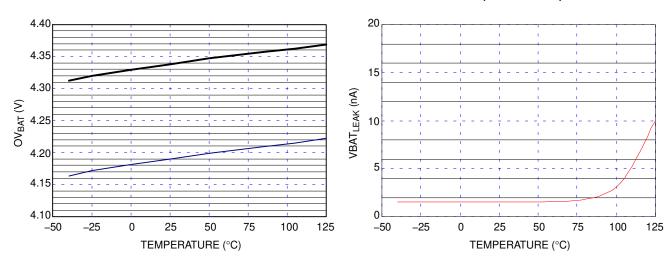

Figure 10. V<sub>BAT</sub> Threshold and Hysteresis vs. Temperature

Figure 11. V<sub>BAT</sub> Pin Leakage vs. Temperature

#### APPLICATION INFORMATION

#### Operation

The NCP367 is an integrated IC which offers a complete protection of the portable devices during the Li ion battery charge.

First, the input pin is protected up to +30 V, protecting the down stream system (charger, transceiver, system...) against the power supply transients such as inrush current or defective functionality. Additional protection level is offered with the overcurrent block which eliminates current peak or opens the charge path if an overcurrent default appears.

More of that, the battery voltage is monitored all along the input power supply is connected, allowing to open charge path if Li ion battery voltage exceeds 4.3 V, caused by CCCV charger or battery pack fault.

The integrated pass element (PMOS FET) is sized to support very high charge DC current up to 2.3 A. The overcurrent threshold can be externally adjusted with a pull–down resistor and gain select pin is available to divide current limit threshold with internal fixed gain. Allowing to adjust with logic pin the overcurrent threshold if USB/500 mA or WA/1.5 A is detected, without changing R<sub>ILIM</sub> resistor, in example.

Undervoltage, Overvoltage, Overcurrent and thermal faults are signalized thanks to the open drain FLAG pin, by pulling its down.

#### **Undervoltage Lockout (UVLO)**

To ensure proper operation under any conditions, the device has a built–in undervoltage lock out (UVLO) circuit. During Vin positive going slope, the output remains disconnected from input until Vin voltage is above 1.85 V plus hysteresis nominal. This circuit has a 80 mV hysteresis to provide noise immunity to transient condition.

#### Overvoltage Lockout (OVLO)

To protect connected systems on Vout pin from overvoltage, the device has a built–in overvoltage lock out (OVLO) circuit. During overvoltage condition, the output remains disabled as long as the input voltage exceeds this threshold.

FLAG output is tied to low as long as Vin is higher than OVLO. This circuit has a 100 mV hysteresis to provide noise immunity to transient conditions.

#### **FLAG** Output

NCP367 provides a FLAG output, which alerts external systems that a fault has occurred.

This pin is tied to low as soon as the OVLO,  $OV_{BAT}, I_{OCP}$  or internal temperature thresholds are exceeded and remains low until between minimum driving voltage and UVLO threshold. When Vin level recovers normal condition,  $\overline{FLAG}$  is held high. The pin is an open drain output, thus a pull up resistor (typically  $1~M\Omega$  – Minimum  $10~k\Omega)$  must be provided to  $V_{CC}.~\overline{FLAG}$  pin is an open drain output, which is able to support 1~mA maximum.

#### **EN** Input

To enable normal operation, the  $\overline{\text{EN}}$  pin shall be forced to low or connected to ground. A <u>high</u> level on the pin, disconnects OUT pin from IN pin.  $\overline{\text{EN}}$  does not overdrive a UVLO or OVLO fault.

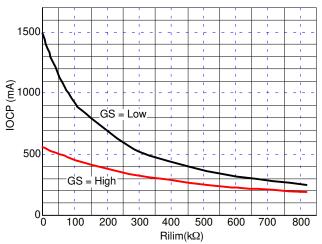

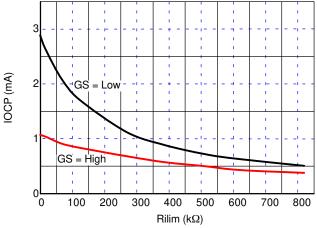

#### **Overcurrent Protection (OCP)**

This device integrates the overcurrent protection function, from wall adapter to battery. That means the current across the internal PMOS is regulated and cut when the value, set by external RSEL resistor, exceeds  $I_{LIM}$  longer than  $t_{REG}$ .

An internal resistor is placed in series with the pin allowing to have a maximum OCP value when I<sub>LIM</sub> pin is directly connected to GND.

By adding external resistors in series with I<sub>LIM</sub> and GND, the OCP value is decreased.

An additional logic pin,  $\overline{GS}$  (gain select), is very useful in case of different charge rate is necessary (Wall adapter and USB, for example).

By setting  $\overline{GS}$  to 0.4 V, overcurrent thresholds are depending on R select resistor, which is connect between pin 4 and GND. When the  $\overline{GS}$  pin is tied to 1.2 V (high logic level) the preselected current limit is divided by 2.75. Due

to this option, both fast charge or USB charge are authorized with the same device.

Figure 12.  $I_{OCP}$  versus  $R_{LIM}$ , GS = low and high, 1.5 A version

Figure 13. Over Current Threshold versus R<sub>LIMIT</sub> 2.85 A Version

Typical R<sub>LIM</sub> calculation is following: NCP367DxMUxxTBG

$$R_{LIM} \left( k\Omega \right) = 249 \ / \ I_{OCP} - 165 \label{eq:RLIM}$$

NCP367OxMUxxTBG

$$R_{LIM}\left(k\Omega\right)=532\:/\:I_{OCP}-180$$

During overcurrent event, charge area is opened and  $\overline{FLAG}$  output is tied to low, allowing the  $\mu Controller$  to take into account the fault event and then open the charge path.

At power up (accessory is plugged on input pins), the current is limited up to I<sub>LIM</sub> during 1.8 ms (typical), to allow capacitor charge and limit inrush current. If the I<sub>LIM</sub> threshold is exceeded over 1.8 ms, the device enter in OCP burst mode until the overcurrent event disappears.

### **V<sub>BAT</sub> Sense**

The connection of the V<sub>BAT</sub> pin to the positive connection of the Li ion battery pack allows preventing overvoltage transient, greater than 4.35 V. In case of wrong charger conditions, the PMOS is then opened, eliminating Battery pack over voltage which could create safety issues and temperature increasing.

The 4.35 V comparator has a 150 mV built—in hysteresis. More of that, deglitch function of 2 ms is integrated to prevent voltage transients on the Battery voltage. If the battery over voltage condition exceeds deglitch time, the charge path is opened and  $\overline{FLAG}$  pin is tied to low level until the  $V_{BAT}$  is greater than 4.35 V – hysteresis.

At wall adapter insertion, and if the battery is fully charged,  $V_{bat}$  comparator stays locked until battery needs to be recharged (4.2 V typ – 4.1 V min).

A serial resistor has to be placed in series with Vbat pin and battery connection, with a 200 k $\Omega$  recommended value.

#### **PCB Recommendations**

The NCP367 integrates low R<sub>DS(on)</sub> PMOS FET, nevertheless PCB layout rules must be respected to properly evacuate the heat out of the silicon. The DFN PAD1 corresponds to the PMOS drain so must be connected to OUT plane to increase the heat transfer. Of course, in any case, this pad shall be not connected to any other potential.

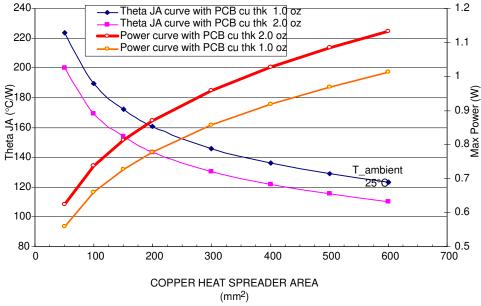

Following figure shows package thermal resistance of a DFN 2.2x2 mm.

Figure 14.

#### **Internal PMOS FET**

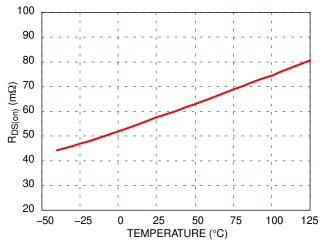

NCP367 includes an internal PMOS FET to protect the systems, connected on OUT pin, from positive over–voltage. Regarding electrical characteristics, the  $R_{DS(on)}$ , during normal operation, will create low losses on  $V_{out}$  pin versus  $V_{in}$ , due to very low  $R_{DS(on)}$ .

Figure 15. Typical R<sub>DS(on)</sub> versus Temperature

#### **ESD Tests**

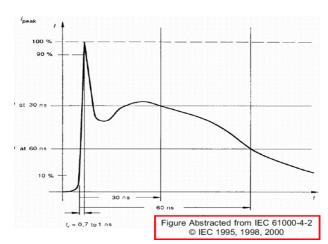

NCP367 fully support the IEC61000–4–2, level 4 (Input pin, 1  $\mu$ F mounted on board). That means, in Air condition, Vin has a  $\pm 15$  kV ESD protected input. In Contact condition, Vin has  $\pm 8$  kV ESD protected input. Please refer to Figure 16 to see the IEC 61000–4–2 electrostatic discharge waveform.

Figure 16. IEC 61000-4-2 Electrostatic Discharge

### **ORDERING INFORMATION**

| Device          | Marking | Package           | Shipping <sup>†</sup> |

|-----------------|---------|-------------------|-----------------------|

| NCP367DPMUECTBG | DC      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367DPMUEETBG | DE      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367DPMUELTBG | DL      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367OPMUEOTBG | P3      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367OPMUEATBG | EA      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367DPMEBTBG  | PE      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP367OPMUECTBG | EC      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **SELECTION GUIDE**

The NCP367 can be available in several undervoltage and overvoltage thresholds versions. Part number is designated as follows:

| Code | Contents                                                                                                                                                                    |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| а    | Overcurrent threshold<br>a = D: 1.51 A<br>a = O: 2.85 A                                                                                                                     |  |  |

| b    | $\begin{array}{c} V_{BAT} \ \mbox{Voltage} \\ \mbox{b: P = 4.36 V} \\ \mbox{(additional thresholds available for a wide} \\ \mbox{Lithium ion material range)} \end{array}$ |  |  |

| С    | UVLO Typical Threshold<br>c: E = 1.85 V                                                                                                                                     |  |  |

| d    | OVLO Typical Threshold (Additional thresholds available) d: C = 5.85 V d: E = 6.07 V d: L = 6.85 V d: O = 7.20 V d: A = 3.80 V d: B = 4.54 V                                |  |  |

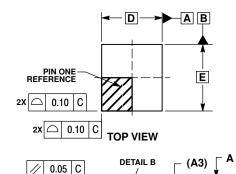

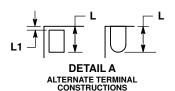

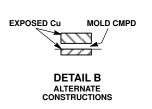

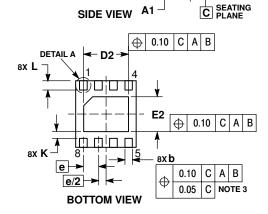

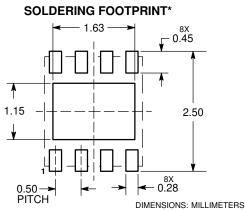

#### PACKAGE DIMENSIONS

#### DFN8, 2.0x2.2, 0.5P CASE 506BP **ISSUE A**

9x 🗀

NOTE 4

0.05 C

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND

- 0.30 mm FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |           |      |  |  |

|-----|-------------|-----------|------|--|--|

| DIM | MIN TYP MAX |           |      |  |  |

| Α   | 0.80        |           | 1.00 |  |  |

| A1  | 0.00        |           | 0.05 |  |  |

| A3  |             | 0.20 REF  |      |  |  |

| b   | 0.20        | 0.20 0.30 |      |  |  |

| D   | 2.00 BSC    |           |      |  |  |

| D2  | 1.43        | 1.43 1.53 |      |  |  |

| E   |             | 2.20 BSC  |      |  |  |

| E2  | 1.05        | 1.2       |      |  |  |

| е   | 0.50 BSC    |           |      |  |  |

| K   | 0.20        | 0.22      | 0.30 |  |  |

| L   | 0.25        |           | 0.35 |  |  |

| L1  | 0.15        |           |      |  |  |

**A**1

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and unarre registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent—Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in extense intended for express intended for express intended for express the product of the scall Conduct. in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your loca Sales Representative