# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

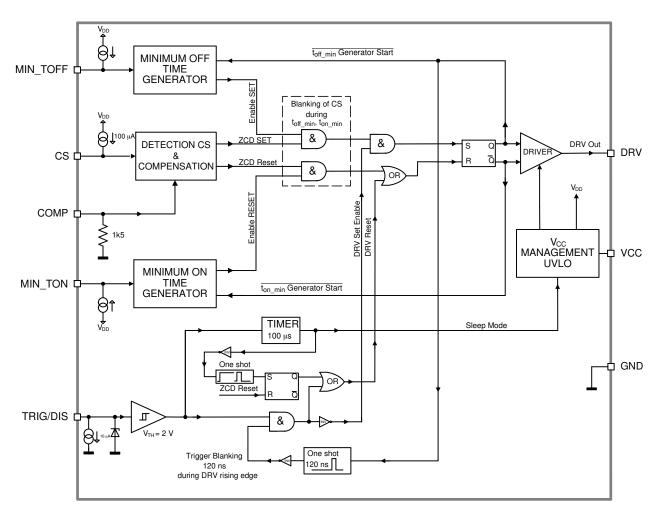

### Secondary Side Synchronous Rectification Driver for High Efficiency SMPS Topologies

The NCP4304A/B is a full featured controller and driver tailored to control synchronous rectification circuitry in switch mode power supplies. Due to its versatility, it can be used in various topologies such as flyback, forward and Half Bridge Resonant LLC.

The combination of externally adjustable minimum on and off times helps to fight the ringing induced by the PCB layout and other parasitic elements. Therefore, a reliable and noise less operation of the SR system is insured.

The extremely low turn off delay time, high sink current capability of the driver and automatic package parasitic inductance compensation system allow to maximize synchronous rectification MOSFET conduction time that enables further increase of SMPS efficiency.

Finally, a wide operating  $V_{CC}$  range combined with two versions of driver voltage clamp eases implementation of the SR system in 24 V output applications.

#### Features

- Self-Contained Control of Synchronous Rectifier in CCM, DCM, and QR Flyback Applications

- Precise True Secondary Zero Current Detection with Adjustable Threshold

- Automatic Parasitic Inductance Compensation Input

- Typically 40 ns Turn off Delay from Current Sense Input to Driver

- Zero Current Detection Pin Capability up to 200 V

- Optional Ultrafast Trigger Interface for Further Improved Performance in Applications that Work in Deep CCM

- Disable Input to Enter Standby or Low Consumption Mode

- Adjustable Minimum On Time Independent of V<sub>CC</sub> Level

- Adjustable Minimum Off Time Independent of V<sub>CC</sub> Level

- 5 A/2.5 A Peak Current Sink/Source Drive Capability

- Operating Voltage Range up to 30 V

- Gate Drive Clamp of Either 12 V (NCP4304A) or 6 V (NCP4304B)

- Low Startup and Standby Current Consumption

- Maximum Frequency of Operation up to 500 kHz

- SOIC-8 Package

- These are Pb–Free Devices

#### **Typical Applications**

- Notebook Adapters

- High Power Density AC/DC Power Supplies

- Gaming Consoles

- All SMPS with High Efficiency Requirements

### **ON Semiconductor®**

www.onsemi.com

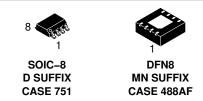

#### MARKING DIAGRAMS

(\*Note: Microdot may be in either location)

#### **PINOUT INFORMATION**

| VCC 📼                     |   | 8 📼 DRV  |

|---------------------------|---|----------|

| MIN_TOFF ==<br>MIN_TON == | 2 | 7 🗖 GND  |

| MIN_TON 📼                 | 3 | 6 📼 COMP |

| TRIG/DIS 📼                | 4 | 5 🖿 CS   |

(NOTE: For DFN the exposed pad must be either unconnected or preferably connected to ground. The GND pin must be always connected to ground.)

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup>  |

|---------------|---------------------|------------------------|

| NCP4304ADR2G  | SOIC-8<br>(Pb-Free) | 2,500 /<br>Tape & Reel |

| NCP4304BDR2G  | SOIC-8<br>(Pb-Free) | 2,500 /<br>Tape & Reel |

| NCP4304AMNTWG | DFN8<br>(Pb–Free)   | 4,000 /<br>Tape & Reel |

| NCP4304BMNTWG | DFN8<br>(Pb–Free)   | 4,000 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

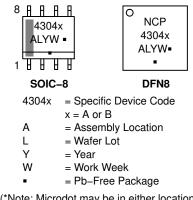

Figure 1. Typical Application Example – LLC Converter

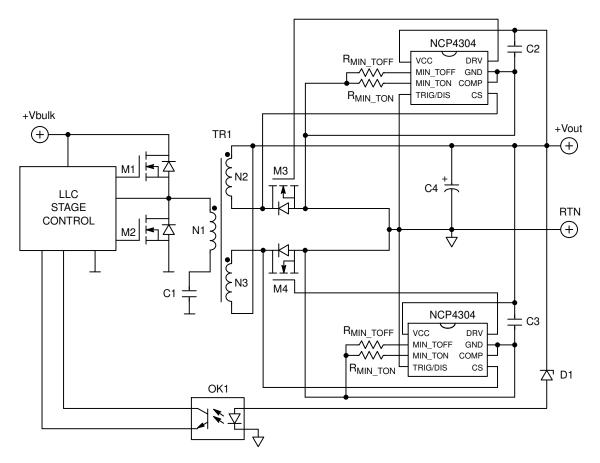

Figure 2. Typical Application Example – DCM or QR Flyback Converter

#### **PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Function                              | Pin Description                                                                                                                                                                                                                                                               |

|---------|----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC      | Supplies the driver                   | Supply terminal of the controller. Accepts up to 30 V continuously.                                                                                                                                                                                                           |

| 2       | MIN_TOFF | Minimum off time adjust               | Adjust the minimum off time period by connecting resistor to ground.                                                                                                                                                                                                          |

| 3       | MIN_TON  | Minimum on time adjust                | Adjust the minimum on time period by connecting resistor to ground.                                                                                                                                                                                                           |

| 4       | TRIG/DIS | Forced reset input                    | This ultrafast input turns off the SR MOSFET in CCM applications. Activates sleep mode if pulled up for more than 100 $\mu s.$                                                                                                                                                |

| 5       | CS       | Current sense of the SR<br>MOSFET     | This pin detects if the current flows through the SR MOSFET and/or its body diode. Basic turn off detection threshold is 0 mV. A resistor in series with this pin can modify the turn off threshold if needed.                                                                |

| 6       | COMP     | Compensation inductance<br>connection | Use as a Kelvin connection to auxiliary compensation inductance. If SR<br>MOSFET package parasitic inductance compensation is not used (like for<br>SMT MOSFETs), connect this pin directly to GND pin.                                                                       |

| 7       | GND      | IC ground                             | Ground connection for the SR MOSFET driver and $V_{CC}$ decoupling capacitor.<br>Ground connection for minimum ton, toff adjust resistors and trigger input.<br>GND pin should be wired directly to the SR MOSFET source<br>terminal/soldering point using Kelvin connection. |

| 8       | DRV      | Gate driver output                    | Driver output for the SR MOSFET.                                                                                                                                                                                                                                              |

#### **MAXIMUM RATINGS**

| Symbol                                       | Rating                                                                                                                                    | Value       | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>                              | IC Supply Voltage                                                                                                                         | -0.3 to 30  | V    |

| V <sub>DRV</sub>                             | Driver Output Voltage                                                                                                                     | -0.3 to 17  | V    |

| V <sub>CS</sub>                              | Current Sense Input dc Voltage                                                                                                            | -4 to 200   | V    |

| V <sub>Csdyn</sub>                           | Current Sense Input Dynamic Voltage (t <sub>pw</sub> = 200 ns)                                                                            | -10 to 200  | V    |

| V <sub>TRIG/DIS</sub>                        | Trigger Input Voltage                                                                                                                     | -0.3 to 10  | V    |

| V <sub>MIN_TON</sub> , V <sub>MIN_TOFF</sub> | MIN_TON and MIN_TOFF Input Voltage                                                                                                        | -0.3 to 10  | V    |

| I <sub>MIN_TON</sub> , I <sub>MIN_TOFF</sub> | MIN_TON and MIN_TOFF Current                                                                                                              | -10 to +10  | mA   |

| V <sub>COMP</sub>                            | Static Voltage Difference between COMP and GND Pins (Internally Clamped)                                                                  | -3 to 10    | V    |

| V <sub>COMP_dyn</sub>                        | Dynamic Voltage Difference between COMP and GND Pins (t <sub>pw</sub> = 200 ns)                                                           | -10 to 10   | V    |

| ICOMP                                        | Current into COMP Pin                                                                                                                     | –5 to 5     | mA   |

| $R_{	ext{	heta}JA}$                          | Thermal Resistance Junction-to-Air, SOIC – A/B Versions                                                                                   | 180         | °C/W |

| $R_{	heta JA}$                               | Thermal Resistance Junction-to-Air, DFN – A/B Versions, 50 mm <sup>2</sup> – 1.0 oz. Copper Spreader                                      | 180         | °C/W |

| $R_{\thetaJA}$                               | Thermal Resistance Junction-to-Air, DFN – A/B Versions, 600 mm <sup>2</sup> – 1.0 oz. Copper Spreader                                     | 80          | °C/W |

| T <sub>Jmax</sub>                            | Maximum Junction Temperature                                                                                                              | 150         | °C   |

| T <sub>Smax</sub>                            | Storage Temperature Range                                                                                                                 | -60 to +150 | °C   |

| T <sub>Lmax</sub>                            | Lead Temperature (Soldering, 10 s)                                                                                                        | 300         | °C   |

|                                              | ESD Capability, Human Body Model except Pin V <sub>CS</sub> – Pin 5, HBM ESD Capability on Pin 5 is 650 V per JEDEC Standard JESD22–A114E | 2           | kV   |

|                                              | ESD Capability, Machine Model per JEDEC Standard JESD22-A115-A                                                                            | 200         | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. This device meets latchup tests defined by JEDEC Standard JESD78.

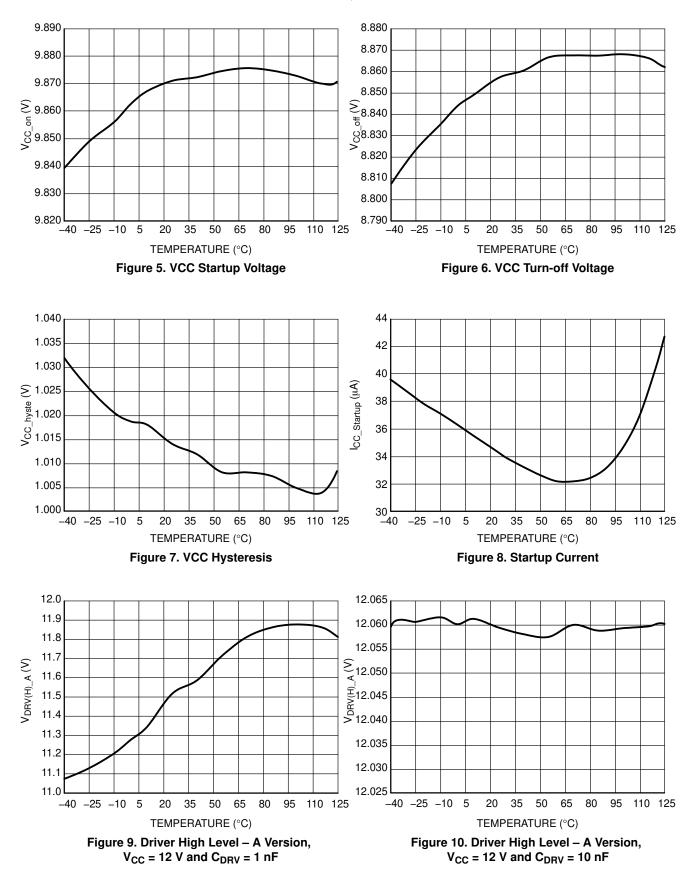

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \\ (\text{For typical values } T_J = 25^\circ\text{C}, \text{ for min/max values } T_J = -40^\circ\text{C} \text{ to } +125^\circ\text{C}, \text{ } V_{CC} = 12 \text{ V}, \text{ } C_{DRV} = 0 \text{ nF}, \text{ } \text{R}_{MIN\_TOF} = \text{R}_{MIN\_TOFF} = 10 \text{ k}\Omega, \text{ } V_{TRIG/DIS} = 0 \text{ V}, \text{ } f_{CS} = 100 \text{ kHz}, \text{ } DC_{CS} = 50\%, \text{ } V_{CS\_high} = 4 \text{ V}, \text{ } V_{CS\_low} = -1 \text{ V} \text{ unless otherwise noted}) \end{array}$

| Symbol                                   | Rating                                                                                                                                                                        | Pin | Min | Тур          | Max        | Unit |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------|------------|------|

| PPLY SECTION                             | l .                                                                                                                                                                           | •   | •   | •            | •          | -    |

| V <sub>CC_on</sub>                       | Turn-on threshold level (V <sub>CC</sub> going up)                                                                                                                            | 1   | 9.3 | 9.9          | 10.5       | V    |

| V <sub>CC_off</sub>                      | Minimum operating voltage after turn-on (V <sub>CC</sub> going down)                                                                                                          | 1   | 8.3 | 8.9          | 9.5        | V    |

| V <sub>CC_hyste</sub>                    | V <sub>CC</sub> hysteresis                                                                                                                                                    | 1   | 0.6 | 1.0          | 1.4        | V    |

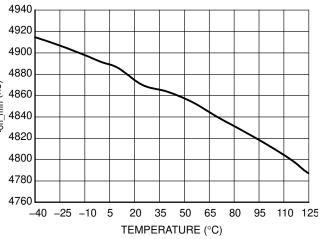

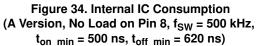

| I <sub>CC1_A</sub><br>I <sub>CC1_B</sub> | Internal IC consumption (no output load on pin 8, $f_{SW}$ = 500 kHz, $t_{on\_min}$ = 500 ns, $t_{off\_min}$ = 620 ns)                                                        | 1   |     | 4.5<br>4.0   | 6.6<br>6.2 | mA   |

| I <sub>CC2_A</sub><br>I <sub>CC2_B</sub> | Internal IC consumption ( $C_{DRV}$ = 1 nF on pin 8, f <sub>SW</sub> = 400 kHz, t <sub>on_min</sub> = 500 ns, t <sub>off_min</sub> = 620 ns)                                  | 1   | -   | 9.0<br>6.5   | 12<br>9    | mA   |

| I <sub>CC3_A</sub><br>I <sub>CC3_B</sub> | Internal IC consumption ( $C_{DRV}$ = 10 nF on pin 8, f <sub>SW</sub> = 400 kHz, t <sub>on_min</sub> = 500 ns, t <sub>off_min</sub> = 620 ns)                                 | 1   |     | 57.0<br>35.0 | 80<br>65   | mA   |

| I <sub>CC_StartUp</sub>                  | Startup current consumption ( $V_{CC} = V_{CC_{on}} - 0.1$ V, no switching at CS pin)                                                                                         | 1   | -   | 35           | 75         | μΑ   |

| CC_Disable_1                             | Current consumption during disable mode (No switching at CS pin, $V_{TRIG/DIS} = 5 \text{ V}$ )                                                                               | 1   | -   | 45           | 90         | μΑ   |

| CC_Disable_2                             | Current consumption during disable mode (CS pin is switching, $f_{SW} = 500 \text{ kHz}, V_{CS\_high} = 4 \text{ V}, V_{CS\_low} = -1 \text{ V}, V_{TRIG/DIS} = 5 \text{ V})$ | 1   | -   | 200          | 330        | μΑ   |

| IVE OUTPUT                               |                                                                                                                                                                               |     |     |              |            |      |

| t <sub>r_A</sub>                         | Output voltage rise-time for A version (C <sub>DRV</sub> = 10 nF)                                                                                                             | 8   | -   | 120          | -          | ns   |

| t <sub>r_B</sub>                         | Output voltage rise-time for B version (C <sub>DRV</sub> = 10 nF)                                                                                                             | 8   | -   | 80           | -          | ns   |

|                                          |                                                                                                                                                                               | -   | 1   |              |            | 1    |

| ۹_               |                                                                      | Ŭ |   |     |   |    |

|------------------|----------------------------------------------------------------------|---|---|-----|---|----|

| t <sub>r_</sub>  | Output voltage rise-time for B version (C <sub>DRV</sub> = 10 nF)    | 8 | - | 80  | - | ns |

| t <sub>f</sub>   | Output voltage fall-time for A version ( $C_{DRV} = 10 \text{ nF}$ ) | 8 | - | 50  | - | ns |

| t <sub>f</sub> _ | Output voltage fall-time for B version ( $C_{DRV} = 10 \text{ nF}$ ) | 8 | - | 35  | - | ns |

| R                | Driver source resistance (Note 1)                                    | 8 | - | 1.8 | 7 | Ω  |

| R                | Driver sink resistance                                               | 8 | - | 1   | 2 | Ω  |

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \text{ (continued)} \\ (\text{For typical values } T_J = 25^\circ\text{C}, \text{ for min/max values } T_J = -40^\circ\text{C} \text{ to } +125^\circ\text{C}, \text{ } V_{CC} = 12 \text{ V}, \text{ } C_{DRV} = 0 \text{ nF}, \text{ } \text{R}_{MIN\_TOFF} = 10 \text{ k}\Omega, \\ \text{V}_{TRIG/DIS} = 0 \text{ V}, \text{ } f_{CS} = 100 \text{ kHz}, \text{ } \text{DC}_{CS} = 50\%, \text{ } \text{V}_{CS\_high} = 4 \text{ V}, \text{ } \text{V}_{CS\_low} = -1 \text{ V} \text{ unless otherwise noted}) \end{array}$

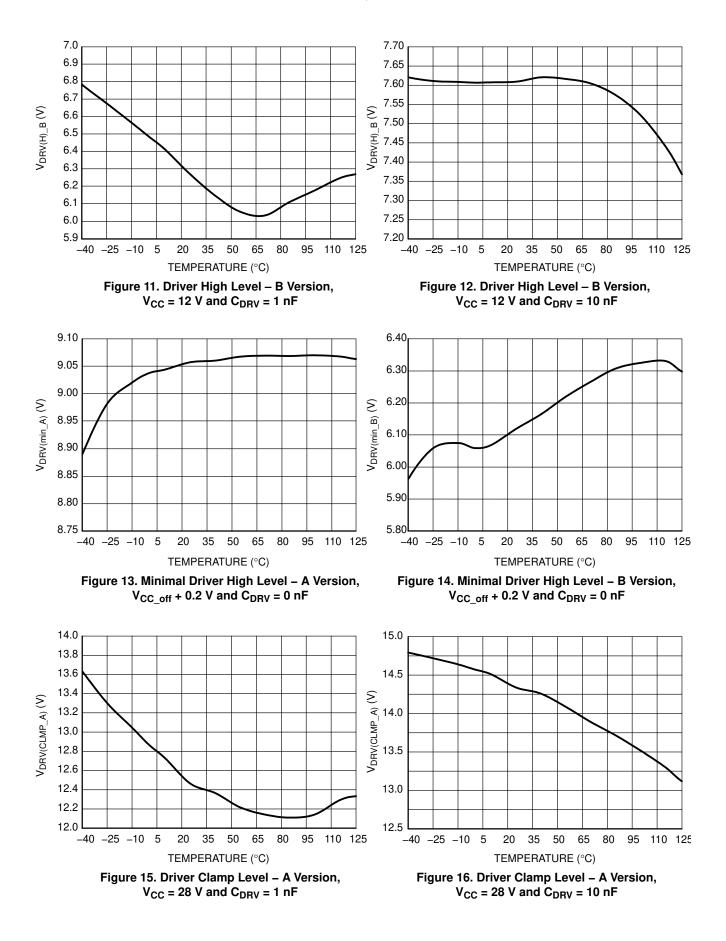

| Symbol                                    | Rating                                                                                                                                                              | Pin   | Min  | Тур | Max   | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|-------|------|

| DRIVE OUTPUT                              | •                                                                                                                                                                   |       |      |     |       |      |

| I <sub>DRV_pk(source)</sub>               | Output source peak current                                                                                                                                          | 8     | -    | 2.5 | -     | Α    |

| IDRV pk(sink)                             | Output sink peak current                                                                                                                                            | 8     | -    | 5   | -     | Α    |

| V <sub>DRV(min_A)</sub>                   | Minimum drive output voltage for A version ( $V_{CC} = V_{CC_{off}} + 200 \text{ mV}$ )                                                                             | 8     | 8.3  | _   | -     | V    |

| V <sub>DRV(min_B)</sub>                   | Minimum drive output voltage for B version ( $V_{CC} = V_{CC_{off}} + 200 \text{ mV}$ )                                                                             | 8     | 4.5  | _   | -     | V    |

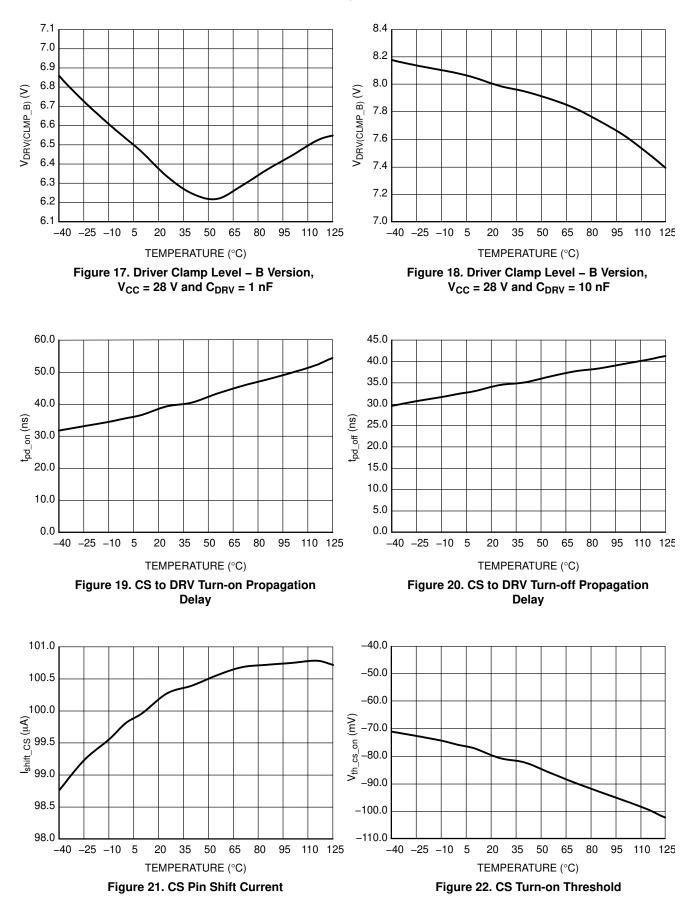

| V <sub>DRV(CLMP_A)</sub>                  | Driver clamp voltage for A version (12 < V <sub>CC</sub> < 28, C <sub>DRV</sub> = 1 nF)                                                                             | 8     | 10   | 12  | 14.3  | V    |

| V <sub>DRV(CLMP_B)</sub>                  | Driver clamp voltage for B version (12 < V <sub>CC</sub> < 28, C <sub>DRV</sub> = 1 nF)                                                                             | 8     | 5    | 6   | 8     | V    |

| CS INPUT                                  |                                                                                                                                                                     |       |      |     |       |      |

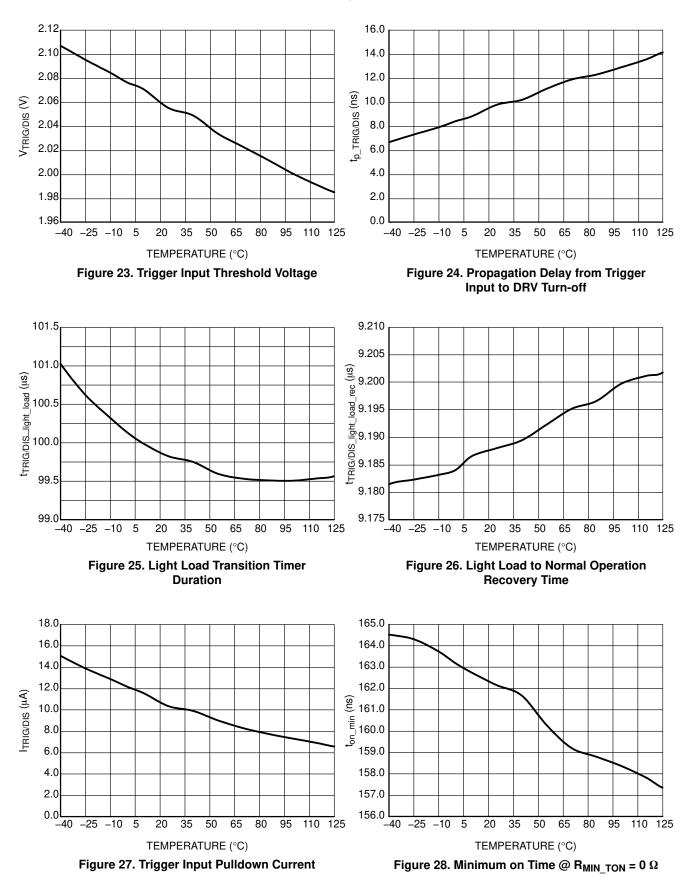

| t <sub>pd_on</sub>                        | The total propagation delay from CS input to DRV output turn on (V <sub>CS</sub> goes down from 4 V to $-1$ V, t <sub>f_CS</sub> = 5 ns, COMP pin connected to GND) | 5, 8  | -    | 60  | 90    | ns   |

| t <sub>pd_off</sub>                       | The total propagation delay from CS input to DRV output turn off ( $V_{CS}$ goes up from –1 V to 4 V, $t_{r_CS}$ = 5 ns, COMP pin connected to GND), (Note 1)       | 5, 8  | -    | 40  | 55    | ns   |

| I <sub>shift_CS</sub>                     | Current sense input current source (V <sub>CS</sub> = 0 V)                                                                                                          | 5     | 95   | 100 | 105   | μΑ   |

| V <sub>th_cs_on</sub>                     | Current sense pin turn-on input threshold voltage                                                                                                                   | 5, 8  | -120 | -85 | -50   | mV   |

| V <sub>th_cs_off</sub>                    | Current sense pin turn-off threshold voltage, COMP pin connected to GND (Note 1)                                                                                    | 5, 8  | -1   | -   | 0     | mV   |

| G <sub>comp</sub>                         | Compensation inverter gain                                                                                                                                          | 5,6,8 |      | _1  |       | -    |

| I <sub>CS_Leakage</sub>                   | Current Sense input leakage current, $V_{CS} = 200 V$                                                                                                               | 5     | -    | -   | 1     | μA   |

| <b>FRIGGER/DISABLE</b>                    | E INPUT                                                                                                                                                             |       |      |     |       |      |

| t <sub>TRIG/DIS_pw_min</sub>              | Minimum trigger pulse width (Note 1)                                                                                                                                | 4     | 30   | -   | -     | ns   |

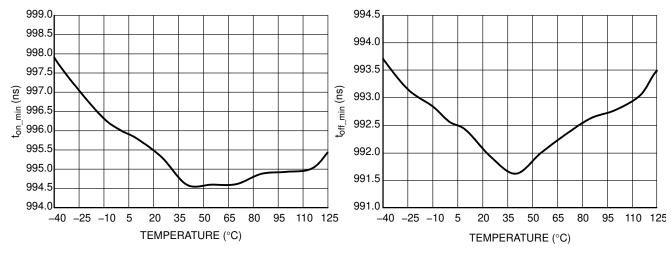

| V <sub>TRIG/DIS</sub>                     | Trigger input threshold voltage (V <sub>TRIG/DIS</sub> goes up)                                                                                                     | 4     | 1.5  | -   | 2.5   | V    |

| t <sub>p_TRIG</sub> /DIS                  | Propagation delay from trigger input to the DRV output $(V_{TRIG/DIS} \text{ goes up from 0 to 5 V}, t_{r_TRIG/DIS} = 5 \text{ ns})$                                | 4     | -    | 13  | 30    | ns   |

| tTRIG/DIS_light_load                      | Light load turn off filter duration                                                                                                                                 | 4     | 70   | 100 | 130   | μs   |

| t <sub>TRIG/DIS_light_</sub><br>load_rec. | IC operation recovery time when leaving light load disable mode $(V_{TRIG/DIS} \text{ goes down from 5 to } 0 \text{ V}, t_{f_TRIG/DIS} = 5 \text{ ns})$            | 4     | -    | -   | 10    | μs   |

| t <sub>TRIG</sub> /DIS_blank              | Blanking time of trigger during DRV rising edge ( $V_{CS} < V_{th_{cs_{on}}}$ , single pulse on trigger $t_{TRIG/DIS_{DW}} = 50$ ns)                                | 4     | -    | 120 | -     | ns   |

| I <sub>TRIG/DIS</sub>                     | Trigger input pull down current (V <sub>TRIG/DIS</sub> = 5 V)                                                                                                       | 4     | -    | 10  | -     | μA   |

| on_min AND t <sub>off_min</sub>           | n ADJUST                                                                                                                                                            |       |      |     |       |      |

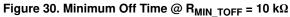

| t <sub>on_min</sub>                       | Minimum $t_{on}$ period ( $R_{MIN_{TON}} = 0 \Omega$ )                                                                                                              | 3     | -    | 130 | -     | ns   |

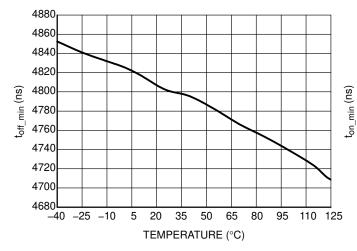

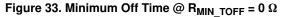

| t <sub>off_min</sub>                      | Minimum $t_{off}$ period ( $R_{MIN_{TOFF}} = 0 \Omega$ )                                                                                                            | 2     | 560  | 600 | 690   | ns   |

| t <sub>on_min</sub>                       | Minimum $t_{on}$ period ( $R_{MIN}$ TON = 10 k $\Omega$ )                                                                                                           | 3     | 0.9  | 1.0 | 1.1   | μs   |

| t <sub>off_min</sub>                      | Minimum t <sub>off</sub> period ( $R_{MIN_{TOFF}} = 10 \text{ k}\Omega$ )                                                                                           | 2     | 0.9  | 1.0 | 1.1   | μs   |

| tta                                       | Minimum $t_{on}$ period ( $R_{MIN_{TON}} = 50 \text{ k}\Omega$ )                                                                                                    | 3     | -    | 4.8 | -     | μs   |

| t <sub>on_min</sub>                       |                                                                                                                                                                     | 2     | _    | 4.8 | _     | μs   |

| t <sub>off_min</sub>                      | Minimum $t_{off}$ period ( $R_{MIN_{TOFF}} = 50 \text{ k}\Omega$ )                                                                                                  | 2     | _    |     |       | P    |

|                                           |                                                                                                                                                                     | 3     | 8.64 | 9.6 | 10.56 | μs   |

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Guaranteed by design.

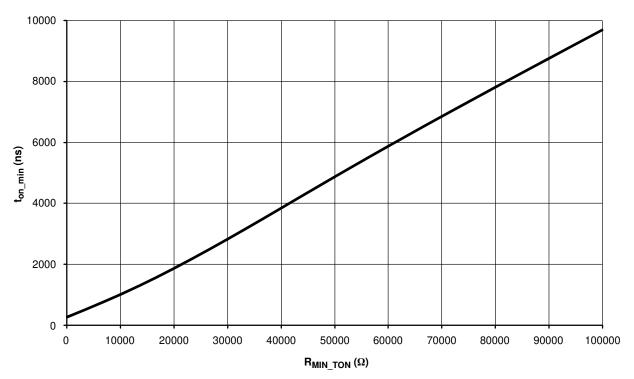

Guaranteed by design and verified by characterization, see Figure 4. t<sub>on\_min</sub> on R<sub>MIN\_TON</sub> dependency.

### **TYPICAL CHARACTERISTICS**

Figure 4.  $t_{on\ min}$  on  $R_{MIN\ TON}$  Dependency

Figure 29. Minimum On Time @  $R_{MIN TON} = 10 \text{ k}\Omega$

625.0 620.0 615.0 610.0 min (ns) 605.0 0.000 أَحَّ 595.0 590.0 585.0 65 95 110 125 -40 -25 -10 5 20 35 50 80 TEMPERATURE (°C)

Figure 32. Minimum On Time @  $\text{R}_{\text{MIN}_{}\text{TON}}$  = 50 k $\Omega$

#### **APPLICATION INFORMATION**

#### **General Description**

The NCP4304A/B is designed to operate either as a standalone IC or as a companion IC to a primary side controller to help achieve efficient synchronous rectification in switch mode power supplies. This controller features a high current gate driver along with high-speed logic circuitry to provide appropriately timed drive signals to a synchronous rectification MOSFET. With its novel architecture, the NCP4304A/B has enough versatility to keep the synchronous rectification efficient under any operating mode.

The NCP4304A/B works from an available bias supply with voltage range from 10.4 V to 28 V (typical). The wide  $V_{CC}$  range allows direct connection to the SMPS output voltage of most adapters such as notebook and LCD TV adapters. As a result, the NCP4304A/B simplifies circuit operation compared to other devices that require specific bias power supplies (e.g. 5 V). The high voltage capability of the V<sub>CC</sub> is also a unique feature designed to allow operation for a broader range of applications.

Precise turn off threshold of the current sense comparator together with accurate offset current source allows the user to adjust for any required turn off current threshold of the SR MOSFET switch using a single resistor. Compared to other SR controllers that provide turn off thresholds in the range of -10 mV to -5 mV, the NCP4304A/B offers a turn off threshold of 0 mV that in combination with a low R<sub>DS(on)</sub> SR MOSFET significantly reduces the turn off current threshold and improves efficiency.

To overcome issues after turn on and off events, the NCP4304A/B provides adjustable minimum on time and off time blanking periods. Blanking times can be adjusted independently of IC  $V_{CC}$  using resistors connected to GND. If needed, blanking periods can be modulated using additional components.

An ultrafast trigger input helps to implement synchronous rectification systems in CCM applications (like CCM flyback or forward). The time delay from trigger input to driver turn off event is 10 ns (typicaly). Additionally, the trigger input can be used to disable the IC and activate a low consumption standby mode. This feature can be used to decrease standby consumption of an SMPS.

Finally, the NCP4304A/B features a special input that can be used to automatically compensate for SR MOSFET parasitic inductance effect. This technique achieves the maximum available on-time and thus optimizes efficiency when a MOSFET in standard package (like TO-220 or TO247) is used. If a SR MOSFET in SMT package with negligible inductance is used, the compensation input is connected to GND pin.

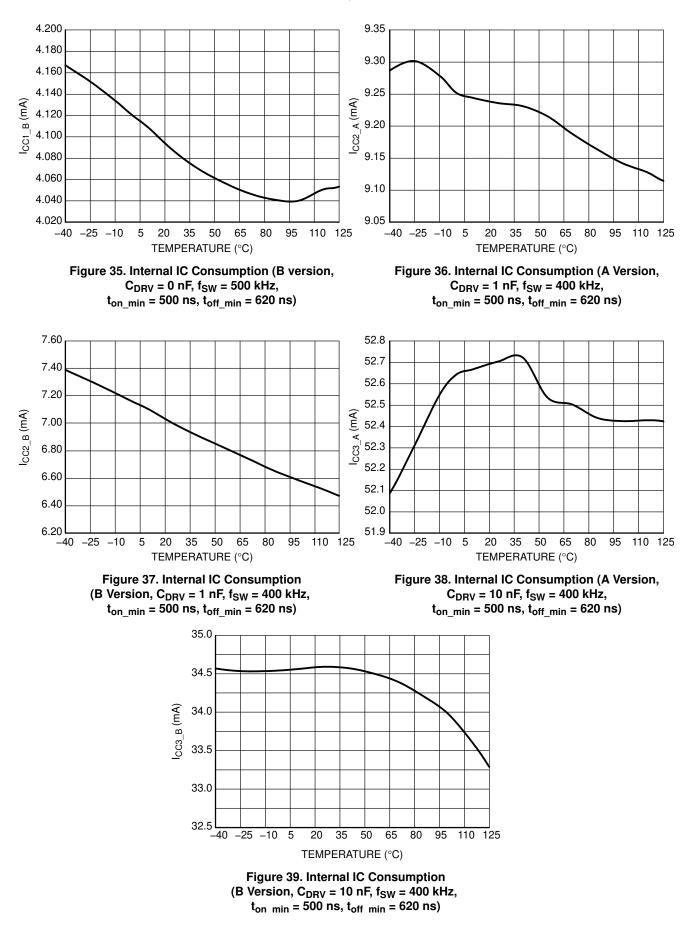

## Zero Current Detection and Parasitic Inductance Compensation

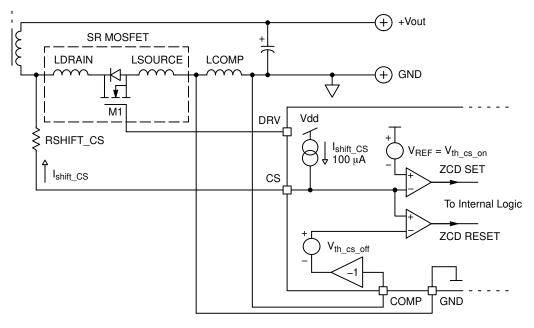

Figure 40 shows the internal connection of the ZCD circuitry on the current sense input. The synchronous rectification MOSFET is depicted with it's parasitic inductances to demonstrate operation of the compensation system.

Figure 40. ZCD Sensing Circuitry Functionality

When the voltage on the secondary winding of the SMPS reverses, the body diode of M1 starts to conduct current and the voltage of M1's drain drops approximately to -1 V. The CS pin sources current of 100  $\mu$ A that creates a voltage drop on the RSHIFT\_CS resistor. Once the voltage on the CS pin is lower than V<sub>th\_cs\_on</sub> threshold, M1 is turned on. Because of parasitic impedances, significant ringing can occur in the application. To overcome sudden turn-off due to mentioned ringing, the minimum conduction time of the SR MOSFET is activated. Minimum conduction time can be adjusted using R<sub>MIN TON</sub> resistor.

The SR MOSFET is turned-off as soon as the voltage on the CS pin is higher than  $V_{th\_cs\_off}$ . For the same ringing reason, a minimum off time timer is asserted once the turn-off is detected. The minimum off time can be externally adjusted using  $R_{MIN\_TOFF}$  resistor. MOSFET M1 conducts when the secondary current decreases, therefore the turn-off time depends on its  $R_{DS(on)}$ . The 0 mV threshold provides an optimum switching period usage while keeping enough time margin for the gate turn off. The RSHIFT\_CS resistor provides the designer with the possibility to modify (increase) the actual turn-off current threshold.

Figure 41. ZCD Comparators Thresholds and Blanking Periods Timing

If no RSHIFT\_CS resistor is used, the turn-on and turn-off thresholds are fully given by the CS input specification (please refer to parametric table). Once non-zero RSHIFT\_CS resistor is used, both thresholds move down (i.e. higher MOSFET turn off current) as the CS pin offset current causes a voltage drop that is equal to:

$$V_{\text{RSHIFT CS}} = \text{RSHIFT}_{\text{CS}} \cdot I_{\text{shift CS}}$$

(eq. 1)

Final turn-on and turn-off thresholds can be then calculated as:

$$V_{\text{CS\_turn\_on}} = V_{\text{th\_cs\_on}} - \left(\text{RSHIFT\_CS} \cdot I_{\text{shift\_CS}}\right) \quad (\text{eq. 2})$$

$$V_{CS\_turn\_off} = V_{th\_cs\_off} - (RSHIFT\_CS \cdot I_{shift\_CS}) \quad (eq. 3)$$

Note that RSHIFT\_CS impact on turn-on threshold is less critical compare to turn-off threshold.

If using a SR MOSFET in TO–220 package (or other package which features leads), the parasitic inductance of the package leads causes a turn-off current threshold increase. This is because current that flows through the SR MOSFET has quite high di(t)/dt that induces error voltage on the SR MOSFET leads inductance. This error voltage, that is proportional to the secondary current derivative, shifts the CS input voltage to zero when significant current still flows through the channel. Zero current threshold is thus detected when current still flows through the SR MOSFET channel – please refer to Figure 42 for better understanding. As a result, the SR MOSFET is turned-off prematurely and the efficiency of the SMPS is not optimized.

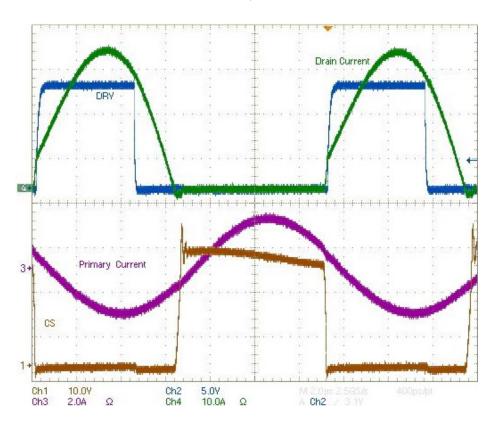

Figure 42. Waveforms from SR System Using MOSFET in TO–220 Package Without Parasitic Inductance Compensation – SR MOSFET Channel Conduction Time is Reduced

Note that the efficiency impact of the error caused by parasitic inductance increases with lower  $R_{DS(on)}$  MOSFETs and/or higher operating frequency.

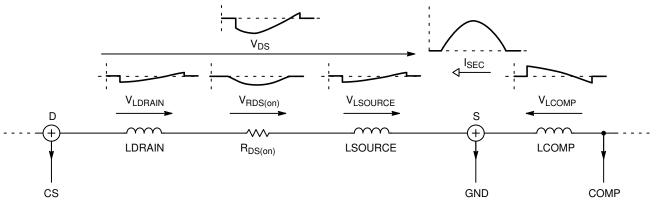

The NCP4304A/B offers a way to compensate for MOSFET parasitic inductances effect – refer to Figure 43.

Figure 43. Package Parasitic Inductances Compensation Principle

Dedicated input (COMP) offers the possibility to use an external compensation inductance (wire strap or PCB). If the value of this compensation inductance is LCOMP = LDRAIN + LSOURCE, the compensation voltage created on this inductance is exactly the same as the sum of error voltages created on drain and source parasitic inductances i.e.  $V_{LDRAIN} + V_{LSOURCE}$ . The internal analog inverter (Figure 40) inverts compensation voltage  $V_{LCOMP}$  and offsets the current sense comparator turn-off threshold. The

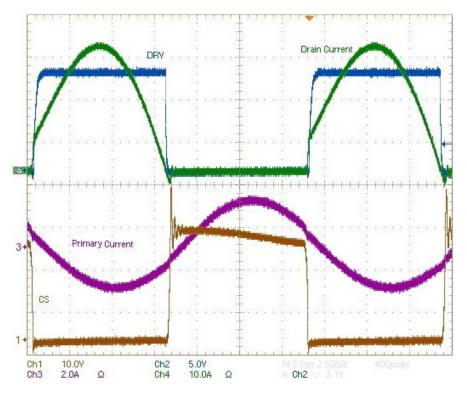

current sense comparator thus "sees" between its terminals a voltage that would be seen on the SR MOSFET channel resistance in case the lead inductances wouldn't exist. The current sense comparator of the NCP4304A/B is thus able to detect the secondary current zero crossing very precisely. More over, the secondary current turn-off threshold is then di(t)/t independent thus the NCP4304A/B allows to increase operating frequency of the SR system. One should note that the parasitic resistance of compensation inductance should be as low as possible compared to the SR MOSFET channel and leads resistance otherwise compensation is not efficient. Typical value of compensation inductance for a TO-220 package is 7 nH. Waveforms from the application with compensated SR system can be seen in Figure 44. One can see the conduction time has been significantly increased and turn-off current reduced.

Figure 44. Waveforms SR System Using MOSFET in TO-220 Package with Parasitic Inductance Compensation – SR MOSFET Channel Conduction Time is Optimized

Note that using the compensation system is only beneficial in applications that are using a low  $R_{DS(on)}$  MOSFET in non-SMT package. Using the compensation method allows for optimized efficiency with a standard TO–220 package that in turn results in reduced costs, as the SMT MOSFETs usually require reflow soldering process and more expensive PCB.

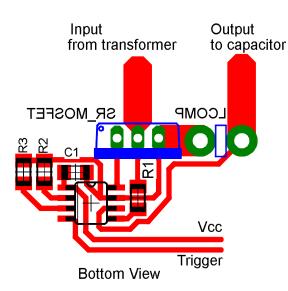

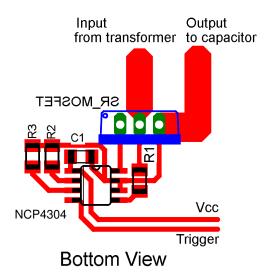

From the above paragraphs and parameter tables it is evident that turn-off threshold precision is quite critical. If we consider a SR MOSFET with  $R_{DS(on)}$  of 1 mQ, the 1 mV error voltage on the CS pin results in a 1 A turn-off current threshold difference. Thus the PCB layout is very critical when implementing the SR system. Note that the CS turn-off comparator as well as compensation inputs are referred to the GND pin. Any parasitic impedance (resistive or inductive – talking about mQ and nH values) can cause a high error voltage that is then evaluated by the CS comparator. Ideally the CS turn-off comparator should detect voltage that is caused by secondary current directly on the SR MOSFET channel resistance. Practically this is not possible because of the bonding wires, leads and soldering. To assure the best efficiency results, a Kelvin connection of the SR controller to the power circuitry should be implemented (i.e. GND pin should be connected to the SR MOSFET source soldering point and current sense pin should be connected to the SR MOSFET drain soldering point). Any impact of PCB parasitic elements on the SR controller functionality is then avoided. Figures 45 and 46 show examples of SR system layouts using parasitic inductance compensation (i.e. for low RDS(on) MOSFET in TO-220 package ) and not using compensation (i.e. for higher R<sub>DS(on)</sub> MOSFET in TO-220 package or SMT package MOSFETs).

#### Figure 45. Recommended Layout When Parasitic Inductance Compensation is Used

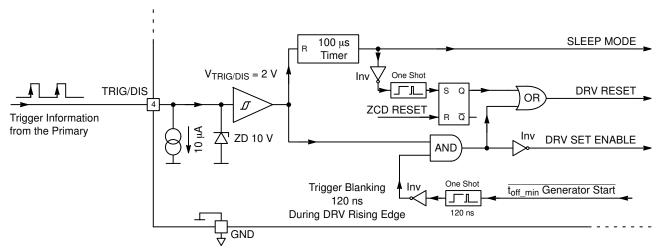

#### Trigger/Disable Input

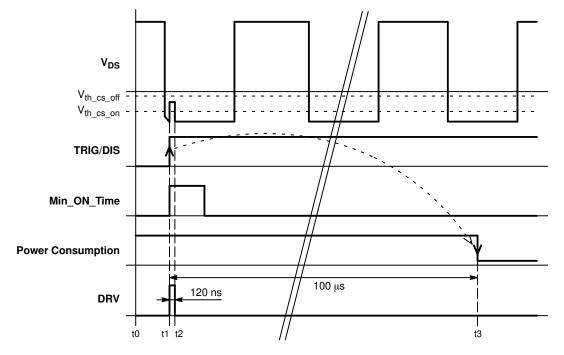

The NCP4304A/B features an ultrafast trigger input that exhibits a typically of 10 ns delay from its activation to the turn-off of the SR MOSFET. The main purpose of this input is to turn-off the SR MOSFET in applications operating in CCM mode via a signal coming from the primary side or direct synchronization SR MOSFET turn-on and turn-off event according to primary controller signals. The NCP4304A/B operation can be disabled using the TRIG/DIS input. If the TRIG/DIS input is pulled high

#### Figure 46. Recommended Layout When Parasitic Inductance Compensation is Not Used

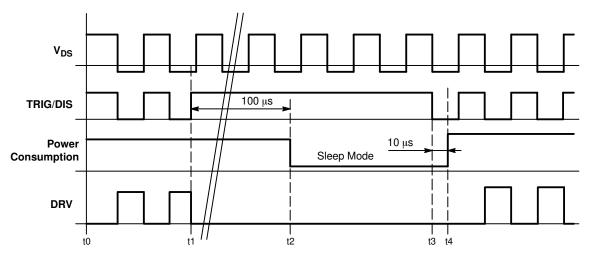

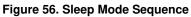

(above 2.5 V) the driver is disabled immediately, except during DRV rising edge when TRIG/DIS is blanked for 120 ns. If the trigger signal is high for more than 100  $\mu$ s the driver enters standby mode. The IC consumption is reduced below 100  $\mu$ A during the standby mode. The device recovers operation in 10  $\mu$ s when the trigger voltage is increased to exit standby mode. TRIG/DIS input is superior to CS input except blanking period. TRIG/DIS signal turns-OFF the SR MOSFET or disable its turn-ON if TRIG/DIS is pulled above V<sub>TRIG/DIS</sub>.

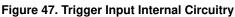

Figure 48 depicts driver turn-ON events. Turn-ON of the SR MOSFET is possible if CS ( $V_{DS}$ ) signal falls under  $V_{th\_cs\_on}$  threshold and TRIG/DIS is pulled LOW (t1 to t3 time interval).

When the CS ( $V_{DS}$ ) reached the  $V_{th\_cs\_on}$  threshold and TRIG/DIS is pulled HIGH the driver stays LOW (t6, t7 time markers) if the TRIG/DIS is HIGH. If the TRIG/DIS is

pulled LOW and CS ( $V_{DS}$ ) is still under  $V_{th\_cs\_on}$  threshold then the DRV is turned-ON (t7 marker).

Time markers t14 and t15 in Figure 48 demonstrate situation when CS ( $V_{DS}$ ) is above  $V_{th\_cs\_on}$  threshold and TRIG/DIS is pulled down. In this case the driver stays LOW (t12 to t15 marker).

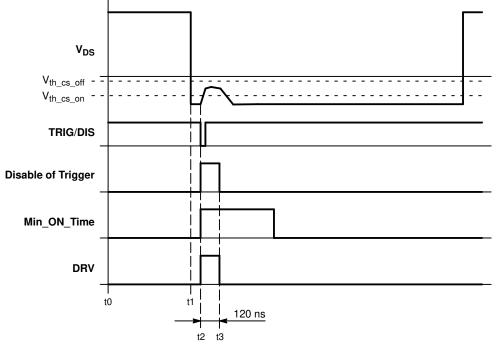

The TRIG/DIS input is blanked for 120 ns after DRV set signal to avoid undesirable behavior during SR MOSFET turn-ON event. The blanking time in combination with high threshold voltage (2 V) prevent triggering on ringing and spikes that are present on the TRIG/DIS input pin during the SR MOSFET turn-on process. DRV response to the short needle pulse on the TRIG/DIS pin is depicted in Figure 49 – this short pulse turns-on the DRV for 120 ns.

Figure 49. Trigger Needle Pulse and Trigger Blank Sequence

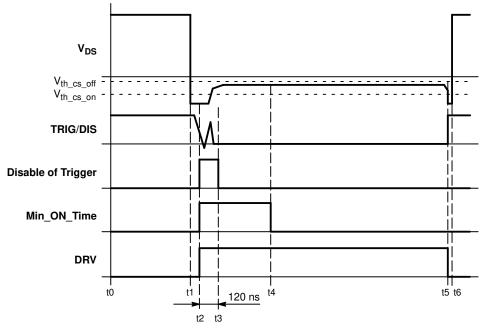

Advantage of the trigger blanking time during DRV turn-ON event is evident from Figure 50. Rising edge of the DRV signal may cause additional spikes on the TRIG/DIS input. These spikes, in combination with ultra-fast performance of the trigger logic, could turn-OFF the SR MOSFET in inappropriate time. Implementation of the trigger blanking time period helps to avoid such situation.

Figure 50. Trigger Blanking Masked-out Noise in Trigger Signal During Switch-ON Event

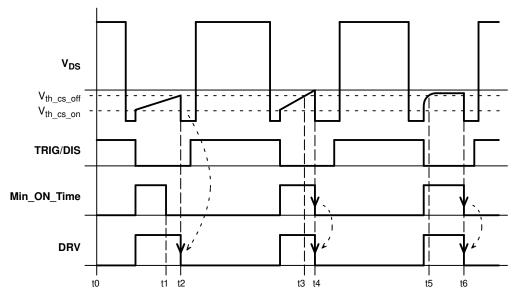

Figure 51 depicts driver turn-OFF events in details. If the CS ( $V_{DS}$ ) stays below  $V_{th\_cs\_off}$  threshold driver is turned-OFF according to rising edge of the TRIG/DIS signal. TRIG/DIS can turn-OFF the driver also during minimum-ON time period (time marker t2 and t3 in Figure 51).

Figure 52 depicts another driver turn-OFF events in details. Driver is turned-OFF according to the CS ( $V_{DS}$ ) signal (t2 marker) and only after minimum-ON time elapsed. TRIG/DIS signal needs to be LOW during this event. If the CS ( $V_{DS}$ ) voltage reaches  $V_{th_cs_off}$  threshold before minimum-ON time period ends and TRIG/DIS pin is LOW the DRV is turned-OFF on the falling edge of the minimum-ON time period (t4 and t6 time markers in Figure 52).

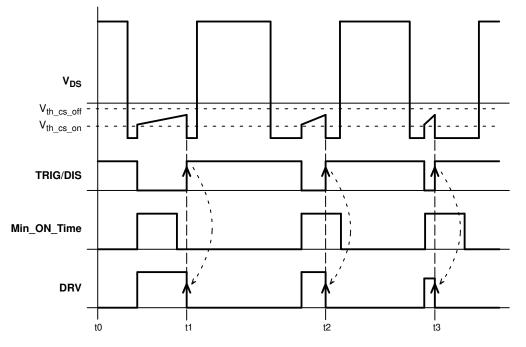

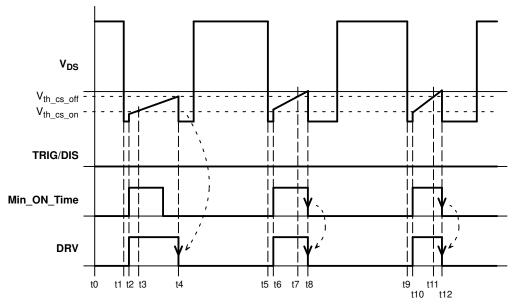

Figure 53 depicts performance of the NCP4304A/B controller when trigger pin is permanently pulled LOW. In this case the DRV is turned ON and OFF according to the CS ( $V_{DS}$ ) signal. The driver can be turned off only after minimum-ON time period elapsed. The driver is turned-ON in the time when CS ( $V_{DS}$ ) reaches  $V_{th_cs_on}$  threshold

(t1-t2, t5-t6, t9-t10 markers). DRV is turned-OFF if CS (V<sub>DS</sub>) signal reaches  $V_{th_cs_off}$  threshold (t4 marker). The DRV ON-time is prolonged till minimum-ON time period falling edge if the CS (V<sub>DS</sub>) reaches  $V_{th_cs_off}$  before minimum-ON time period elapsed (t7-t8, t11-t12 markers).

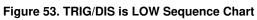

Figure 54 depicts entering into the sleep mode. If the TRIG/DIS is pulled up for more than 100  $\mu$ s the NCP4304A/B enters low consumption mode. The DRV stays LOW (disabled) during entering sleep mode.

Figure 55 shows sleep mode transition 2nd case – i.e. TRIG/DIS rising edge comes during the trigger blank period.

Figure 56 depicts entering into sleep mode and wake-up sequence.

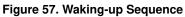

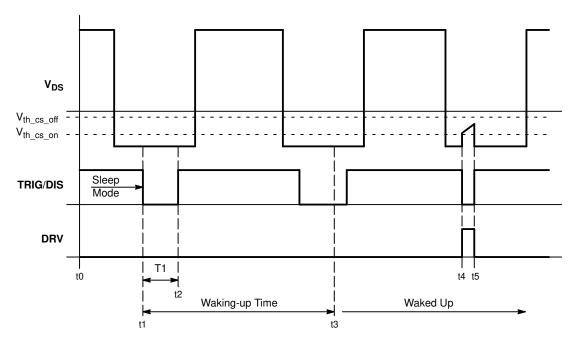

Figures 57 and 58 show wake-up situations in details. If the NCP4304A/B is in sleep mode and TRIG/DIS is pulled LOW NCP4304A/B requires up to 10  $\mu$ s period to recover all internal circuitry to normal operation mode. The driver is then enabled in the next cycle of CS (V<sub>DS</sub>) signal only. The DRV stays LOW during waking-up time period.

Figure 51. Driver Turn-OFF Events Based on the TRIG/DIS Input

Figure 52. Driver OFF Sequence Chart 2

Figure 55. TRIG/DIS from LOW to HIGH Sequence 2

Figure 59 shows IC behavior in case the trigger signal features two pulses during one cycle of the  $V_{DS}$  (CS) signal. TRIG/DIS enables driver at time t1 and DRV turns ON because the  $V_{DS}$  voltage is under  $V_{th_cs_on}$  threshold voltage. The trigger signal and consequently DRV output fall down in time t2. The minimum OFF time generator is triggered in time t2. TRIG/DIS drops down to LOW level in time t3 but there is still minimum OFF time sequence present so the DRV output stays low. When the minimum OFF time

sequence elapses in time t4 the DRV is turned ON. In time t5 Trigger signal rises up and terminates this cycle of the CS signal in time t5. Next cycle starts in time t6. Trigger enables DRV and  $V_{DS}$  is under  $V_{th\_cs\_on}$  threshold voltage so DRV turns ON in time t6. TRIG/DIS signal rises up to HIGH level in time t7, consequently DRV turns OFF and this starts minimum OFF time generator. Because minimum OFF time period is longer then the rest of time to the end of cycle of  $V_{DS}$  – DRV is disabled.

Figure 59. IC Behavior when Multiple Trigger Pulses Appear on TRIG/DIS Input

Note that the TRIG/DIS input is an ultrafast input that is sensitive even to very narrow voltage pulses. Thus it is wise to keep this input on a low impedance path and provide it with a clean triggering signal in the time this input is enabled by internal logic.

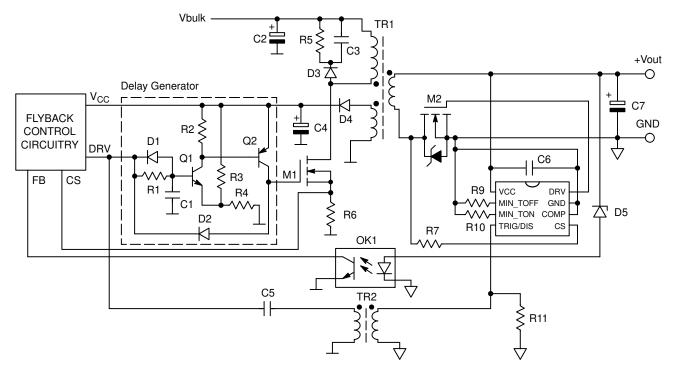

A typical application schematic of a CCM flyback converter with the NCP4304A/B driver can be seen in Figure 60. In this application the trigger signal is taken directly from the flyback controller driver output and transmitted to the secondary side by pulse transformer TR2. Because the TRIG/DIS input is edge sensitive, it is not necessary to transmit the entire primary driver pulse to the secondary. The coupling capacitor C5 is used to allow pulse transformer core reset and also to prepare a needle pulse (a pulse with width lower than 100 ns) to be transmitted to the NCP4304A/B TRIG/DIS input. The advantage of needle trigger pulse usage is that the required volt-second product of the pulse transformer is very low and that allows the designer to use very small and cheap magnetics. The trigger transformer can be for instance prepared on a small toroidal ferrite core with diameter of 8 mm. Proper safety insulation between primary and secondary sides can be easily assured by using triple insulated wire for one or even both windings.

The primary MOSFET gate voltage rising edge is delayed by external circuitry consisting of transistors Q1, Q2 and surrounding components. The primary MOSFET is thus turned-on with a slight delay so that the secondary controller turns-off the SR MOSFET by trigger signal prior to the primary switching. This method reduces the commutation losses and the SR MOSFET drain voltage spike, which results in improved efficiency.

It is also possible to use capacitive coupling (use additional capacitor with safety insulation) between the primary and secondary to transmit the trigger signal. We do not recommend this technique as the parasitic capacitive currents between primary and secondary may affect the trigger signal and thus overall system functionality.

Figure 60. Typical Application Schematic when NCP4304A/B is Used in CCM Flyback Converter

#### ton\_min and toff\_min Adjustment

The NCP430 $\overline{4}$ A/B offers adjustable minimum ON and OFF time periods that ease the implementation of the synchronous rectification system in a power supply. These

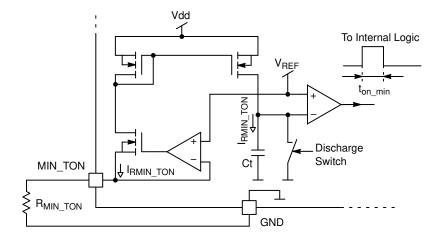

timers avoid false triggering on the CS input after the MOSFET is turned on or off. The adjustment is based on an internal timing capacitance and external resistors connected to the GND pin – refer to Figure 61 for better understanding.

Current through the  $R_{MIN\_TON}$  adjust resistor can be calculated as:

$$I_{RMIN\_TON} = \frac{V_{REF}}{R_{MIN\_TON}}$$

(eq. 4)

As the same current is used for the internal timing capacitor  $(C_t)$  charging, one can calculate the minimum on-time duration using this equation.

$$t_{on\_min} = C_{t} \cdot \frac{V_{REF}}{I_{RMIN\_TON}} = C_{t} \cdot \frac{\frac{V_{REF}}{V_{REF}}}{R_{MIN\_TON}}$$

(eq. 5)

= C\_{t} \cdot R\_{MIN\\_TON}

• •

As can be seen from Equation 5, the minimum ON and OFF times are independent of the  $V_{REF}$  or VCC level. The