Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High and Low Side Gate Driver, High Performance, 700 V, with 3.5 A Source and 3 A Sink Currents

NCP51530 is a 700 V high side and low side driver with 3.5 A source & 3 A sink current drive capability for AC–DC power supplies and inverters. NCP51530 offers best in class propagation delay, low quiescent current and low switching current at high frequencies of operation. This device is tailored for highly efficient power supplies operating at high frequencies. NCP51530 is offered in two versions, NCP51530A/B. NCP51530A has a typical 60 ns propagation delay, while NCP51530B has a typical propagation delay of 25 ns. NCP51530 comes in SOIC8 and DFN10 packages.

#### **Features**

- High voltage range: Up to 700 V

- NCP51530A: Typical 60 ns Propagation Delay

- NCP51530B: Typical 25 ns Propagation Delay

- Low Quiescent and Operating Currents

- 15 ns Max Rise and Fall Time

- 3.5 A Source / 3 A Sink Currents

- Under-voltage Lockout for Both Channels

- 3.3 V and 5 V Input Logic Compatible

- High dv/dt Immunity up to 50 V/ns

- Pin to Pin Compatible with Industry Standard Half-bridge ICs.

- Matched Propagation Delay (7 ns Max)

- High Negative Transient Immunity on Bridge Pin

- DFN10 Package Offers Both Improved Creepage and Exposed Pad

#### **Applications**

- High-density SMPS for Servers, Telecom and Industrial

- Half/Full-bridge & LLC Converters

- Active Clamp Flyback/Forward Converters

- Solar Inverters & Motor Controls

- Electric Power Steering

#### ON Semiconductor®

www.onsemi.com

**MARKING**

NCP51530 = Specific Device Code

x = A or B version A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week G = Pb-Free Package

(Note: Microdot may be in either location)

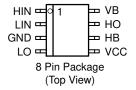

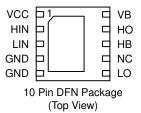

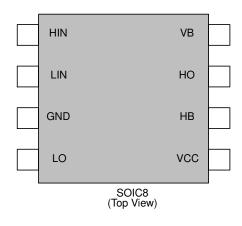

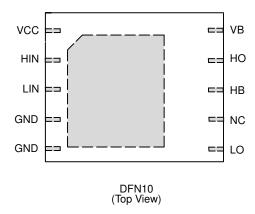

#### PINOUT INFORMATION

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 22 of this data sheet.

**Table 1. PIN DESCRIPTION SOIC 8 PACKAGE**

| Pin Out | Name | Function                  |

|---------|------|---------------------------|

| 1       | HIN  | High side input           |

| 2       | LIN  | Low side input            |

| 3       | GND  | Ground reference          |

| 4       | LO   | Low side output           |

| 5       | VCC  | Low side and logic supply |

| 6       | НВ   | High side supply return   |

| 7       | НО   | High side output          |

| 8       | VB   | High side voltage supply  |

**Table 2. PIN DESCRIPTION DFN10 PACKAGE**

| Pin Out | Name | Function                  |

|---------|------|---------------------------|

| 1       | VCC  | Low side and logic supply |

| 2       | HIN  | High side input           |

| 3       | LIN  | Low side input            |

| 4       | GND  | Ground reference          |

| 5       | GND  | Ground reference          |

| 6       | LO   | Low side output           |

| 7       | NC   | No Connect                |

| 8       | НВ   | High side supply return   |

| 9       | НО   | High side output          |

| 10      | VB   | High side voltage supply  |

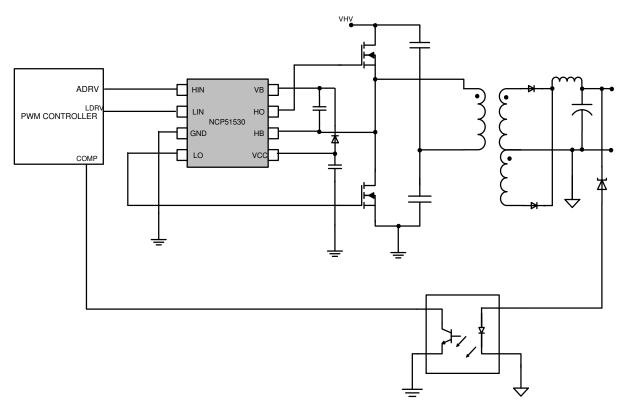

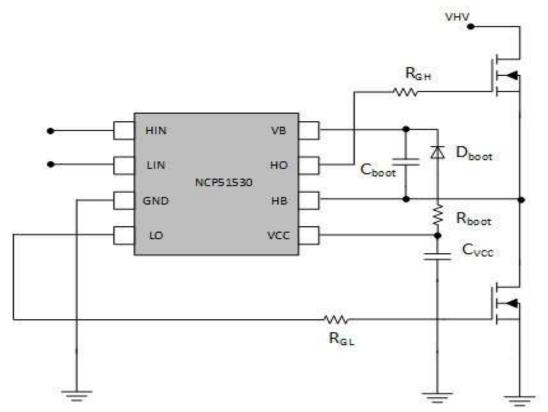

Figure 1. Simplified Applications Schematic for a Half-Bridge Converter (SOIC8)

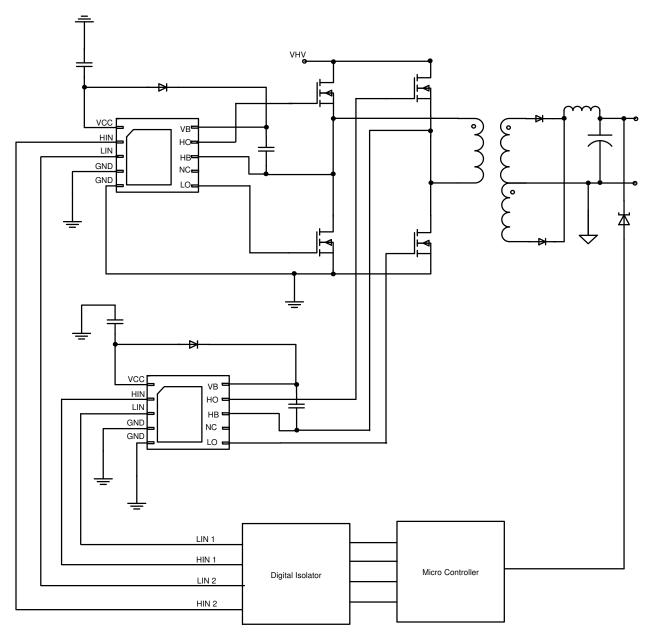

Figure 2. Simplified Applications Schematic for a Full Bridge Converter (DFN 10)

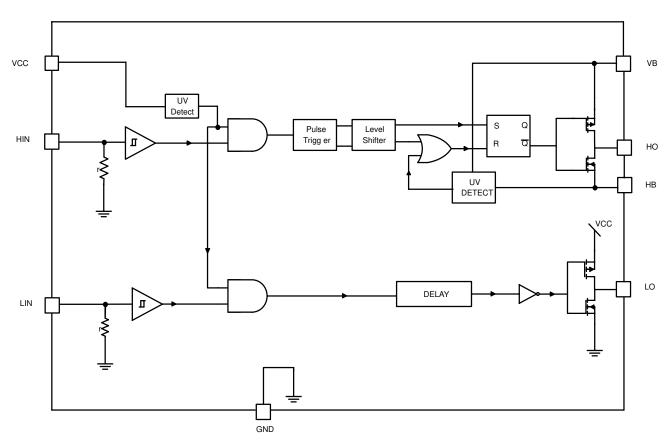

Figure 3. Internal Block Diagram for NCP51530

Table 3. ABSOLUTE MAXIMUM RATINGS All voltages are referenced to GND pin.

| Rating                                                                                                                         | Symbol                                 | Value                         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------|------|

| Input voltage range                                                                                                            | V <sub>CC</sub>                        | -0.3 to 20                    | V    |

| High side boot pin voltage                                                                                                     | V <sub>B</sub>                         | -0.3 to 720                   | V    |

| High side floating voltage                                                                                                     | $V_{B}-V_{HB}$                         | -0.3 to 20                    | V    |

| High side drive output voltage                                                                                                 | V <sub>HO</sub>                        | $V_{HB} - 0.3$ to $V_B + 0.3$ | V    |

| Low side drive output voltage                                                                                                  | $V_{LO}$                               | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Allowable hb slew rate                                                                                                         | dV <sub>HB</sub> /dt                   | 50                            | V/ns |

| Drive input voltage                                                                                                            | V <sub>LIN</sub> ,<br>V <sub>HIN</sub> | –5 to V <sub>CC</sub> + 0.3   | V    |

| Junction temperature                                                                                                           | $T_{J(MAX)}$                           | 150°                          | С    |

| Storage temperature range                                                                                                      | T <sub>STG</sub>                       | –55° to 150°                  | С    |

| ESD Capability (Note 1) Human Body Model per JEDEC Standard JESD22-A114E. Charge Device Model per JEDEC Standard JESD22-C101E. |                                        | 4000<br>1000                  | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles ONLY), Pb-Free Versions (Note 2)                                              |                                        | 260                           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

- should not be assumed, damage may occur and reliability may be affected.

1. This device series incorporates ESD protection and is tested by the following methods. ESD Human Body Model tested per AEC-Q100-002(EIA/JESD22-A114)

- ESD Charged Device Model tested per AEC-Q100-11(EIA/JESD22-C101E) Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

- 2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

**Table 4. THERMAL CHARACTERSTICS**

| Rating                                                                               |                 | Val | Unit |      |

|--------------------------------------------------------------------------------------|-----------------|-----|------|------|

| Thermal Characteristics, SOIC8 (Note 3) Thermal Resistance, Junction to Air (Note 4) | $R_{\theta JA}$ | 130 | 145  | °C/W |

| Thermal Characteristics, DFN10 Thermal Resistance, Junction to Air                   | $R_{	heta JA}$  | 45  | 72   | °C/W |

Refer to ELECTRICAL CHARACTERSTICS and APPLICATION INFORMATION for Safe Operating Area.

Values based on copper area of 645 mm² (or 1 in²) of 1 oz thickness and FR4 PCB substrate.

#### **Table 5. RECOMMENDED OPERATING CONDITIONS**

| Rating                               | Symbol                                 | Min             | Max                | Unit |

|--------------------------------------|----------------------------------------|-----------------|--------------------|------|

| Input Voltage Range                  | V <sub>CC</sub>                        | 10              | 17                 | V    |

| High Side Floating Voltage           | V <sub>B</sub> –V <sub>HB</sub>        | 10              | 17                 | V    |

| High Side Bridge pin Voltage         | V <sub>HB</sub>                        | -1              | 700                | V    |

| High Side Output Voltage             | V <sub>HO</sub>                        | V <sub>HB</sub> | V <sub>B</sub>     | V    |

| High Side Output Voltage             | V <sub>LO</sub>                        | GND             | V <sub>CC</sub>    | V    |

| Input Voltage on LIN and HIN pins    | V <sub>LIN</sub> ,<br>V <sub>HIN</sub> | GND             | V <sub>CC</sub> -2 | V    |

| Operating Junction Temperature Range | T <sub>J</sub>                         | -40             | 125                | °C   |

#### **Table 6. ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}\text{C} < \text{T}_{J} < 125^{\circ}\text{C}, \text{ V}_{CC} = \text{V}_{B} = 12\text{V}, \text{ V}_{HB} = \text{GND}, \text{ outputs are not loaded, all voltages are referenced to GND; unless otherwise noted, Typical values are at T<sub>J</sub> = 25^{\circ}\text{C}.)$

| Parameters                        | Test Conditions                                                  | Symbol                | Min | Тур   | Max  | Unit |

|-----------------------------------|------------------------------------------------------------------|-----------------------|-----|-------|------|------|

| SUPPLY SECTION                    |                                                                  |                       | _   |       |      |      |

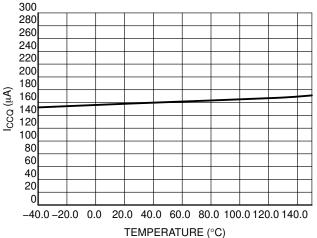

| V <sub>CC</sub> quiescent current | V <sub>LIN</sub> =V <sub>HIN</sub> =0                            | I <sub>CCQ</sub>      |     | 0.15  | 0.25 | mA   |

| V <sub>CC</sub> operating current | f = 500 kHz, C <sub>LOAD</sub> = 0                               | I <sub>CCO</sub>      |     | 2     | 2.5  | mA   |

| Boot voltage quiescent current    | V <sub>LIN</sub> = V <sub>HIN</sub> = 0 V                        | I <sub>BQ</sub>       |     | 0.1   | 0.15 | mA   |

| Boot voltage operating current    | f = 500 kHz, C <sub>LOAD</sub> = 0                               | I <sub>BO</sub>       |     | 2     | 2.5  | mA   |

| HB to GND quiescent current       | V <sub>HS</sub> = V <sub>HB</sub> = 700 V                        | I <sub>HBQ</sub>      |     | 6     | 11   | μΑ   |

| INPUT SECTION                     |                                                                  |                       |     |       |      |      |

| Input rising threshold            |                                                                  | V <sub>HIT</sub>      | 2.3 | 2.7   | 3.1  | V    |

| Input falling threshold           |                                                                  | V <sub>LIT</sub>      | 1   | 1.4   | 1.8  | V    |

| Input voltage Hysteresis          |                                                                  | V <sub>IHYS</sub>     |     | 1.3   |      | V    |

| Input pulldown resistance         | V <sub>XIN</sub> = 5 V                                           | R <sub>IN</sub>       | 100 | 175   | 250  | kΩ   |

| UNDER VOLTAGE LOCKOUT (UV         | LO)                                                              |                       | _   |       |      |      |

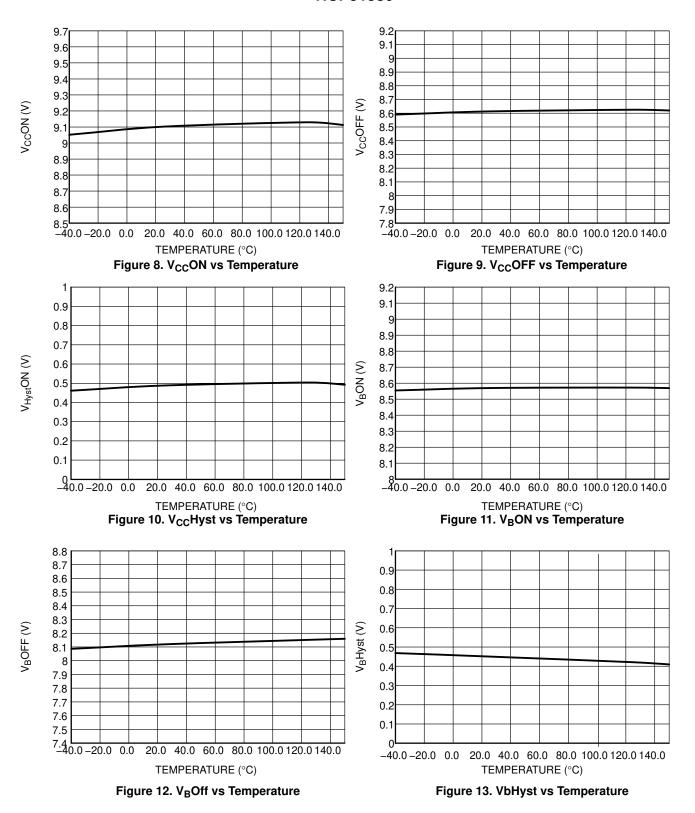

| V <sub>CC</sub> ON                | V <sub>CC</sub> Rising                                           | V <sub>CCon</sub>     | 8.6 | 9.1   | 9.6  | V    |

| V <sub>CC</sub> hysteresis        |                                                                  | V <sub>CChys</sub>    |     | 0.5   |      | V    |

| V <sub>B</sub> ON                 | V <sub>B</sub> Rising                                            | V <sub>Bon</sub>      | 8   | 8.5   | 9    | V    |

| V <sub>B</sub> hysteresis         |                                                                  | V <sub>Bhyst</sub>    |     | 0.5   |      | V    |

| High Side Startup Time            | Time between V <sub>B</sub> > UVLO & 1 <sup>st</sup><br>HO Pulse | T <sub>startup</sub>  |     |       | 10   | μs   |

| LO GATE DRIVER                    |                                                                  |                       | •   | •     |      |      |

| Low level output voltage          | I <sub>LO</sub> = 100 mA                                         | $V_{LOL}$             |     | 0.125 |      | V    |

| High level output voltage         | $I_{LO}$ = -100 mA, $V_{LOH}$ = $V_{CC}$ - $V_{LO}$              | $V_{LOH}$             |     | 0.150 |      | V    |

| Peak source current               | V <sub>LO</sub> = 0 V                                            | I <sub>LOpullup</sub> |     | 3.5   |      | Α    |

#### **Table 6. ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}\text{C} < \text{T}_{J} < 125^{\circ}\text{C}, \text{ V}_{CC} = \text{V}_{B} = 12\text{V}, \text{ V}_{HB} = \text{GND}, \text{ outputs are not loaded, all voltages are referenced to GND; unless otherwise noted, Typical values are at T<sub>J</sub> = 25^{\circ}\text{C}.)$

| Parameters                                         | Test Conditions                                                                        | Symbol                  | Min | Тур   | Max | Unit |

|----------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|-----|-------|-----|------|

| LO GATE DRIVER                                     | •                                                                                      |                         |     |       |     |      |

| Peak sink current                                  | V <sub>LO</sub> = 12 V                                                                 | I <sub>LOpulldown</sub> |     | 3.0   |     | Α    |

| HO GATE DRIVER                                     |                                                                                        |                         |     |       | -   | •    |

| Low level output voltage                           | I <sub>HO</sub> = 100 mA                                                               | V <sub>HOL</sub>        |     | 0.125 |     | V    |

| High level output voltage                          | I <sub>HO</sub> = -100 mA, V <sub>HOH</sub> = V <sub>HB</sub><br>-V <sub>HO</sub>      | V <sub>HOH</sub>        |     | 0.150 |     | V    |

| Peak source current                                | V <sub>HO</sub> = 0 V                                                                  | I <sub>HOpullup</sub>   |     | 3.5   |     | Α    |

| Peak sink current                                  | V <sub>HO</sub> = 12 V                                                                 | l <sub>HOpulldown</sub> |     | 3.0   |     | Α    |

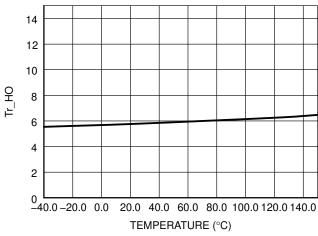

| OUTPUT RISE AND FALL TIME                          |                                                                                        |                         |     |       |     |      |

| Rise Time LO, HO                                   | C <sub>load</sub> = 1000 pF                                                            | T <sub>R</sub>          |     | 8     | 15  | ns   |

| Fall Time LO, HO                                   | C <sub>load</sub> = 1000 pF                                                            | T <sub>F</sub>          |     | 8     | 15  | ns   |

| DELAY MATCHING                                     |                                                                                        |                         |     |       |     |      |

| LI ON, HI OFF                                      | Pulse width = 1 μs                                                                     | T <sub>MON</sub>        |     |       | 7   | ns   |

| LI OFF, HI ON                                      | Pulse width = 1 μs                                                                     | T <sub>MOFF</sub>       |     |       | 7   | ns   |

| TIMING                                             |                                                                                        |                         |     |       |     |      |

| Minimum Input Filter (NCP51530A)                   | V <sub>XIN</sub> = 5 V , Input pulse width above which output change occurs.           | T <sub>FT</sub>         | 30  | 40    |     | ns   |

| PROPAGATION DELAY<br>NCP51530A                     | •                                                                                      |                         |     |       |     |      |

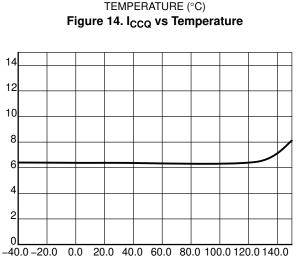

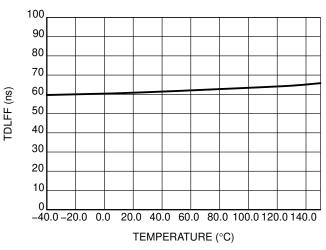

| $V_{LI}$ falling to $V_{LO}$ falling               | C <sub>load</sub> = 0, Minimum On/Off-time<br>to register as a valid change =<br>50 ns | T <sub>DLFF</sub>       |     | 60    | 100 | ns   |

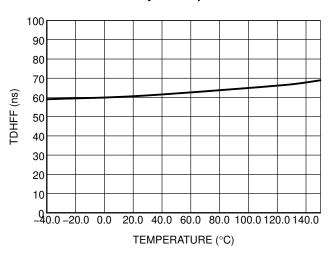

| V <sub>HI</sub> falling to V <sub>HO</sub> falling | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DHFF</sub>       |     | 60    | 100 | ns   |

| $V_{LI}$ rising to $V_{LO}$ rising                 | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DLRR</sub>       |     | 60    | 100 | ns   |

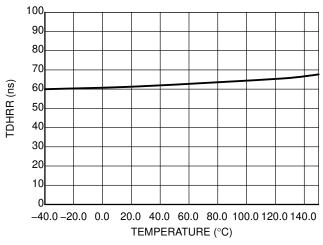

| $V_{HI}$ rising to $V_{HO}$ rising                 | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DHRR</sub>       |     | 60    | 100 | ns   |

| PROPAGATION DELAY<br>NCP51530B                     | •                                                                                      |                         | •   | •     |     |      |

| $V_{LI}$ falling to $V_{LO}$ falling               | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DLFF</sub>       |     | 25    | 40  | ns   |

| V <sub>HI</sub> falling to V <sub>HO</sub> falling | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DHFF</sub>       |     | 25    | 40  | ns   |

| $V_{LI}$ rising to $V_{LO}$ rising                 | C <sub>load</sub> = 0, Minimum On/Off–time<br>to register as a valid change =<br>50 ns | T <sub>DLRR</sub>       |     | 25    | 40  | ns   |

| $V_{HI}$ rising to $V_{HO}$ rising                 | C <sub>load</sub> = 0, Minimum On/Off-time<br>to register as a valid change =<br>50 ns | T <sub>DHRR</sub>       |     | 25    | 40  | ns   |

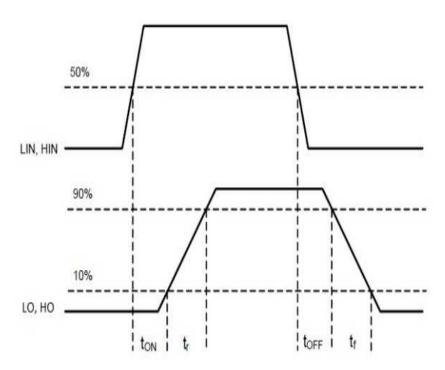

Figure 4. Propagation Delay, Rise and Fall Times

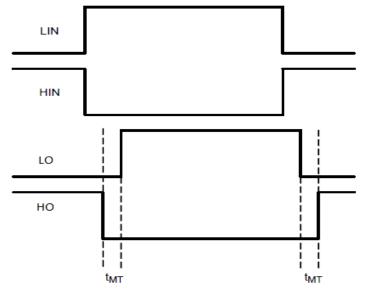

Figure 5. Delay Matching

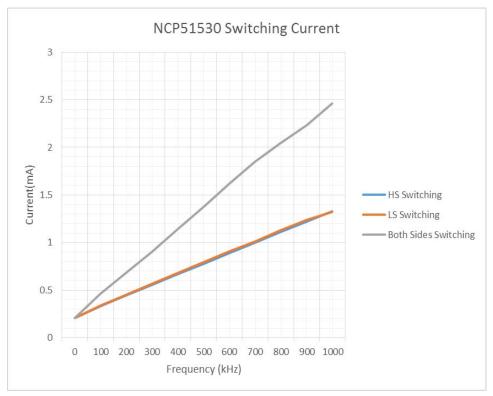

Figure 6. NCP51530 Operating Currents (No Load,  $V_{CC} = 12V$ )

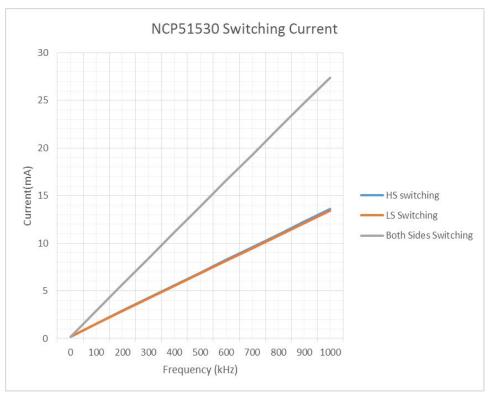

Figure 7. NCP51530 Operating Currents (1nF load,  $V_{CC} = 12V$ )

12

10

8

I<sub>HB</sub>\_LEAK (µA)

TEMPERATURE (°C) Figure 16. I<sub>HB</sub>\_Leakage vs Temperature

Figure 18. Low Side Turn on Propagation **Delay vs Temperature**

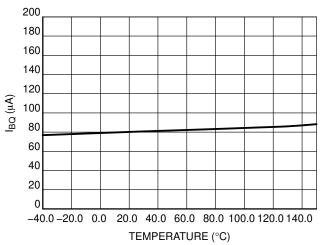

Figure 15. I<sub>BQ</sub> vs Temperature

Figure 17. Low Side Turn on Propagation **Delay vs Temperature**

Figure 19. High Side Turn off Propagation **Delay vs Temperature**

Figure 20. High Side Turn off Propagation Delay vs Temperature

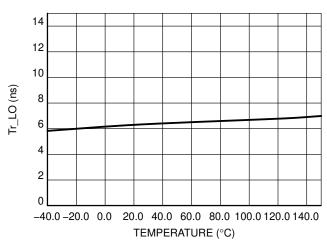

Figure 21. Low Side Rise Time vs Temperature

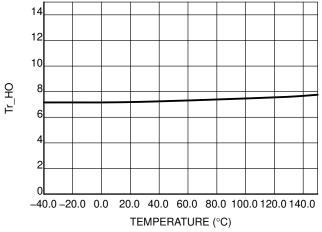

Figure 22. High Side Rise Time vs

Temperature

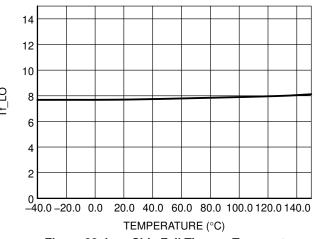

Figure 23. Low Side Fall Time vs Temperature

Figure 24. High Side Fall Time vs Temperature

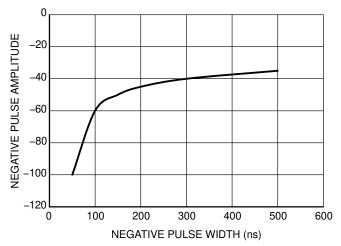

Figure 25. Typical Safe Operating Area with Negative Transient Voltage on HB Pin

#### **GENERAL DESCRIPTION**

For popular topologies like LLC, half bridge converters, full bridge converters, two switch forward converter etc. low-side high-side drivers are needed which perform the function of both buffer and level shifter. These devices can drive the gate of the topside MOSFETs whose source node is a dynamically changing node. The bias for the high side driver in these devices is usually provided through a bootstrap circuit.

In a bid to make modern power supplies more compact and efficient, power supply designers are increasingly opting for high frequency operations. High frequency operation causes higher losses in the drivers, hence reducing the efficiency of the power supply.

NCP51530 is a 700 V high side—low side driver for AC–DC power supplies and inverters. NCP51530 offers best in class propagation delay, low quiescent current and low switching current at high frequencies of operation. This device thus enables highly efficient power supplies operating at high frequencies.

NCP51530 is offered in two versions, NCP51530A/B. NCP51530A has a typical 60 ns propagation delay, while NCP51530B has propagation delay of 25 ns.

NCP51530 comes in SOIC8 and DFN10 packages. SOIC8 package of the device is pin to pin compatible with industry standard solutions.

NCP51530 has two independent input pins HIN and LIN allowing it to be used in a variety of applications. This device also includes features wherein, in case of floating input, the logic is still defined. Driver inputs are compatible with both CMOS and TTL logic hence it provides easy interface with analog and digital controllers. NCP51530 has under voltage lock out feature for both high and low side drivers which

ensures operation at correct  $V_{CC}$  and  $V_{B}$  voltage levels. The output stage of NCP51530 has 3.5 A/3 A current source/sink capability which can effectively charge and discharge a 1 nF load in 15 ns.

#### **FEATURES**

#### **INPUT STAGES**

NCP51530 has two independent input pins HIN and LIN allowing it to be used in a variety of applications. The input stages of NCP51530 are TTL and CMOS compatible. This ensures that the inputs of NCP51530 can be driven with 3.3 V or 5 V logic signals from analog or digital PWM controllers or logic gates.

The input pins have Schmitt triggers to avoid noise induced logic errors. The hysteresis on the input pins is typically 1.3 V. This high value ensures good noise immunity.

NCP51530 comes with an important feature wherein outputs (HO, LO) stays low in case any of the input pin is floating. At both the input pins there is an internal pull down resistor to define its logic value in case the pin is left open or NCP51530 is driven by open drain signal. The input logic is explained in the Table 7 below.

NCP51530 input pins are also tolerant to negative voltage below the GND pin level as long as it is within the ratings defined in the datasheet. This tolerance allows the use of transformer as an isolation barrier for input pulses.

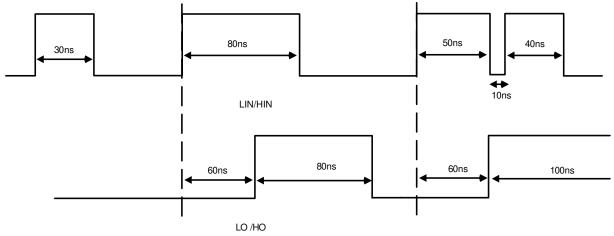

NCP51530A features a noise rejection function to ensure that any pulse glitch shorter than 30 ns will not produce any output. These features are well illustrated in the Figure 26 below.

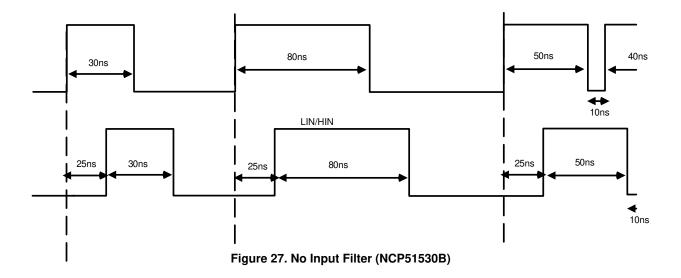

NCP51530B has no such filters in the input stages. The timing diagram NCP51530B is Figure 27 below.

**Table 7. INPUT TABLE**

| S.No | LIN | HIN | НО | LO |

|------|-----|-----|----|----|

| 1    | 0   | 0   | 0  | 0  |

| 2    | 0   | 1   | 0  | 1  |

| 3    | 1   | 0   | 1  | 0  |

| 4    | 1   | 1   | 1  | 1  |

| 5    | X   | 0   | 0  | 0  |

| 6    | Х   | 1   | 0  | 1  |

| 7    | X   | X   | 0  | 0  |

| 8    | 0   | Х   | 0  | 0  |

| 9    | 1   | Х   | 1  | 0  |

Figure 26. Input Filter (NCP51530A)

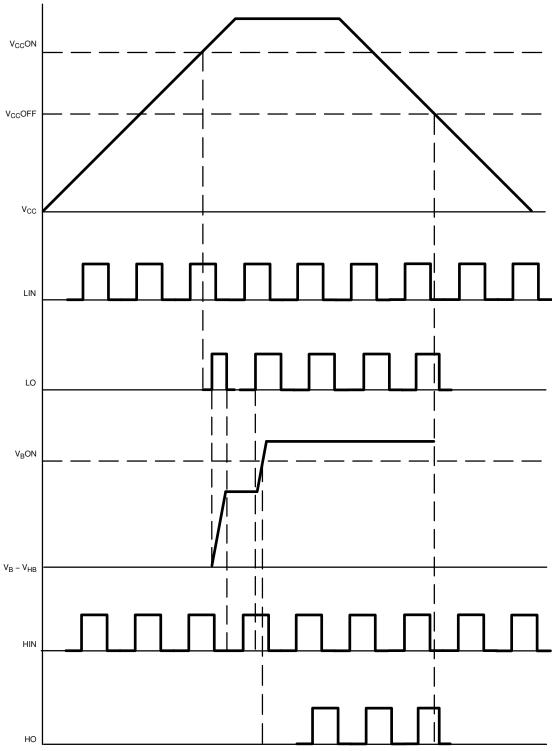

Figure 28. UVLO Timing Diagram

#### **UNDER VOLTAGE LOCK-OUT**

NCP51530 has under voltage lockout protection on both the high side and the low side driver. The function of the UVLO circuits is to ensure that there is enough supply voltages ( $V_{CC}$  and  $V_{B}$ ) to correctly bias high side and low side circuits. This also ensures that the gate of external MOSFETs are driven at an optimum voltage.

If the  $V_{CC}$  is below the  $V_{CC}$  UVLO voltage, the low side driver output (LO) and high side driver output (HO) both remain low.

If  $V_B$  is below  $V_B$  UVLO voltage the high side driver output (HO) remains low. However if the  $V_{CC}$  is above  $V_{CC}$  UVLO voltage level, the low side driver output (LO) can still turn on and off based on the low side driver input (LI)

and is not affected by the  $V_B$  status. This ensures proper charging of the bootstrap capacitor to bring the high side bias supply  $V_B$  above UVLO voltage.

Both the  $V_{CC}$  and  $V_B$  UVLO circuits are provided with hysteresis feature. This hysteresis feature avoids errors due to ground noise in the power supply. The hysteresis also

ensures continuous operation in case of a small drop in the bias voltage. This drop in the bias can happen when device starts switching MOSFET and the operating current of the device increases. The UVLO feature of the device is explained in the Figure 30.

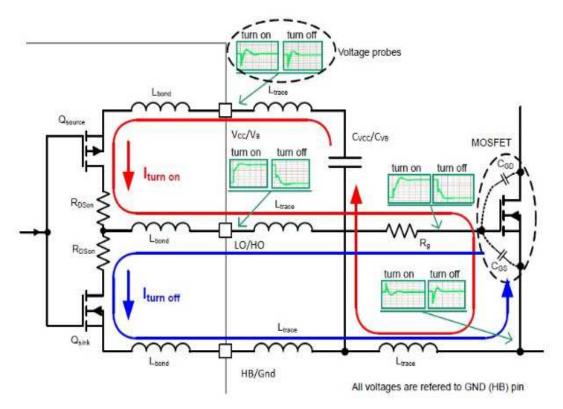

Figure 29. NCP51530 Turn ON-OFF Paths

#### **OUTPUT STAGES**

The NCP51530 is equipped with two independent drivers. The output stage of NCP51530 has 3.5 A/3 A current source/sink capability which can effectively charge and discharge a 1 nF load in 15 ns.

The outputs of NCP51530 can be turned on at the same time and there is no internal dead–time built between them. This allows NCP51530 to be used in topologies like two switch forward converter.

The figure below show the output stage structure and the charging and discharging path of the external power MOSFET. The bias supply  $V_{CC}$  or  $V_B$  supply the energy to charge the gate capacitance Cgs of the low side or the top

side external MOSFETs respectively. When a logic high is received from input stage, Qsource turns on and  $V_{CC}/V_B$  starts charging Cgs through Rg. Once the Cgs is charged to the drive voltage level the external power MOSFET turns on the external MOSFET to discharge to GND/HB level.

When a logic low signal is received from the input stage, Qsource turns off and Qsink turns on providing a path for gate terminal of

As seen in the figure, there are parasitic inductances in charging and discharging path of the Cgs. This can result in a little dip in the bias voltages  $V_{CC}/V_B$ . If the  $V_{CC}/V_B$  drops below UVLO the power supply can shut down the device.

Figure 30. Low Side Turn-ON Propagation Delay (NCP51530A)

#### **FAST PROPAGATION DELAY**

NCP51530 boasts of industry best propagation delay between input and output. NCP51530A has a typical of 60 ns propagation delay. The best in class propagation delay in NCP51530 makes it suitable for high frequency operation.

Since NCP51530B doesn't have the input filter included, the propagation delay are even faster. NCP51530B offers 25 ns propagation delay between input and output.

Figure 31. Low Side Turn-Off Propagation Delay (NCP51530A)

Figure 32. High Side Turn-Off Propagation Delay (NCP51530B)

Figure 33. High Side Turn-Off Propagation Delay (NCP51530B)

Figure 34. Bootstrap Circuit

#### **COMPONENT SELECTION**

#### **CBOOT CAPACITOR VALUE CALCULATION**

NCP51530 has two independent drivers for driving high side and low side external MOSFETs. The bias for the high side driver is usually provided through a bootstrap circuit. A typical bootstrap circuit is shown in the figure 8 below.

The high side driver is biased by the  $C_{boot}$  (bootstrap capacitor). As can be seen in the circuit,  $C_{boot}$  will charge only when HB goes to GND level. Low value of  $C_{boot}$  can result in a little dip in the bias voltages  $V_B$ . If the  $V_B$  drops below UVLO the power supply can shut down the high side driver. Therefore choosing the right value of  $C_{boot}$  is very important for a robust design.

An example design for C<sub>boot</sub> is given below.

$$Q_g = 30 \text{ nC}, V_{CC} = 15 \text{ V}$$

(eq. 1)

$$Q_b = I_{BQ} * t_{discharge} = 81 \ \mu C * 5 \ \mu S = 405 \ pC \ \ (eq. 2)$$

$$Q_{tot} = Q_q + Q_h = 30 \text{ nC} + 405p = 30.4 \text{ pC}$$

(eq. 3)

$$C_{boot} = \frac{Q_{tot}}{V_{ripple}} = \frac{30.4 \text{ nC}}{150 \text{ mV}} = 203 \text{ nF}$$

(eq. 4)

Qg is equivalent gate charge of the FET

I<sub>BO</sub> is the boot quiescent current

$t_{dish charge}$  is the discharge time for bootstrap capacitor  $V_{ripple}$  is the allowed ripple voltage in the bootstrap capacitor

It is recommended to use a larger value so as to cover any variations in the gate charge and voltage with temperature.

#### R<sub>boot</sub> RESISTOR VALUE CALCULATION

$R_{boot}$  resistor value is very important to ensure proper function of the device. A high value of  $R_{boot}$  would slow down the charging of the  $C_{boot}$  while too low a value would push very high charging currents for  $C_{boot}$ . For NCP51530 a value between 2  $\Omega$  and 10  $\Omega$  is recommended for  $R_{boot}$ .

For example  $R_{boot} = 5 \Omega$

$$I_{boot(pk)} = \frac{V_{CC} - V_{D}}{R_{boot}} = \frac{15 \text{ V} - 1 \text{ V}}{5 \Omega} = 2.8 \text{ A}$$

(eq. 5)

Where  $V_D$  is the bootstrap diode forward drop. Thus,  $R_{boot}$  value of 5  $\Omega$  keeps the peak current below 2.8 A.

#### HIN AND LIN INPUT FILTER

For PWM connection on the LIN and HIN pin of the NCP51530, a RC is recommended to filter high frequency input noise.

This filter is particularly important in case of NCP51530B where no internal filter is included.

The recommended value for  $R_{LIN}/R_{HIN}$  and  $C_{HIN}/C_{LIN}$  are as below.

$R_{LIN}/R_{HIN} = 100 \Omega$

$C_{HIN}/C_{LIN} = 120 pF$

#### **V<sub>CC</sub> CAPACITOR SELECTION**

$V_{CC}$  capacitor value should be selected at least ten times the value of  $C_{boot}$ . In this case thus  $C_{VCC} > 2~\mu F$ .

#### R<sub>gate</sub> SELECTION

$R_{gate}$  are selected to limit the peak gate current during charging and discharging of the gate capacitance. This resistance also helps to damp the ringing due to the parasitic inductances.

For example for a  $R_{gate}$  value of 5  $\Omega$ , the peak source and sink currents would be limited to the following values.

$$R_{\text{gate}} = 5\Omega$$

(eq. 6)

$$I_{LO\_Source} = \frac{V_{CC}}{R_{Loate} + R_{LOH}} = \frac{15 \text{ V}}{6.7 \Omega} = 2.23 \text{ A (eq. 7)}$$

$$I_{LO\_Sink} = \frac{V_{CC}}{R_{Loate} + R_{LOL}} = \frac{15 \text{ V}}{6.8 \Omega} = 2.20 \text{ A}$$

(eq. 8)

$$I_{HO\_Source} = \frac{V_{CC} - V_{Dboot}}{R_{Lgate} + R_{HOH}} = \frac{14 \text{ V}}{6.7 \Omega} = 2.09 \text{ A} \text{ (eq. 9)}$$

$$I_{HO\_Sink} = \frac{V_{CC} - V_{Dboot}}{R_{Lgate} + R_{HOL}} = \frac{15 \text{ V} - 1 \text{ V}}{6.8 \Omega} = 2.06 \text{ A}^{\text{(eq. 10)}}$$

#### **TOTAL POWER DISSIPATION**

Total power dissipation of NCP51530 can be calculated as follows.

1. Static power loss of device (excluding drivers) while switching at an appropriate frequency.

$$P_{\text{operating}} = V_{\text{boot}} * I_{\text{BO}} + V_{\text{CC}} * I_{\text{CCO}}$$

(eq. 11)

= 14 V \* 0.4 mA + 15 V \* 0.4 mA = 11.6 mW

$I_{BO}$  is the operating current for the high side driver  $I_{CCO}$  is the operating current for the low side driver

2. Power loss of driving external FET (Hard Switching)

$$\begin{split} &P_{drivers} = \left( \left( Q_g * V_{boost} \right) + \left( Q_g * V_{CC} \right) \right) &f \\ &= \left( (30 \text{ nC} * 14 \text{ V}) + (30 \text{ nC} * 15 \text{ V}) \right) * 100 \text{ kHz} = 87 \text{ mW} \end{split}$$

(eq. 12)

Qg is total gate charge of the MOSFET

3. Power loss of driving external FET (Soft Switching)

$$P_{drivers} = ((Q_{gs} * V_{boot}) + (Q_{gs} * V_{CC})) * f$$

(eq. 13)

= ((4 nC \* 14 V) + (4 nC \* 15 V)) \* 100 kHz = 11 mW

4. Level shifting losses

$$\begin{aligned} & P_{levelshifting} = \left( V_r + V_b \right) * Q * f \\ & = 415 \ V * 1 \ nC * 100 \ kHz = 41.5 \ mW \end{aligned}$$

(eq. 14)

Vr is the rail voltage

Q is the substrate charge on the level shifter

5. Total Power Loss (Hard Switching)

$$P_{\text{total}} = P_{\text{driver}} + P_{\text{operating}} + P_{\text{levelshifting}}$$

(eq. 15)

= 11.6 mW + 87 mW + 40 mW = 138.6 mW

6. Junction temperature increase

$$t_{.I} = R_{\theta,IA} * P_{total} = 183 * 0.14 = 25^{\circ} C$$

(eq. 16)

#### LAYOUT RECOMMENDATIONS

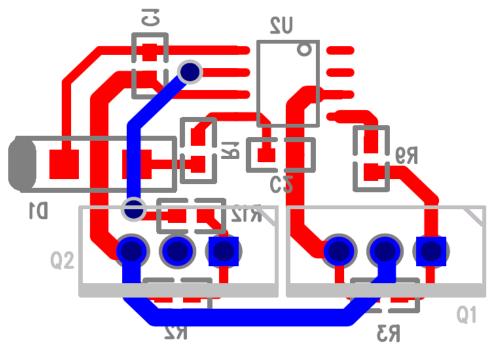

NCP51530 is a high speed and high current high side and low side driver. To avoid any device malfunction during device operation, it is very important that there is very low parasitic inductance in the current switching path. It is very important that the best layout practices are followed for the PCB layout of the NCP51530. An example layout is shown in the figure below. Some of the layout rules to be followed are listed below.

- Keep the low side drive path LO-Q1-GND as small as possible. This reduces the parasitic inductance in the path and hence eliminates ringing on the gate terminal of the low side MOSFET Q1.

- Keep the high side drive loop HO–Q2–HB as small as possible. This reduces the parasitic inductance in the

- path and hence eliminates ringing on the gate terminal of the low side MOSFET Q1.

- Keep C<sub>VCC</sub> as near to the V<sub>CC</sub> pin as possible and the V<sub>CC</sub>-CV<sub>CC</sub>-GND loop as small as possible.

- Keep C<sub>VB</sub> as near to VB pin as possible and VB–CVB–HB loop as small as possible.

- Keep the HB-GND-Q1 loop as small as possible. This

loop has the potential to produce a negative voltage

spike on the HB pin. This negative voltage spike can

cause damage to the driver. This negative spike can

increase the boot capacitor voltage above the maximum

rating and hence cause damage to the driver.

Figure 35. Example Layout

#### **ORDERING INFORMATION**

| Device         | Propagation Delay<br>(ns) | Input filter | Package                | Shipping <sup>†</sup> |

|----------------|---------------------------|--------------|------------------------|-----------------------|

| NCP51530ADR2G  | 60                        | Yes          | SOIC-8<br>(Pb-Free)    | 2500 / Tape & Reel    |

| NCP51530BDR2G  | 25                        | No           | SOIC-8<br>(Pb-Free)    | 2500 / Tape & Reel    |

| NCP51530AMNTWG | 60                        | Yes          | DFN10 4x4<br>(Pb-Free) | 4000 / Tape & Reel    |

| NCP51530BMNTWG | 25                        | No           | DFN10 4x4<br>(Pb-Free) | 4000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

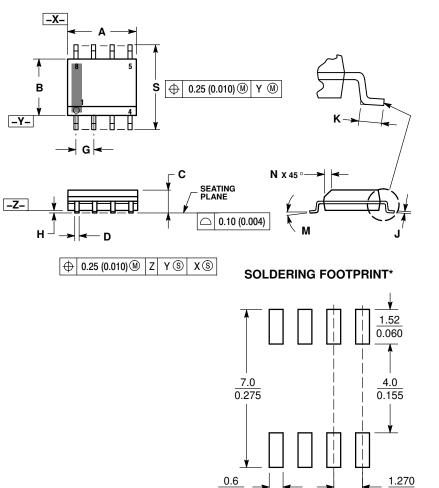

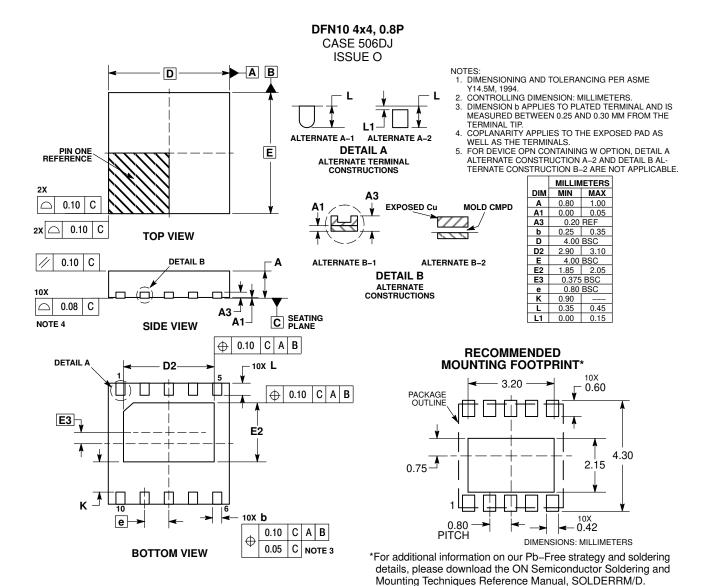

#### **PACKAGE DIMENSIONS**

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

0.024

#### \*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

0.050

SCALE 6:1

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION, ALLOWARIE DAMBAR DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. 751–01 THRU 751–06 ARE OBSOLETE. NEW STANDARD IS 751–07.

|     | MILLIMETERS |       | ERS INCHES |       |

|-----|-------------|-------|------------|-------|

| DIM | MIN         | MAX   | MIN        | MAX   |

| Α   | 4.80        | 5.00  | 0.189      | 0.197 |

| В   | 3.80        | 4.00  | 0.150      | 0.157 |

| С   | 1.35        | 1.75  | 0.053      | 0.069 |

| D   | 0.33        | 0.51  | 0.013      | 0.020 |

| G   | 1.27        | 7 BSC | 0.050 BSC  |       |

| Н   | 0.10        | 0.25  | 0.004      | 0.010 |

| J   | 0.19        | 0.25  | 0.007      | 0.010 |

| K   | 0.40        | 1.27  | 0.016      | 0.050 |

| М   | 0 °         | 8 °   | 0 °        | 8 °   |

| N   | 0.25        | 0.50  | 0.010      | 0.020 |

| S   | 5.80        | 6.20  | 0.228      | 0.244 |

#### PACKAGE DIMENSIONS

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and ho

expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative