# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Dual Synchronous Buck Controller for Notebook Power System**

The NCP5215, a high-efficiency and fast-transient-response dual-channel buck controller, provides a multifunctional power solution for notebook power system. 180° interleaved operation function between the two channels has capabilities of reducing the common input capacitor requirement and improving noise immunity. Adaptive-Voltage-Positioning (AVP) control reduces the requirement of output filter capacitors. Programmable power-saving operation ensures high efficiency over entire load range. Input feedforward voltage-mode control is employed to deal with wide input voltage range. Transient-Response-Enhancement (TRE) control for the both channels enables fast transient response.

#### Features

- Wide Input Voltage Range: 4.5 V to 24 V

- Adjustable Output Voltage Range: 0.8 V to 3.0 V

- Selectable Nominal Fixed Switching Frequency: 200 kHz, 300 kHz, and 400 kHz

- 180° Interleaved Operation Function between the Two Channels

- Programmable Adaptive-Voltage-Positioning (AVP) Operation

- TACTAINE • Programmable Transient-Response-Enhancement (TRE) Control

- Power Saving Operation under Light Load Condition

- Input Feedforward Voltage Mode Control

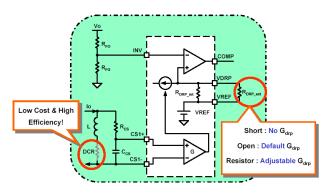

- Resistive or Inductor's DCR Current Sensing

- 1% Internal 0.8 V Reference

- External Soft-Start Operation

- Output Discharge and Soft-Stop

- Built-in Gate Drivers

- Input Supplies Undervoltage Lockout

- Output Overvoltage and Undervoltage Protections

- Accurate Overcurrent Protection

- Thermal Shutdown Protection

- QFN40 Package

- This is a Pb–Free Device

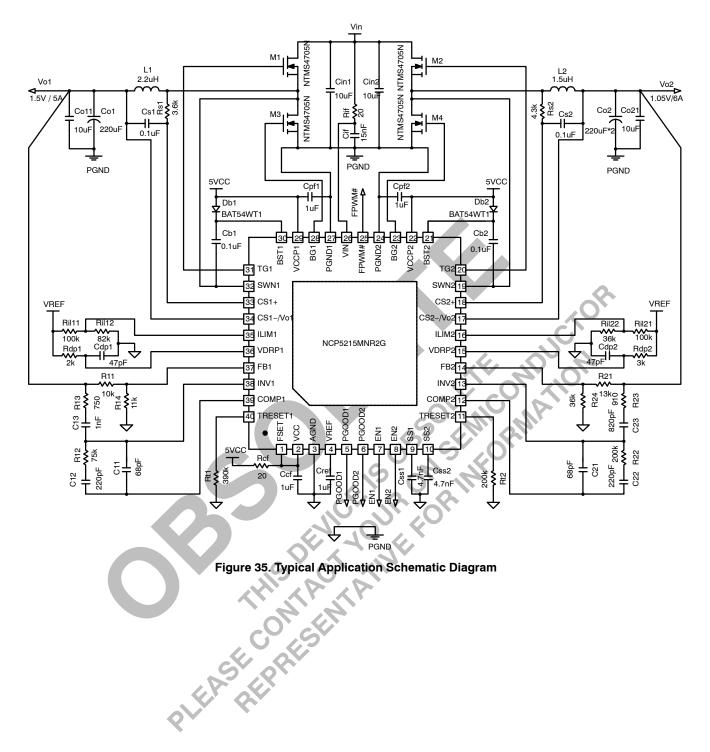

#### **Typical Applications**

- Notebook Computers

- CPU Chipset Power Supplies

#### **ON Semiconductor**<sup>®</sup>

#### http://onsemi.com

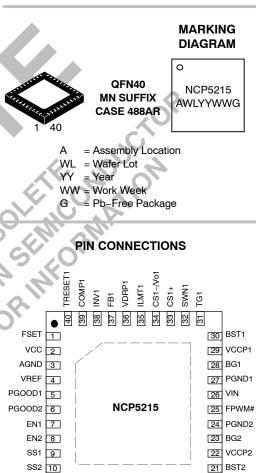

13 15 16 17 18 19

FB2

/DRP2 ILIM2

(Top View)

**ORDERING INFORMATION**

Package

QFN40

(Pb-Free) +For information on tape and reel specifications, including part orientation and tape sizes, please

F 4

RESET2

Device

NCP5215MNR2G

refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

20

TG2

Shipping

2500/Tape & Reel

SWN2

CS2-No2 CS2+

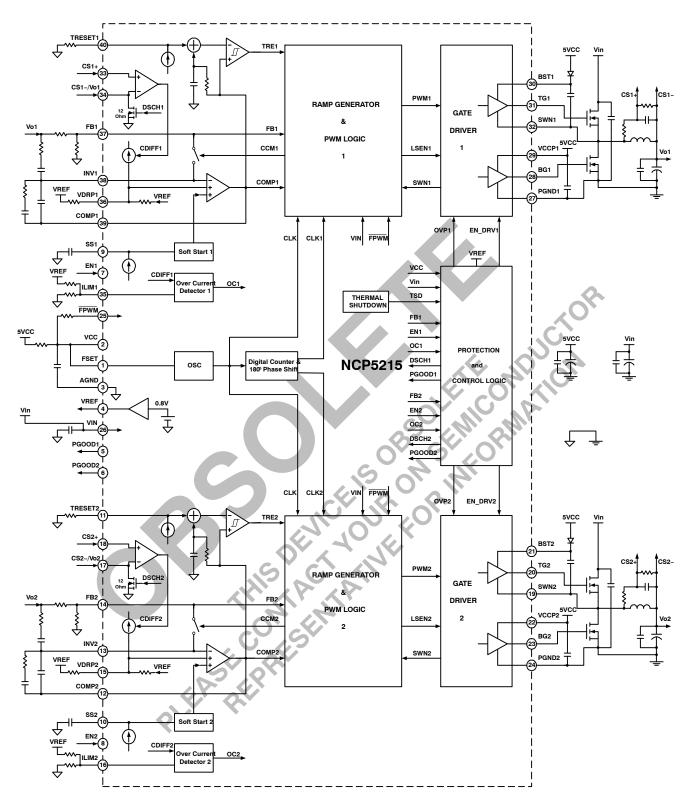

Figure 1. Internal Block Diagram and Typical Application

#### **PIN FUNCTION DESCRIPTION**

| Pin No. | Symbol     | Description                                                                                                                                                        |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | FSET       | Frequency SET Programmable pin of switching frequency for two channels.                                                                                            |

| 2       | VCC        | VCC This pin powers the control section of IC.                                                                                                                     |

| 3       | AGND       | Analog Ground Low noise ground for control section of IC.                                                                                                          |

| 4       | VREF       | Reference Voltage Output Internal 0.8 V reference output.                                                                                                          |

| 5       | PGOOD1     | <b>Power GOOD 1</b> Power good indicator of the output voltage of Channel 1. (Open drained)                                                                        |

| 6       | PGOOD2     | Power GOOD 2 Power good indicator of the output voltage of Channel 2. (Open drained)                                                                               |

| 7       | EN1        | Enable 1 Enable logic input of Channel 1.                                                                                                                          |

| 8       | EN2        | Enable 2 Enable logic input of Channel 2.                                                                                                                          |

| 9       | SS1        | Soft-Start 1 Soft-starting programmable pin of Channel 1.                                                                                                          |

| 10      | SS2        | Soft Start 2 Soft-starting programmable pin of Channel 2.                                                                                                          |

| 11      | TRESET2    | Transient Response Enhancement SET 2 Channel 2 Transient-Response-Enhancement (TRE) programmable pin.                                                              |

| 12      | COMP2      | COMP2 Output of the error amplifier of Channel 2.                                                                                                                  |

| 13      | INV2       | Inverting Input 2 Error amplifier's inverting input pin of Channel 2.                                                                                              |

| 14      | FB2        | Feedback 2 Output voltage feedback of Channel 2.                                                                                                                   |

| 15      | VDRP2      | <b>Voltage Droop 2</b> Channel 2 voltage droop output to the compensation. This pin is used to program the adaptive-voltage-position (AVP) function for Channel 2. |

| 16      | ILMT2      | Current Limit 2 Current limit programmable pin of Channel 2.                                                                                                       |

| 17      | CS2- / Vo2 | Current Sense 2- Channel 2 inductor current differential sense inverting input.                                                                                    |

| 18      | CS2+       | Current Sense 2+ Channel 2 inductor current differential sense non-inverting input.                                                                                |

| 19      | SWN2       | Switch Node 2 Switch node between the top MOSFET and bottom MOSFET of Channel 2.                                                                                   |

| 20      | TG2        | Top Gate 2 Gate driver output of the top N-Channel MOSFET for Channel 2.                                                                                           |

| 21      | BST2       | <b>BOOTSTRAP Connection 2</b> Channel 2 top gate driver input supply, a bootstrap capacitor connection between SWN2 and this pin.                                  |

| 22      | VCCP2      | VCC Power 2 This pin powers the bottom gate driver of Channel 2.                                                                                                   |

| 23      | BG2        | Bottom Gate 2 Gate driver output of the bottom N-Channel MOSFET for Channel 2.                                                                                     |

| 24      | PGND2      | Power Ground 2 Ground reference and high-current return path for the bottom gate driver of Channel 2.                                                              |

| 25      | FPWM#      | Forced PWM Forced PWM enable logic input. Low to enable forced PWM mode and disable power-saving mode for both channels.                                           |

| 26      | Vin        | Vin Input voltage monitor input.                                                                                                                                   |

| 27      | PGND1      | Power Ground 1 Ground reference and high-current return path for the bottom gate driver of Channel 1.                                                              |

| 28      | BG1        | Bottom Gate 1 Gate driver output of the bottom N-Channel MOSFET for Channel 1.                                                                                     |

| 29      | VCCP1      | VCC Power 1 This pin powers the bottom gate driver of Channel 1.                                                                                                   |

| 30      | BST1       | <b>BOOTSTRAP Connection 1</b> Channel 1 top gate driver input supply, a bootstrap capacitor connection between SWN1 and this pin.                                  |

| 31      | TG1        | Top Gate 1 Gate driver output of the top N-Channel MOSFET for Channel 1.                                                                                           |

| 32      | SWN1       | Switch Node 1 Switch node between the top MOSFET and bottom MOSFET of Channel 1.                                                                                   |

| 33      | CS1+       | Current Sense 1+ Channel 1 inductor current differential sense non-inverting input.                                                                                |

| 34      | CS1- / Vo1 | Current Sense 1- Channel 1 inductor current differential sense inverting input.                                                                                    |

| 35      | ILMT1      | Current Limit 1 Current limit programmable pin of Channel 1.                                                                                                       |

| 36      | VDRP1      | <b>Voltage Droop 1</b> Channel 1 voltage droop output to the compensation. This pin is used to program the Adaptive–Voltage–Position (AVP) function for Channel 1. |

| 37      | FB1        | Feedback 1 Output voltage feedback of Channel 1.                                                                                                                   |

| 38      | INV1       | Inverting Input 1 Error amplifier's inverting input pin of Channel 1.                                                                                              |

| 39      | COMP1      | COMP1 Output of the error amplifier of Channel 1.                                                                                                                  |

| 40      | TRESET1    | Transient Response Enhancement SET 1 Channel 1 Transient-Response-Enhancement (TRE) program pin.                                                                   |

#### MAXIMUM RATINGS

| Rating                                                                                                                     | Symbol                                                                                                                                          | Value                            | Unit |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|

| Power Supply Voltages to AGND                                                                                              | V <sub>CC</sub> , V <sub>CCP1</sub> ,<br>V <sub>CCP2</sub>                                                                                      | -0.3, 6.0                        | V    |

| High-Side Gate Driver Supplies: BST1 to SWN1, BST2 to SWN2<br>High-Side FET Gate Driver Voltages: TG1 to SWN1, TG2 to SWN2 | $\label{eq:VBST1} \begin{split} & V_{BST1} - V_{SWN1}, \\ & V_{BST2} - V_{SWN2}, \\ & V_{TG1} - V_{SWN1}, \\ & V_{TG2} - V_{SWN2}, \end{split}$ | -0.3, 6.0                        | V    |

| Input Voltage Sense Inputs to AGND                                                                                         | V <sub>in</sub>                                                                                                                                 | -0.3, 27                         | V    |

| Switch Nodes                                                                                                               | V <sub>SWN1</sub> , V <sub>SWN2</sub>                                                                                                           | -4.0 (<100 ns),<br>-0.3 (dc), 32 | V    |

| PGND1, PGND2 to AGND                                                                                                       | V <sub>GND</sub>                                                                                                                                | -0.3, 0.3                        | V    |

| Thermal Characteristics<br>Thermal Resistance, Junction-to-Air (Pad soldered to PCB)                                       | R <sub>0JA</sub>                                                                                                                                | 36                               | °C/W |

| Operating Junction Temperature Range                                                                                       | Тј                                                                                                                                              | -40 to +150                      | °C   |

| Operating Ambient Temperature Range                                                                                        | T <sub>A</sub>                                                                                                                                  | -40 to +85                       | °C   |

| Storage Temperature Range                                                                                                  | T <sub>stg</sub>                                                                                                                                | -55 to +150                      | °C   |

| Moisture Sensitivity Level                                                                                                 | MSL                                                                                                                                             |                                  | _    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the . Pin 17 and Pin 94, which a. B. Charles and the second se Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device contains ESD protection and exceeds the following tests:

Human Body Model (HBM)  $\leq$ 2.0kV per JEDEC standard: JESD22–A114. Machine Model (MM) = $\leq$ 200V per JEDEC standard: JESD22–A115, except Pin 17 and Pin 34, which are  $\leq$ 150V.

2. Latchup Current Maximum Rating: ≤150mA per JEDEC standard: JESD78.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 5.0 V,  $V_{IN}$  = 12 V,  $F_{SET}$  = 5.0 V, Fsw = 300 kHz,  $T_A$  = -40°C to 85°C, unless otherwise noted.)

| Characteristic                                                        | Symbol                  | Test Conditions                                                           | Min      | Тур | Max | Unit |

|-----------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------|----------|-----|-----|------|

| SUPPLY VOLTAGE                                                        | ·                       |                                                                           |          |     |     |      |

| Input Voltage                                                         | Vin                     | -                                                                         | 4.5      | -   | 24  | V    |

| V <sub>CC</sub> Operating Voltage                                     | V <sub>CC</sub>         | -                                                                         | 4.5      | 5.0 | 5.5 | V    |

| V <sub>CCP1</sub> Operating Voltage                                   | V <sub>CCP1</sub>       | -                                                                         | 4.5      | 5.0 | 5.5 | V    |

| V <sub>CCP2</sub> Operating Voltage                                   | V <sub>CCP2</sub>       | _                                                                         | 4.5      | 5.0 | 5.5 | V    |

| SUPPLY CURRENT                                                        |                         |                                                                           |          |     |     |      |

| V <sub>CC</sub> Quiescent Supply Current in Normal<br>Operation       | IVCC_N                  | VEN1 = VEN2 = 5.0 V,<br>VFPWM# = 0 V TG1, BG1, TG2,<br>and BG2 are open   | _        | 3.0 | 6.0 | mA   |

| V <sub>CC</sub> Quiescent Supply Current in<br>Power–Saving Operation | Ivcc_ps                 | VEN1 = VEN2 = 5.0 V,<br>VFPWM# = 5.0 V TG1, BG1,<br>TG2, and BG2 are open | -        | 3.0 | 6.0 | mA   |

| V <sub>CC</sub> Shutdown Current                                      | I <sub>VCC_SD</sub>     | VEN1 = VEN2 = 0 V                                                         | -        | -   | 10  | μA   |

| V <sub>CCP</sub> Quiescent Supply Current in Normal<br>Operation      | IVCCP1_N,<br>IVCCP2_N   | VEN1 = VEN2 = 5.0 V,<br>VFPWM# = 0 V TG1, BG1, TG2,<br>and BG2 are open   | -        | 1.2 | 2.0 | mA   |

| V <sub>CCP</sub> Shutdown Current                                     | IVCCP1_SD,<br>IVCCP2_SD | VEN1 = VEN2 = 0 V                                                         | N        | 0   | 10  | μΑ   |

| BST Quiescent Supply Current in Normal<br>Operation                   | IBST1_N, IBST2_N        | VEN1 = VEN2 = 5.0 V,<br>VFPWM# = 0 V TG1, BG1, TG2,<br>and BG2 are open   | MA       | 1.0 | 2.0 | mA   |

| BST Shutdown Current                                                  | IBST1_SD,<br>IBST2_SD   | VEN1 = VEN2 = 0 V                                                         | <u> </u> | -   | 5.0 | μΑ   |

| VOLTAGE-MONITOR                                                       |                         | 16. 7 S                                                                   |          |     |     |      |

#### VOLTAGE-MONITOR

| V <sub>CC</sub> Start Threshold                 | VCC <sub>UV+</sub>  | $V_{CC}$ and $V_{CCP}$ are connected to the same voltage source | 4.05 | 4.25   | 4.48 | V  |

|-------------------------------------------------|---------------------|-----------------------------------------------------------------|------|--------|------|----|

| V <sub>CC</sub> UVLO Hysteresis                 | VCC <sub>hys</sub>  |                                                                 | 200  | 275    | 400  | mV |

| Power Good Higher Threshold                     | VPGH                | With Respect to Error Comparator<br>Threshold of 0.8 V          | -    | 112    | -    | %  |

| Power Good Lower Threshold                      | VPGL                | With Respect to Error Comparator<br>Threshold of 0.8 V          | -    | 88     | -    | %  |

| Output Overvoltage Trip Threshold               | FBOVPth             | With respect to Error Comparator<br>Threshold of 0.8 V          | 113  | 117    | 121  | %  |

| Overvoltage Fault Propagation Delay             |                     | FB forced 2% above trip threshold                               | -    | 1.5    | -    | μs |

| Output Undervoltage Trip Threshold              | FBUVPth             | With respect to Error Comparator<br>Threshold of 0.8 V          | 63   | 68     | 73   | %  |

| Output Undervoltage Protection Blanking<br>Time | UVPT <sub>blk</sub> | (Note 3)                                                        | -    | 16/fsw | -    | s  |

#### VREF OUTPUT

| Reference Voltage         | V <sub>ref</sub> | $T_A = 25^{\circ}C$<br>$T_A = -40$ to $85^{\circ}C$ | 0.796<br>0.792 | 0.8<br>_ | 0.804<br>0.808 | V  |

|---------------------------|------------------|-----------------------------------------------------|----------------|----------|----------------|----|

| Reference Load Regulation | $\Delta V_{ref}$ | lvref = 0 to 100 μA                                 | -              | -        | 4.0            | mV |

| Sinking Current           | lsink_VREF       | Vref rises 10%                                      | 20             | -        | -              | μA |

#### CURRENT LIMIT

| Current Limit Threshold | V <sub>((CS+)-(CS-))</sub> | $V_{ILIM} = 0.4 V$ | 72 | 80 | 88  | mV |

|-------------------------|----------------------------|--------------------|----|----|-----|----|

| ILIM Setting Range      | Range <sub>ILIM</sub>      | (Note 3)           | -  | -  | 0.8 | V  |

3. Guaranteed by design, not tested in production.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{CC}$  = 5.0 V,  $V_{IN}$  = 12 V,  $F_{SET}$  = 5.0 V, Fsw = 300 kHz,  $T_A$  = -40°C to 85°C, unless otherwise noted)

| Characteristic                | Symbol                                  | Test Conditions                                                                         | Min          | Тур      | Max          | Unit |

|-------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------|--------------|----------|--------------|------|

| THERMAL SHUTDOWN              | ·                                       |                                                                                         |              |          |              |      |

| Thermal Shutdown              | Tsd                                     | (Note 4)                                                                                | _            | 150      | -            | °C   |

| Thermal Shutdown Hysteresis   | Tsdhys                                  | (Note 4)                                                                                | -            | 30       | -            | °C   |

| OSCILLATOR                    | ·                                       |                                                                                         |              |          |              |      |

| Operation Frequency           | Fsw                                     | FSET pin open loop ( $T_A = 25^{\circ}C$ )                                              | 160          | 200      | 240          | kHz  |

|                               |                                         | Pull high FSET pin ( $T_A = 25^{\circ}C$ )<br>( $T_A = -40^{\circ}C$ to $85^{\circ}C$ ) | 262.5<br>255 | 300<br>- | 337.5<br>345 | kHz  |

|                               |                                         | Pull low FSET pin (T <sub>A</sub> = 25°C)                                               | 340          | 400      | 460          | kHz  |

| SOFT-START                    |                                         |                                                                                         |              |          |              |      |

| Soft-Start Source Current     | I <sub>SS</sub>                         | -                                                                                       | 3.0          | 4.0      | 5.0          | μA   |

| Soft-Start Complete Threshold | V <sub>SSTh</sub>                       | (Note 4)                                                                                | -            | 0.9      | -            | V    |

| SWITCHING REGULATORS          |                                         |                                                                                         |              |          |              |      |

| Main Ramp Amplitude Voltage   | Vramp                                   | V <sub>IN</sub> = 5.0 V (Note 4)                                                        | -            | 1.25     | -            | V    |

| Maximum Duty Cycle            | Dmax                                    | V <sub>IN</sub> = 5.0 V                                                                 |              | 92       | -            | %    |

|                               |                                         | V <sub>IN</sub> = 12 V                                                                  | ()           | 48       | -            | %    |

|                               |                                         | V <sub>IN</sub> = 24 V                                                                  |              | 27       | -            | %    |

| GATE DRIVERS                  |                                         |                                                                                         | . 6          |          |              |      |

| TG Gate Pull-HIGH Resistance  | $R_{H_{TG1}}, R_{H_{TG2}}$              | $V_{BST}-V_{SWN} = 5.0 V,$<br>$V_{TG}-V_{SWN} = 4.0 V$                                  | 214          | 1.5      | 4.0          | Ω    |

| TG Gate Pull-LOW Resistance   | $R_{L_TG1}, R_{L_TG2}$                  | $V_{BST}-V_{SWN} = 5.0 \text{ V},$<br>$V_{TG}-V_{SWN} = 1.0 \text{ V}$                  | -            | 1.5      | 4.0          | Ω    |

| BG Gate Pull-HIGH Resistance  | R <sub>H_BG1</sub> , R <sub>H_BG2</sub> | $V_{CCP} = 5.0 \text{ V}, \text{ V}_{BG} = 4.0 \text{ V}$                               | -            | 1.5      | 4.0          | Ω    |

| BG Gate Pull-LOW Resistance   | R <sub>L_BG1</sub> , R <sub>L_BG2</sub> | V <sub>CCP</sub> = 5.0 V, V <sub>BG</sub> = 1.0 V                                       | -            | 0.5      | 1.5          | Ω    |

| Dead Time                     | T <sub>LH</sub>                         | BG Falling to TG Rising                                                                 | -            | 42       | 1            | ns   |

|                               | THL                                     | TG Falling to BG Rising                                                                 | _            | 34       | -            |      |

| DIFFERENTIAL CURRENT ERROR AM |                                         |                                                                                         |              |          |              |      |

| Input Bias Current            | CS-IIB                                  | - 7                                                                                     | -200         | -        | 200          | nA   |

| CS+ to CS- Input Signal Range | VCS_MAX                                 | Refer to AGND                                                                           | -            | -        | 3.0          | V    |

| Output Voltage Swing          | VOS_DRP                                 | (Note 4)                                                                                | 0.6          | -        | 1.0          | V    |

| Offset Current at VDRP        | loffset_DRP                             | (CS+)–(CS–) = 0 V, no connection<br>from VDRP pin to VREF                               | -1.0         | -        | 1.0          | μA   |

| S                          |                                              | from VDRP pin to VREF       |      |      |      |     |

|----------------------------|----------------------------------------------|-----------------------------|------|------|------|-----|

| [(CS+)-(CS-)] to VDRP Gain | Gain_CS<br>((V_VDRP-Vref)/<br>((CS+)-(CS-))) | (CS+)-(CS-) = 20 mV         | 2.35 | 2.6  | 2.85 | V/V |

| Internal Droop Resistance  | R <sub>DRP</sub>                             | From $V_{DRP}$ to $V_{REF}$ | 2.4  | 2.65 | 2.9  | kΩ  |

|                            |                                              |                             |      |      |      |     |

4. Guaranteed by design, not tested in production.

| <b>ELECTRICAL CHARACTERISTICS (continued)</b> ( $V_{CC} = 5.0 \text{ V}$ , $V_{IN} = 12 \text{ V}$ , $F_{SET} = 5.0 \text{ V}$ , $Fsw = 300 \text{ kHz}$ , $T_A = -40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ , unless the second | s |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| otherwise noted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| Characteristic                                                                  | Symbol                                               | Test Conditions                        | Min | Тур            | Max | Unit |

|---------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|-----|----------------|-----|------|

| VOLTAGE ERROR AMPLIFIER                                                         |                                                      |                                        |     |                |     |      |

| DC Gain                                                                         | GAIN_VEA                                             | (Note 5)                               | -   | 80             | -   | dB   |

| Unity Gain Bandwidth                                                            | Ft_VEA                                               | (Note 5)                               | _   | 13             | -   | MHz  |

| Slew Rate                                                                       | SR_VEA                                               | (Note 5)<br>(COMP PIN TO GND = 100 pF) | _   | 1.0            | -   | V/µs |

| Inverting Input Current                                                         | I <sub>INV1</sub> , I <sub>INV2</sub>                | V <sub>INV</sub> = 0.8 V               | _   | -              | 0.5 | μΑ   |

| Output Voltage Swing                                                            | VOS_EA                                               | -                                      | 1.0 | -              | 3.0 | V    |

| Source Current                                                                  | Isource_EA                                           | COMP = 3.0 V                           | 2.0 | 4.0            | -   | mA   |

| Sink Current                                                                    | lsink_EA                                             | COMP = 1.0 V                           | 1.5 | 2.0            | -   | mA   |

| CONTROL SECTION                                                                 | 1                                                    |                                        |     |                |     |      |

| VEN1, VEN2 Threshold High                                                       | $V_{EN1_H}, V_{EN2_H}$                               | -                                      | 1.4 | -              | -   | V    |

| VEN1, VEN2 Threshold Low                                                        | V <sub>EN1_L</sub> , V <sub>EN2_L</sub>              | -                                      | -   | -0             | 0.5 | V    |

| VEN1, VEN2 Source Current                                                       | I <sub>EN1_SOURCE</sub> ,<br>I <sub>EN2_SOURCE</sub> | -                                      | -   | C <sup>1</sup> | 0.5 | μΑ   |

| VEN1, VEN2 Sink Current                                                         | I <sub>EN1_SINK</sub> ,<br>I <sub>EN2_SINK</sub>     |                                        | JO' | 3              | 0.5 | μA   |

| VFPWM# Threshold High                                                           | V <sub>FPWM_H</sub>                                  |                                        | 1.4 | <u> </u>       | -   | V    |

| VFPWM# Threshold Low                                                            | VFPWM_L                                              |                                        | 47  | -              | 0.5 | V    |

| VFPWM# Source Current                                                           | IFPWM_SOURCE                                         |                                        | 2   | -              | 0.5 | μA   |

| VFPWM# Sink Current                                                             | IFPWM_SINK                                           | 0 <sup>v</sup> -, 5 <sup>v</sup> ,0    | -   | -              | 0.5 | μA   |

| PGOOD Pin ON Resistance                                                         | PGOOD_R                                              | I_PGOOD = 5.0 mA                       | _   | 25             | -   | Ω    |

| PGOOD Pin OFF Current                                                           | PGOOD_LK                                             | K A A                                  | -   | -              | 1.0 | μA   |

| OUTPUT DISCHARGE MODE                                                           |                                                      |                                        |     |                |     |      |

| Output Discharge On-Resistance                                                  | R <sub>discharge</sub>                               |                                        | -   | 12             | -   | Ω    |

| System Restart Threshold of the Output Voltage                                  | Vth_SRST                                             | The-                                   | 0.2 | 0.3            | 0.4 | V    |

| TRE OFFSET                                                                      |                                                      |                                        |     | •              |     |      |

| TRESET Offset Current                                                           | ITRE                                                 | -                                      | 3.0 | 4.0            | 5.0 | μA   |

| TRE OFFSET TRESET Offset Current Guaranteed by design, not tested in production | h <sub>TRE</sub>                                     | -                                      | 3.0 | 4.0            | 5.0 | μ    |

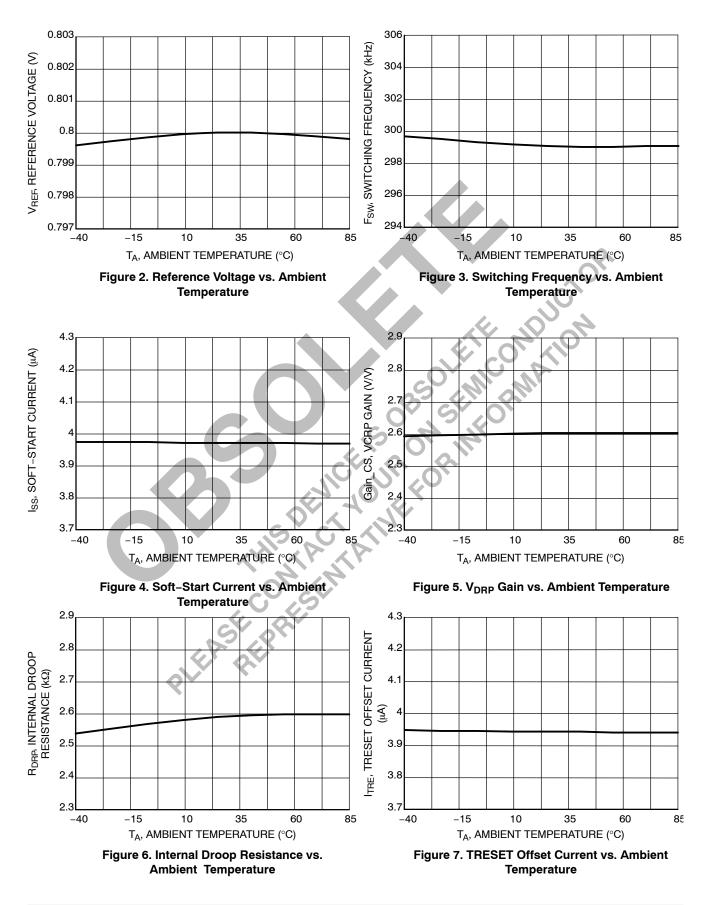

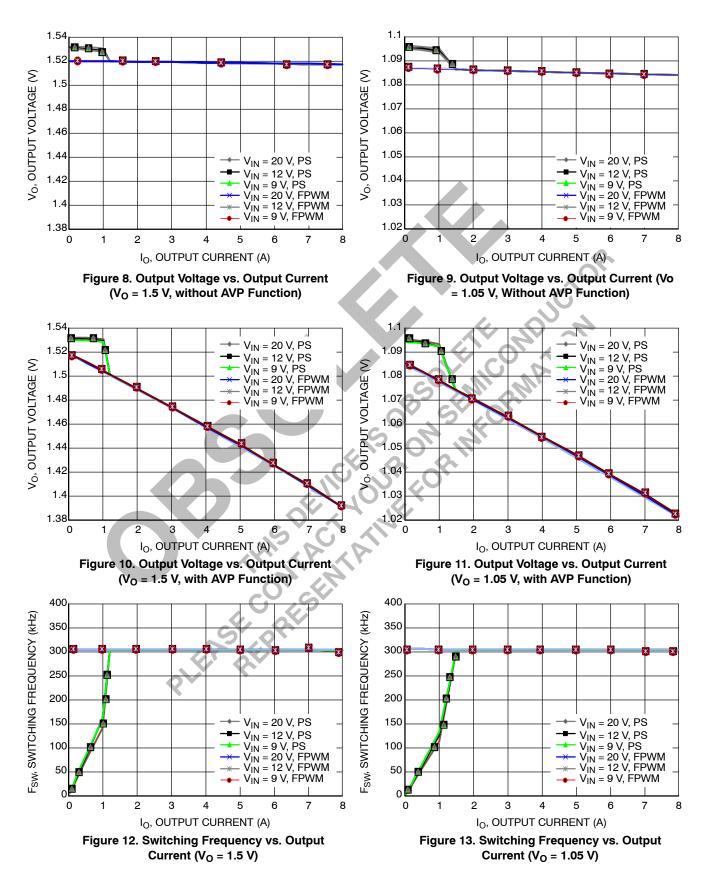

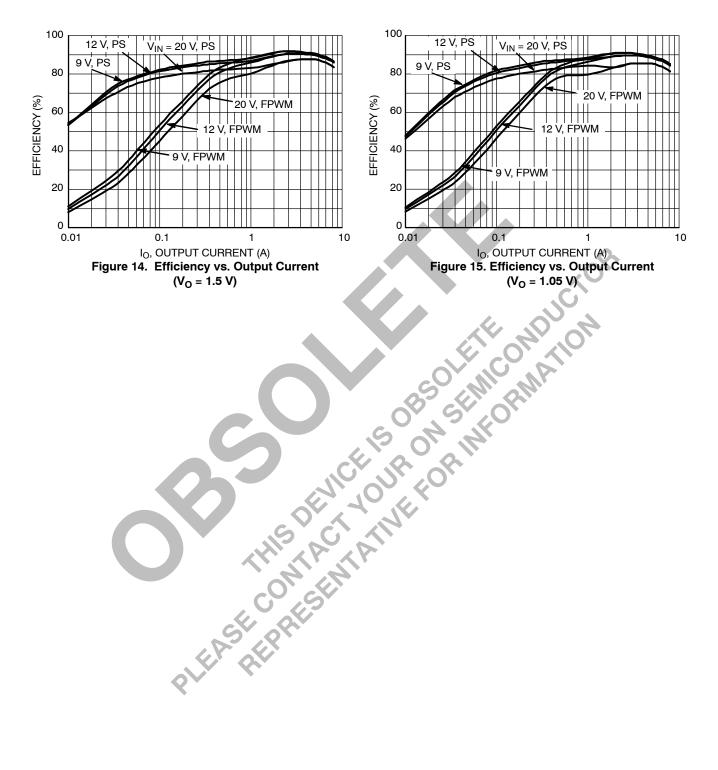

#### **TYPICAL OPERATING CHARACTERISTICS**

#### **TYPICAL OPERATING CHARACTERISTICS**

#### TYPICAL OPERATING CHARACTERISTICS

#### TYPICAL OPERATING CHARACTERISTICS

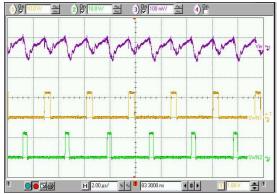

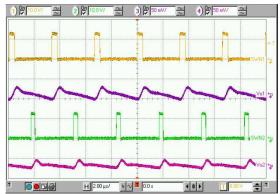

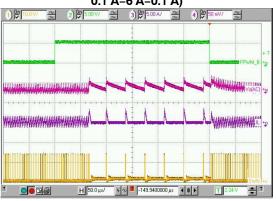

Top: Vin, Input Voltage Ripple, (100mV/div) Middle: SWN1, CH1 Switching Node Voltage, (10V/div) Bottom: SWN2, CH2 Switching Node Voltage, (10V/div) Time: 2μs/div

Figure 16. Input Voltage Ripple with Interleaved Operation (V<sub>O</sub>1 = 1.5 V, I<sub>O</sub>1 = 4 A, V<sub>O</sub>2 = 1.05 V, I<sub>O</sub>2 = 6 A)

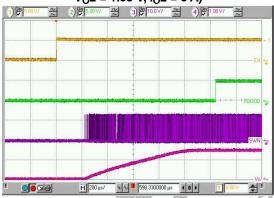

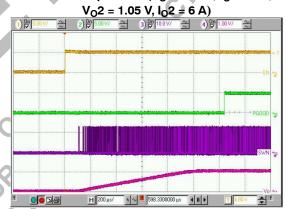

Top: EN1, CH1 Enable Signal, (5V/div) Middle 1: PGOOD1, CH1 Power Good Signal, (5V/div) Middle 2: SWN1, CH1 Switching Node Voltage, (10V/div) Bottom: V<sub>0</sub>1, CH1 Output Voltage, (1V/div)

Time: 200µs/div

Figure 18. Powerup Operation ( $V_01 = 1.5 V_1$

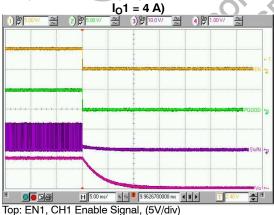

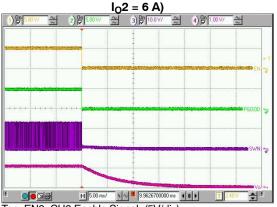

Middle 1: PGOOD1, CH1 Power Good Signal, (5V/div) Middle 2: SWN1, CH1 Switching Node Voltage, (10V/div) Bottom: V<sub>O</sub>1, CH1 Output Voltage, (1V/div) Time: 5ms/div

Figure 20. Powerdown Operation ( $V_01 = 1.5 V$ ,  $I_01 = 0 A$ , FPWM)

Top: SWN1, CH1 Switching Node Voltage, (10V/div) Middle 1: Vo1, CH1 Output Voltage Ripple, (50mV/div) Middle 2: SWN2, CH2 Switching Node Voltage, (10V/div) Bottom: Vo2, CH2 Output Voltage Ripple, (50mV/div) Time: 2μs/div

Figure 17. Output Voltage Ripple with Interleaved Operation ( $V_01 = 1.5 V$ ,  $I_01 = 4 A$ ,

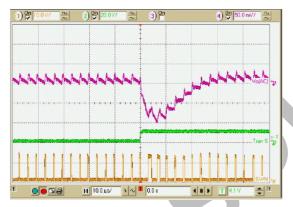

Top: EN2, CH2 Enable Signal, (5V/div)

Middle 1: PGOOD2, CH2 Power Good Signal, (5V/div) Middle 2: SWN2, CH2 Switching Node Voltage, (10V/div) Bottom: V<sub>O</sub>2, CH2 Output Voltage, (1V/div) Time: 200μs/div

#### Figure 19. Powerup Operation ( $V_02 = 1.05 V$ ,

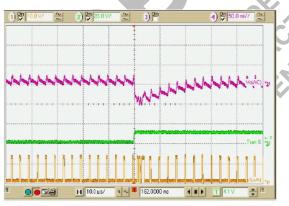

Top: EN2, CH2 Enable Signal, (5V/div) Middle 1: PGOOD2, CH2 Power Good Signal, (5V/div) Middle 2: SWN2, CH2 Switching Node Voltage, (10V/div) Bottom: Vo2, CH2 Output Voltage, (1V/div) Time: 5ms/div

Figure 21. Powerdown Operation ( $V_02 = 1.05 V$ ,  $I_02 = 0 A$ , FPWM)

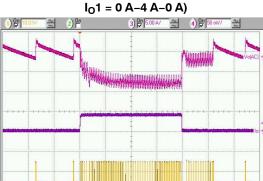

Top: Vo1, CH1 Output Voltage Ripple, (50mV/div) Middle: Io1, CH1 Output Current, (5A/div) Bottom: SWN1, CH1 Switching Node Voltage, (10V/div) Time: 20us/div

#### Figure 22. Load Transient Response with FPWM Operation ( $V_01 = 1.5 V_1$ ,

Η 50.0 μs/ 🔹 🕶 99.4190000 μs 🖌 0 🕨 T 1.91 A 0000 Top: Vo1, CH1 Output Voltage Ripple, (50mV/div) Middle: Io1, CH1 Output Current, (5A/div) Bottom: SWN1, CH1 Switching Node Voltage, (10V/div) Time: 50µs/div

#### Figure 24. Load Transient Response with Skip-Mode Operation (V<sub>0</sub>1 = 1.5 V, I<sub>0</sub>1 =

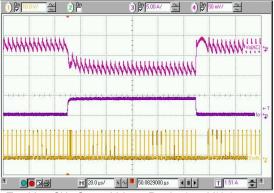

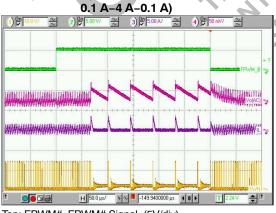

Top: FPWM#, FPWM# Signal, (5V/div) Middle 1: Vo1, CH1 Output Voltage Ripple, (50mV/div) Middle 2: iL1, CH1 Inductor Current, (5A/div) Bottom: SWN1, CH1 Switching Node Voltage, (10V/div) Time: 50us/div

Figure 26. On-Line Mode-Changing Operation (V<sub>0</sub>1 = 1.5 V, I<sub>0</sub>1 = 0.2 A, FPWM-Skip Mode-FPWM)

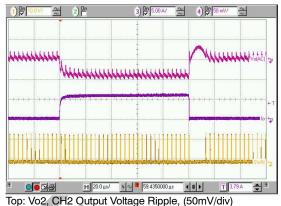

Middle: Io2, CH2 Output Current, (5A/div) Bottom: SWN2, CH2 Switching Node Voltage, (10V/div) Time: 20µs/div

Figure 23. Load Transient Response with FPWM Operation (V<sub>0</sub>2 = 1.05 V, I<sub>0</sub>2 =

0 A-6 A-0 A)

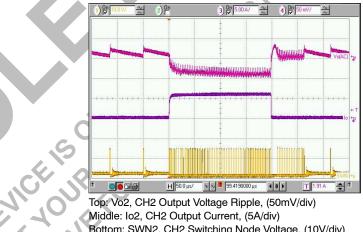

Top: Vo2, CH2 Output Voltage Ripple, (50mV/div) Middle: Io2, CH2 Output Current, (5A/div) Bottom: SWN2, CH2 Switching Node Voltage, (10V/div) Time: 50µs/div

Figure 25. Load Transient Response with Skip-Mode Operation (V<sub>0</sub>2 = 1.05 V, I<sub>0</sub>2 = 0.1 A-6 A-0.1 A)

Top: FPWM#, FPWM# Signal, (5V/div) Middle 1: Vo2, CH2 Output Voltage Ripple, (50mV/div) Middle 2: iL2, CH2 Inductor Current, (5A/div) Bottom: SWN2, CH2 Switching Node Voltage, (10V/div) Time: 50us/div

Figure 27. On-Line Mode-Changing Operation (V<sub>0</sub>2 = 1.05 V, I<sub>0</sub>2 = 0.2 A, FPWM-Skip Mode-FPWM)

#### **OPERATION DESCRIPTION**

#### General

The NCP5215. high-efficiency а and fast-transient-response dual-channel buck controller, provides a multifunctional power solution for notebook power system. 180° interleaved operation function between the two channels has capabilities of reducing the common input capacitor requirement and improving noise immunity. Adaptive-Voltage-Positioning (AVP) control reduces the requirement of output filter capacitors. Programmable power-saving operation ensures high efficiency over entire load range. Input feedforward voltage-mode control is employed to deal with wide input voltage range. Transient-Response-Enhancement (TRE) control for the both channels enables fast transient response.

#### **PWM Operation**

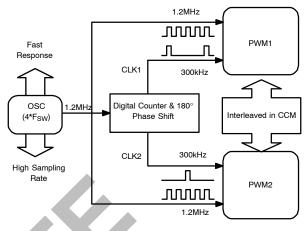

The NCP5215 operates at a pin-selectable normal operation switching frequency, allowing 200 kHz, 300 kHz, or 400 kHz. As shown in Table 1, the connection of the pin FSET determines normal operation frequency in continuous-conduction-mode (CCM).

#### Table 1. SWITCHING FREQUENCY SELECTION

| FSET Pin  | Float | VCC | GND |

|-----------|-------|-----|-----|

| Fsw (kHz) | 200   | 300 | 400 |

To speed up transient response and increase sampling rate, an internal high-frequency clock is employed, which frequency is four times of the selected normal operating frequency. As an instance, if the FSET pin is connected to  $V_{CC}$ , the normal switching frequency is set to 300 kHz. The internal high-frequency clock is 1.2 MHz. Figure 28 shows internal clocks of the NCP5215 in this case. The 1.2MHz high-frequency clock with 50% duty-ratio introduced to the two PWM channels. A digital circuitry generates two interleaved 300 kHz clocks using the 1.2 MHz clock and output them to the two PWM channels as normal operation clocks in CCM, respectively.

#### Forced-PWM Operation (FPWM Mode)

If the FPWM# pin is pulled low, the NCP5215 works under forced–PWM operation and thus always in CCM. The two channels always run in selected fixed frequency and 180° interleaved operation. In this mode, the low–side gate–drive signal is forced to be the complement of the high–side gate–drive signal. This mode allows reverse inductor current, in such a way that it provides more accurate voltage regulation and fast transient response.

During soft-start operation, the NCP5215 automatically runs in FPWM mode regardless of the FPWM# pin's setting to guarantee smooth powerup.

Figure 28. Internal Clocks in the NCP5215 as  $F_{SW} = 300 \text{ kHz}$

#### Light-Load Pulse-Skipping Operation (Skip Mode)

If the skip mode is enabled by pulling high FPWM# pin, the NCP5215 works in pulse-skipping enabled operation (PS).

In medium and high load range, the converter still runs in CCM, and the switching frequency is fixed as the selected frequency. If both channels run in CCM, they operate interleaved.

In light load range, the converter will enter skip mode if negative inductor current appears continuously. In the skip mode, the bottom MOSFET will be turned off when the inductor current is going negative. The top MOSFET's on-time is fixed to around 1.5 times as the on-time in CCM. The NCP5215 continuously monitors the voltage at FB pin and comparing to the voltage at VDRP Pin. When the FB voltage drops below the VDRP voltage, a fixed on-time will be initiated at the time of the next coming high-frequency clock edge, which can be either rising edge or falling edge. The minimum off-time is half high-frequency cycle.

When the load increases and the inductor current becomes continuous, the controller will automatically return to fixed-frequency operation and be synchronized to the normal operation clock.

#### **Transient Response Enhancement (TRE)**

In the skip mode, the operation of the NCP5215 is similar to constant on-time scheme. The response time of the controller is between half to one cycle of the high-frequency clock. However, for a conventional trailing-edge PWM controller in CCM, the fastest response time is one switching cycle in the worst case. To further improve transient response in CCM, a transient response enhancement circuitry is introduced to the NCP5215.

In CCM operation, the controller continuously monitors the output voltage (COMP) of the error amplifier to detect load transient events. As shown in Figure 1, there is a threshold voltage in each channel made in a way that a filtered COMP signal pluses an adjustable offset voltage, which is set by an external resistor. Once large load transient occurs, the COMP signal is possible to exceed the threshold and then TRE signal will be high in a short period, which is typically around one normal switching cycle. In this short period, the controller will be running at high frequency and therefore has faster response. After that the controller comes back to normal switching frequency operation. Figure 29 shows TRE effect on a load transient response.

Top: Vo (50mV/div), Middle: Transient signal (20V/div), Bottom: SWN (10V/div), Time: (10us/div) (a) TRE disabled

Top: Vo (50mV/div), Middle: Transient signal (20V/div), Bottom: SWN (10V/div), Time: (10us/div) (b) TRE enabled

#### Figure 29. Transient Response Comparison on TRE

The internal offset voltage of the TRE threshold is set by an external resistor  $R_{TRE}$  connected from the TRESET Pin to AGND.

$$V_{th\_TRE} = \frac{I_{TRE} \cdot R_{TRE}}{4}$$

(eq. 1)

where  $I_{TRE}$  is a sourcing current out the TRESET pin. A recommended value for  $V_{th_TRE}$  is around 1.5 times of peak-to-peak value of the COMP signal in CCM operation. The higher  $V_{th_TRE}$ , the lower sensitivity to load transient. The TRE function can be disabled by pulling high the TRESET pin to  $V_{CC}$  or just leaving it float.

#### Adaptive Voltage Positioning (AVP)

For applications with fast transient currents, adaptive voltage positioning can reduce peak-to-peak output voltage deviations due to load transients and allow use of a smaller output filter. Adaptive voltage positioning sets output voltage higher than nominal at light loads, and output voltage is allowed limited sag when the load current is applied. Upon removal of the load, output voltage returns no higher than the original level, allowing one output transient peak to be canceled over a load stepup and release cycle.

Figure 30 shows how AVP works. The waveform labeled "Vo without AVP" shows output voltage waveform in a converter without AVP. On the left, the output voltage sags when the output current is stepped up and later overshoots when current is stepped back down. With AVP, the peak-to-peak excursions are cut around in half. The controller can be configured to adjust the output voltage based on the output current of the converter as shown in Figure 31. In order to realize the AVP function, a resistor is connected between  $V_{REF}$  and  $V_{DRP}$  During no-load conditions, the VDRP Pin voltage stays at the same voltage level as the  $V_{REF}$ . As the output current increases, the VDRP Pin voltage decreases. This causes  $V_{OUT}$  to droop according to a loadline set by the resistor.

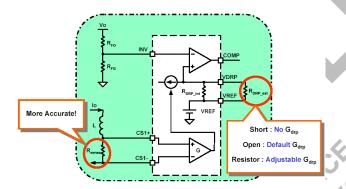

In the NCP5215, the output current of each channel is sensed differentially. A high gain and low offset-voltage differential amplifier in each channel allows low-resistance current-sensing resistor or low-DCR inductor to be used to minimize power dissipation. For lossless inductor current sensing as shown in Figure 31, the sensing RC network should satisfy

$$R_{CS} \times C_{CS} = \frac{L}{DCR}$$

(eq. 2)

where DCR is a DC resistance of a inductor, and normally  $C_{cs}$  is selected to be around 0.1  $\mu$ F. In high accuracy

applications, to compensate measurement error caused by temperature, an additional resistance network including a negative-temperature-coefficient (NTC) thermistor can be connected with  $C_{CS}$  in parallel.

Figure 31. Programmable AVP with Lossless Inductor Current Sensing

#### Figure 32. Figure 32. Programmable AVP with Resistive Current Sensing

The output voltage with AVP is

$$V_{O} = V_{OO} - I_{O} \cdot R_{LL}$$

(eq. 3)

where  $I_0$  is load current, no–load output voltage  $V_{00}$  is set by the external resistor divider, that is

$$V_{O0} = \left(1 + \frac{R_{FO}}{R_{FG}}\right) \cdot V_{REF}$$

(eq. 4)

$R_{FO}$  is a resistor connected between the output and the FB pin, and  $R_{FG}$  is a resistor connected between the FB Pin to AGND. The load-line impedance  $R_{LL}$  by the AVP function is given by

$$R_{LL} = DCR \text{ Gain}_CS \cdot \frac{R_{DRP\_ext}}{R_{DRP\_int} + R_{DRP\_ext}} \cdot \frac{V_{O0}}{V_{REF}}$$

where DCR is DC resistance of the inductor, Gain\_CS is a gain from [(CS+)-(CS-)] to (VDRP-VREF), R<sub>DRP\_int</sub> is a internal resistance connected between the output reference and the VDRP Pin, R<sub>DRP\_ext</sub> is a external resistance connected between the output reference and the VDRP pin.

If an additional current sensing resistor ( $R_{CS}$ ) is employed to improve accuracy, as shown in Figure 32, the load line resistance can be calculated by

$$R_{LL} = R_{CS} \operatorname{Gain}_{CS} \cdot \frac{R_{DRP\_ext}}{R_{DRP\_int} + R_{DRP\_ext}} \cdot \frac{V_{00}}{V_{REF}}^{(eq. 6)}$$

The AVP function can be easily disabled by shorting VDRP pin and VREF pin together.

#### **Control Logic**

t<sub>ss</sub> =

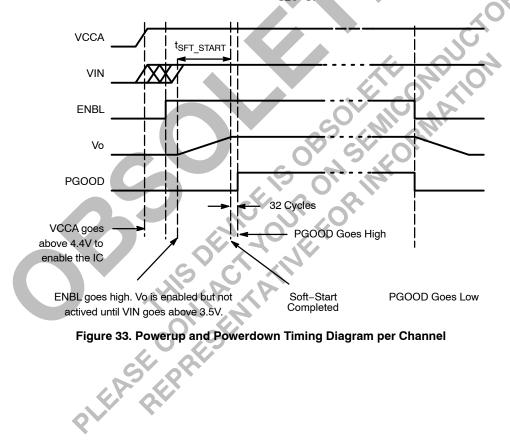

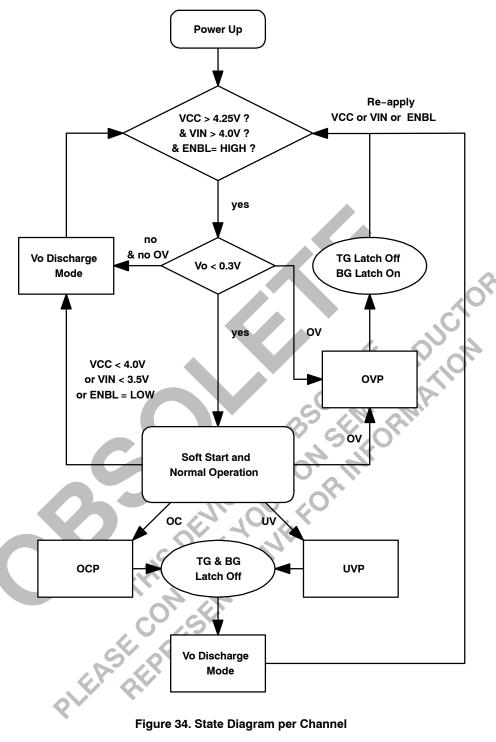

The internal control logic is powered by  $V_{CC}$ . Figure 33 shows a power–up and powerdown timing diagram for each channel. Figure 34 shows a state diagram for each channel.

The NCP5215 continuously monitors  $V_{CC}$  and  $V_{IN}$  level with an undervoltage lockout (UVLO) function. If both  $V_{CC}$  and  $V_{IN}$  are in operation range, and output voltage is below 0.3 V, the converter has a soft–start after ENBL signal goes high. The soft–start time is programmed by an external capacitor  $C_{SS}$  connected from the SS Pin to AGND, which can be calculated by

$$= \frac{0.8 \times C_{SS}}{I_{SS}}$$

(eq. 7)

where I<sub>SS</sub> is a sourcing current output from the SS pin.

When the ENBL goes low, or the internal fault latch is set by over current or output undervoltage, the device operates in soft stop and output discharge mode. The output is discharged to GND through an internal 12  $\Omega$  switch connected from the CS–/Vo pin to the PGND Pin, until the output voltage decreases to 0.3 V. Also if restart the system when the output voltage is still above 0.3 V, the device will discharge the output voltage to 0.3 V first and then start soft–start.

#### **Overcurrent Protection (OCP)**

The NCP5215 protects power system if overcurrent occurs. The current through each channel is continuously monitored with the differential current sense. Current limit threshold is related to an external voltage at the  $I_{LIM}$  pin, which is normally produced by an external resistor divider ( $R_{il1}$  and  $R_{il2}$ ) connected from the  $V_{REF}$  pin to AGND. The current–limit threshold for peak current is set by

$$I_{\text{LIM(Peak)}} = 0.2 \cdot \frac{\mathsf{R}_{\text{il2}} \cdot \mathsf{V}_{\text{REF}}}{\left(\mathsf{R}_{\text{il1}} + \mathsf{R}_{\text{il2}}\right) \cdot \mathsf{DCR}} \tag{eq. 8}$$

or

$$I_{\text{LIM}(\text{Peak})} = 0.2 \cdot \frac{R_{\text{il2}} \cdot V_{\text{REF}}}{\left(R_{\text{il1}} + R_{\text{il2}}\right) \cdot R_{\text{CS}}} \tag{eq. 9}$$

If inductor current exceeds the current threshold continuously, the top gate drive will be turned off cycle–by–cycle. In the meanwhile, an internal fault timer will be triggered to count normal operation clock. After 16 continuous clock pulses, if the fault still exists the part latches off, both the top gate drive and the bottom gate drive

are turned off and their outputs are float. The fault remains set until the system has shutdown and re-applied power or the enable input signal to the regulator controller has toggled states.

#### **Overvoltage Protection (OVP)**

An OVP circuit monitors the output voltages to prevent from over voltage. OVP limit is typically 117% of the nominal output voltage level. If the output voltage is above this threshold, an OV fault is set, the top gate drive is turned OFF, and then the bottom gate drive is latched ON to discharge the output. The fault remains set until the system has shutdown and re–applied power or the enable input signal to the regulator controller has toggled states.

#### Undervoltage Protection (UVP)

A UVP circuit monitors the output voltages to detect undervoltage. UVP limit is 68% of the nominal output voltage level. If the output voltage is below this threshold, a UV fault is set. If an OV protection is set before, the bottom gate drive is forced high. If no OV protection set, an internal fault timer will be triggered to count normal operation clock. After 16 continuous clock pulses, if the fault still exists the part latches off, both the top gate drive and the bottom gate drive are turned off and their outputs are float. The fault remains set until the system has shutdown and re–applied power or the enable input signal to the regulator controller has toggled states.

#### **Thermal Protection**

The NCP5215 has a thermal shutdown protection to protect the device from overheating when the die temperature exceeds  $150^{\circ}$ C. Once the thermal protection is triggered, the fault state can be ended by re–applying V<sub>CC</sub>, V<sub>IN</sub>, or ENBL when the temperature drops down below 120°C.

Figure 34. State Diagram per Channel

| ltem | PCS | Part<br>Reference | Description                                                              | Value  | Package | Part Number    | Manufacturer     |

|------|-----|-------------------|--------------------------------------------------------------------------|--------|---------|----------------|------------------|

| 1    | 1   | IC1               | NCP5215                                                                  |        | QFN40   | NCP5215MNR2G   | ON Semiconductor |

| 2    | 4   | M1, M2,<br>M3, M4 | Power MOSFET 30 V, 12 A,<br>Single N–Channel SO–8                        |        | SO8     | NTMS4705N      | ON Semiconductor |

| 3    | 2   | Db1, Db2          | Schottky Diode, 30V                                                      |        | SC70    | BAT54WT1G      | ON Semiconductor |

| 4    | 2   | Cdp1,             | MLCC Cap 50V, ±5%, Char:                                                 | 47pF   | 0603    | ECJ1VB1H470J   | Panasonic        |

|      |     | Cdp2              | COG                                                                      |        |         | C1608C0G1H470J | TDK              |

| 5    | 2   | C11, C22          | MLCC Cap 50V, ±5%, Char:                                                 | 68pF   | 0603    | ECJ1VB1H680J   | Panasonic        |

|      |     |                   | COG                                                                      |        |         | C1608C0G1H680J | TDK              |

| 6    | 2   | C12, C22          | MLCC Cap 50V, ±5%, Char:                                                 | 220pF  | 0603    | ECJ1VC1H221J   | Panasonic        |

|      |     |                   | COG                                                                      |        |         | C1608C0G1H221J | TDK              |

| 7    | 1   | C23               | MLCC Cap 50V, ±5%, Char:                                                 | 820pF  | 0603    | ECJ1VC1H821J   | Panasonic        |

|      |     |                   | COG                                                                      |        |         | C1608C0G1H821J | TDK              |

| 8    | 1   | C13               | MLCC Cap 50V, ±5%, Char:                                                 | 1000pF | 0603    | ECJ1VC1H102J   | Panasonic        |

|      |     |                   | COG                                                                      |        |         | C1608C0G1H102J | TDK              |

| 9    | 2   | CSS1,             | MLCC Cap 50V, ±10%, Char:                                                | 4700pF | 0603    | ECJ1VB1H472K   | Panasonic        |

|      |     | CSS2              | X7R                                                                      |        |         | C1608X7R1H472K | ТДК              |

| 10   | 1   | CIF               | MLCC Cap 50V, ±10%, Char:                                                | 15nF   | 0603    | ECJ1VB1H153K   | Panasonic        |

|      |     |                   | X7R                                                                      |        | 51      | C1608X7R1H153K | TDK              |

| 11   | 4   | Cb1, Cb2,         | MLCC Cap 16V, ±10%, Char:                                                | 0.1µF  | 0603    | ECJ1VB1C104K   | Panasonic        |

|      |     | Cs1, Cs2          | X7R                                                                      | S      |         | C1608X7R1H104K | TDK              |

| 12   | 4   | Ccf, Cpf1,        | MLCC Cap 25V, ±10%, Char:                                                | 1μF    | 0805    | ECJ2FB1E105K   | Panasonic        |

|      |     | Cpf2, Cref        | X5R                                                                      |        |         | C3216X5R1H105K | TDK              |

| 13   | 2   | Co11,             | MLCC Cap 10V, ±20%, Char:                                                | 10µF   | 0805    | ECJ3YB1C106M   | Panasonic        |

|      |     | Co21              | X7R                                                                      |        |         | C3216X7R1C106M | TDK              |

| 14   | 2   | CIN1,<br>CIN2     | MLCC Cap 25V, ±20%, Char:<br>X7R                                         | 10μF   | 1812    | C4532X7R1E106M | TDK              |

| 15   | 3   | Co1, Co2<br>(x2)  | SP–Cap/Polymer Aluminum Capacitors, 22 $\mu$ F, 2 V, ESR = 12 m $\Omega$ | 220µF  | 7343    | EEFUD0D221XR   | Panasonic        |

| 16   | 2   | Rcf, Rif          | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 20Ω    | 0603    | ERJ3EKF20R0V   | Panasonic        |

| 17   | 1   | R13               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 750Ω   | 0603    | ERJ3EKF7500V   | Panasonic        |

| 18   | 1   | R23               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 910Ω   | 0603    | ERJ3EKF9100V   | Panasonic        |

| 19   | 1   | Rdp1              | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 2kΩ    | 0603    | ERJ3EKF2001V   | Panasonic        |

| 20   | 1   | Rdp2              | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 3kΩ    | 0603    | ERJ3EKF3001V   | Panasonic        |

| 21   | 1   | RS1               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 3.6kΩ  | 0603    | ERJ3EKF3601V   | Panasonic        |

| 22   | 1   | RS2               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 4.3kΩ  | 0603    | ERJ3EKF4301V   | Panasonic        |

| 23   | 1   | R11               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%              | 10kΩ   | 0603    | ERJ3EKF1002V   | Panasonic        |

#### Table 2. BILL OF MATERIALS FOR THE TYPICAL APPLICATION

| Item | PCS | Part<br>Reference | Description                                                       | Value         | Package | Part Number    | Manufacturer |

|------|-----|-------------------|-------------------------------------------------------------------|---------------|---------|----------------|--------------|

| 24   | 1   | R14               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm 1\%$      | 11kΩ          | 0603    | ERJ3EKF1102V   | Panasonic    |

| 25   | 1   | R21               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 13kΩ          | 0603    | ERJ3EKF1302V   | Panasonic    |

| 26   | 2   | R24, Ril22        | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 36kΩ          | 0603    | ERJ3EKF3602V   | Panasonic    |

| 27   | 1   | R12               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 75kΩ          | 0603    | ERJ3EKF7502V   | Panasonic    |

| 28   | 1   | Ril12             | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 82kΩ          | 0603    | ERJ3EKF8202V   | Panasonic    |

| 29   | 2   | Ril11,<br>Ril21   | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 100k $\Omega$ | 0603    | ERJ3EKF1003V   | Panasonic    |

| 30   | 2   | R22, Rt2          | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm$ 1%       | 200kΩ         | 0603    | ERJ3EKF2003V   | Panasonic    |

| 31   | 1   | Rt1               | Thick Film Chip Resistors, Power Rating 0.1W, Tol: $\pm 1\%$      | 390kΩ         | 0603    | ERJ3EKF3903V   | Panasonic    |

| 32   | 1   | L1                | Power Choke Coil, DCR = 7.0m $\Omega$ , IDC = 12A, ISAT = 27A     | 2.2µH         |         | PCMC104T-2R2MN | Cyntec       |

| 33   | 1   | L2                | Power Choke Coil, DCR = $4.2m\Omega$ , IDC = $16A$ , ISAT = $33A$ | 1.5μΗ         |         | PCMC104T-1R5MN | Cyntec       |

220H POMCIONT-26 220H POMCIONT-26 33A

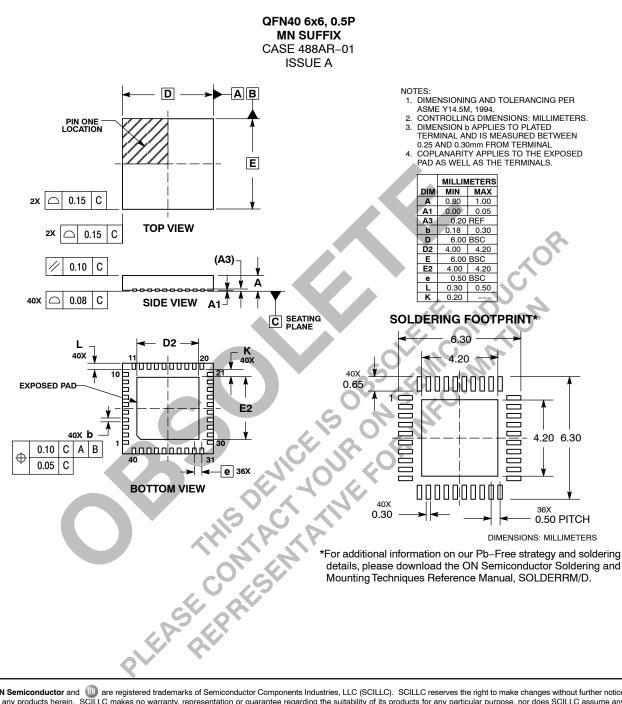

#### PACKAGE DIMENSIONS

ON Semiconductor and ()) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be validated for each customer applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use as and expenses, and is not for regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

#### ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850

For additional information, please contact your loca Sales Representative