Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Three-Phase VRM 9.0 Buck Controller

Multiphase controllers provide fast, accurate regulation with the control features required to power the next generation of processors in desktop, workstation and server applications. Combined with external gate drivers and power components, the NCP5306 implements a compact, highly integrated buck converter. Enhanced V<sup>2™</sup> control inherently compensates for variations in both line and load. Current sharing between phases is achieved by Peak Current Sharing.

The NCP5306 includes Power Good with a programmable lower threshold.

Applications include Embedded Processor Power and low voltage/high current power supplies.

#### **Features**

- Switching Regulator Controller

- Lossless Current Sensing

- Enhanced V<sup>2</sup> Control Method Provides Excellent Regulation and Fast Transient Response

- Programmable Up to 800 kHz Switching Frequency (Per Phase)

- Duty Cycle 0% to 100%

- Programmable Adaptive Voltage Positioning Reduces Output Capacitor Requirements

- Programmable Soft Start

- Accurate Current Sharing

- Protection Features

- Pulse-by-Pulse Current Limit for Each Phase

- Programmable Hiccup Overcurrent Protection

- All "1" DAC Code Fault

- Processor Overvoltage Protection through Bottom MOSFETs

- Undervoltage Lockout

- System Power Management

- 5-Bit DAC With 1.0% Tolerance Compatible with VRM 9.0

- Power Good Output

- Programmable Power Good Lower Threshold

- Guaranteed Startup at -20°C

## ON Semiconductor®

http://onsemi.com

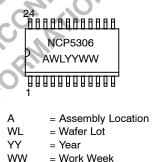

#### **MARKING DIAGRAM**

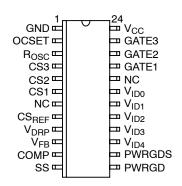

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Device      | Package | Shipping         |

|-------------|---------|------------------|

| NCP5306DW   | SO-24L  | 30 Units/Rail    |

| NCP5306DWR2 | SO-24L  | 1000 Tape & Reel |

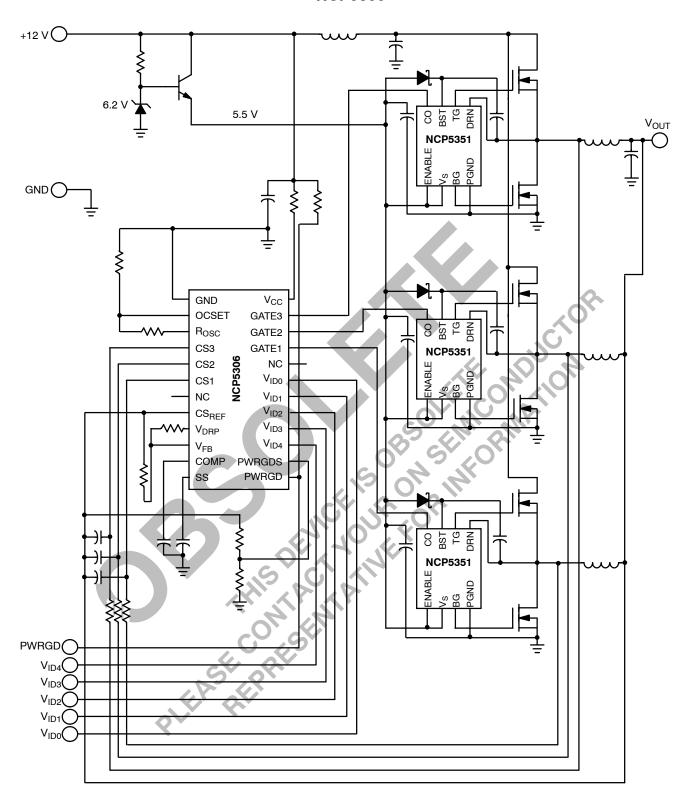

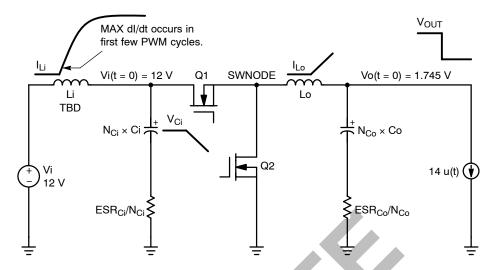

Figure 1. Application Diagram, 12 V to 1.5 V/60 A Three-Phase Converter

#### **MAXIMUM RATINGS\***

| Rating                                                                                            | Value      | Unit         |

|---------------------------------------------------------------------------------------------------|------------|--------------|

| Operating Junction Temperature                                                                    | 150        | °C           |

| Storage Temperature Range                                                                         | -65 to 150 | °C           |

| ESD Susceptibility (Human Body Model)                                                             | 2.0        | kV           |

| Package Thermal Resistance Junction-to-Case, $R_{\theta JC}$ Junction-to-Ambient, $R_{\theta JA}$ | 16<br>80   | °C/W<br>°C/W |

| Lead Temperature Soldering: Reflow (Note 1.)                                                      | 230 peak   | °C           |

| MSL                                                                                               | Level 1    | _            |

<sup>1. 60</sup> second maximum above 183°C.

## **MAXIMUM RATINGS**

| Pin Number | Pin Symbol                         | V <sub>MAX</sub> | V <sub>MIN</sub> | ISOURCE                  | ISINK                   |

|------------|------------------------------------|------------------|------------------|--------------------------|-------------------------|

| 1          | GND                                | N/A              | N/A              | 0.4 A, 1.0 μs, 100 mA DC | N/A                     |

| 2          | OCSET                              | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 3          | R <sub>OSC</sub>                   | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 4–6        | CS3-CS1                            | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 7, 20      | NC                                 |                  | N/A              | 0,40 "                   | -                       |

| 8          | CS <sub>REF</sub>                  | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 9          | V <sub>DRP</sub>                   | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 10         | V <sub>FB</sub>                    | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 11         | COMP                               | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 12         | SS                                 | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 13         | PWRGD                              | 18 V             | -0.3 V           | 1.0 mA                   | 10 mA                   |

| 14         | PWRGDS                             | 7.0 V            | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 15–19      | V <sub>ID4</sub> -V <sub>ID0</sub> | 18 V             | -0.3 V           | 1.0 mA                   | 1.0 mA                  |

| 21-23      | GATE1-GATE3                        | 7.0 V            | -0.3 V           | 0.1 A, 1.0 μs, 25 mA DC  | 0.1 A, 1.0 μs, 25 mA DC |

| 24         | V <sub>CC</sub>                    | 18 V             | -0.3 V           | 100 mA                   | 1.0 mA                  |

|            | Vcc<br>Pl///ASK                    | EPRES            |                  |                          |                         |

<sup>\*</sup>The maximum package power dissipation must be observed.

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} & (0^{\circ}C < T_{A} < 70^{\circ}C; \ 0^{\circ}C < T_{J} < 125^{\circ}C; \ 9.5 \ V < V_{CC} < 14 \ V; \ C_{GATEx} = 100 \ pF, \\ C_{COMP} = 0.01 \mu F, \ C_{SS} = 0.1 \mu F, \ C_{VCC} = 0.1 \mu F, \ R_{ROSC} = 32.4 \ k\Omega, \ V_{OCSET} = 0.54 \ V, \ DAC \ Code \ 01110; \ unless \ otherwise \ stated.) \end{array}$

|                  | Pa                | aramet           | er               |                  | Test Conditions                                                                                           | Min                 | Тур             | Max        | Unit |

|------------------|-------------------|------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------|---------------------|-----------------|------------|------|

| Voltaç           | ge Iden           | tificatio        | on DAC           | (0 = C           | onnected to GND, 1 = Open or Pull-U                                                                       | p to Internal 3.3 V | or External Vol | tage 12 V) | 1    |

|                  | ıracy (a<br>ocode | ll code:         | 5)               |                  | Connect V <sub>FB</sub> to COMP,<br>Measure COMP                                                          | -1.0                | -               | +1.0       | %    |

| $V_{\text{ID4}}$ | $V_{\text{ID3}}$  | $V_{\text{ID2}}$ | $V_{\text{ID1}}$ | $V_{\text{ID0}}$ |                                                                                                           |                     |                 |            |      |

| 1                | 1                 | 1                | 1                | 1                |                                                                                                           |                     | Output Off      |            |      |

| 1                | 1                 | 1                | 1                | 0                |                                                                                                           | 1.089               | 1.100           | 1.111      | V    |

| 1                | 1                 | 1                | 0                | 1                |                                                                                                           | 1.114               | 1.125           | 1.136      | V    |

| 1                | 1                 | 1                | 0                | 0                |                                                                                                           | 1.139               | 1.150           | 1.162      | V    |

| 1                | 1                 | 0                | 1                | 1                |                                                                                                           | 1.163               | 1.175           | 1.187      | V    |

| 1                | 1                 | 0                | 1                | 0                |                                                                                                           | 1.188               | 1.200           | 1.212      | V    |

| 1                | 1                 | 0                | 0                | 1                |                                                                                                           | 1.213               | 1.225           | 1.237      | V    |

| 1                | 1                 | 0                | 0                | 0                |                                                                                                           | 1.238               | 1.250           | 1.263      | V    |

| 1                | 0                 | 1                | 1                | 1                |                                                                                                           | 1.263               | 1.275           | 1.288      | V    |

| 1                | 0                 | 1                | 1                | 0                |                                                                                                           | 1.287               | 1.300           | 1.313      | V    |

| 1                | 0                 | 1                | 0                | 1                |                                                                                                           | 1.312               | 1.325           | 1.338      | V    |

| 1                | 0                 | 1                | 0                | 0                |                                                                                                           | 1.337               | 1.350           | 1.364      | V    |

| 1                | 0                 | 0                | 1                | 1                |                                                                                                           | 1.361               | 1.375           | 1.389      | V    |

| 1                | 0                 | 0                | 1                | 0                |                                                                                                           | 1.386               | 1.400           | 1.414      | V    |

| 1                | 0                 | 0                | 0                | 1                | C                                                                                                         | 1.411               | 1.425           | 1.439      | V    |

| 1                | 0                 | 0                | 0                | 0                |                                                                                                           | 1.436               | 1.450           | 1.465      | V    |

| 0                | 1                 | 1                | 1                | 1                |                                                                                                           | 1.460               | 1.475           | 1.490      | V    |

| 0                | 1                 | 1                | 1                | 0                | 10                                                                                                        | 1.485               | 1.500           | 1.515      | V    |

| 0                | 1                 | 1                | 0                | 1                |                                                                                                           | 1.510               | 1.525           | 1.540      | V    |

| 0                | 1                 | 1                | 0                | 0                |                                                                                                           | 1.535               | 1.550           | 1.566      | V    |

| 0                | 1                 | 0                | 1                | 1                | 7,71,71,                                                                                                  | 1.560               | 1.575           | 1.591      | V    |

| 0                | 1                 | 0                | 1                | 0                | 60, 66,                                                                                                   | 1.584               | 1.600           | 1.616      | V    |

| 0                | 1                 | 0                | 0                | 1                |                                                                                                           | 1.609               | 1.625           | 1.641      | V    |

| 0                | 1                 | 0                | 0                | 0                | 5,04                                                                                                      | 1.634               | 1.650           | 1.667      | V    |

| 0                | 0                 | 1                | 1                | 1                |                                                                                                           | 1.658               | 1.675           | 1.692      | V    |

| 0                | 0                 | 1                | 1                | 0                |                                                                                                           | 1.683               | 1.700           | 1.717      | V    |

| 0                | 0                 | 1                | 0                | 1                |                                                                                                           | 1.708               | 1.725           | 1.742      | V    |

| 0                | 0                 | 1                | 0                | 0                |                                                                                                           | 1.733               | 1.750           | 1.768      | V    |

| 0                | 0                 | 0                | 1                | 1                |                                                                                                           | 1.757               | 1.775           | 1.793      | V    |

| 0                | 0                 | 0                | 1                | 0                |                                                                                                           | 1.782               | 1.800           | 1.818      | V    |

| 0                | 0                 | 0                | 0                | 1                |                                                                                                           | 1.807               | 1.825           | 1.843      | V    |

| 0                | 0                 | 0                | 0                | 0                |                                                                                                           | 1.832               | 1.850           | 1.869      | V    |

| Input            | t Thresh          | nold             |                  |                  | $V_{ID4},V_{ID3},V_{ID2},V_{ID1},V_{ID0}$                                                                 | 1.00                | 1.25            | 1.5        | V    |

| Input            | t Pull-U          | lp Resi          | stance           |                  | $ \begin{array}{l} 0 \; V < V_{ID4}, \; V_{ID3}, \; V_{ID2}, V_{ID1}, \\ V_{ID0} < 3.3 \; V \end{array} $ | 25                  | 50              | 100        | kΩ   |

$\label{eq:continued} \textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (0^{\circ}\text{C} < T_{A} < 70^{\circ}\text{C}; \ 0^{\circ}\text{C} < T_{J} < 125^{\circ}\text{C}; \ 9.5 \ \text{V} < \text{V}_{CC} < 14 \ \text{V}; \ C_{GATEx} = 100 \ \text{pF}, \\ C_{COMP} = 0.01 \mu\text{F}, \ C_{SS} = 0.1 \mu\text{F}, \ C_{VCC} = 0.1 \mu\text{F}, \ R_{ROSC} = 32.4 \ \text{k}\Omega, \ \text{V}_{OCSET} = 0.54 \ \text{V}, \ DAC \ Code \ 01110; \ unless \ otherwise \ stated.)$

| Parameter                                                                    | Test Conditions                                                                                                                                                                                                      | Min                 | Тур                | Max                 | Unit |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|------|

| Voltage Identification DAC (0 =                                              | Connected to GND, 1 = Open or Pull-U                                                                                                                                                                                 | p to Internal 3.3 V | or External Vol    | tage 12 V) (continu | red) |

| Pull-Up Voltage                                                              | 1.0 MΩ to GND                                                                                                                                                                                                        | 2.5                 | 2.7                | 3.0                 | V    |

| Power Good Output                                                            |                                                                                                                                                                                                                      |                     |                    | 1                   |      |

| Upper Threshold                                                              | Threshold Force PWRGDS                                                                                                                                                                                               |                     | 1.975              | 2.074 (+5%)         | V    |

| Lower Threshold                                                              | Force PWRGDS                                                                                                                                                                                                         | -5%                 | V <sub>ID</sub> /2 | +5%                 | V    |

| Switch Leakage Current                                                       | V <sub>CC</sub> = 14 V, PWRGDS = 1.4 V                                                                                                                                                                               | -                   | 0.1                | 1.0                 | μΑ   |

| Delay                                                                        | PWRGDS low to PWRGD low                                                                                                                                                                                              | 100                 | 800                | 2000                | μs   |

| Output Low Voltage                                                           | PWRGDS = 1.0 V,<br>I <sub>PWRGD</sub> = 4.0 mA                                                                                                                                                                       | -                   | 0.15               | 0.4                 | V    |

| Voltage Feedback Error Amplif                                                | lier                                                                                                                                                                                                                 |                     |                    |                     |      |

| V <sub>FB</sub> Bias Current                                                 | Note 2                                                                                                                                                                                                               | 9.9                 | 10.25              | 10.6                | μΑ   |

| Comp Source Current                                                          | COMP = 0.5 V to 2.0 V,<br>V <sub>FB</sub> = 1.8 V, DAC = 00000                                                                                                                                                       | 15                  | 30                 | 60                  | μА   |

| Comp Sink Current                                                            | COMP = 0.5 V to 2.0 V,<br>V <sub>FB</sub> = 1.15 V, DAC = 11110                                                                                                                                                      | 15                  | 30                 | 60                  | μА   |

| Transconductance                                                             | -10 μA < I <sub>COMP</sub> < +10 μA, Note 3                                                                                                                                                                          | 200                 | 500                | 750                 | μmho |

| Output Impedance                                                             |                                                                                                                                                                                                                      | -0                  | 2.5                | _                   | MΩ   |

| Open Loop DC Gain                                                            | Note 3                                                                                                                                                                                                               | 45                  | 95                 | _                   | dB   |

| Unity Gain Bandwidth                                                         |                                                                                                                                                                                                                      | 0,-2,               | 50                 | -                   | kHZ  |

| PSRR @ 1.0 kHz                                                               | - (                                                                                                                                                                                                                  | 02 12               | 60                 | -                   | dB   |

| COMP Max Voltage                                                             | V <sub>FB</sub> = 0 V                                                                                                                                                                                                | 2.4                 | 2.7                | _                   | V    |

| COMP Min Voltage                                                             | V <sub>FB</sub> = 1.6 V                                                                                                                                                                                              | 2, °Ö.              | 50                 | 150                 | mV   |

| PWM Comparators                                                              |                                                                                                                                                                                                                      |                     |                    |                     |      |

| Minimum Pulse Width                                                          | 6-7                                                                                                                                                                                                                  | _                   | 40                 | 70                  | ns   |

| Transient Response Time                                                      | $\label{eq:measured from CS_REF} \begin{tabular}{ll} Measured from CS_{REF} to GATEx, \\ COMP = 2.1 \ V, \\ CSx = CS_{REF} = 0.5 \ V, \\ CS_{REF} \begin{tabular}{ll} Stepped from 1.2 \ V-2.0 \ V \\ \end{tabular}$ | _                   | 40                 | 60                  | ns   |

| Channel Start-Up Offset $ \begin{aligned}                                  $ |                                                                                                                                                                                                                      | 350                 | 600                | 750                 | mV   |

| Artificial Ramp Amplitude                                                    | 50% Duty Cycle, Note 3                                                                                                                                                                                               | -                   | 115                | -                   | mV   |

| Gates                                                                        |                                                                                                                                                                                                                      |                     |                    |                     |      |

| High Voltage                                                                 | Measure GATEx<br>I <sub>GATEx</sub> = 1.0 mA                                                                                                                                                                         | 2.0                 | 2.6                | 3.0                 | V    |

| Low Voltage                                                                  | Measure GATEx, I <sub>GATEx</sub> = 1.0 mA                                                                                                                                                                           | _                   | 0.5                | 0.7                 | V    |

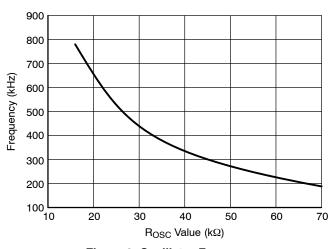

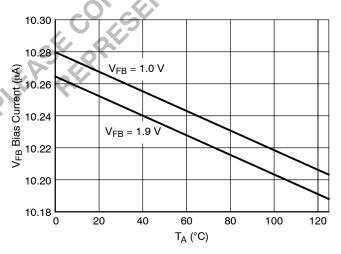

<sup>2.</sup> The  $V_{FB}$  Bias Current changes with the value of  $R_{OSC}$  per Figure 4. 3. Guaranteed by design. Not tested in production.

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (0^{\circ}\text{C} < \text{T}_{A} < 70^{\circ}\text{C}; \ 0^{\circ}\text{C} < \text{T}_{J} < 125^{\circ}\text{C}; \ 9.5 \ \text{V} < \text{V}_{CC} < 14 \ \text{V}; \ C_{GATEx} = 100 \ \text{pF}, \\ C_{COMP} = 0.01 \mu\text{F}, \ C_{SS} = 0.1 \mu\text{F}, \ C_{VCC} = 0.1 \mu\text{F}, \ R_{ROSC} = 32.4 \ \text{k}\Omega, \ \text{V}_{OCSET} = 0.54 \ \text{V}, \ DAC \ Code \ 01110; \ unless \ otherwise \ stated.) \\ \end{array}$

| Parameter                                                                                       | Test Conditions                                                                                                                                                                                                            | Min     | Тур  | Max         | Unit   |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------------|--------|

| Gates                                                                                           |                                                                                                                                                                                                                            |         | •    |             | •      |

| Rise Time                                                                                       | 0.8 V < GATEx < 2.0 V,<br>V <sub>CC</sub> = 10 V                                                                                                                                                                           | -       | 5.0  | 20          | ns     |

| Fall Time $2.0 \text{ V} > \text{GATEx} > 0.8 \text{ V},$ $\text{V}_{\text{CC}} = 10 \text{ V}$ |                                                                                                                                                                                                                            | -       | 5.0  | 20          | ns     |

| Oscillator                                                                                      |                                                                                                                                                                                                                            |         | 1    |             |        |

| Switching Frequency                                                                             | R <sub>OSC</sub> = 32.4 kΩ                                                                                                                                                                                                 | 300 400 |      | 500         | kHz    |

| Switching Frequency                                                                             | $R_{OSC}$ = 66.5 k $\Omega$ , Note 4                                                                                                                                                                                       | 150     | 200  | 250         | kHz    |

| Switching Frequency                                                                             | $R_{OSC}$ = 15.4 k $\Omega$ , Note 4                                                                                                                                                                                       | 600     | 800  | 1000        | kHz    |

| R <sub>OSC</sub> Voltage                                                                        |                                                                                                                                                                                                                            | 0.90    | 1.00 | 1.10        | V      |

| Phase Delay                                                                                     | -                                                                                                                                                                                                                          | 105     | 120  | 140         | deg    |

| Adaptive Voltage Positioning                                                                    |                                                                                                                                                                                                                            |         | *    | <b>∠</b> 0' |        |

| V <sub>DRP</sub> Output Voltage to<br>DAC <sub>OUT</sub> Offset                                 | CSx = CS <sub>REF</sub> , V <sub>FB</sub> = COMP,<br>Measure V <sub>DRP</sub> - COMP                                                                                                                                       | -5.0    | 0    | 5.0         | mV     |

| Maximum V <sub>DRP</sub> Voltage                                                                | $\begin{aligned} & \text{CSx} - \text{CS}_{\text{REF}} = 50 \text{ mV}, \\ & \text{V}_{\text{FB}} = \text{COMP}, \text{T}_{\text{A}} = 25^{\circ}\text{C}, \\ & \text{Measure V}_{\text{DRP}} - \text{COMP} \end{aligned}$ | 500     | 560  | 625         | mV     |

| Current Sense Input<br>to V <sub>DRP</sub> Gain                                                 | $CSx - CS_{REF} = 50 \text{ mV},$<br>$V_{FB} = COMP, T_A = 25^{\circ}C,$<br>$Measure V_{DRP} - COMP$                                                                                                                       | 3.33    | 3.75 | 4.17        | V/V    |

| Temperature Coefficient of V <sub>DRP</sub> Gain                                                | (V@temp - V@room) · 10 <sup>6</sup><br>ΔT · V@room                                                                                                                                                                         | 01/1/1  | -850 | _           | ppm/°C |

| V <sub>DRP</sub> Source Current Limit                                                           | CSx - CS <sub>REF</sub> = 50 mV,<br>V <sub>FB</sub> = COMP, Measure V <sub>DRP</sub> -<br>COMP V <sub>DRP</sub> = 1.5 V                                                                                                    | 1.0     | 7.0  | 14          | mA     |

| Soft Start                                                                                      | 00,4                                                                                                                                                                                                                       |         |      |             |        |

| SS Source Current                                                                               | V <sub>CC</sub> = 10 V                                                                                                                                                                                                     | 130     | 160  | 200         | μΑ     |

| SS Sink Current                                                                                 | V <sub>CC</sub> = 7.0 V                                                                                                                                                                                                    | 4.0     | 5.0  | 6.25        | μА     |

| SS Min Threshold                                                                                | V <sub>CC</sub> = 10 V                                                                                                                                                                                                     | 0.25    | 0.3  | 0.35        | V      |

| SS Max Threshold                                                                                | V <sub>CC</sub> = 10 V                                                                                                                                                                                                     | 2.4     | 2.7  | -           | V      |

| SS Source/Sink Ratio                                                                            |                                                                                                                                                                                                                            | 20      | 32   | 48          | _      |

| SS COMP Pull Down Current                                                                       | V <sub>CC</sub> = 10 V                                                                                                                                                                                                     | 200     | 900  | 3000        | μΑ     |

| Current Sense Amplifiers                                                                        | C. O.                                                                                                                                                                                                                      |         |      |             |        |

| CS <sub>REF</sub> Input Bias Current                                                            | CS <sub>REF</sub> = CSx = 0 V                                                                                                                                                                                              | -       | 2.6  | 3.0         | μΑ     |

| CSx Input Bias Current                                                                          | CS <sub>REF</sub> = CSx = 0 V                                                                                                                                                                                              | _       | 0.1  | 1.0         | μΑ     |

| Sense Amp Gain                                                                                  | CS <sub>REF</sub> = 0 V, CSx = 0.05 V,<br>Measure V(COMP) when GATEx<br>switches high                                                                                                                                      | _       | 2.60 | -           | V/V    |

| Common Mode Input Range                                                                         | Note 4                                                                                                                                                                                                                     | 0       | -    | 2.0         | V      |

| Bandwidth                                                                                       | -                                                                                                                                                                                                                          | -       | 7.0  | -           | MHz    |

| Single Phase Pulse by Pulse<br>Current Limit                                                    | V <sub>FB</sub> = CS <sub>REF</sub> = 1.5 V, COMP = 2.0 V, Measure CSx - CS <sub>REF</sub> when GATEx goes low                                                                                                             | 75      | 85   | 100         | mV     |

<sup>4.</sup> Guaranteed by design. Not tested in production.

$\label{eq:continued} \textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (0^{\circ}\text{C} < T_{A} < 70^{\circ}\text{C}; \ 0^{\circ}\text{C} < T_{J} < 125^{\circ}\text{C}; \ 9.5 \ V < V_{CC} < 14 \ V; \ C_{GATEx} = 100 \ pF, \\ C_{COMP} = 0.01 \mu\text{F}, \ C_{SS} = 0.1 \mu\text{F}, \ C_{VCC} = 0.1 \mu\text{F}, \ R_{ROSC} = 32.4 \ k\Omega, \ V_{OCSET} = 0.54 \ V, \ DAC \ Code \ 01110; \ unless \ otherwise \ stated.)$

| 7 7 66 7 7 1066 7 7 1066             |                                                                                   |     |     |     |       |  |

|--------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| Parameter                            | Test Conditions                                                                   | Min | Тур | Max | Unit  |  |

| Current Sense Amplifiers             |                                                                                   |     | ,   |     | *     |  |

| OCSET Input Bias Current             | OCSET = 0 V                                                                       | _   | 0.1 | 1.0 | μΑ    |  |

| Current Sense Input to OCSET<br>Gain | OCSET/(CSx-CS <sub>REF</sub> ), 0.25 V <<br>OCSET < 0.6 V, GATEx not<br>switching | 3.2 | 3.7 | 4.3 | V/V   |  |

| Current Limit Filter Slew Rate       | CS <sub>REF</sub> = 1.1 V, CSx = 1.0 V, pulse<br>CSx to 1.16 V, Note 5.           | 2.0 | 5.0 | 13  | mV/μs |  |

| General Electrical Specification     |                                                                                   |     |     |     |       |  |

| V <sub>CC</sub> Operating Current    | COMP = 0.3 V (no switching)                                                       | -   | 20  | 30  | mA    |  |

| UVLO Start Threshold                 | SS Charging Gates Switching                                                       | 8.5 | 9.0 | 9.5 | V     |  |

| UVLO Stop Threshold                  | Gates not switching, SS & COMP discharging                                        | 7.5 | 8.0 | 8.5 | V     |  |

| UVLO Hysteresis                      | Start-Stop                                                                        | 0.8 | 1.0 | 1.2 | V     |  |

<sup>5.</sup> Guaranteed by design. Not tested in production.

#### **PACKAGE PIN DESCRIPTION**

| Die Number | Din Cumbal                         | Din Name                                  | F(11)                                                                                                                                                                                  |

|------------|------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Pin Symbol                         | Pin Name                                  | Function                                                                                                                                                                               |

| 1          | GND                                | Ground                                    | IC power supply return. Connected to IC substrate.                                                                                                                                     |

| 2          | OCSET                              | Overcurrent Set                           | Resistor divider from $R_{\mbox{\scriptsize OSC}}$ to GND. Programs the threshold of the hiccup overcurrent protection.                                                                |

| 3          | R <sub>OSC</sub>                   | Oscillator Frequency<br>Adjust            | R <sub>OSC</sub> is a regulated 1.0 V output and programs the oscillator frequency with a resistor to GND.                                                                             |

| 4–6        | CS3-CS1                            | Current Sense Inputs                      | Non-inverting inputs to the current sense amplifiers.                                                                                                                                  |

| 7, 20      | NC                                 | No Connect                                | Pins not connected to IC.                                                                                                                                                              |

| 8          | CS <sub>REF</sub>                  | Current Sense Reference                   | Inverting input to the current sense amplifiers and reference for Power Good.                                                                                                          |

| 9          | V <sub>DRP</sub>                   | Current Sense Amp<br>Output               | Programs the voltage drop due to loading. A resistor from V <sub>DRP</sub> to FB programs the amount of Adaptive Voltage Positioning. Omitting this resistor defeats the AVP function. |

| 10         | V <sub>FB</sub>                    | Voltage Feedback                          | Error Amplifier inverting input. Input bias current is used to program AVP light load offset via a resistor connected to the converter output voltage.                                 |

| 11         | COMP                               | Error Amp Output and PWM Comparator Input | Provides loop compensation and is clamped by SS.                                                                                                                                       |

| 12         | SS                                 | Soft Start                                | Controls fault timing and startup.                                                                                                                                                     |

| 13         | PWRGD                              | Power Good Output                         | Open collector output, which is "low" when the converter output is out of regulation.                                                                                                  |

| 14         | PWRGDS                             | Power Good Sense                          | A resistor divider from V <sub>OUT</sub> to GND programs the Power Good lower threshold.                                                                                               |

| 15–19      | V <sub>ID4</sub> -V <sub>ID0</sub> | DAC V <sub>ID</sub> Inputs                | TTL–compatible logic input used to program the converter output voltage. Internal 50 k $\Omega$ pull–ups to 3.3 V via a blocking diode are provided. All high generates fault.         |

| 21-23      | GATE3-1                            | Channel Outputs                           | PWM outputs to drive FET driver IC.                                                                                                                                                    |

| 24         | V <sub>CC</sub>                    | Supply Input                              | IC bias input.                                                                                                                                                                         |

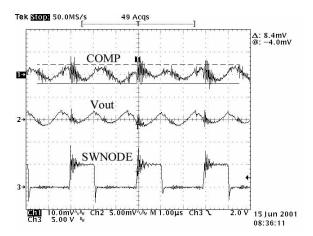

#### TYPICAL PERFORMANCE CHARACTERISTICS

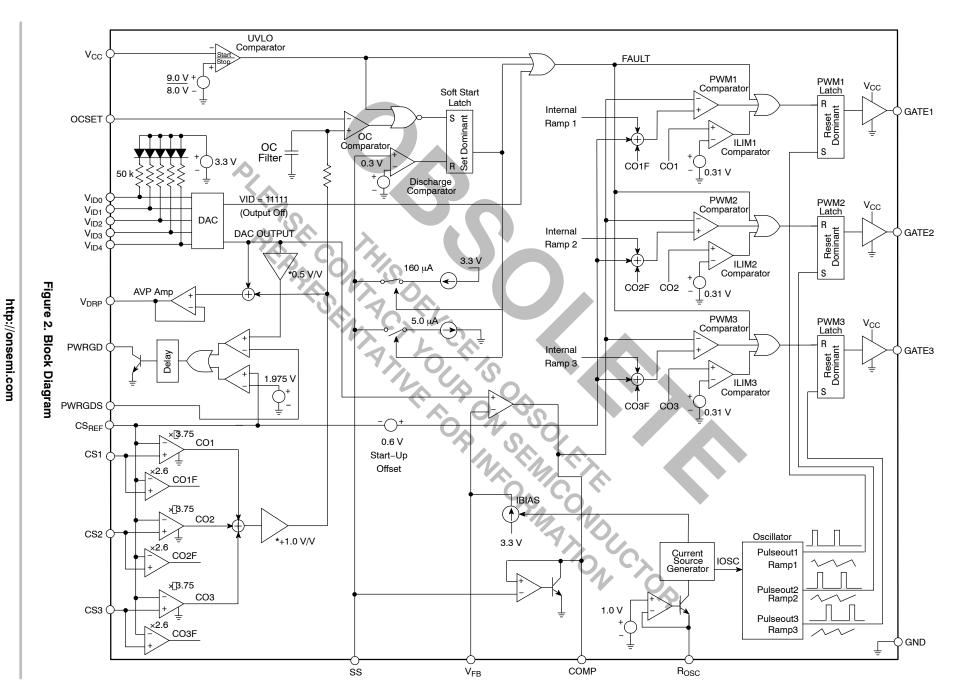

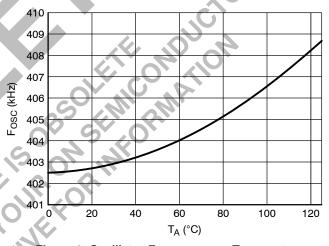

Figure 3. Oscillator Frequency

Figure 4. V<sub>FB</sub> Bias Current vs. R<sub>OSC</sub> Value

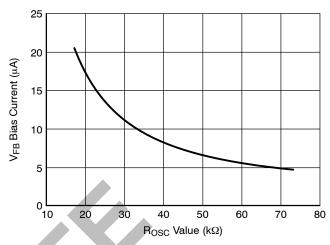

Figure 5. I<sub>CC</sub> vs. Temperature

Figure 6. Oscillator Frequency vs. Temperature  $(R_{OSC} = 32.4 \text{ k}\Omega)$

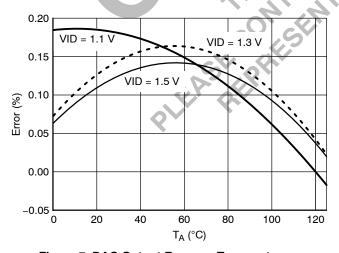

Figure 7. DAC Output Error vs. Temperature

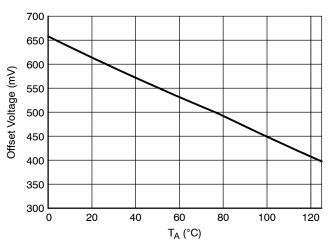

Figure 8. Current Sense Amplifier Channel Startup

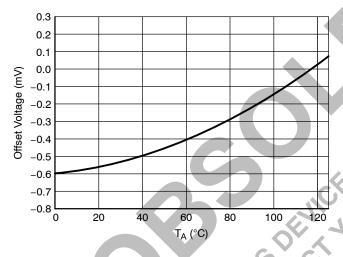

Offset Voltage vs. Temperature

## **TYPICAL PERFORMANCE CHARACTERISTICS**

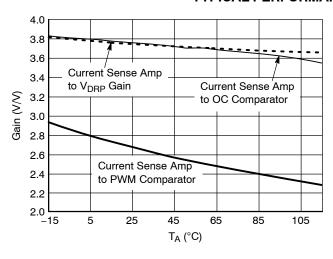

Figure 9. Sense Amp Gains vs. Temperature

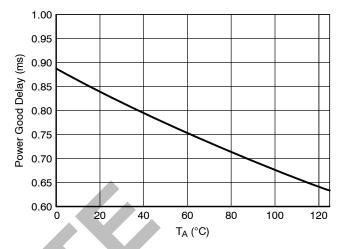

Figure 10. Power Good Delay vs. Temperature

Figure 11. V<sub>DRP</sub> to DAC Output Offset Voltage vs. Temperature

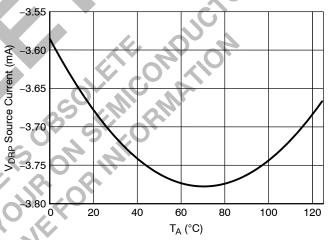

Figure 12. V<sub>DRP</sub> Source Current vs. Temperature

Figure 13.  $V_{FB}$  Bias Currents vs. Temperature ( $R_{OSC}$  = 32.4  $k\Omega$ )

#### **APPLICATIONS INFORMATION**

#### Overview

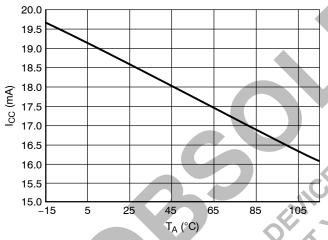

The NCP5306 DC/DC controller from ON Semiconductor was developed using the Enhanced V<sup>2</sup> topology. Enhanced V<sup>2</sup> combines the original V<sup>2</sup> topology with peak current-mode control for fast transient response and current sensing capability. The addition of an internal PWM ramp and implementation of fast-feedback directly from Vcore has improved transient response and simplified design. The NCP5306 includes Power Good (PWRGD), providing a highly integrated solution to simplify design, minimize circuit board area, and reduce overall system cost.

Two advantages of a multi-phase converter over a single-phase converter are current sharing and increased apparent output frequency. Current sharing allows the designer to use less inductance in each phase than would be required in a single-phase converter. The smaller inductor will produce larger ripple currents but the total per-phase power dissipation is reduced because the RMS current is lower. Transient response is improved because the control loop will measure and adjust the current faster in a smaller output inductor. Increased apparent output frequency is desirable because the off- time and the ripple voltage of the multi-phase converter will be less than that of a single-phase converter.

#### Fixed Frequency Multi-Phase Control

In a multi-phase converter, multiple converters are connected in parallel and are switched on at different times. This reduces output current from the individual converters and increases the apparent ripple frequency. Because several converters are connected in parallel, output current can ramp up or down faster than a single converter (with the same value output inductor) and heat is spread among multiple components.

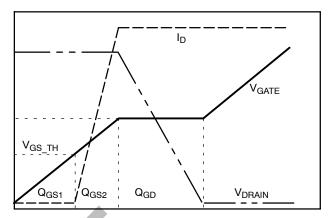

The NCP5306 controller uses three-phase, fixed-frequency, Enhanced V<sup>2</sup> architecture to measure and control currents in individual phases. Each phase is delayed 120° from the

previous phase. Normally, GATEx transitions to a high voltage at the beginning of each oscillator cycle. Inductor current ramps up until the combination of the current sense signal, the internal ramp and the output voltage ripple trip the PWM comparator and bring GATEx low. Once GATEx goes low, it will remain low until the beginning of the next oscillator cycle. While GATEx is high, the Enhanced V² loop will respond to line and load variations. On the other hand, once GATEx is low, the loop cannot respond until the beginning of the next PWM cycle. Therefore, constant frequency Enhanced V² will typically respond to disturbances within the off-time of the converter.

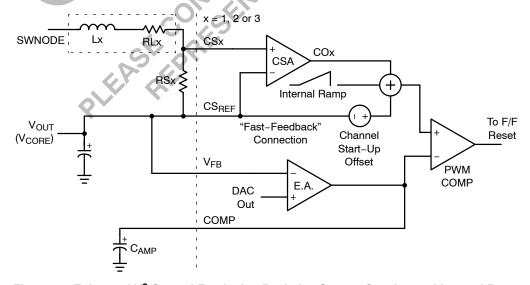

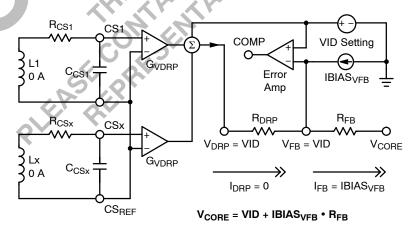

The Enhanced  $V^2$  architecture measures and adjusts the output current in each phase. An additional input (CSx) for inductor current information has been added to the V<sup>2</sup> loop for each phase as shown in Figure 14. The triangular inductor current is measured differentially across RS, amplified by CSA and summed with the channel startup offset, the internal ramp and the output voltage at the non-inverting input of the PWM comparator. The purpose of the internal ramp is to compensate for propagation delays in the NCP5306. This provides greater design flexibility by allowing smaller external ramps, lower minimum pulse widths, higher frequency operation and PWM duty cycles above 50% without external slope compensation. As the sum of the inductor current and the internal ramp increase, the voltage on the positive pin of the PWM comparator rises and terminates the PWM cycle. If the inductor starts a cycle with higher current, the PWM cycle will terminate earlier providing negative feedback. The NCP5306 provides a CSx input for each phase, but the CS<sub>REF</sub> and COMP inputs are common to all phases. Current sharing is accomplished by referencing all phases to the same CS<sub>REF</sub> and COMP pins, so that a phase with a larger current signal will turn off earlier than a phase with a smaller current signal.

Figure 14. Enhanced V<sup>2</sup> Control Employing Resistive Current Sensing and Internal Ramp

Enhanced  $V^2$  responds to disturbances in  $V_{CORE}$  by employing both "slow" and "fast" voltage regulation. The internal error amplifier performs the slow regulation. Depending on the gain and frequency compensation set by the amplifier's external components, the error amplifier will typically begin to ramp its output to react to changes in the output voltage in one or two PWM cycles. Fast voltage feedback is implemented by a direct connection from Vcore to the non–inverting pin of the PWM comparator via the summation with the inductor current, internal ramp and offset. A rapid increase in output current will produce a negative offset at Vcore and at the output of the summer. This will cause the PWM duty cycle to increase almost instantly. Fast feedback will typically adjust the PWM duty cycle in one PWM cycle.

As shown in Figure 14, an internal ramp (nominally 115 mV at a 50% duty cycle) is added to the inductor current ramp at the positive terminal of the PWM comparator. This additional ramp compensates for propagation time delays from the current sense amplifier (CSA), the PWM comparator and the MOSFET gate drivers. As a result, the minimum ON time of the controller is reduced and lower duty–cycles may be achieved at higher frequencies. Also, the additional ramp reduces the reliance on the inductor current ramp and allows greater flexibility when choosing the output inductor and the  $R_{\rm CSx}C_{\rm CSx}$  time constant of the feedback components from  $V_{\rm CORE}$  to the CSx pin.

Including both current and voltage information in the feedback signal allows the open loop output impedance of the power stage to be controlled. When the average output current is zero, the COMP pin will be:

Int\_Ramp is the "partial" internal ramp value at the corresponding duty cycle, Ext\_Ramp is the peak-to-peak external steady-state ramp at 0 A,  $G_{CSA}$  is the current sense amplifier gain (nominally 2.6 V/V) and the channel startup offset is typically 0.60 V. The magnitude of the Ext\_Ramp can be calculated from:

$$Ext_Ramp = D \cdot (VIN - VOUT)/(RCSx \cdot CCSx \cdot fSW)$$

For example, if  $V_{OUT}$  at 0 A is set to 1.700 V with AVP and the input voltage is 12.0 V, the duty cycle (D) will be 1.700/12.0 or 14.2%. Int\_Ramp will be 115 mV/50% [14.2% = 33 mV. Realistic values for  $R_{CSx}$ ,  $C_{CSx}$  and  $f_{SW}$  are 10 k $\Omega$ , 0.015  $\mu F$  and 650 kHz. Using these and the previously mentioned formula, Ext. Ramp will be 15.0 mV.

$$V_{COMP} = 1.700 \text{ V} + 0.60 \text{ V} + 33 \text{ mV} + 2.6 \text{ V/V} \cdot 15.0 \text{ mV/2} = 2.3 \text{ Vdc.}$$

If the COMP pin is held steady and the inductor current changes, there must also be a change in the output voltage.

Or, in a closed loop configuration when the output current changes, the COMP pin must move to keep the same output voltage. The required change in the output voltage or COMP pin depends on the scaling of the current feedback signal and is calculated as:

$$\Delta V = Rs \cdot GCSA \cdot \Delta IOUT$$

The single-phase power stage output impedance is:

Single Stage Impedance =

$$\Delta V_{OUT}/\Delta I_{OUT} = R_S \cdot G_{CSA}$$

The total output impedance will be the single stage impedance divided by 3.

The output impedance of the power stage determines how the converter will respond during the first few microseconds of a transient before the feedback loop has repositioned the COMP pin.

The peak output current can be calculated from:

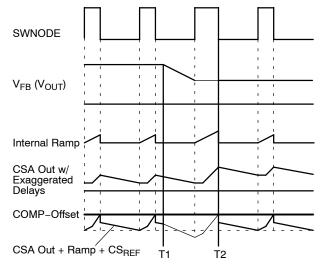

Figure 15 shows the step response of the COMP pin at a fixed level. Before T1, the converter is in normal steady-state operation. The inductor current provides a portion of the PWM ramp through the current sense amplifier. The PWM cycle ends when the sum of the current ramp, the "partial" internal ramp voltage signal and offset exceed the level of the COMP pin. At T1, the output current increases and the output voltage sags. The next PWM cycle begins and the cycle continues longer than previously while the current signal increases enough to make up for the lower voltage at the V<sub>FB</sub> pin and the cycle ends at T2. After T2, the output voltage remains lower than at light load and the average current signal level (CSx output) is raised so that the sum of the current and voltage signal is the same as with the original load. In a closed loop system, the COMP pin would move higher to restore the output voltage to the original level.

Figure 15. Open Loop Operation

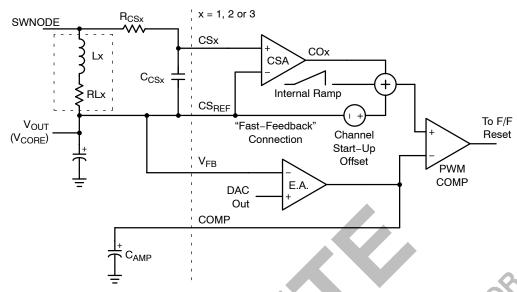

Figure 16. Enhanced V<sup>2</sup> Control Employing Lossless Inductive Current Sensing and Internal Ramp

#### **Inductive Current Sensing**

For lossless sensing, current can be sensed across the inductor as shown in Figure 16. In the diagram, L is the output inductance and  $R_L$  is the inherent inductor resistance. To compensate the current sense signal, the values of  $R_{CSx}$  and  $C_{CSx}$  are chosen so that  $L/R_L = R_{CSx} \ \Box C_{CSx}$ . If this criteria is met, the current sense signal will be the same shape as the inductor current and the voltage signal at CSx will represent the instantaneous value of inductor current. Also, the circuit can be analyzed as if a sense resistor of value  $R_L$  was used.

When choosing or designing inductors for use with inductive sensing, tolerances and temperature effects should be considered. Cores with a low permeability material or a large gap will usually have minimal inductance change with temperature and load. Copper magnet wire has a temperature coefficient of 0.39% per °C. The increase in winding resistance at higher temperatures should be considered when setting the OCSET threshold. If a more accurate current sense is required than inductive sensing can provide, current can be sensed through a resistor as shown in Figure 14.

#### **Current Sharing Accuracy**

Printed circuit board (PCB) traces that carry inductor current can be used as part of the current sense resistance depending on where the current sense signal is picked off. For accurate current sharing, the current sense inputs should sense the current at relatively the same point for each phase and the connection to the CS<sub>REF</sub> pin should be made so that no phase is favored. In some cases, especially with inductive sensing, resistance of the PCB can be useful for increasing the current sense resistance. The total current sense resistance used for calculations must include any PCB trace resistance between the CSx input and the CS<sub>REF</sub> input that carries inductor current.

Current Sense Amplifier (CSA) input mismatch and the value of the current sense component will determine the

accuracy of the current sharing between phases. The worst case CSA input mismatch is  $\pm 10$  mV and will typically be within 4.0 mV. The difference in peak currents between phases will be the CSA input mismatch divided by the current sense resistance. If all current sense components are of equal resistance, a 3.0 mV mismatch with a 2.0 m $\Omega$  sense resistance will produce a 1.5 A difference in current between phases.

#### **External Ramp Size and Current Sensing**

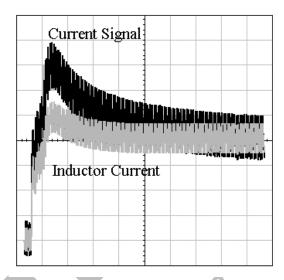

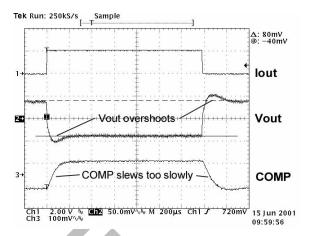

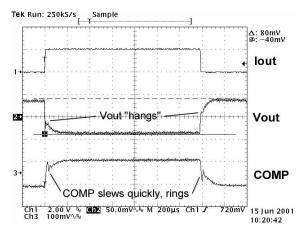

The internal ramp allows flexibility in setting the current sense time constant. Typically, the current sense R<sub>CSx</sub> [C<sub>CSx</sub> time constant should be equal to or slightly slower than the inductor's time constant. If RC is chosen to be smaller (faster) than L/R<sub>L</sub>, the AC or transient portion of the current sensing signal will be scaled larger than the DC portion. This will provide a larger steady-state ramp, but circuit performance will be affected and must be evaluated carefully. The current signal will overshoot during transients and settle at the rate determined by  $R_{CSx}$   $\Box C_{CSx}$ . It will eventually settle to the correct DC level, but the error will decay with the time constant of  $R_{CSx} \square C_{CSx}$ . If this error is excessive, it will affect transient response, adaptive positioning and current limit. During a positive current transient, the COMP pin will be required to undershoot in response to the current signal in order to maintain the output voltage. Similarly, the V<sub>DRP</sub> signal will overshoot which will produce too much transient droop in the output voltage. The single-phase pulse-by-pulse overcurrent protection will trip earlier than it would if compensated correctly and hiccup-mode current limit will have a lower threshold for fast rising step loads than for slowly rising output currents.

The waveforms in Figure 17 show a simulation of the current sense signal and the actual inductor current during a positive step in load current with values of L = 500 nH,  $R_L$  = 1.6 m $\Omega$ ,  $R_{CSx}$  = 20 k $\Omega$  and  $C_{CSx}$  = .01  $\mu F$ . In this case, ideal current signal compensation would require  $R_{CSx}$  to be 31 k $\Omega$ .

Due to the faster than ideal RC time constant, there is an overshoot of 50% and the overshoot decays with a  $200~\mu s$  time constant. With this compensation, the OCSET pin threshold must be set more than 50% above the full load current to avoid triggering current limit during a large output load step.

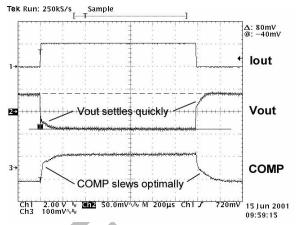

#### **Transient Response and Adaptive Voltage Positioning**

For applications with fast transient currents, the output filter is frequently sized larger than ripple currents require in order to reduce voltage excursions during load transients. Adaptive voltage positioning can reduce peak-peak output voltage deviations during load transients and allow for a smaller output filter. The output voltage can be set higher than nominal at light loads to reduce output voltage sag when the load current is applied. Similarly, the output voltage can be set lower than nominal during heavy loads to reduce overshoot when the load current is removed. For low current applications, a droop resistor can provide fast, accurate adaptive positioning. However, at high currents, the loss in a droop resistor becomes excessive. For example, a 50 A converter with a 1 m $\Omega$  resistor would provide a 50 mV change in output voltage between no load and full load and would dissipate 2.5 W.

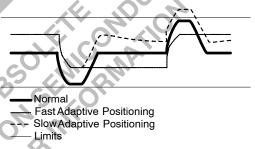

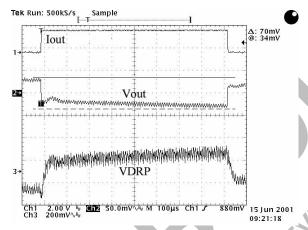

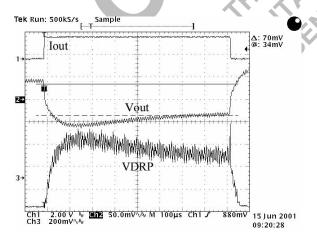

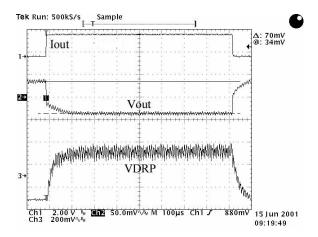

Lossless adaptive voltage positioning (AVP) is an alternative to using a droop resistor, but it must respond to changes in load current. Figure 18 shows how AVP works. The waveform labeled "normal" shows a converter without AVP. On the left, the output voltage sags when the output current is stepped up and later overshoots when current is stepped back down. With fast (ideal) AVP, the peak—to—peak excursions are cut in half. In the slow AVP waveform, the output voltage is not repositioned quickly enough after current is stepped up and the upper limit is exceeded.

The controller can be configured to adjust the output voltage based on the output current of the converter. (Refer to the application diagram in Figure 1). To set the no-load positioning, a resistor is placed between the output voltage and  $V_{FB}$  pin. The  $V_{FB}$  bias current will develop a voltage across the resistor to adjust the no-load output voltage. The  $V_{FB}$  bias current is dependent on the value of  $R_{OSC}$  as shown in the datasheets.

During no–load conditions, the  $V_{DRP}$  pin is at the same voltage as the  $V_{FB}$  pin, so none of the  $V_{FB}$  bias current flows through the  $V_{DRP}$  resistor. When output current increases, the  $V_{DRP}$  pin voltage increases proportionally. Current set by the  $V_{DRP}$  resistor offsets the  $V_{FB}$  bias current, causing the output voltage to decrease.

The response during the first few microseconds of a load transient is controlled primarily by power stage output impedance, and by the ESR and ESL of the output filter. The transition between fast and slow positioning is controlled by the total ramp size and the error amp compensation. If the ramp size is too large or the error amp too slow, there will be a long transition to the final voltage after a transient. This will be most apparent with low capacitance output filters.

Figure 17. Inductive Sensing Waveform During a Load Step with Fast RC Time Constant (50  $\mu s/div$ )

Figure 18. Adaptive Voltage Positioning

## Overvoltage Protection

Overvoltage protection (OVP) is provided as a result of the normal operation of the Enhanced  $V^2$  control topology with synchronous rectifiers. The control loop responds to an overvoltage condition within 40 ns, causing the GATEx output to shut off. The (external) MOSFET driver should react normally to turn off the top MOSFET and turn on the bottom MOSFET. This results in a "crowbar" action to clamp the output voltage and prevent damage to the load. The regulator will remain in this state until the overvoltage condition ends or the input voltage is pulled low.

#### **Power Good**

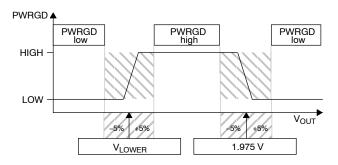

According to the latest specifications, the Power Good (PWRGD) signal must be asserted when the output voltage is within a window defined by the VID code, as shown in Figure 19.

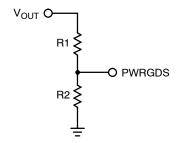

The PWRGDS pin is provided to allow the PWRGD comparators to accurately sense the output voltage. The effect of the PWRGD lower threshold can be modified using a resistor divider from the output to PWRGDS to ground, as shown in Figure 20.

Figure 19. PWRGD Assertion Window

Since the internally-set thresholds for PWRGDS are VID/2 for the lower threshold and a fixed 1.975V for the upper threshold, a simple equation can be provided to assist the designer in selecting a resistor divider to provide the desired PWRGD performance.

$$V_{LOWER} = \frac{V_{VID}}{2} \cdot \frac{R_1 + R_2}{R_1}$$

$$V_{UPPER} = 1.975 \text{ V}$$

The logic circuitry inside the chip sets PWRGD low only after a delay period has been passed. A "power bad" event does not cause PWRGD to go low unless it is sustained through the delay time of  $500~\mu s$ . If the anomaly disappears before the end of the delay, the PWRGD output will never be set low.

In order to use the PWRGD pin as specified, the user is advised to connect external resistors as necessary to limit the current into this pin to 4 mA or less.

#### **Undervoltage Lockout**

The NCP5306 includes an undervoltage lockout circuit. This circuit keeps the IC's output drivers low until  $V_{\rm CC}$  applied to the IC reaches 9 V. The GATE outputs are disabled when  $V_{\rm CC}$  drops below 8 V.

## Soft Start and Hiccup Mode

At initial power-up, both SS and COMP voltages are zero. The total SS capacitance will begin to charge with a current of 160  $\mu A$ . The error amplifier directly charges the COMP capacitance. An internal clamp ensures that the COMP pin voltage will always be less than the voltage at the SS pin, ensuring proper start-up behavior. All GATE outputs are held low until the COMP voltage reaches 0.6 V. Once this threshold is reached, the GATE outputs are released to operate normally. In current limit, the internal fault latch will initiate a 5  $\mu A$  discharge current on the SS pin, and the internal clamp will discharge the capacitor connected to the COMP pin at a similar rate. This performance will result in GATE pulses being generated until the overcurrent condition reoccurs and the discharge/soft start cycle begins anew.

Figure 20. Adjusting the PWRGD Threshold

#### Current Limit

Two levels of over-current protection are provided. First, if the voltage on the Current Sense pins (CSx) exceeds CS<sub>REF</sub> by more than a fixed threshold (Single Pulse Current Limit), the PWM comparator is turned off. This provides fast peak current protection for individual phases. Second, the individual phase currents are summed and low-pass filtered to compare an averaged current signal to a user adjustable voltage on the OCSET pin. If the OCSET voltage is exceeded, the fault latch trips and the Soft Start capacitor discharges until the Soft Start pin reaches 0.3 V. Then Soft Start begins. The converter will continue to operate in a low average current hiccup-mode until the fault condition is corrected.

## **Fault Protection Logic**

The NCP5306 includes fault protection circuitry to prevent harmful modes of operation from occurring. The fault logic is described in Table 1.

#### **Gate Outputs**

The NCP5306 is designed to operate with external gate drivers. Accordingly, the gate outputs are capable of driving a 100 pF load with typical rise and fall times of 5 ns.

#### Digital to Analog Converter (DAC)

The output voltage of the NCP5306 is set by means of a 5-bit, 1% DAC. The DAC pins are internally pulled up to a 3.3 V rail through a blocking diode and a set of 50 k $\Omega$  resistors. The blocking diode allows external pull up to a bias voltage greater than 3.3 V and less than 13 V.

The output of the DAC is described in the Electrical Characteristics section of the data sheet. These outputs are consistent with the latest VRM and processor specifications. The DAC output is equal to the VID code specification.

In order to produce a workable power supply using the NCP5306, the designer is expected to use AVP as described earlier to position the output voltage below the DAC output, resulting in an output voltage somewhere in the middle of the acceptable range.

**Table 1. Fault Protection Logic**

| Fault Modes                          | Stop Switching | SS Pin Characteristics | Reset Method    |  |

|--------------------------------------|----------------|------------------------|-----------------|--|

| Undervoltage Lockout                 | Yes            | -5.0 μΑ                | SS < 0.3 V      |  |

| VID-11111                            | Yes            | -5.0 μΑ                | Change VID Code |  |

| Phase Over Current<br>(0.31 V Limit) | No             | Not Affected           | Automatic       |  |

The latest VRM and processor specifications require a power supply to turn its output off in the event of a 11111 VID code. When the DAC sees such a code, the GATE pins stop switching and go low. This condition is described in Table 1.

#### **Design Procedure**

#### 1. Output Capacitor Selection

The output capacitors filter the current from the output inductor and provide a low impedance for transient load current changes. Typically, microprocessor applications require both bulk (electrolytic, tantalum) and low impedance, high frequency (ceramic) types of capacitors. The bulk capacitors provide "hold up" during transient loading. The low impedance capacitors reduce steady–state ripple and bypass the bulk capacitance when the output current changes very quickly. The microprocessor manufacturers usually specify a minimum number of ceramic capacitors. The designer must determine the number of bulk capacitors.

Choose the number of bulk output capacitors to meet the peak transient requirements. The formula below can be used to provide a starting point for the minimum number of bulk capacitors (N<sub>OUT,MIN</sub>):

Nout, MIN = ESR per capacitor

$$\cdot \frac{\Delta IO, MAX}{\Delta VO, MAX}$$

(1)

In reality, both the ESR and ESL of the bulk capacitors determine the voltage change during a load transient according to:

$$\Delta V_{O,MAX} = (\Delta I_{O,MAX}/\Delta t) \cdot ESL + \Delta I_{O,MAX} \cdot ESR$$

(2)

Unfortunately, capacitor manufacturers do not specify the ESL of their components and the inductance added by the PCB traces is highly dependent on the layout and routing. Therefore, it is necessary to start a design with slightly more than the minimum number of bulk capacitors and perform transient testing or careful modeling/simulation to determine the final number of bulk capacitors.

## 2. Output Inductor Selection

The output inductor may be the most critical component in the converter because it will directly effect the choice of other components and dictate both the steady-state and transient performance of the converter. When selecting an inductor, the designer must consider factors such as DC current, peak current, output voltage ripple, core material,

magnetic saturation, temperature, physical size and cost (usually the primary concern).

In general, the output inductance value should be electrically and physically as small as possible to provide the best transient response at minimum cost. If a large inductance value is used, the converter will not respond quickly to rapid changes in the load current. On the other hand, too low an inductance value will result in very large ripple currents in the power components (MOSFETs, capacitors, etc.) resulting in increased dissipation and lower converter efficiency. Increased ripple currents force the designer to use higher rated MOSFETs, oversize the thermal solution, and use more, higher rated input and output capacitors, adversely affecting converter cost.

One method of calculating an output inductor value is to size the inductor to produce a specified maximum ripple current in the inductor. Lower ripple currents will result in less core and MOSFET losses and higher converter efficiency. Equation 3 may be used to calculate the minimum inductor value to produce a given maximum ripple current ( $\alpha$ ) per phase. The inductor value calculated by this equation is a minimum because values less than this will produce more ripple current than desired. Conversely, higher inductor values will result in less than the selected maximum ripple current.

$$Lo_{MIN} = \frac{(V_{IN} - V_{OUT}) \cdot D}{(\alpha \cdot I_{O.MAX} \cdot f_{SW})}$$

(3)

$\alpha$  is the ripple current as a percentage of the maximum output current *per phase* ( $\alpha$  = 0.15 for ±15%,  $\alpha$  = 0.25 for ±25%, etc.). If the minimum inductor value is used, the inductor current will swing ±  $\alpha$ % about its value at the center. Therefore, for a three–phase converter, the inductor must be designed or selected such that it will not saturate with a peak current of  $(1 + \alpha) \cdot I_{O,MAX}/3$ .

The maximum inductor value is limited by the transient response of the converter. If the converter is to have a fast transient response, the inductor should be made as small as possible. If the inductor is too large its current will change too slowly, the output voltage will droop excessively, more bulk capacitors will be required and the converter cost will be increased. For a given inductor value, it is useful to determine the times required to increase or decrease the current.

For increasing current:

$$\Delta t_{INC} = Lo \cdot \Delta I_{O}/(V_{IN} - V_{OUT})$$

(3.1)

For decreasing current:

$$\Delta t_{DEC} = Lo \cdot \Delta I_{O}/(V_{OUT})$$

(3.2)

For typical processor applications with output voltages less than half the input voltage, the current will be increased much more quickly than it can be decreased. Thus, it may be more difficult for the converter to stay within the regulation limits when the load is removed than when it is applied and excessive overshoot may result.

The output voltage ripple can be calculated using the output inductor value derived in this Section ( $Lo_{MIN}$ ), the number of output capacitors ( $N_{OUT,MIN}$ ) and the per capacitor ESR determined in the previous Section:

$$VOUT,P-P = (ESR per cap / NOUT,MIN) \cdot (4)$$

$$\{(VIN - #Phases \cdot VOUT) \cdot D / (LOMIN \cdot fSW)\}$$

This formula assumes steady-state conditions with no more than one phase on at any time. The second term in Equation 4 is the total ripple current seen by the output capacitors. The total output ripple current is the "time summation" of the three individual phase currents that are 120 degrees out-of-phase. As the inductor current in one phase ramps upward, current in the other phase ramps downward and provides a canceling of currents during part of the switching cycle. Therefore, the total output ripple current and voltage are reduced in a multi-phase converter.

#### 3. Input Capacitor Selection

The choice and number of input capacitors is primarily determined by their voltage and ripple current ratings. The designer must choose capacitors that will support the worst case input voltage with adequate margin. To calculate the number of input capacitors, one must first determine the total RMS input ripple current. To this end, begin by calculating the average input current to the converter:

$$I_{IN,AVG} = I_{O,MAX} \cdot D/\eta$$

(5)

where:

D is the duty cycle of the converter, D =  $V_{OUT}/V_{IN}$ ;  $\eta$  is the specified minimum efficiency;

I<sub>O,MAX</sub> is the maximum converter output current.

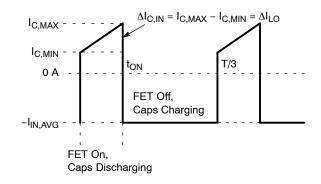

The input capacitors will discharge when the control FET is ON and charge when the control FET is OFF as shown in Figure 21.

The following equations will determine the maximum and minimum currents delivered by the input capacitors:

$$I_{C,MAX} = I_{Lo,MAX}/\eta - I_{IN,AVG}$$

(6)

$$I_{C,MIN} = I_{Lo,MIN}/\eta - I_{IN,AVG}$$

(7)

I<sub>Lo,MAX</sub> is the maximum output inductor current:

$$I_{LO,MAX} = I_{O,MAX}/3 + \Delta I_{LO}/2$$

(8)

I<sub>I.O.MIN</sub> is the minimum output inductor current:

$$I_{LO,MIN} = I_{O,MAX}/3 - \Delta I_{LO}/2$$

(9)

$\Delta I_{Lo}$  is the peak-to-peak ripple current in the output inductor of value Lo:

$$\Delta I_{LO} = (V_{IN} - V_{OUT}) \cdot D/(Lo \cdot f_{SW})$$

(10)

For the three-phase converter, the input capacitor(s) RMS current is then: