# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Nuvoton DDR Termination Regulator NCT3107S

### DATE: NOVEMBER, 2011

**Revision: A2**

### -Table of Content-

| 1.GENERATION DESCRIPTION                            | 1  |

|-----------------------------------------------------|----|

| 2.FEATURES                                          | 1  |

| 3.BLOCK DIAGRAM                                     | 2  |

| 4.PIN CONFIGURATION AND TYPICAL APPLICATION CIRCUIT | 2  |

| 5.PIN DESCRIPTION                                   | 3  |

| 6.FUNCTIONAL DESCRIPTION                            | 3  |

| 7.ELECTRICAL CHARACTERISTIC                         | 9  |

| 8.TYPICAL OPERATING CHARACTERISTICS AND WAFEFORMS   | 11 |

| 9.PACKAGE DIMENSION                                 | 16 |

| 10.ORDERING INFORMATION                             | 17 |

| 11.TOP MARKING SPECIFICATION                        | 17 |

| 12.REVISION HISTORY                                 | 18 |

### **1. GENERATION DESCRIPTION**

The NCT3107S is a sink/source linear regulator for DDR-SDRAM VTT bus termination. The device contains a high speed operational amplifier to provide excellent response to load transients and only requires a minimum output capacitance of 10uF. The NCT3107S also incorporates a remote sensing function (VSEN pin) to provide superior load regulation and a VREF output as a reference for the chipset and DIMMS. An additional feature found on the NCT3107S is an active low shutdown (SD# pin) that provides Suspend to RAM (STR) functionality. When SD# is pilled low, the VTT output voltage will be discharged to ground but VREF remains active. A power savings advantage can be obtained in this mode through lower quiescent current. NCT3107S is available in ESOP-8 package. It is specified from -40°C to 85°C.

### 2. FEATURES

#### General

- Sink and Source Current

- Low Output Voltage Offset

- No External Resistors Required

- Linear Topology

- Suspend to RAM (STR) Functionality

- Low External Component Count

- Required Minimum Output Capacitance of 10uF for Memory Termination Applications (DDR)

- Built-in Over Current Protection

#### Applications

- Memory Termination Regulator for DDR2 and DDR3

- Motherboards

- LCD TV/PDP TV, Copier/Printer, Set Top Box

- Thermal Shutdown

- Remote Sensing (VSEN)

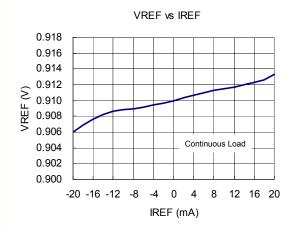

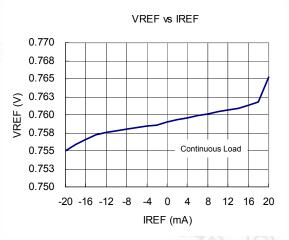

- ± 10mA Buffered Reference Output (VREF)

- Meets DDR2 Specifications; Support DDR3 VTT Applications

- ESOP-8 150mil with Exposed Pad Package

- Green Package (Lead Free and Halogen Free)

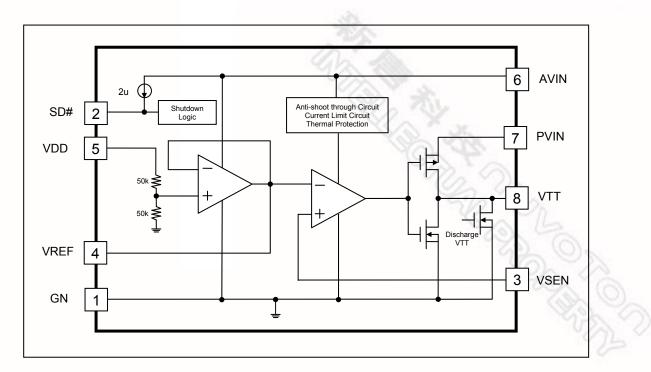

### 3. BLOCK DIAGRAM

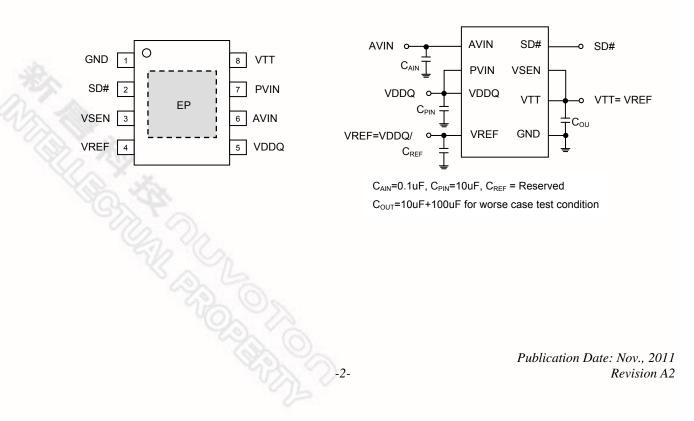

### 4. PIN CONFIGURATION AND TYPICAL APPLICATION CIRCUIT

### 5. PIN DESCRIPTION

| PIN NAME | NO | PIN TYPE | DESCRIPTION                                             |

|----------|----|----------|---------------------------------------------------------|

| GND      | 1  | Ground   | Ground                                                  |

| SD#      | 2  | I        | Shutdown VTT output voltage.                            |

| VSEN     | 3  | AI       | Feedback pin for regulating VTT.                        |

| VREF     | 4  | AO       | Buffered internal reference voltage of ½VDDQ.           |

| VDDQ     | 5  | AI       | Input for internal reference equal to ½VDDQ.            |

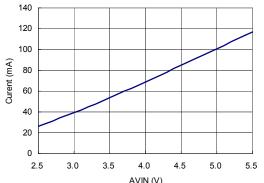

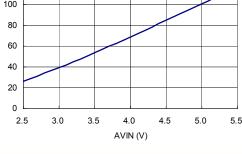

| AVIN     | 6  | Power    | Analog input pin for power source.                      |

| PVIN     | 7  | AI       | Analog input pin for internal power MOSFET source.      |

| VTT      | 8  | AO       | Output voltage for connection to termination resistors. |

| EP       |    |          | Exposed pad thermal connection. Connect to ground.      |

| PIN TYPE | PIN Attribute               |  |

|----------|-----------------------------|--|

| AO       | Output pin (Analog)         |  |

| AI       | Input pin (Analog)          |  |

| I        | Input pin (Digital)         |  |

| POWER    | Positive power supply input |  |

| GROUND   | GROUND Power supply ground  |  |

### 6. FUNCTIONAL DESCRIPTION

#### **General Description**

The NCT3107S is a sink/source linear regulator for DDR-SDRAM VTT bus termination. The device contains a high speed operational amplifier to provide excellent response to load transients and only requires a minimum output capacitance of 10uF. The NCT3107S also incorporates a remote sensing function (VSEN pin) to provide superior load regulation and a VREF output as a reference for the chipset and DIMMS. An additional feature found on the NCT3107S is an active low shutdown (SD# pin) that provides Suspend to RAM (STR) functionality. When SD# is pilled low, the VTT output voltage will be discharged to ground but, VREF remains active. A power savings advantage can be obtained in this mode through lower quiescent current.

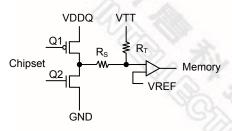

Series Stub Termination Logic (SSTL) was created to improve signal integrity of the data transmission across the memory bus. This termination scheme is essential to prevent data error from signal reflections while transmitting at high frequencies encountered with DDR-SDRAM. The DDR-SDRAM memory termination structure determines the main characteristics of the VT rail, which is to be able to sink and source current while maintaining acceptable VTT tolerance. Fig. 6-1 shows typical characteristics for a single memory cell.

When Q1 is on and Q2 is off:

- Current flows from VDDQ via the termination resistor to VTT

- VTT sinks current

When Q1 is off and Q2 is on:

- Current flows from VTT via the termination resistor to GND

- VTT sources current

Fig. 6-1 DDR Physical Signal System Bi-Directional SSTL Signaling

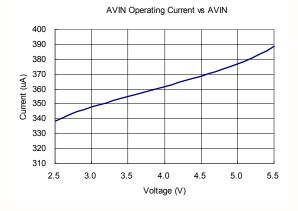

#### **AVIN and PVIN**

AVIN and PVIN are the input supply voltage pins for NCT3107S. AVIN is used to supply the internal control circuitry and PVIN is used to provide the rail voltage for the output staged used to create VTT. AVIN has to be greater than or equal to PVIN in any applications. This prevents the thermal limit from tripping because of excessive internal power dissipation. If the junction temperature exceeds the thermal shutdown threshold, the part will enter a shutdown state identical to the manual shutdown where VTT is tri-stated and VREF remains active. A lower rail can be used but it will reduce the maximum output current.

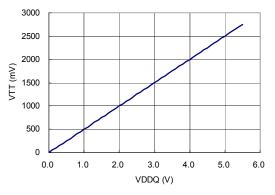

#### VDDQ

VDDQ is the input used to create the internal reference voltage for regulating VTT. The reference voltage is generated from a resistor divider of two internal 50k $\Omega$  resistors. This guarantees that VTT will precisely track VREF. The optimal implementation of VDDQ is as a remote sense. This can be achieved by connecting VDDQ directly to the power rail at the DIMM instead of PVIN. This ensures that the reference voltage precisely tracks the DDR memory rails without a large voltage drop from the power lines.

#### VREF

VREF provides the buffered output of the internal reference voltage ½VDDQ. This output should be used to provide the reference voltage for chipset and memory. Typically, there is no necessary to place output capacitor. But for worse condition, an output bypass capacitor could be reserved, close to the pin, to secure a suitable phase margin. Insufficient capacitance may cause an oscillation. A ceramic capacitor in the range 0.01uF to 0.1uF is recommended. The output remains active during the shutdown state and thermal shutdown events for the Suspend to RAM functionality.

#### VTT

VTT is the regulated output that is used to terminate the bus resistors. It is capable of sinking and sourcing current while regulating the output precisely to VREF. If a transient is expected to last above the maximum continuous current rating for a significant amount of time, then the bulk output capacitor should be sized large enough to prevent an excessive voltage drop. If the NCT3107S is to operate in elevated temperatures for long durations, care should be taken to ensure the maximum operating junction temperature is not exceeded. Proper thermal de-rating

### nuvoton

should always be used. If the junction temperature exceeds the thermal shutdown threshold, VTT will tri-state until the part returns below the temperature hysteresis trip-point.

#### VSEN

The purpose of the sense pin is to provide improved remote load regulation. In most motherboard applications, the termination resistors will connect to VTT in a long plane. If the output voltage was regulated only at the output of the NCT3107S, then the long trace will cause a significant DC voltage drop resulting in a termination voltage lower at one end of the bus than the other. The VSEN pin can be used to improve this performance by connecting it to the middle of the bus. This will provide a better distribution across the entire termination bus. If remote load regulation is not used, then the VSEN pin must be connected to VTT. Care should be taken when a long VSEN trace is implemented in close proximity to the memory. Noise pick up in the VSEN trace can cause problems with precise regulation of VTT. A small 0.1uF ceramic capacitor placed next to the VSEN pin can help filter any high frequency signals and prevent errors.

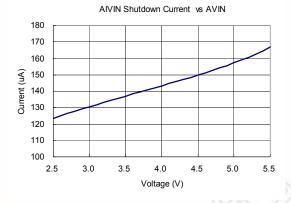

#### Shutdown

The NCT3107S contains an active low shutdown pin that can be used for Suspend to RAM functionality. In the condition, the VTT output voltage will be discharged to ground while the VREF output remains active and provides a constant reference signal for the memory and chipset. During shutdown, VTT should not be exposed to voltages that exceed PVIN. With the shutdown pin asserted low, the quiescent current of the NCT3107S will drop. However, VDDQ always maintain its constant impedance of 100k $\Omega$  for generating the internal reference. Therefore, to calculate the total power loss in shutdown, both currents need to be considered. The shutdown pin also has an internal pull up current. Therefore, to turn the part on, the shutdown pin can either be connected to AVIN or left open.

#### **Current Limit Protection**

The NCT3107S provides a current limit circuitry for short circuit protection, which monitors the output current and controls internal power MOSFET gate voltage to limit the output current. This reduction is a non latch protection.

#### **Thermal Shutdown**

The NCT3107S has a thermal shutdown circuitry to limit the junction temperature. When the junction temperature exceeds 150°C, the thermal shutdown circuitry let the output into tri-state, allowing the device to cool down. The output circuitry is enabled again after the junction temperature cools down by 30°C, resulting in a pulsed output during continuous thermal overload conditions. The thermal protection is designed to protect the IC in the event of over temperature conditions. For reliabile operation, the junction temperature cannot exceed 125°C.

#### **Input Decoupling**

To achieve the best results when using the NCT3107S, decouple the power supply for AVIN with a 0.1uF to 4.7uF capacitor. For PVIN pin, use a 10uF (or greater) capacitor to improve performance during large load transients to prevent the input rail from dropping. Provide more input capacitance as more output capacitance is used at VTT. In general, use one-half of the COUT value for input. Use a high quality ceramic surface mount capacitor if possible. Surface mount components minimize lead inductance, which improves performance, and ceramic capacitors tend to have adequate high frequency response for decoupling applications.

## nuvoton

#### **Output Stability**

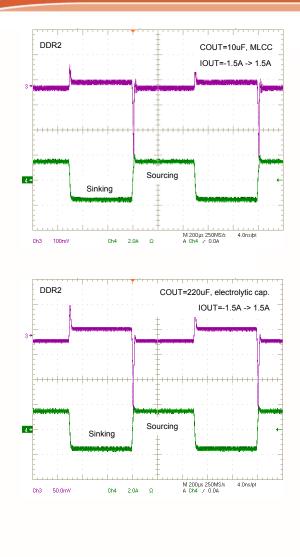

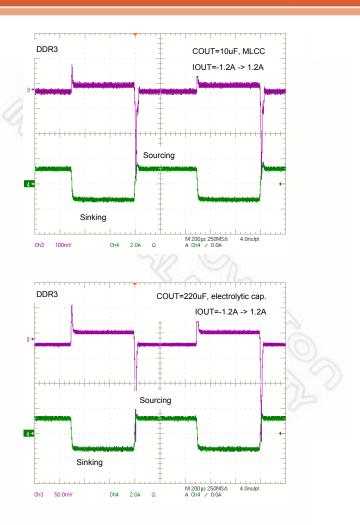

To maintain circuit stability and improve transient response over temperature and current, the NCT3107S needs a suitable output capacitor. In order to insure the circuit stability, the suitable output capacitor should be larger than 10uF. For worse case test condition (from maximum sinking current to maximum sourcing current), the capacitance has to be large than 100uF. The choice for output capacitor will be determined solely on the application and the requirements for load transient response of VTT. The value of ESR should be determined by the maximum current spikes expected and the extent at which the output voltage is allowed to droop.

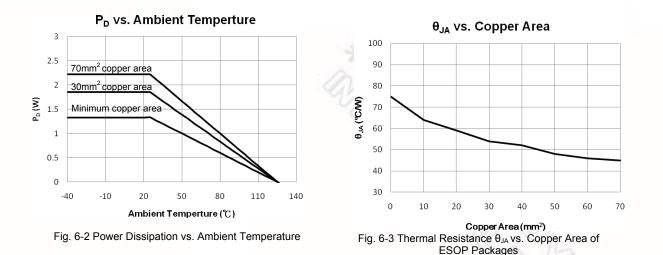

#### **Thermal Design**

Because the NCT3107S is a linear regulator, the VTT current flows in both source and sink directions, thereby dissipating power from the device. When the device is sourcing current, the voltage difference between PVIN and VTT times IOUT current becomes the power dissipation as shown in below equation.

$$P_{DISS\_SRC} = (PVIN - VTT) \times IOUT_{SRC}$$

In this case, if PVIN is connected to an alternative power supply lower than the VDDQ voltage, overall power loss can be reduced. For the sink phase, VTT voltage is applied across the internal LDO regulator, and the power dissipation, PDISS SNK can be calculated by below equation.

Since the device does not sink and source at the same time and IOUT varies rapidly with time, actual power dissipation need to be considered for thermal design is an average of above value over thermal relaxation duration of the system. Another source of power consumption is the current used for internal control circuitry from AVIN supply and PVIN supply. This can be estimated as 5mW or less during normal operating conditions. This power must be effectively dissipated from the package.

Maximum power dissipation allowed by the package is calculated by below equation.

$$\mathsf{P}_{\mathsf{PKG}} = [\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}(\mathsf{MAX})}] / \theta_{\mathsf{JA}}$$

where

- T<sub>J (MAX)</sub> is +125°C

- T<sub>A (MAX)</sub> Is the maximum ambient temperature in the system

- θ<sub>IA</sub> Is the thermal resistance from junction to ambient

$\theta_{IA}$  highly depends on IC package, PCB layout, the aireflow. Thermal resistance  $\theta_{IA}$  can be improved by adding copper under the exposed pad of ESOP-8 while the IC package is fixed. The copper under the exposed pad of ESOP-8 is an effective heatsink and is useful for improving thermal conductivity. Figure show the relationship between thermal resistance  $\theta_{IA}$  vs. copper area on a standard JEDEC 51-7 (4 layers, 2S2P) thermal test board at TA = 25°C, PCB copper thickness = 2oz. The 70mm<sup>2</sup> copper plane reduce  $\theta_{JA}$  from 75°C/W to 45°C/W and ś ma. increases maximum power disspation from 1.33W to 2.22W.

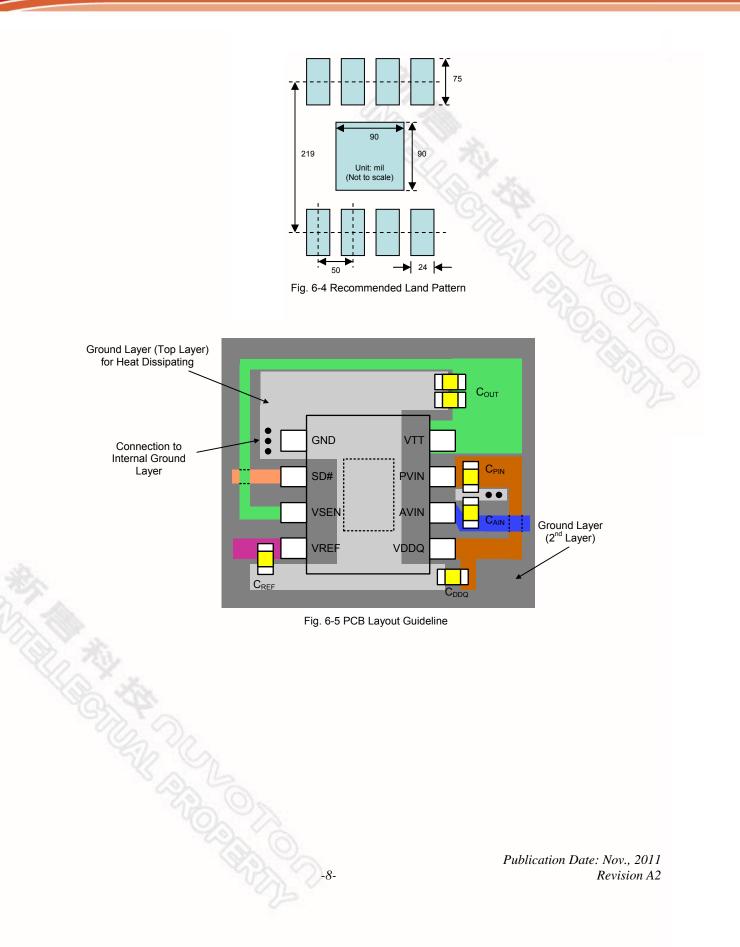

#### Layout Consideration

Consider the following points before starting the NCT3107S layout design.

- The input bypass capacitors for AVIN, PVIN and VSEN should be placed as close as possible to the pin with short and wide connections.

- The output capacitors for VTT and VREF should be placed close to the pin with short and wide connection in order to avoid ESR and/or ESL trace inductance.

- VSEN should be connected to the positive node of VTT output capacitor(s) as a separate trace from the high current power line. The configuration is strongly recommended to avoid additional ESR and/or ESL. If sensing the voltage at the point of the load is required, it is recommended to attach the output capacitor(s) at that point. Also, it is recommended to minimized any additional ESR and/or ESL of ground trace between the GND pin and the output capacitor(s).

- VDDQ can be connected separately from PVIN. Remember that this sensing potential is the reference voltage of VREF. Avoid any noise generative lines.

- The negative nose of the VTT output capacitor(s) and the VREF capacitor should be tied together by avoiding common impedance to the high current path of the VTT source/sink current. Also, place bulk caps close to the DIMM load point, route the VSEN to the DIMM load sense point.

- In order to effectively remove heat from the package, properly prepare the thermal land. Apply solder directly to the package's thermal pad. The wide traces of component and the side copper connected to the thermal land pad help to dissipate heat. The thermal land connected to the ground plane could also be used to help dissipation. Numerous vias connected from the thermal land to the internal/solder side ground plane(s) should also be used to help dissipation.

### 7. ELECTRICAL CHARACTERISTIC

#### **Absolute Maximum Ratings**

| PAF            | RAMETER          | RATING                                     |    |

|----------------|------------------|--------------------------------------------|----|

| Power Pins A   | AVIN, PVIN, VDDQ | -0.3 to 6V                                 | V  |

| Voltage        | on Other Pins    | -0.3 to 6V                                 | V  |

| Junctior       | Temperature      | 150                                        | °C |

| Storage        | Temperature      | -50 to 150                                 | °C |

| Solderin       | g Temperature    | Refer to IPC/JEDEC J-STD-020 Specification |    |

|                | Human Body Mode  | 2 50                                       | kV |

| ESD Protection | Machine Mode     | 200                                        | V  |

|                | Latch-up         | 100                                        | mA |

Note1. No pin should exceed AVIN.

Note2. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

Note3. Devices are ESD sensitive. Handling precaution recommended.

#### **Thermal Information**

| ITEM                                                    | RATING | UNIT |

|---------------------------------------------------------|--------|------|

| Power Dissipation, $P_D \textcircled{O} T_A=25^\circ C$ | 1.33   | W    |

| Package Thermal Resistance, ESOP8, $\theta_{JA}$        | 75     | °C/W |

Note1. At elevated temperatures, devices must be de-rated based on thermal resistance. The device in the ESOP-8 package must be de-rated at  $\theta_{JA}$ =75 °C/W junction to ambient with minimum PCB footprint.

### **Recommended Operating Conditions**

| PARAMETER                                | RATING      | UNIT                     |

|------------------------------------------|-------------|--------------------------|

| Operating Temperature                    | -40 to 85   | °C                       |

| Junction Temperature                     | -40 to 125  | °C                       |

| Supply Voltage, AVIN                     | 2.2 to 5.5  | V                        |

| Capacitance of AVIN Decoupling Capacitor | 0.1 to 4.7  | uF                       |

| Capacitance of PVIN Decoupling Capacitor | 10 to 270   | uF                       |

| Capacitance of VDDQ Decoupling Capacitor | 0.1 to 270  | uF                       |

| Capacitance of VREF Regulation Capacitor | 0.01 to 0.1 | uF                       |

| Capacitance of VTT Regulation Capacitor  | 10 to 470   | uF                       |

|                                          | Publication | Date: Nov., 2<br>Revisio |

#### **Electrical Characteristics**

AVIN=2.5V, PVIN=VDDQ=1.8V, COUT=10uF and all outputs are unload (unless otherwise noted). Typical value are at Ta=25°C and limits apply over the full operating temperature, Ta= -40~85°C.

| PARAMETER                                   | SYM.              | MIN.      | TYP.     | MAX.      | UNIT | CONDITIONS                             |

|---------------------------------------------|-------------------|-----------|----------|-----------|------|----------------------------------------|

| Reference Voltage                           |                   | •         | No.      | No.       |      |                                        |

| VREF                                        |                   | 0.49×VDDQ | 0.5×VDDQ | 0.51×VDDQ | V    | I <sub>REF</sub> =0mA                  |

| Source Current                              | I <sub>REF+</sub> | 10        |          | Lay       | mA   |                                        |

| Sink Current                                | I <sub>REF-</sub> |           |          | -10       | mA   | ~                                      |

| VREF Voltage Tolerance                      |                   | -15       |          | +15       | mV   | I <sub>REF</sub> =± 10mA               |

| VDDQ Input Impedance                        |                   |           | 100      |           | kΩ   | N CA                                   |

| Input / Output Current                      |                   |           |          |           | - 33 | ~h                                     |

| Quiescent Current <sup>(1)</sup>            | lα                |           | 320      | 500       | uA   | I <sub>OUT</sub> =0A                   |

| Shutdown Quiescent Current <sup>(1)</sup>   | I <sub>SD</sub>   |           | 115      | 150       | uA   | SD#=0V                                 |

| Shutdown Leakage Current                    | I <sub>Q_SD</sub> |           | 2        | 5         | uA   | SD#=0V                                 |

| VSEN Input Current                          | I <sub>VSEN</sub> | -1        |          | 1         | uA   | - 7.9                                  |

| VTT Discharge Current in Shutdown           | $I_{VTT_Dis}$     |           | 20       |           | mA   | SD#=0V, VTT=0.4V                       |

| Output Voltage Offset (VREF-VTT)            |                   |           |          |           |      |                                        |

| DDR2, PVIN=VDDQ=1.8V                        |                   | -20       |          | 20        | mV   | I <sub>OUT</sub> =0A                   |

| DDR3, PVIN=VDDQ=1.5V                        | Vos               | -20       |          | 20        | mV   | I <sub>OUT</sub> =0A                   |

| DDR2, PVIN=VDDQ=1.8V                        | VOS               | -30       |          | 30        | mV   | I <sub>OUT</sub> =±1.5A <sup>(2)</sup> |

| DDR3, PVIN=VDDQ=1.5V                        |                   | -30       |          | 30        | mV   | I <sub>OUT</sub> =±1.2A <sup>(2)</sup> |

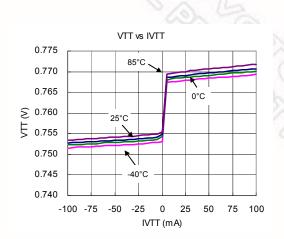

| Logic Input Level                           |                   |           |          | _         |      |                                        |

| Minimum Shutdown High Level                 | V <sub>IH</sub>   | 1.9       |          |           | V    | AVIN=2.2V~5.5V                         |

| Maximum Shutdwon Low Level                  | VIL               |           |          | 0.8       | V    | AVIN-2.20-5.50                         |

| Current Limit Protection                    |                   |           |          |           |      |                                        |

| Output Current Limit                        | ILIM              | 2.5       |          |           | А    | PVIN=VDDQ=1.8V                         |

|                                             | LIM               | 1.5       |          |           | А    | PVIN=VDDQ=1.5V                         |

| Over Temperature Protection                 |                   |           |          |           |      |                                        |

| Thermal Shutdown Temperature <sup>(3)</sup> |                   | 145       | 150      | 160       | °C   |                                        |

| Thermal Shutdown Hysteresis                 |                   | 20        | 30       | 40        | °C   |                                        |

Note1. Quiescent is defined as the current flow into AVIN.

Note2. VTT load regulation is tested by using a 10ms current pulse and measuring VTT.

- Note3. The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction to ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub> exceeding the maximum allowable power dissipation will cause excessive die temperature and the regulator will go into thermal shutdown. Ensured by design, no production tested.

- Note4. Limits are 100% production tested at 25°C. Limits over operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate average outgoing quality level.

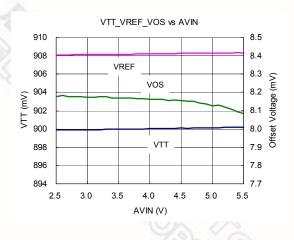

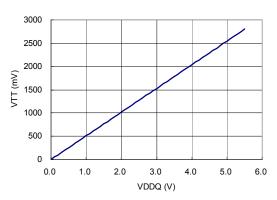

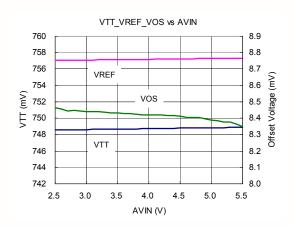

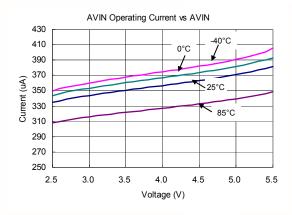

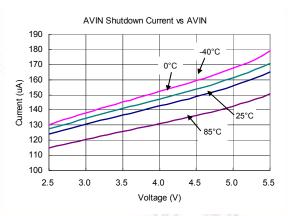

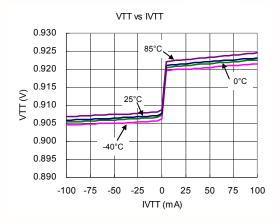

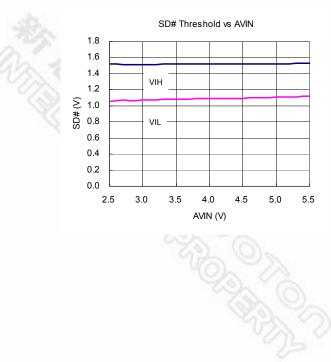

### 8. TYPICAL OPERATING CHARACTERISTICS AND WAFEFORMS

-11-

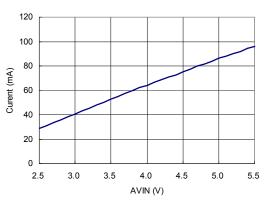

VREF Sourcing Current Limit vs AVIN

VREF Sinking Current Limit vs AVIN

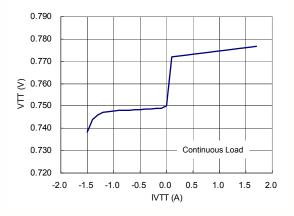

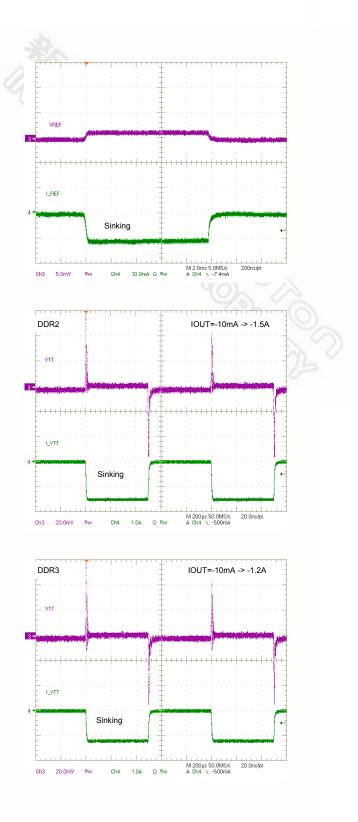

#### **Operating Waveforms**

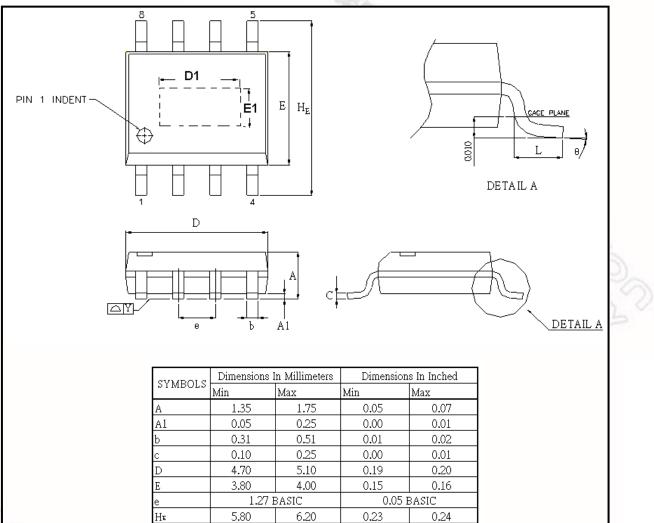

### 9. PACKAGE DIMENSION

0.10

1.27

10°

3.50

2.60

---

0.40

0°

1.94 ·

1.94

0.00

0.05

10°

0.14

0.10

---

0.02

0°

0.08

0.08

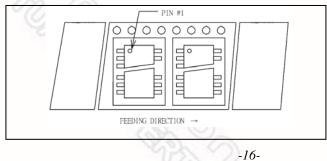

### **Taping Specification**

Y

θ

D1

E1

### 10. ORDERING INFORMATION age

| Part Number | Package Type                 | Supplied as              | Production Flow             |

|-------------|------------------------------|--------------------------|-----------------------------|

| NCT3107S    | 8PIN ESOP (Green<br>Package) | T Shape: 2,500 units/T&R | Commercial, -40°C to + 85°C |

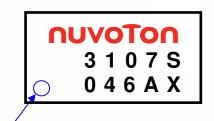

### **11. TOP MARKING SPECIFICATION**

#### Pin 1 index

1<sup>st</sup> Line: Nuvoton logo

2<sup>nd</sup> Line: 3107S (NCT3107S)

3<sup>rd</sup> line: Tracking code

- <u>046</u>: packages assembled in Year 2010, week 46

- <u>A</u>: assembly house ID.

- <u>X</u>: IC version. (A means A; B means B and C means C...etc.

### **12. REVISION HISTORY**

| VERSION | DATE       | PAGE           | DESCRIPTION                          |

|---------|------------|----------------|--------------------------------------|

| A0      | 2010/12/17 | All            | First Published                      |

| A1      | 2011/1/17  | 8              | Add PCB Layout Guideline             |

|         |            | 8, 16, 17 & 19 | 1. Modified Recommended Land Pattern |

| A2      | 2011/11/10 |                | 2. Modified Thermal Pad Dimension    |

| AZ      | 2011/11/10 |                | 3. Modified Ordering Information     |

|         |            |                | 4. Modified Importance Notice        |

### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.