Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# NCT5917W Nuvoton Level translating I2C-bus/SMBus Repeater

Date: Oct./08/2012 Revision: 1.0

## **NCT5917W Datasheet Revision History**

|   | PAGES | DATES      | VERSION | MAIN CONTENTS        |

|---|-------|------------|---------|----------------------|

| 1 |       | 2012/01/17 | 0.1     | Draft version.       |

| 2 |       | 2012/05/15 | 0.5     | Preliminary version. |

| 3 |       | 2012/10/08 | 1.0     | Public release       |

|   |       |            |         | 20°C                 |

|   |       |            |         |                      |

|   |       |            |         |                      |

|   |       |            |         |                      |

- I -

Release Date: Oct., 2012

### **NCT5917W**

# nuvoTon

| Tabl |       | Content-                     |    |

|------|-------|------------------------------|----|

| 1.   | GEN   | NERAL DESCRIPTION            | 1  |

| 2.   |       | TURES                        |    |

| 3.   |       | OCK DIAGRAM                  |    |

| 4.   | PIN ( | CONFIGURATION                | 2  |

|      | 4.1   |                              |    |

| 5.   | FUN   | ICTIONAL DESCRIPTION         |    |

|      | 5.1   | Enable Pin                   | 7  |

| 6.   | ELE   | CTRICAL CHARACTERISTICS      | 8  |

|      | 6.1   | Absolute Maximum Ratings     |    |

|      | 6.2   | DC Characteristics           |    |

|      | 6.3   | AC CHARACTERISTICS           | 11 |

|      | 6.4   | Test Information             | 12 |

| 7.   | ORD   | DER INSTRUCTION              | 13 |

| 8.   | TOP   | MARKING SPECIFICATION        | 13 |

| 9.   | TAP   | PING SPECIFICATION           | 13 |

| 10.  | PAC   | CKAGE DRAWING AND DIMENSIONS | 14 |

### 1. GENERAL DESCRIPTION

The NCT5917W is a CMOS integrated circuit that provides bidirectional level shifting between higher voltage (2.7 V to 5.5 V) and low voltage (down to 0.9 V) up to 400KHz for SMBus<sup>™</sup> applications. While retaining all the operating modes and features of the I2C-bus system during the level shifts, it also permits extension of the I<sup>2</sup>C-bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus enabling two buses of 400pF. The SDA and SCL pins are over voltage 5V tolerant and are high-impedance when the NCT5917W is unpowered.

The NCT5917W drivers are not enabled unless  $V_{CCB}$  is above 2.5 V and  $V_{CCA}$  is above 0.8 V. The EN pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the enable pin when the bus is idle.

The output pull-down on the B-side internal buffer LOW is set for approximately 0.5 V, while the input threshold of the internal buffer is set about 70 mV lower (0.43 V). When the B-side I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on the A-side drives a hard LOW and the input level is set at 0.3V<sub>CCA</sub> to accommodate the need for a lower LOW level in systems where the low voltage side supply voltage is as low as 0.9 V. The NCT5917W is packaged in MSOP-8 type.

### 2. FEATURES

- 2 channels, bidirectional voltage level from 0.9V to 5.5V and from 2.7V to 5.5V

- A side operating supply voltage VCCA range from 0.9V to 5.5V

- B side operating supply voltage VCCB range from 2.7V to 5.5V

- Isolates Input/output sides

- I<sup>2</sup>C® Compatible System Management bus (SMBus<sup>TM</sup>) operated up to 400 KHz

- High active's enable input

- 5V tolerant I<sup>2</sup>C-bus and active high enable pin

- high-impedance for I<sup>2</sup>C-bus pins in power-off (V<sub>CCA</sub><0.5 or V<sub>CCB</sub><2.0)</li>

- 8-pin MSOP Green Package (Halogen-free)

- ESD protection exceeds 6KV HBM, 500V MM, and 1KV CDM

- Latch-up exceeds 100mA

Release Date: Oct., 2012

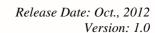

### 3. BLOCK DIAGRAM

Figure 1 – Functional Diagram

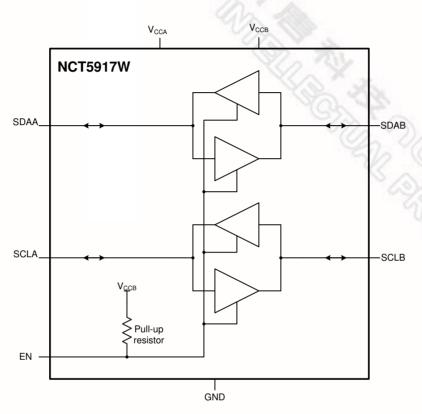

### 4. PIN CONFIGURATION

### 4.1 Pin Description

| PIN | NAME             | DESCRIPTION                          |

|-----|------------------|--------------------------------------|

| 1   | V <sub>CCA</sub> | A-side supply voltage (0.9V to 5.5V) |

| 2   | SCLA             | Serial clock bus, A side.            |

| 3   | SDAA             | Serial data bus, A side.             |

| 4   | GND              | Supply ground                        |

| 5   | EN               | Active-high repeater enable input.   |

| 6   | SDAB             | Serial data bus, B side.             |

| 7   | SCLB             | Serial clock bus, B side.            |

| 8   | V <sub>CCB</sub> | B-side supply voltage (2.7V to 5.5V) |

Release Date: Oct., 2012

### 5. FUNCTIONAL DESCRIPTION

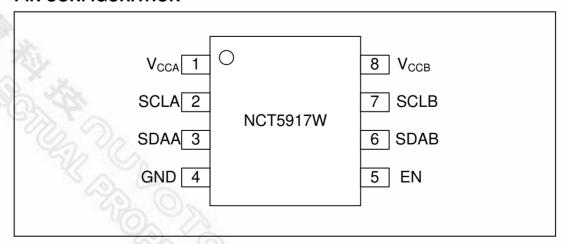

A typical application is shown in Figure 2. In this example, the system master is running on a 3.3 V  $I^2$ C-bus while the slave is connected to a 1.2 V bus. Both buses run at 400 kHz. Master devices can be placed on either bus.

Figure 2 - Typical Application

The NCT5917W is 5 V tolerant, so it does not require any additional circuitry to translate between 0.9 V to 5.5 V bus voltages and 2.7 V to 5.5 V bus voltages.

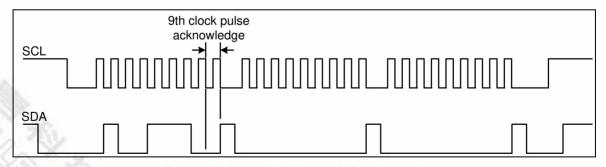

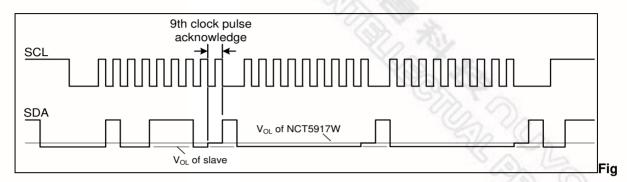

When the A-side of the NCT5917W is pulled LOW by a driver on the I<sup>2</sup>C-bus, a comparator detects the falling edge when it goes below 0.3VccA and causes the internal driver on the B-side to turn on, causing the B-side to pull down to about 0.5 V. When the B-side of the NCT5917W falls, first a CMOS hysteresis type input detects the falling edge and causes the internal driver on the A-side to turn on and pull the A-side pin down to ground. In order to illustrate what would be seen in a typical application, refer to Figure 6 and Figure 7. If the bus master in Figure 2 were to write to the slave through the NCT5917W, waveforms shown in Figure 6 would be observed on the A bus. This looks like a normal I<sup>2</sup>C-bus transmission except that the HIGH level may be as low as 0.9 V, and the turn on and turn off of the acknowledge signals are slightly delayed.

On the B bus side of the NCT5917W, the clock and data lines would have a positive offset from ground equal to the Vol of the NCT5917W B side. After the 8th clock pulse, the data line will be pulled to the Vol of the NCT5917W in this example. At the end of the acknowledge, the level rises from the LOW level set by the driver in the NCT5917W while the A bus side rises above 0.3VccA, then it

Release Date: Oct., 2012

continues HIGH. It is important to note that any arbitration or clock stretching events require that the LOW level on the B bus side at the input of the NCT5917W (VIL) be at or below 0.4 V to be recognized by the NCT5917W and then transmitted to the A bus side.

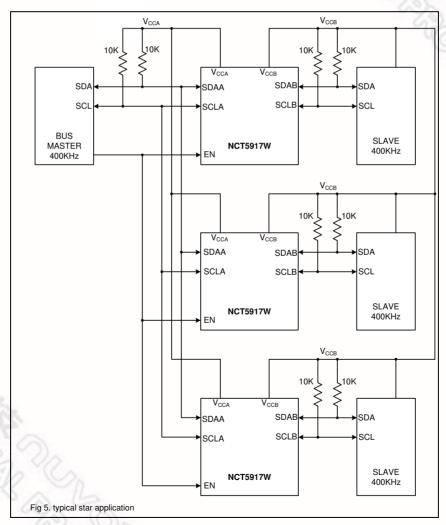

Multiple NCT5917W A-sides can be connected in a star configuration (Figure 3), allowing all nodes to communicate with each other.

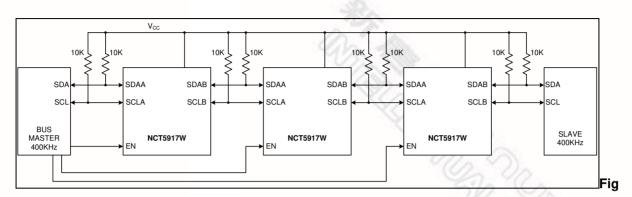

Multiple NCT5917Ws can be connected in series (Figure 4) as long as the A-side is connected to the B-side. I<sup>2</sup>C-bus slave devices can be connected to any of the bus segments. The number of devices that can be connected in series is limited by repeater delay/time-of-flight considerations on the maximum bus speed requirements.

Figure 3 - Typical star application

Figure 4 - Typical series application

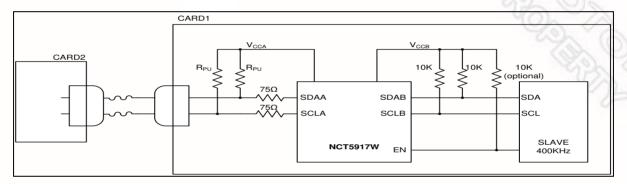

Figure 5 - Typical Application of NCT5917 driving a short cable

Figure 6 - Bus A (0.9V to 5.5V bus) waveform

- 6 -

Figure 7 - Bus B (2.7V to 5.5V bus) waveform

### 5.1 Enable Pin

The EN pin is active HIGH with an internal pull-up to VCCB and allows the user to select when the repeater is active. This can be used to isolate a badly behaved slave on power-up until after the system power-up reset. It should never change state during and I<sup>2</sup>C-bus operation because disabling during a bus operation will hang the bus and enabling part way through a bus cycle could confuse the I<sup>2</sup>C-bus parts being enabled.

The enable pin should only change state when the global bus and the repeater port are in an idle state to prevent system failures.

| INPUT EN | FUNCTION       |  |  |

|----------|----------------|--|--|

| L        | Output Disable |  |  |

| (A)      | SDAA = SDAB    |  |  |

| T all    | SCLA = SCLB    |  |  |

- 7 -

Release Date: Oct., 2012

### 6. ELECTRICAL CHARACTERISTICS

### 6.1 Absolute Maximum Ratings

| PARAMETER                                                   | RATING      | UNIT |  |

|-------------------------------------------------------------|-------------|------|--|

| Power Supply Voltage (V <sub>CCA</sub> , V <sub>CCB</sub> ) | -0.5 to 6.0 | V    |  |

| Input/Output Voltage                                        | -0.5 to 6.0 | V    |  |

| Operating Temperature (in free air)                         | -40 to +85  | ° C  |  |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

### 6.2 DC Characteristics

$V_{\text{CC}}$ =2.7V to 5.5V; GND=0V;  $T_{\text{amb}}$ =-40  $\,^{\circ}\!\!$ C to 85 $\,^{\circ}\!\!$ C; unless otherwise specified.

| Symbol                | Parameter                              | Conditions                                                                                 | Min                 | Тур  | Max          | Unit    |

|-----------------------|----------------------------------------|--------------------------------------------------------------------------------------------|---------------------|------|--------------|---------|

| V <sub>CCB</sub>      | Supply voltage, B-side bus             |                                                                                            | 2.7                 | -    | 5.5          | ٧       |

| V <sub>CCA</sub>      | Supply voltage, A-side bus             |                                                                                            | <sup>[1]</sup> 0.9  | -    | 5.5          | ٧       |

| I <sub>CC(VCCA)</sub> | Supply current on pin V <sub>CCA</sub> |                                                                                            | -                   | -    | 1            | mA      |

| I <sub>CCH</sub>      | HIGH-state supply current              | Both channels HIGH; $V_{CC} = 5.5V$ ; $SDAn = SCLn = V_{CC}$                               | -                   | 1.5  | 5            | mA      |

| Iccl                  | HIGH-state supply current              | Both channels LOW;<br>$V_{CC} = 5.5V$ ;<br>One SDA and one SCL = GND<br>SDAn = SCLn = open | -                   | 1.5  | 5            | mA      |

| I <sub>CCAc</sub>     | Quiescent supply current in contention | $V_{CC} = 5.5V$ ;<br>SDAn = SCLn = $V_{CC}$                                                | -                   | 1.5  | 5            | mA      |

| Input and             | d output SDAB and SCLB                 |                                                                                            |                     |      |              |         |

| $V_{IH}$              | HIGH-level input voltage               |                                                                                            | 0.7V <sub>C</sub>   | -    | 5.5          | ٧       |

| V <sub>IL</sub>       | LOW-level input voltage                |                                                                                            | <sup>[2]</sup> -0.5 | -    | +0.3V<br>CCB | V       |

| V <sub>ILc</sub>      | LOW-level input voltage contention     |                                                                                            | -0.5                | 0.4  | -            | ٧       |

| $V_{ILK}$             | Input clamping voltage                 | I <sub>I</sub> =-18mA                                                                      | -                   | -    | -1.2         | V       |

| ILI                   | Input leakage current                  | V <sub>I</sub> =3.6V                                                                       | -                   | -    | ±1           | $\mu$ A |

| I <sub>IL</sub>       | LOW-level input current                | SDA, SCL; V <sub>I</sub> = 0.2V                                                            | -                   | -    | 10           | $\mu$ A |

| V <sub>OL</sub>       | LOW-level output voltage               | IOL= 100 μ A or 6mA                                                                        | 0.47                | 0.52 | 0.6          | ٧       |

| Symbol                            | Parameter                                                    | Conditions                          | Min                 | Тур  | Max          | Unit    |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------|---------------------|------|--------------|---------|

| V <sub>OL</sub> -V <sub>ILC</sub> | LOW-level input voltage<br>below output LOW-level<br>voltage | Guaranteed by design                | -                   | 70   | -            | mV      |

| I <sub>LOH</sub>                  | HIGH-level output leakage current                            | V <sub>O</sub> = 3.6V               |                     | -    | 10           | $\mu$ A |

| 0                                 | logot/outrout compaiton                                      | VI=3V or 0V; VCC=3.3V               |                     | 6    | _            |         |

| Cio                               | Input/output capacitance                                     | VI=3V or 0V; VCC=0V                 | X                   | б    | 7            | pF      |

| Input and                         | d output SDAA and SCLA                                       | 100                                 | 2.0                 | 12   |              |         |

| V <sub>IH</sub>                   | HIGH-level input voltage                                     |                                     | 0.7V <sub>C</sub>   | (8)  | 5.5          | V       |

| $V_{IL}$                          | LOW-level input voltage                                      |                                     | <sup>[3]</sup> -0.5 | 2    | +0.3V<br>CCA | V       |

| V <sub>ILK</sub>                  | Input clamping voltage                                       | I <sub>I</sub> =-18mA               | -                   | (3)  | -1.2         | V       |

| ILI                               | Input leakage current                                        | V <sub>I</sub> =3.6V                | -                   | Vi   | ±1           | $\mu$ A |

| I <sub>IL</sub>                   | LOW-level input current                                      | SDA, SCL; V <sub>I</sub> = 0.2V     | -                   | -    | 10           | $\mu$ A |

| V <sub>OL</sub>                   | LOW-level output voltage                                     | IOL= 6mA                            | -                   | 0.15 | 0.2          | V       |

| I <sub>LOH</sub>                  | HIGH-level output leakage current                            | V <sub>O</sub> = 3.6V               | -                   | -    | 10           | $\mu$ A |

| 0                                 | log. d/o. de. de o o o o ido o o o                           | VI=3V or 0V; VCC=3.3V               |                     | 6    | -            | 9       |

| Cio                               | Input/output capacitance                                     | VI=3V or 0V; VCC=0V                 | -                   |      | 7            | pF      |

| <b>ENable</b>                     |                                                              |                                     |                     |      |              |         |

| $V_{IL}$                          | LOW-level input voltage                                      |                                     | <sup>[2]</sup> -0.5 | ı    | +0.3V<br>CCB | V       |

| V <sub>IH</sub>                   | HIGH-level input voltage                                     |                                     | 0.7V <sub>C</sub>   | -    | 5.5          | V       |

| I <sub>IL(EN)</sub>               | LOW-level input current on pin EN                            | V <sub>I</sub> = 0.2V, EN; Vcc=3.6V | -                   | -10  | -30          | $\mu$ A |

| ILI                               | Input leakage current                                        |                                     | -1                  | -    | +1           | $\mu$ A |

| C <sub>i</sub>                    | Input capacitance                                            | V <sub>I</sub> =3.0V or 0V          | -                   | 6    | 7            | pF      |

Release Date: Oct., 2012 Version: 1.0

- 9 -

<sup>[1]</sup> LOW-level supply voltage.

[2] VIL specification is for the first LOW level seen by the SDAB/SCLB lines. VILc is for the second and subsequent LOW levels seen by the SDAB/SCLB lines.

<sup>[3]</sup> VIL for A-side with envelope noise must be below 0.3Vcca for stable performance.

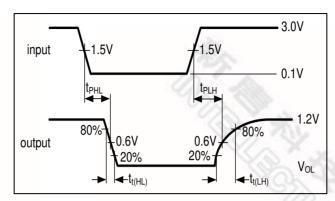

Figure 8 - Propagation delay and transition times; B-side to A-side

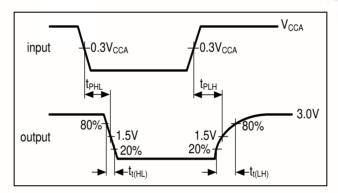

Figure 9 - Propagation delay and transition times; A-side to B-side

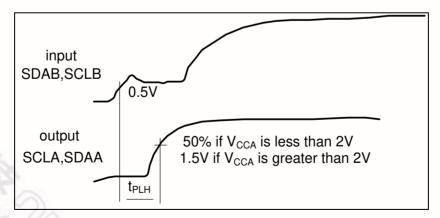

Figure 10 - Propagation delay

### 6.3 AC CHARACTERISTICS

$V_{CC}$ =2.7V to 5.5V; GND=0V;  $T_{amb}$ =-40 °C to 85°C; unless otherwise specified. [1][2]

| Symbol           | Parameter                     | Conditions                                                   | Min               | Тур               | Max | Unit |

|------------------|-------------------------------|--------------------------------------------------------------|-------------------|-------------------|-----|------|

| t <sub>PLH</sub> | LOW-to-HIGH propagation delay | B-side to A-side; figure 10                                  | [4]<br>100        | 140               | 250 | ns   |

|                  | HIGH-to-LOW propagation       | B-side to A-side; <u>figure 8</u><br>V <sub>CCA</sub> ≤ 2.7V | 30                | <sup>[5]</sup> 23 | 110 | ns   |

| t <sub>PHL</sub> | delay                         | B-side to A-side; <u>figure 8</u><br>V <sub>CCA</sub> ≥ 3V   | 10                | 40                | 300 | ns   |

| $t_{t(LH)}$      | LOW-to-HIGH transition time   | A-side; figure 8                                             | 10                | 14                | 30  | ns   |

|                  | HIGH-to-LOW transition time   | A-side; <u>figure 8</u><br>V <sub>CCA</sub> ≤ 2.7V           | -                 | <sup>[5]</sup> 2  | 105 | ns   |

| $t_{t(HL)}$      |                               | A-side; <u>figure 8</u><br>V <sub>CCA</sub> ≥ 3V             | -                 | 4                 | 175 | ns   |

| t <sub>PLH</sub> | LOW-to-HIGH propagation delay | A-side to B-side; figure 9                                   | <sup>[6]</sup> 25 | 103               | 110 | ns   |

| t <sub>PHL</sub> | HIGH-to-LOW propagation delay | A-side to B-side; figure 9                                   | <sup>[6]</sup> 60 | 94                | 230 | ns   |

| $t_{t(LH)}$      | LOW-to-HIGH transition time   | B-side; <u>figure 9</u>                                      | -                 | 113               | 170 | ns   |

| $t_{t(HL)}$      | HIGH-to-LOW transition time   | B-side; figure 9                                             | -                 | <sup>[5]</sup> 19 | 90  | ns   |

| t <sub>su</sub>  | set-up time                   | EN HIGH before START condition                               | [7]<br>100        | -                 | -   | ns   |

| t <sub>h</sub>   | hold time                     | EN HIGH after STOP condition                                 | [7]<br>100        | -                 | -   | ns   |

<sup>[1]</sup> Times are specified with loads of 1.35 k $\Omega$  pull-up resistance and 57 pF load capacitance on the B-side, and 167  $\Omega$  pull-up resistance and 57 pF load capacitance on the A-side. Different load resistance and capacitance will alter the RC time constant, thereby changing the propagation delay and transition times.

<sup>[2]</sup> Pull-up voltages are VCCA on the A-side and VCCB on the B-side.

<sup>[3]</sup> Typical values were measured with VCCA = 3.3 V at Tamb = 25 °C, unless otherwise noted.

<sup>[4]</sup> The tPLH delay data from B-side to A-side is measured at 0.5 V on the B-side to 0.5 VCCA on the A-side when VCCA is less than 2 V, and 1.5 V on the A-side if Vcca is greater than 2 V.

<sup>[5]</sup> Typical value measured with VCCA = 0.9 V at Tamb = 25 °C.

<sup>[6]</sup> The proportional delay data from A-side to B-side is measured at 0.3VccA on the A-side to 1.5 V on the B-side.

ρin, τ [7] The enable pin, EN, should only change state when the global bus and the repeater port are in an idle state.

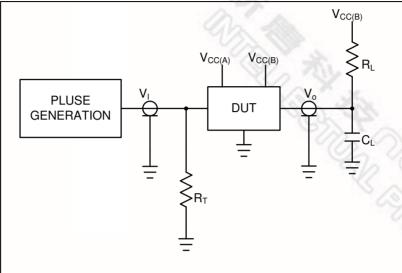

### 6.4 Test Information

$R_L =$  load resistor; 1.35k $\Omega$  on B-side; 167 $\Omega$  on A-side(0.9V to 2.7V) and 450  $\Omega$  on A-side(3.0V to 5.5V).

C<sub>L</sub>= load capacitance include jig and probe capacitcance;57pF

$R_{T}$ = termination resistance should be equal  $Z_0$  of pulse generators

Figure 11 - Test circuit for open-drain outputs

- 12 -

Release Date: Oct., 2012

### 7. ORDER INSTRUCTION

| PART NO.   | PACKAGE       | SUPPLIED AS                      |  |  |

|------------|---------------|----------------------------------|--|--|

| NCT5917W   | MSOP-8        | E shape (Tube)                   |  |  |

| 1101391700 | Green Package | T shape (Tape & Reel); MOQ=4Kpcs |  |  |

### 8. TOP MARKING SPECIFICATION

5917W 215GA

1<sup>st</sup> line: Part number: **5917W** means NCT5917W

2<sup>nd</sup> line: Assembly tracking code

2 15 : packages made in year 2012, week 15

**G**: Assembly house code

A: Nuvoton internal tracking code

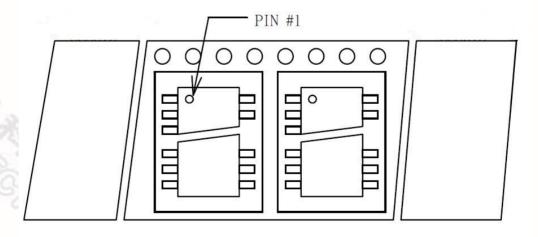

### 9. TAPING SPECIFICATION

- 13 -

FEEDING DIRECTION →

Release Date: Oct., 2012

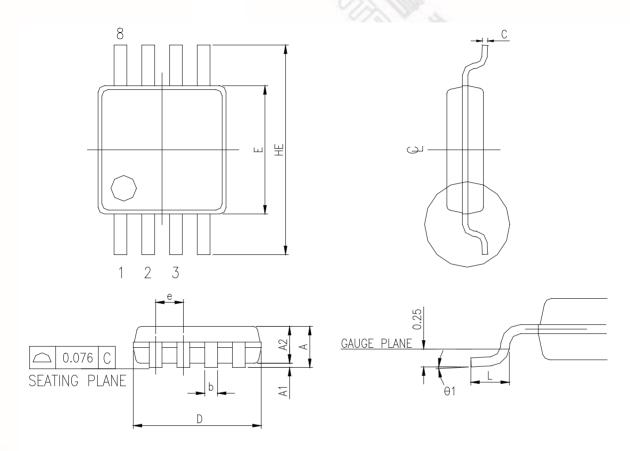

# 10. PACKAGE DRAWING AND DIMENSIONS MSOP-8L 3 X 3mm

CONTROLLING DIMENSION: MILLIMETERS

| SYMBOL | DIMENSION IN MM |          |       | DIMENSION IN INCH |           |        |  |

|--------|-----------------|----------|-------|-------------------|-----------|--------|--|

|        | MIN.            | NOM.     | MAX.  | MIN.              | NOM.      | MAX.   |  |

| А      |                 |          | 1.10  |                   |           | 0.043  |  |

| A1     | 0.05            |          | 0.15  | 0.002             |           | 0.006  |  |

| A2     | 0.81            | 0.86     | 0.91  | 0.032             | 0.034     | 0.036  |  |

| С      | 0.13            |          | 0.23  | 0.005             |           | 0.009  |  |

| b      | 0.25            |          | 0.40  | 0.0098            |           | 0.0157 |  |

| D      | 2.90            | 3.00     | 3.10  | 0.114             | 0.118     | 0.122  |  |

| E      | 2.90            | 3.00     | 3.10  | 0.114             | 0.118     | 0.122  |  |

| HE     |                 | 4.90 BSC |       |                   | 0.193 BSC |        |  |

| L      | 0.445           | 0.55     | 0.648 | 0.0175            | 0.0217    | 0.0255 |  |

| 01     | 0°              |          | 6°    | 0°                |           | 6°     |  |

| е      |                 | 0.65 BS  | С     | 0.026 BSC         |           |        |  |

Release Date: Oct., 2012 Version: 1.0

- 14 -

### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

Release Date: Oct., 2012