# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Test Procedure for the NCV47411PAAJGEVB Evaluation Board**

The NCV47411 is dual channel adjustable Low Dropout Regulator with:

- Two adjustable output voltages from 3.3 V to 20 V

- Two adjustable current limits up to 150 mA

- Enable inputs with 3.3 V Logic compatible thresholds

Power supplying of the chip is possible from one or two independent sources. **INPUT1** must be always supplied and **INPUT2** as optional for  $V_{in2}$  supply.

#### 1. Power supplying

#### a. Power supplying from one source

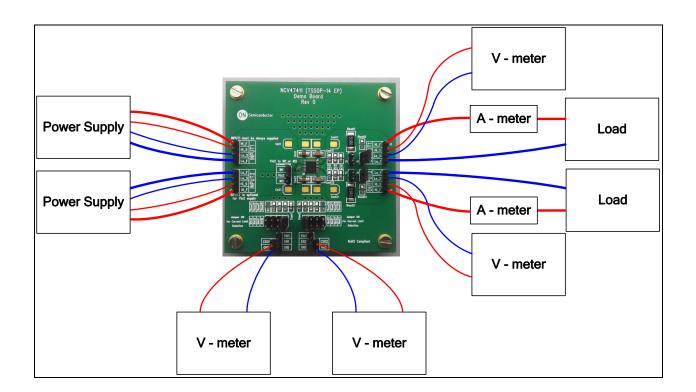

Connect the test setup as is shown in Figure 1 (See Table 1 with required equipment). Connect power supply to INPUT1 connector  $J_1$  (Power supplying of INPUT2 is not needed).

- **Hi\_F** Positive Force line

- **Hi\_S** Positive Sense line

- **Lo\_F** Negative Force line

- Lo\_S Negative Sense line

Connect V<sub>in2</sub> pin to INPUT1 via appropriate position of jumper "V<sub>in2</sub> to IN1 or IN2 connection".

#### b. Power supplying from two sources

Connect the test setup as is shown in Figure 1 (See Table 1 with required equipment). Connect two power supplies to INPUT1 connector  $J_1$  and to INPUT2 connector  $J_2$ , respectively.

- **Hi\_F** Positive Force line

- **Hi\_S** Positive Sense line

- $\mathbf{Lo}\mathbf{F}$  Negative Force line

- Lo\_S Negative Sense line

Values of input voltages  $V_{in1}$  and  $V_{in2}$  can be different. This option is suitable for reducing of power dissipation on chip.

Connect  $V_{in2}$  pin to INPUT2 via appropriate position of jumper " $V_{in2}$  to IN1 or IN2 connection".

- 2. Connect jumpers  $J_{10} J_{13}$  for output current limitation from  $V_{out1}$  pin and  $J_{20} J_{23}$  for output current limitation from  $V_{out2}$  pin.

- $J_{n0} I_{LIMn0} \sim 10 \text{ mA}$

- $J_{n1} I_{LIMn1} \sim 50 \text{ mA}$

- $J_{n2} I_{LIMn2} \sim 100 \text{ mA}$

- $J_{n3} I_{LIMn3} R_{CSOn3}$  positions available for individual current limit setting by resistor from range 850  $\Omega$  to 12.75 k $\Omega$

- 3. Set Input Voltage and turn on Power Supply/Supplies.

- 4. Enable output of the channel to power the regulated output voltage by connecting the **ENABLE** pin to corresponding  $V_{in}$  via jumper. Enabling can be performed by external voltage source as well.

- 5. Load the outputs by resistive loads connected via jumpers:

- $J_{5}, J_{7} 51 \Omega$

- $J_6, J_8 1 k\Omega$

External loads can be used instead build-in resistive loads as well.

10/18/2012

#### www.onsemi.com

6. Monitor Output Voltages, given according to Equation 1.

$$V_{out\_nom\_n} = 1.275 \left(1 + \frac{R_{n1}}{R_{n2}}\right)$$

(eq. 1)

7. Monitor Current Sense Output voltages on appropriate connector. They should be max 2.55 V in steady state. The CSO voltages are proportional to output currents according to Equation 2.

$$V_{CSO_n} = I_{out_n} \left( R_{CSO_n} \times \frac{1}{50} \right)$$

(eq. 2)

8. Compare your results with measured results in Table 2.

Figure 1. General Test Setup

| Table 1: Kequirea Equipment |                  |

|-----------------------------|------------------|

| Equipment                   | Ranges           |

| Power Supply                | 0 V – 45 V / 1 A |

| Load                        | 0 mA – 500 mA    |

| V - meter                   | 0 V - 20 V       |

| A - meter                   | 0 mA – 500 mA    |

**Table 1: Required Equipment**

10/18/2012

www.onsemi.com

**ON Semiconductor®**

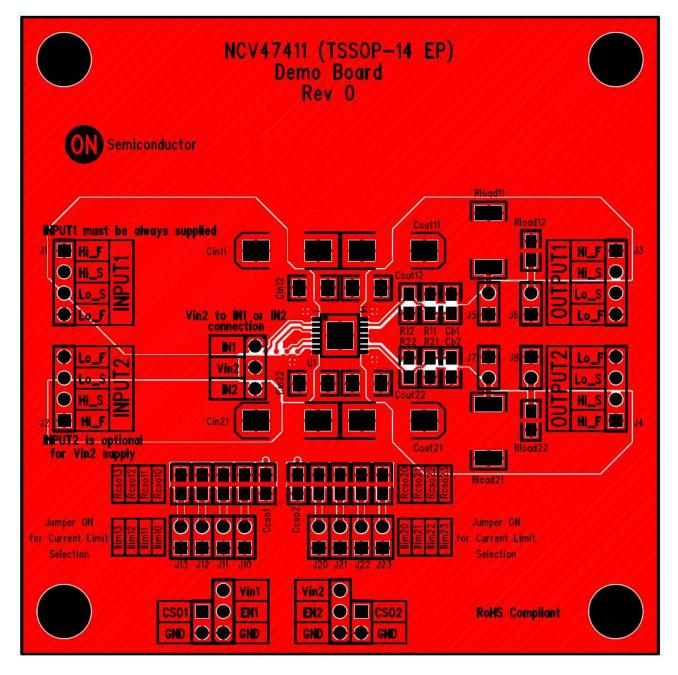

Figure 2. Top side PCB Layout (3 x 3 inch)

**ON Semiconductor®**

## Table 2: Measured Results

|                |                                                                                                                                                |                   | Value   |          |      |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|----------|------|

| Parameter      | Test Conditions                                                                                                                                | Symbol            | Nominal | Measured | Unit |

| Output Voltage | $V_{in}$ = 13.5 V, $V_{out\_nom\_n}$ = 5.02 V, $I_{out\_n}$ = 5 mA, $R_{CSO\_n}$ = Short to ground                                             | V <sub>out1</sub> | 5.02    | 5.006    | v    |

|                |                                                                                                                                                | V <sub>out2</sub> |         | 5.005    |      |

|                | $V_{in}$ = 13.5 V, $V_{out\_nom\_n}$ = 5.02 V, $I_{out\_n}$ = 100 mA, $R_{CSO\_n}$ = Short to ground                                           | V <sub>out1</sub> |         | 5.005    |      |

|                |                                                                                                                                                | V <sub>out2</sub> |         | 5.005    |      |

| Output Current | $V_{in} = 13.5 \text{ V}, V_{out\_nom\_n} = 5.02 \text{ V}, V_{out\_n} = 90 \% \text{ of } V_{out\_nom\_n}, R_{CSO\_n} = 12.7 \text{ k}\Omega$ | I <sub>out1</sub> | 10.04   | 10.06    | mA   |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 10       |      |

|                | $V_{in} = 13.5 \text{ V}, V_{out_nom_n} = 5.02 \text{ V}, V_{out_n} = 90 \% \text{ of } V_{out_nom_n}, R_{CSO_n} = 2.49 \text{ k}\Omega$       | I <sub>out1</sub> | 51.2    | 52.47    |      |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 52.19    |      |

|                | $V_{in}$ = 13.5 V, $V_{out\_nom\_n}$ = 5.02 V, $V_{out\_n}$ = 90 % of $V_{out\_nom\_n},$ $R_{CSO\_n}$ = 1.2 k $\Omega$                         | I <sub>out1</sub> | 106.25  | 110.28   |      |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 109.95   |      |

| Output Current | $V_{in} = 13.5 \text{ V}, V_{out_nom_n} = 5.02 \text{ V}, V_{out_n} = 0 \text{ V}, R_{CSO_n} = 12.7 \text{ k}\Omega$                           | I <sub>out1</sub> | 10.04   | 10.55    | mA   |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 10.49    |      |

|                | $V_{in} = 13.5 \text{ V}, V_{out\_nom\_n} = 5.02 \text{ V}, V_{out\_n} = 0 \text{ V}, R_{CSO\_n} = 2.49 \text{ k}\Omega$                       | I <sub>out1</sub> | 51.2    | 54.44    |      |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 54.17    |      |

|                | $V_{in} = 13.5 \text{ V}, V_{out_nom_n} = 5.02 \text{ V}, V_{out_n} = 0 \text{ V}, R_{CSO_n} = 1.2 \text{ k}\Omega$                            | I <sub>out1</sub> | 106.25  | 115.32   |      |

|                |                                                                                                                                                | I <sub>out2</sub> |         | 114.37   |      |